Chapter 1 Chapter 3 Circuit Under Design From

- Slides: 47

Chapter 1 & Chapter 3

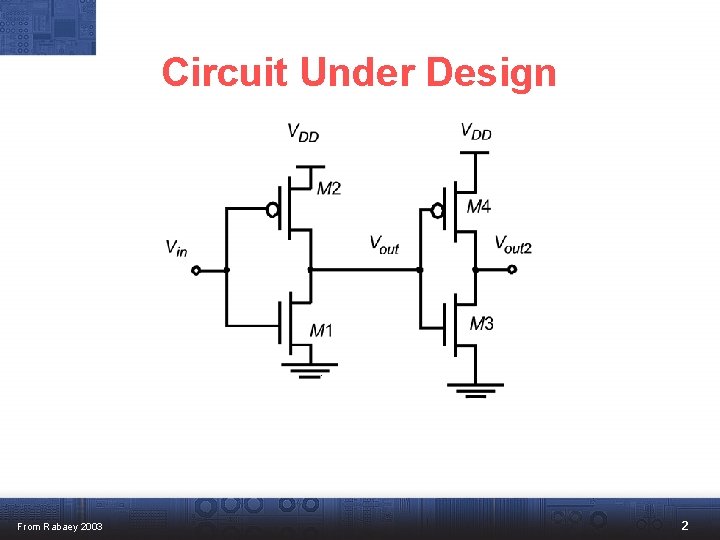

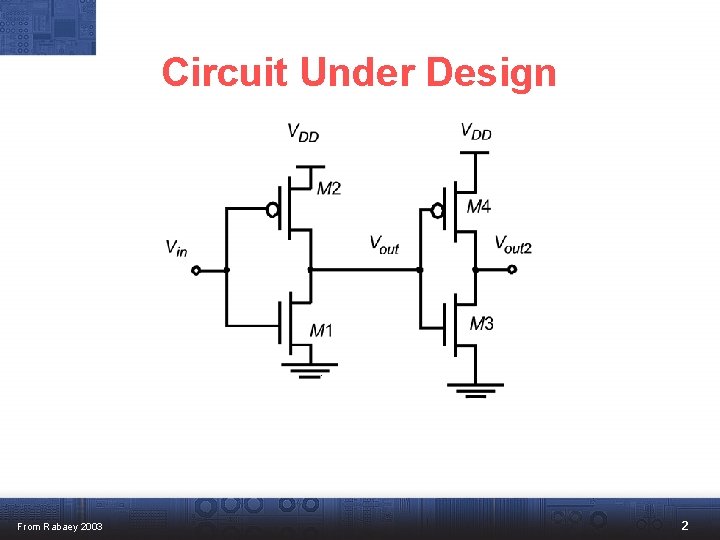

Circuit Under Design From Rabaey 2003 2

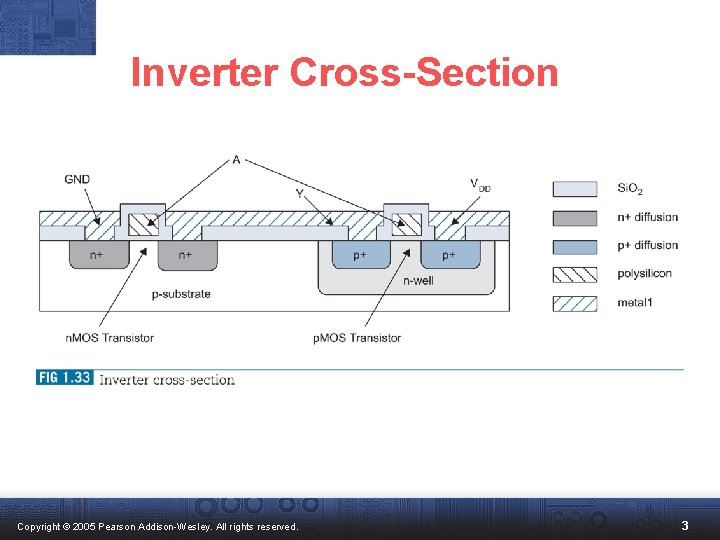

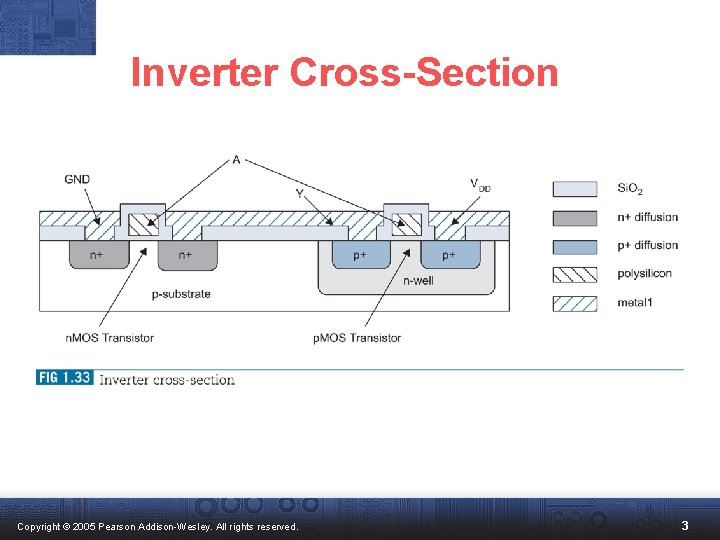

Inverter Cross-Section Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3

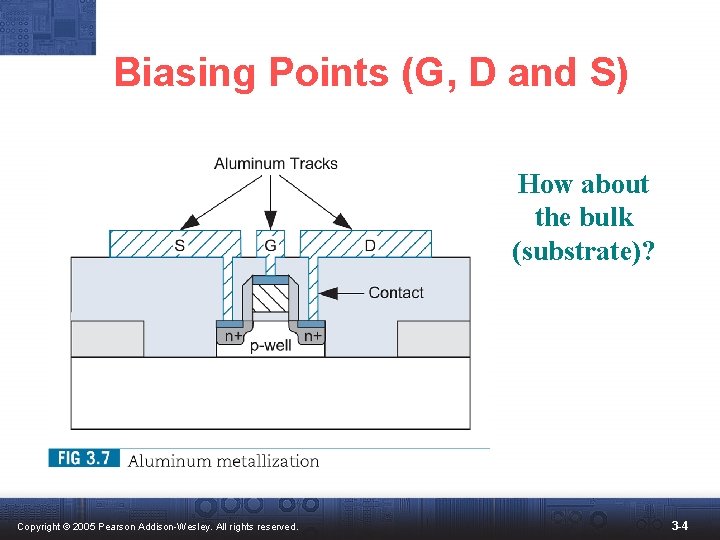

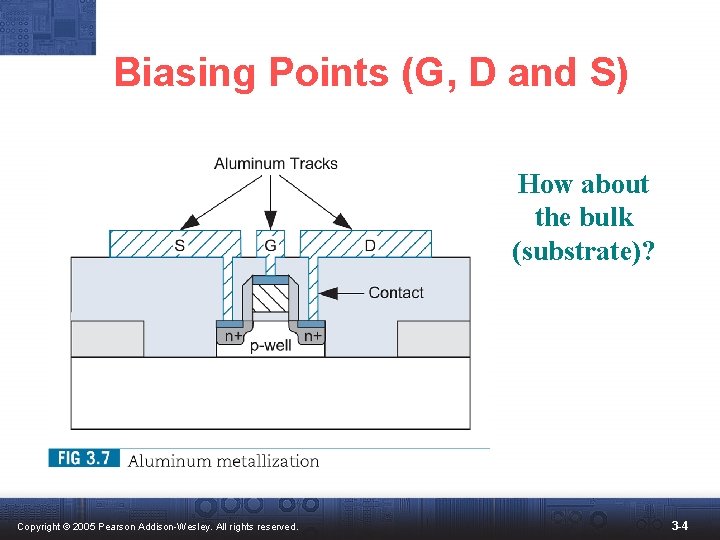

Biasing Points (G, D and S) How about the bulk (substrate)? Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -4

With Substrate Contacts Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 5

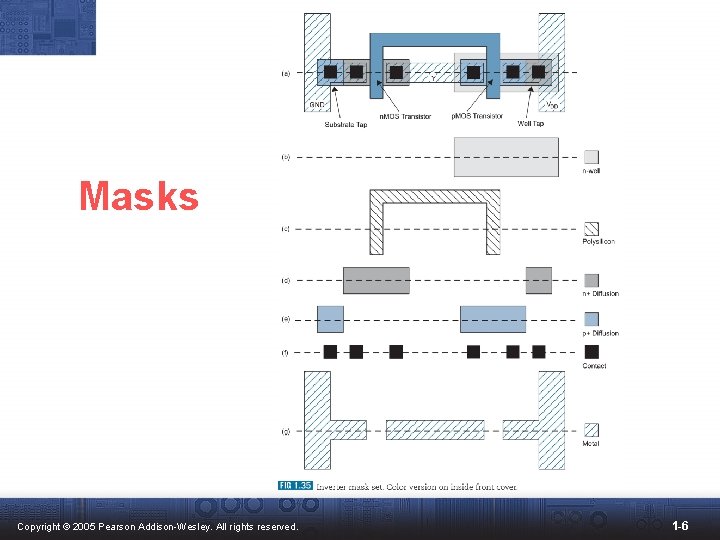

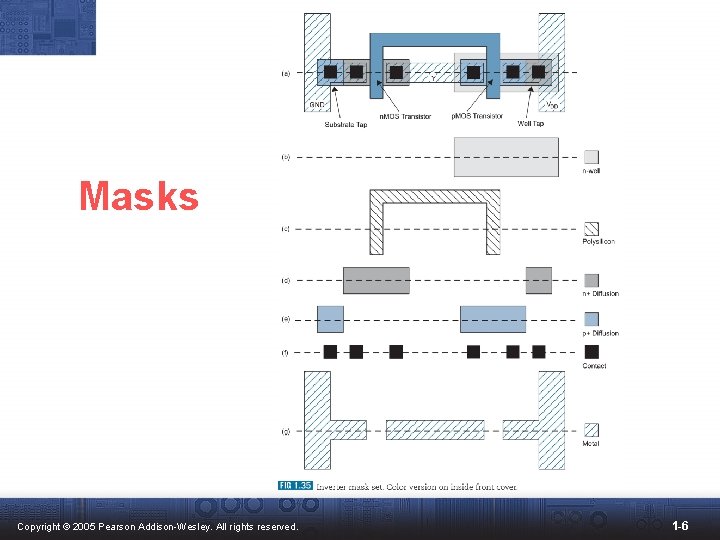

Masks Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -6

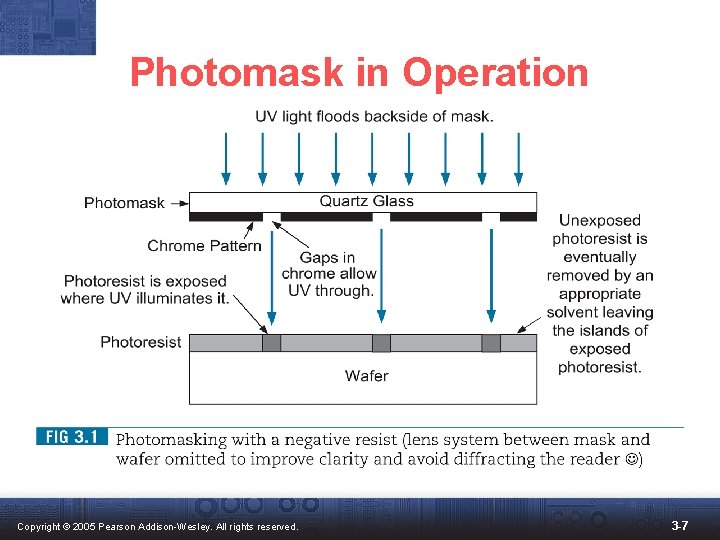

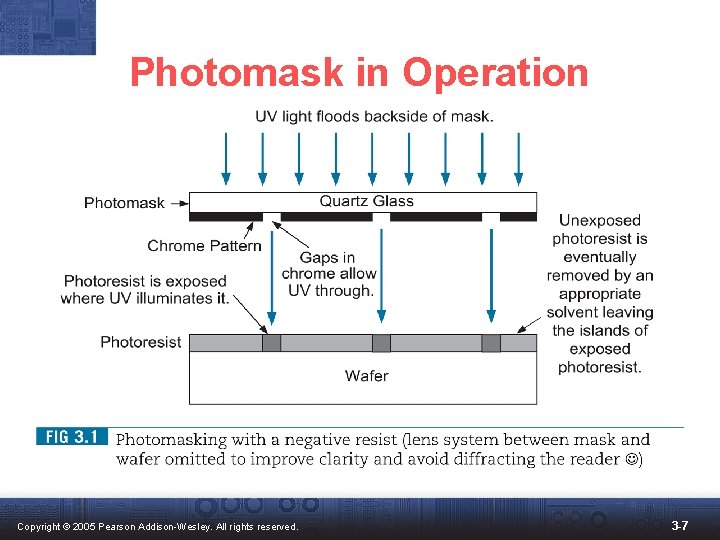

Photomask in Operation Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -7

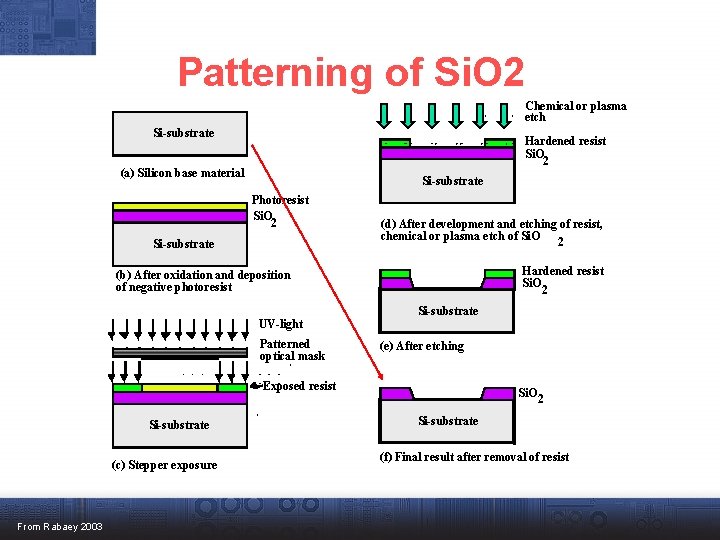

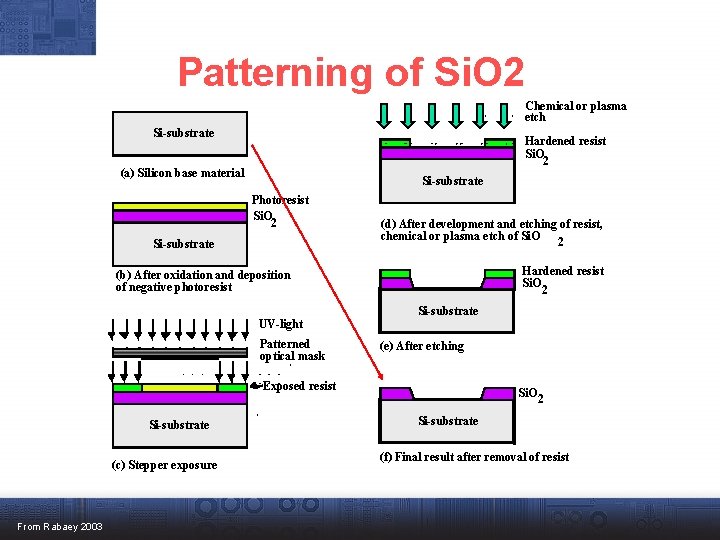

Patterning of Si. O 2 Chemical or plasma etch Si-substrate Hardened resist Si. O 2 (a) Silicon base material Si-substrate Photoresist Si. O 2 Si-substrate (d) After development and etching of resist, chemical or plasma etch of Si. O 2 Hardened resist Si. O 2 (b) After oxidation and deposition of negative photoresist UV-light Patterned optical mask Si-substrate (e) After etching Exposed resist Si-substrate (c) Stepper exposure From Rabaey 2003 Si. O 2 Si-substrate (f) Final result after removal of resist

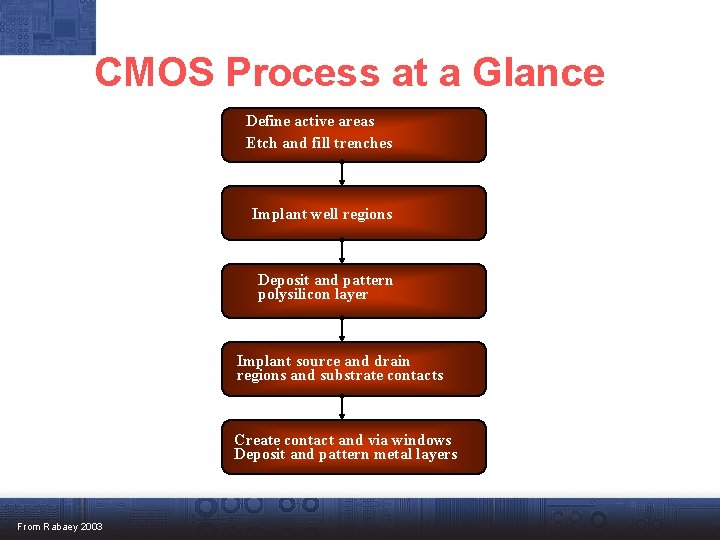

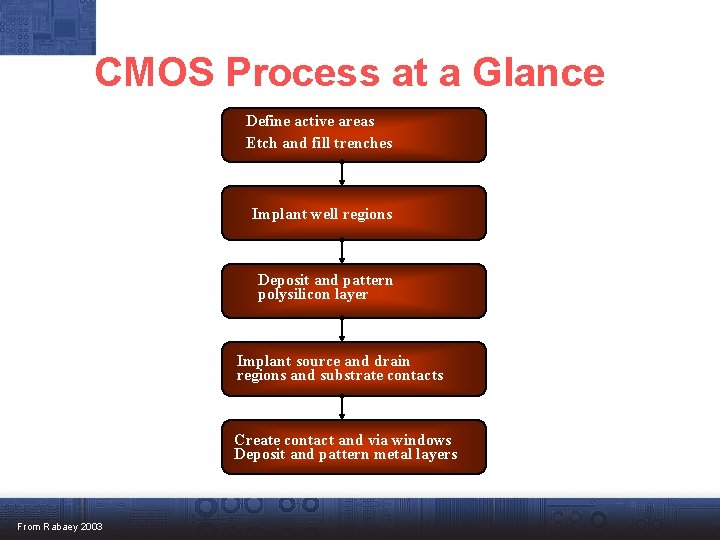

CMOS Process at a Glance Define active areas Etch and fill trenches Implant well regions Deposit and pattern polysilicon layer Implant source and drain regions and substrate contacts Create contact and via windows Deposit and pattern metal layers From Rabaey 2003

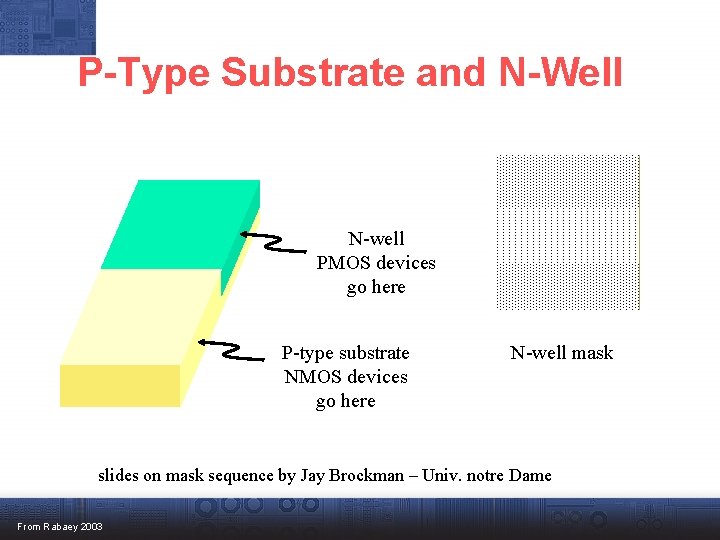

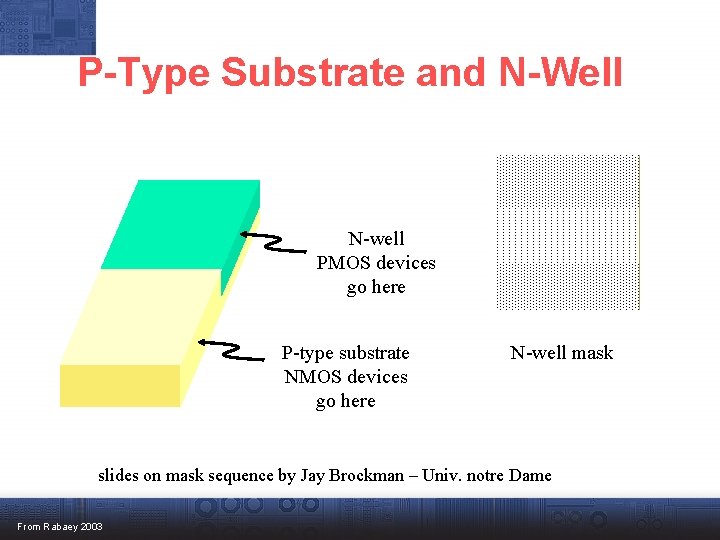

P-Type Substrate and N-Well N-well PMOS devices go here P-type substrate NMOS devices go here N-well mask slides on mask sequence by Jay Brockman – Univ. notre Dame From Rabaey 2003

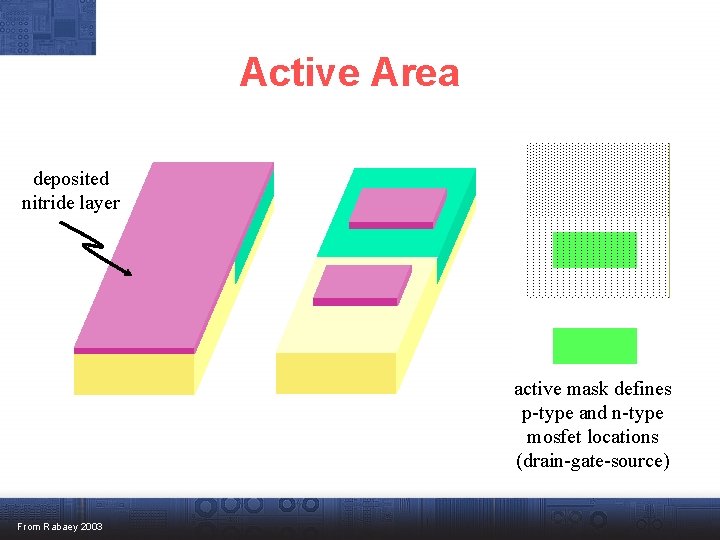

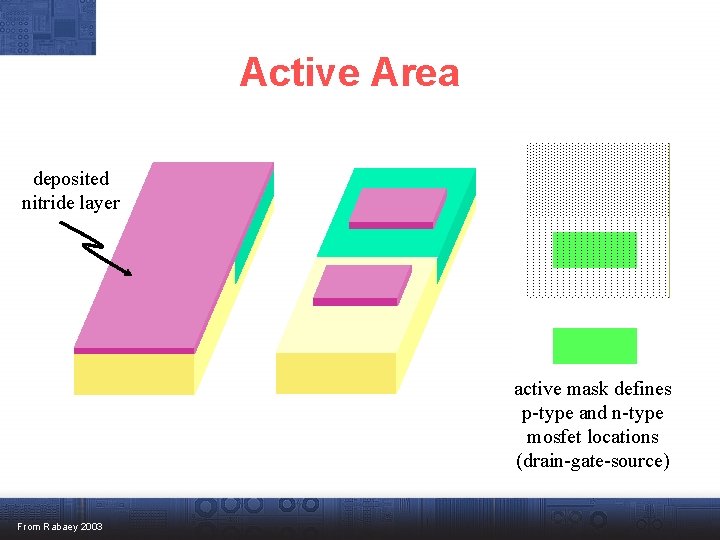

Active Area deposited nitride layer active mask defines p-type and n-type mosfet locations (drain-gate-source) From Rabaey 2003

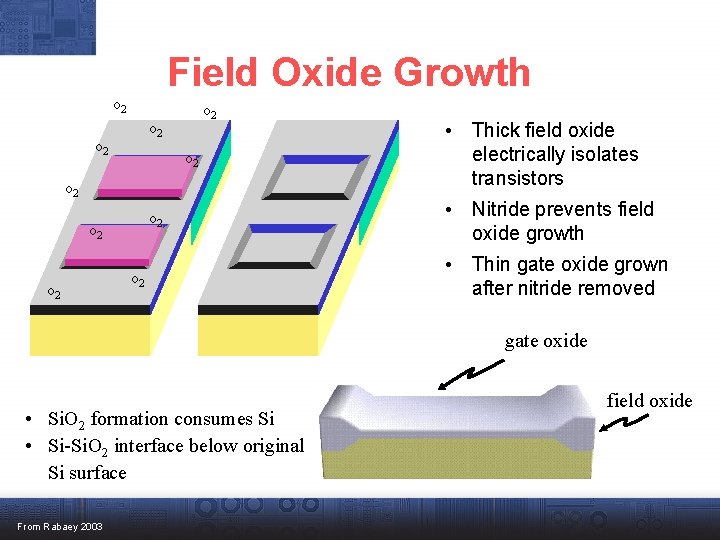

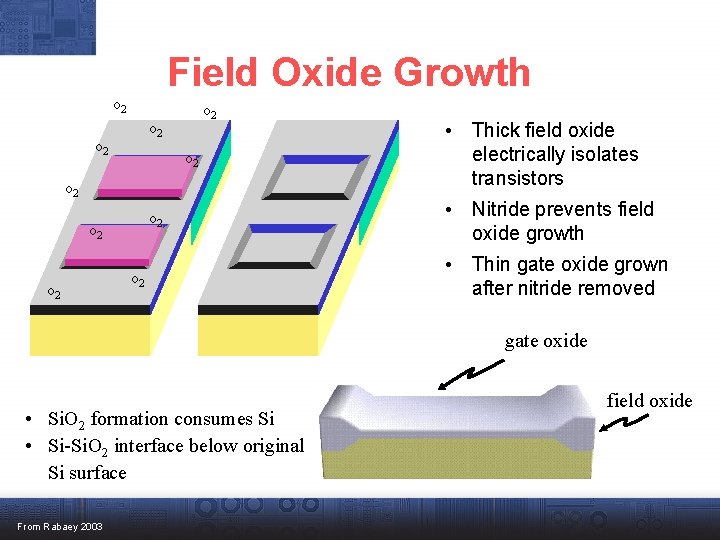

Field Oxide Growth o 2 o 2 o 2 • Thick field oxide electrically isolates transistors • Nitride prevents field oxide growth • Thin gate oxide grown after nitride removed gate oxide • Si. O 2 formation consumes Si • Si-Si. O 2 interface below original Si surface From Rabaey 2003 field oxide

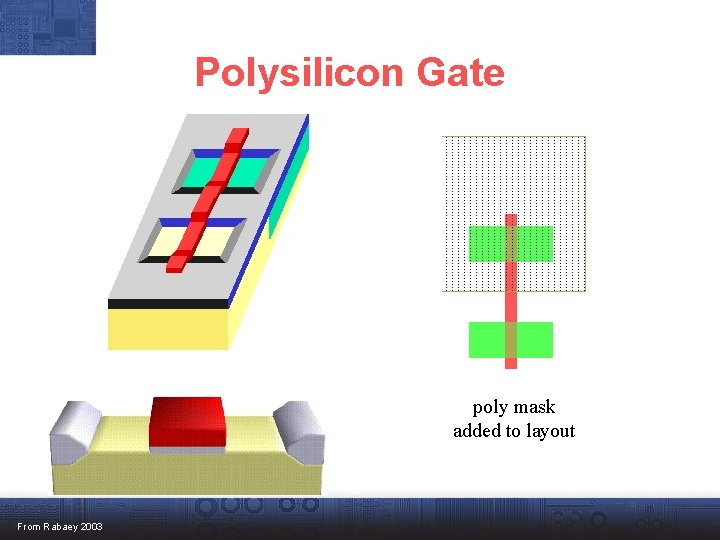

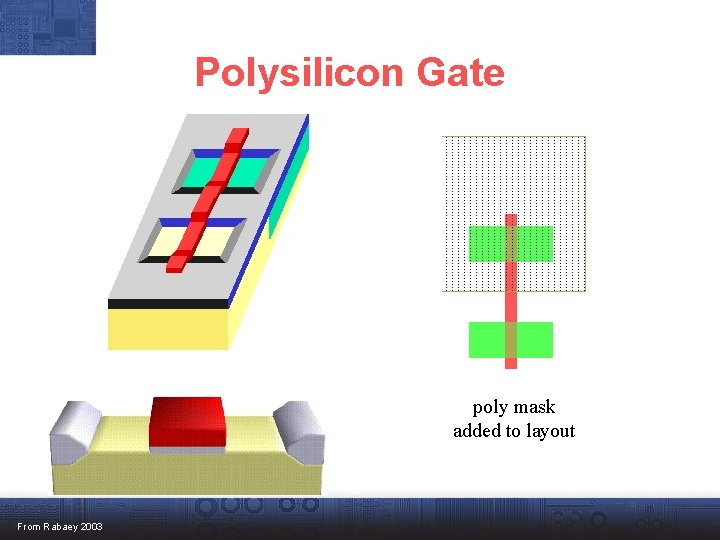

Polysilicon Gate poly mask added to layout From Rabaey 2003

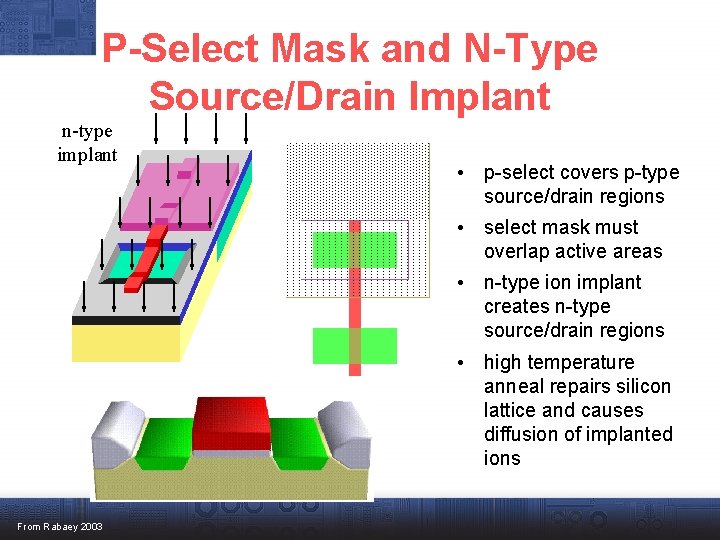

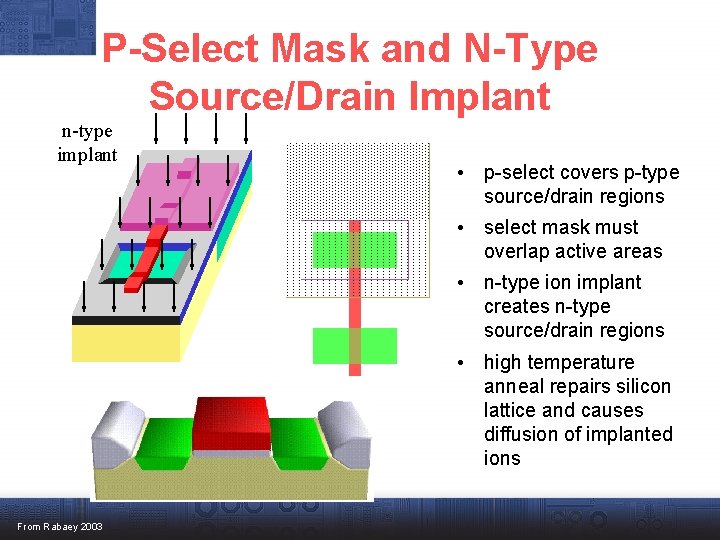

P-Select Mask and N-Type Source/Drain Implant n-type implant • p-select covers p-type source/drain regions • select mask must overlap active areas • n-type ion implant creates n-type source/drain regions • high temperature anneal repairs silicon lattice and causes diffusion of implanted ions From Rabaey 2003

N-Select Mask and P-Type Source/Drain Implant p-type implant From Rabaey 2003 finished mosfets both select masks added

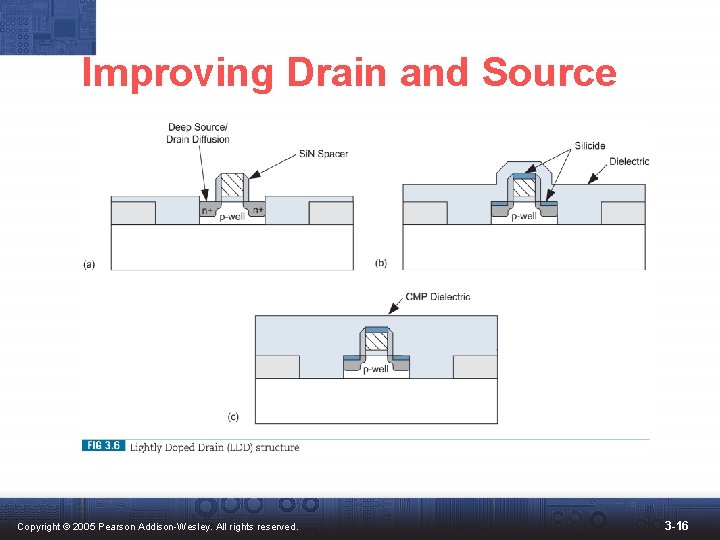

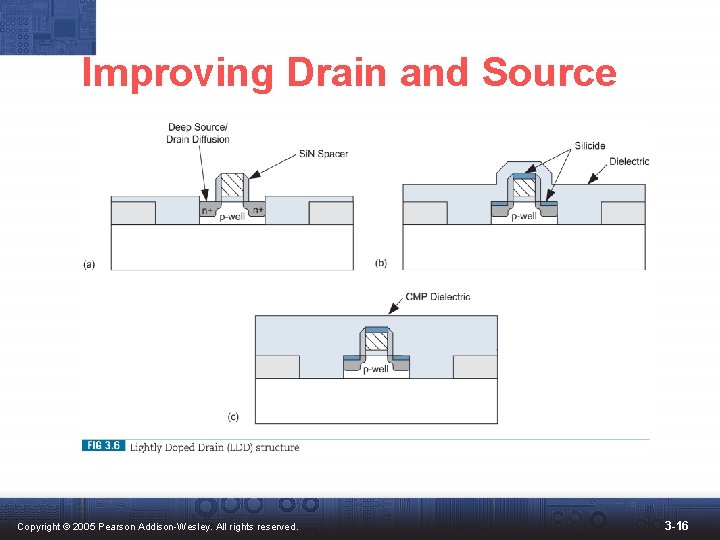

Improving Drain and Source Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -16

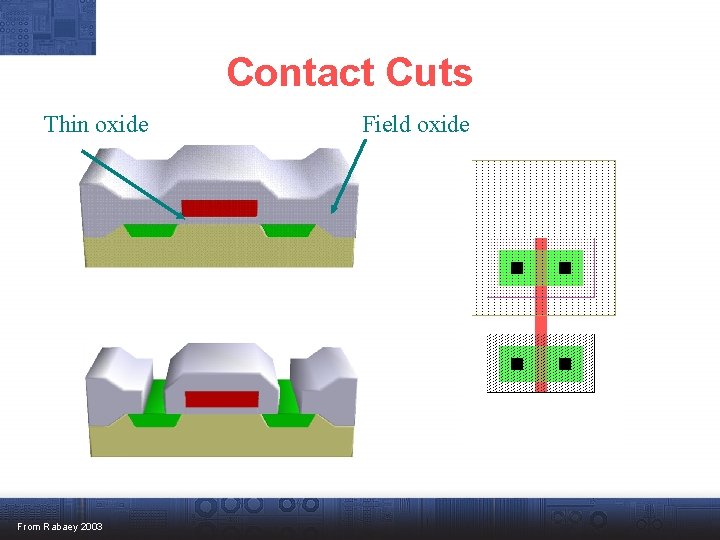

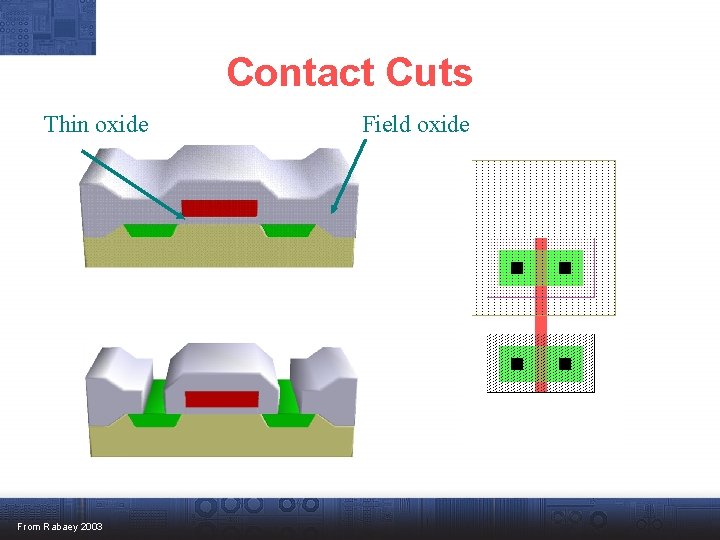

Contact Cuts Thin oxide From Rabaey 2003 Field oxide

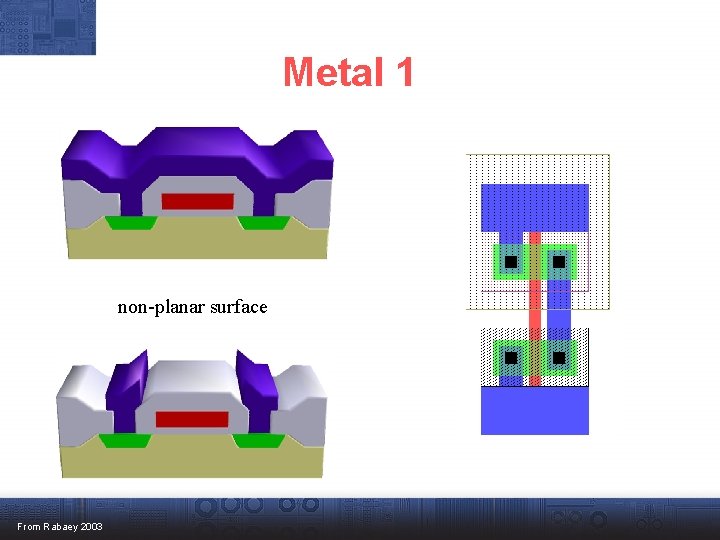

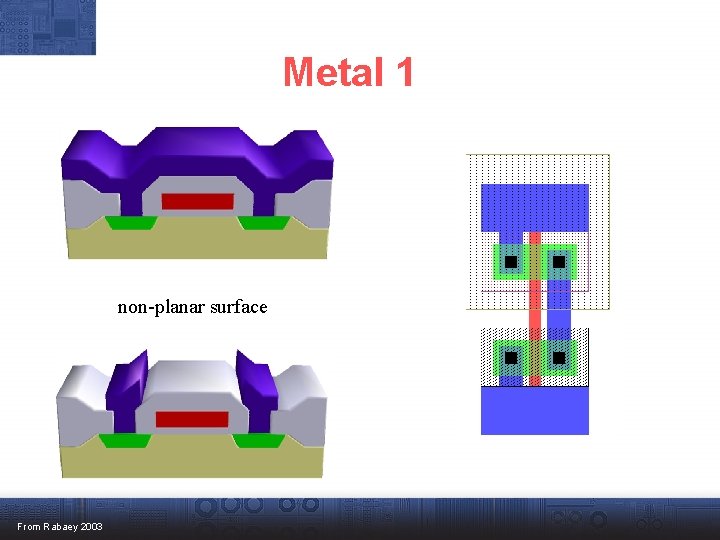

Metal 1 non-planar surface From Rabaey 2003

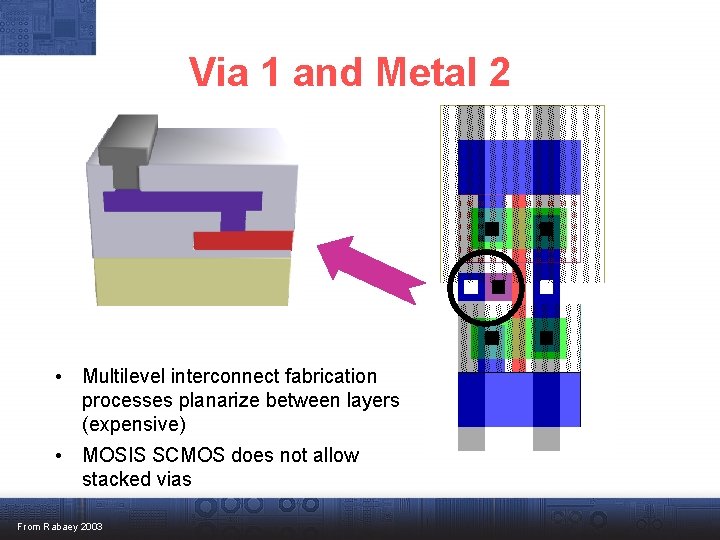

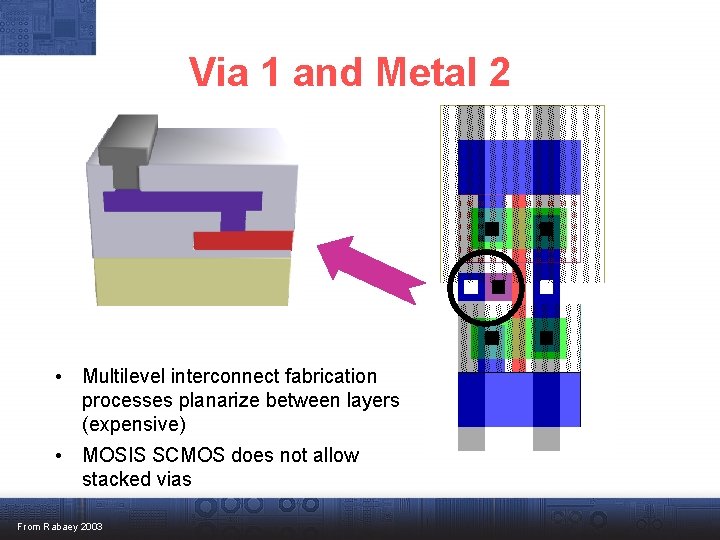

Via 1 and Metal 2 • Multilevel interconnect fabrication processes planarize between layers (expensive) • MOSIS SCMOS does not allow stacked vias From Rabaey 2003

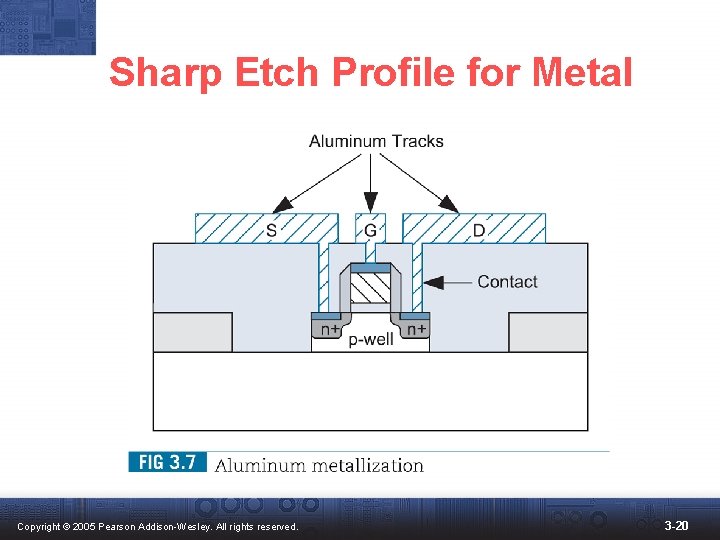

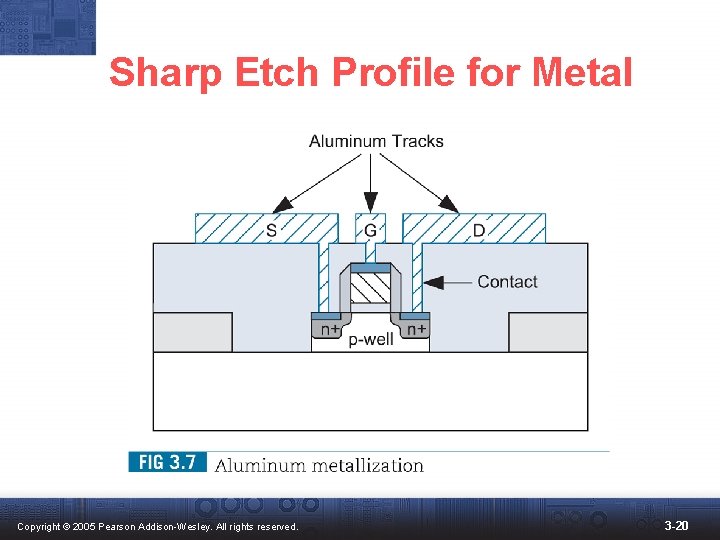

Sharp Etch Profile for Metal Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -20

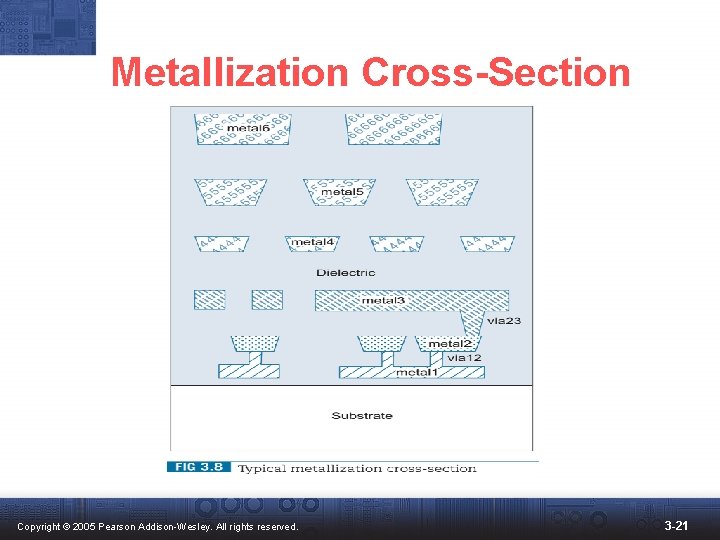

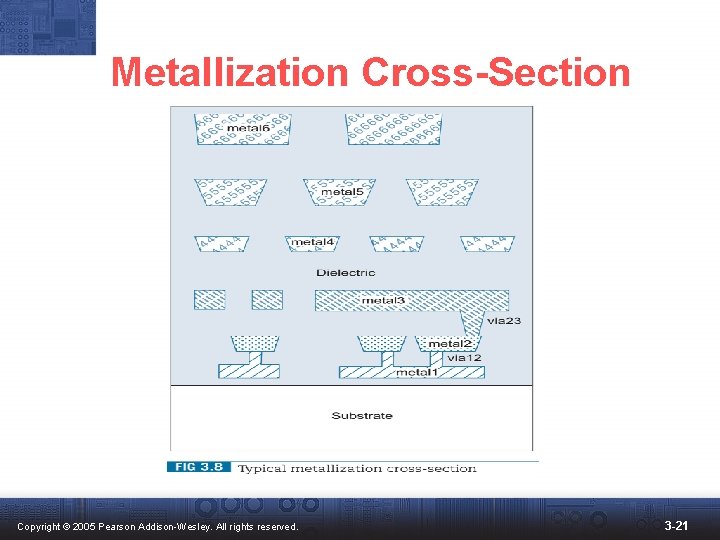

Metallization Cross-Section Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -21

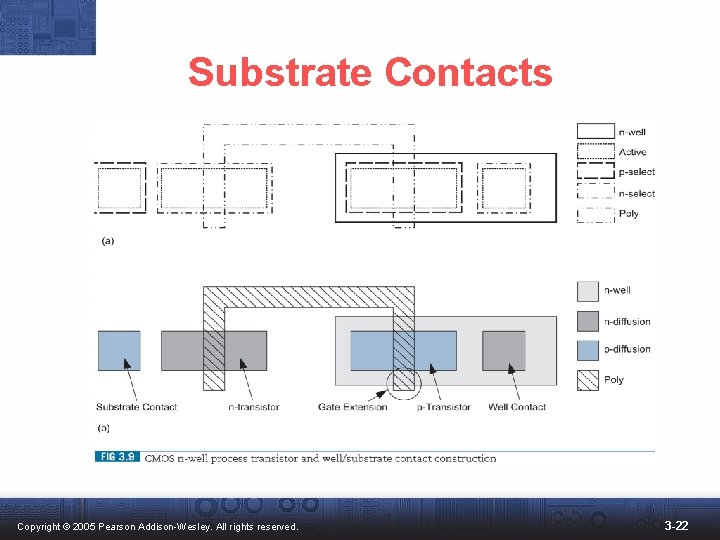

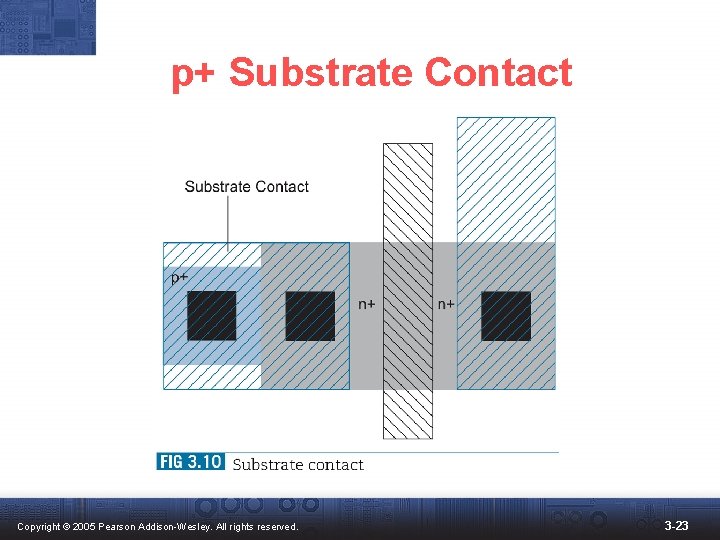

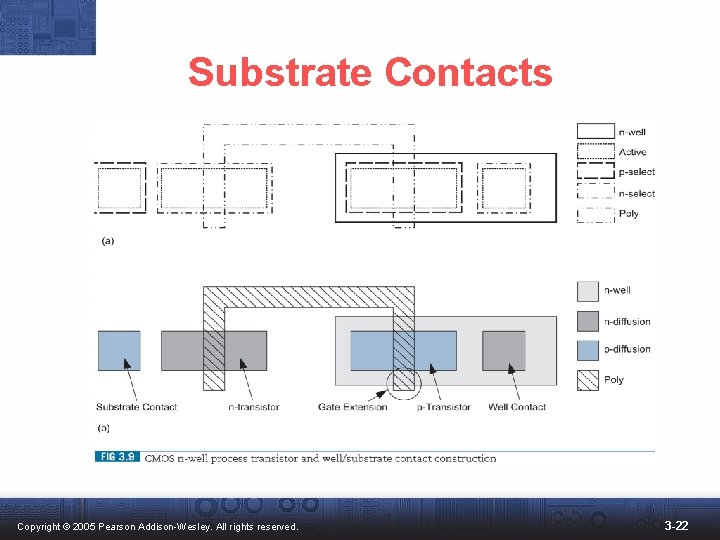

Substrate Contacts Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -22

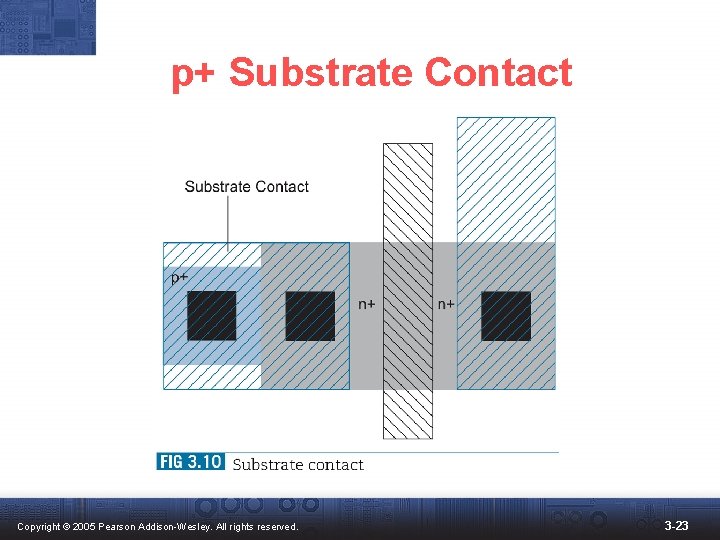

p+ Substrate Contact Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -23

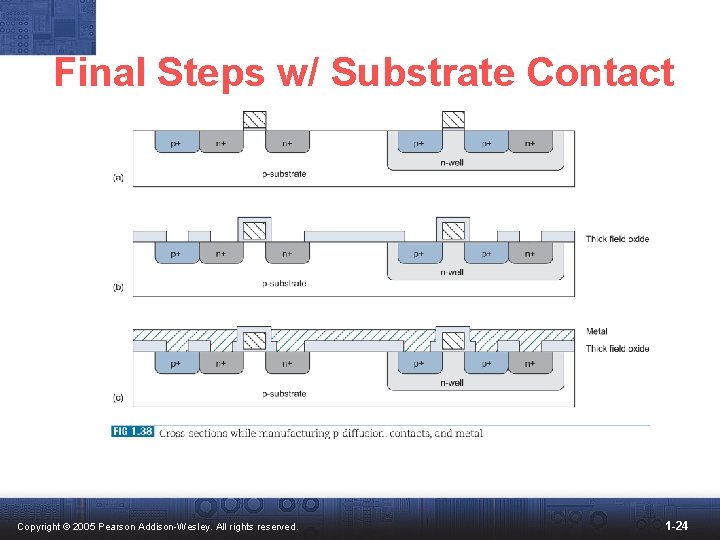

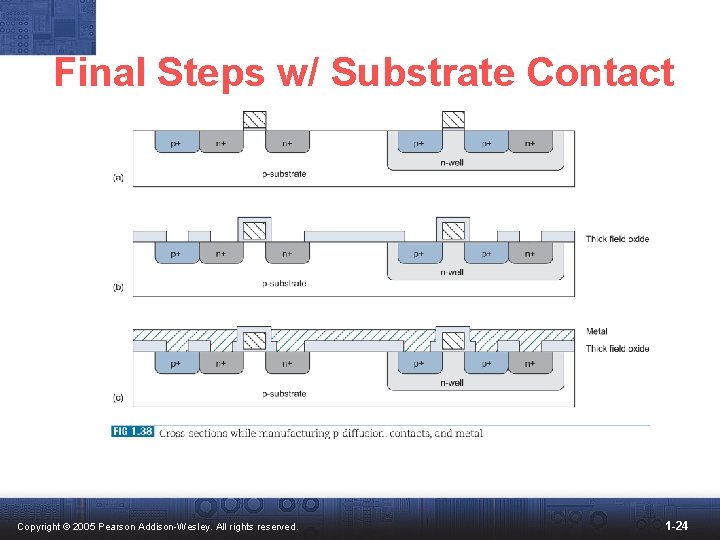

Final Steps w/ Substrate Contact Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -24

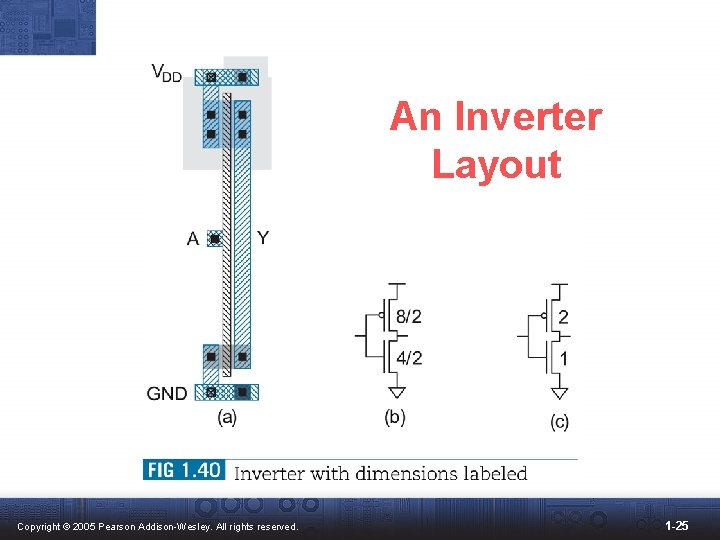

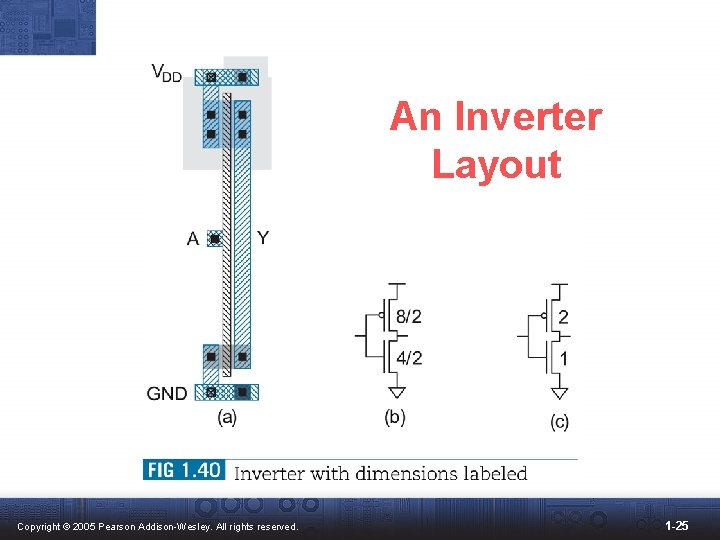

An Inverter Layout Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -25

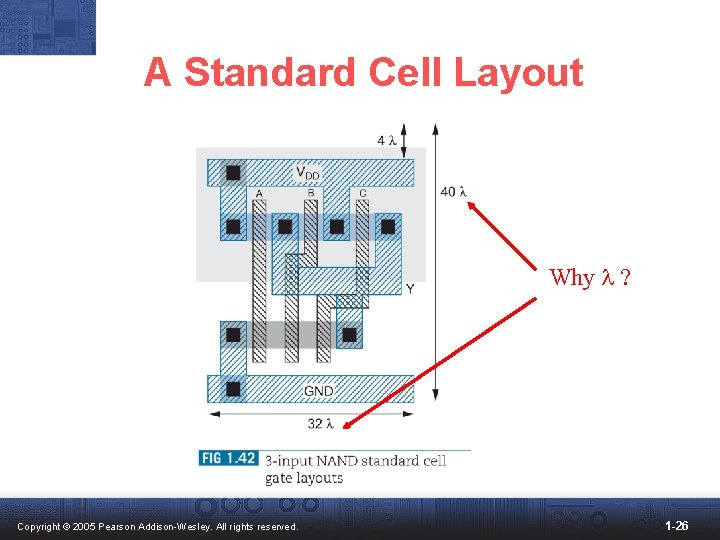

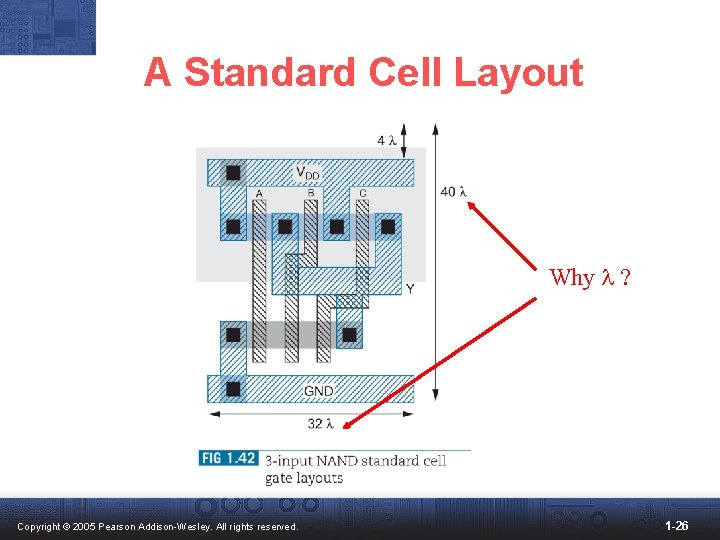

A Standard Cell Layout Why l ? Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -26

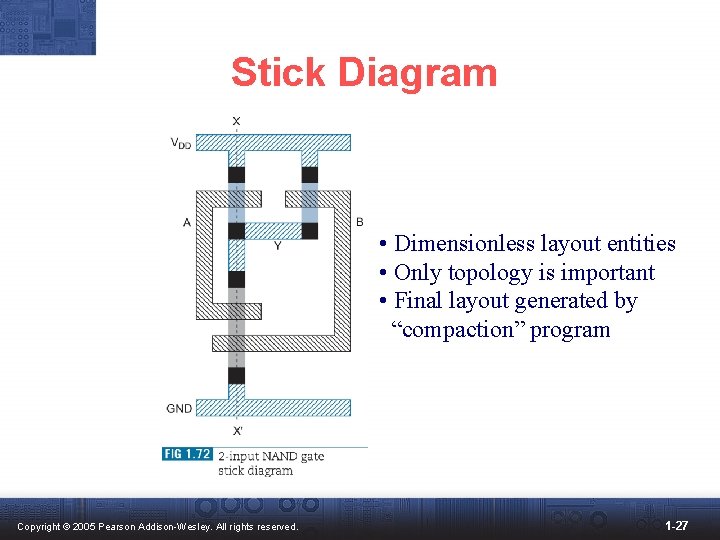

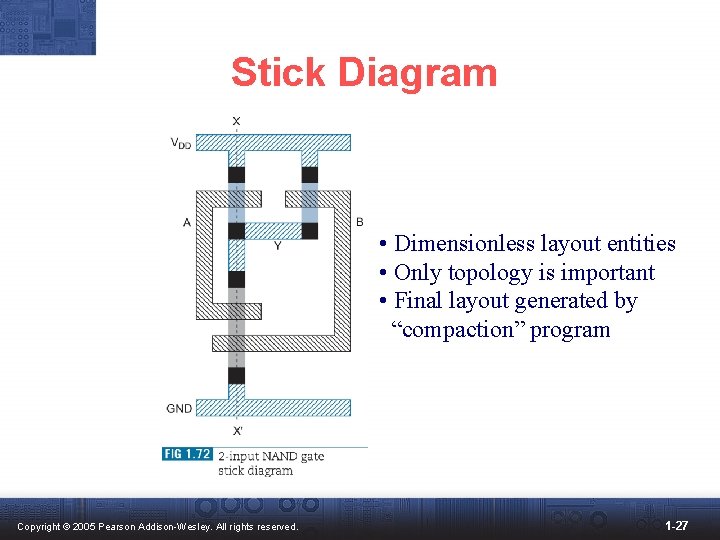

Stick Diagram • Dimensionless layout entities • Only topology is important • Final layout generated by “compaction” program Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -27

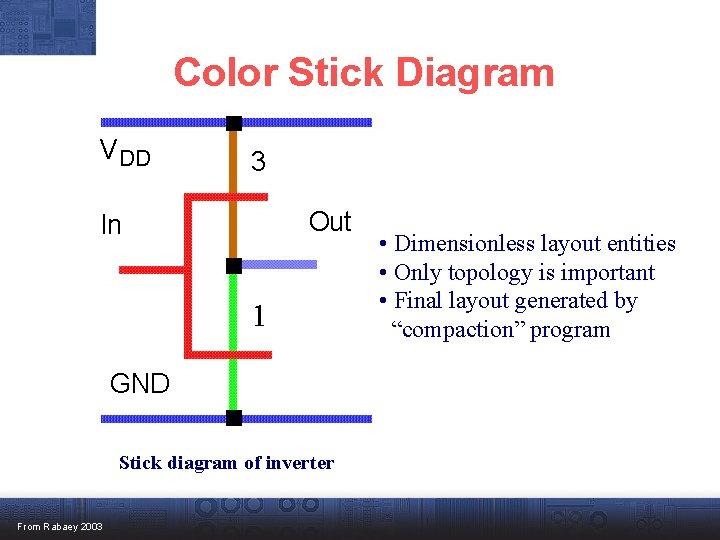

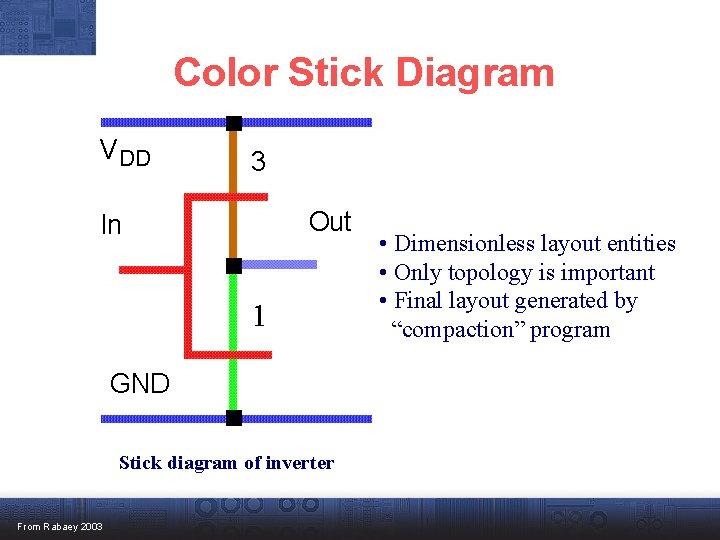

Color Stick Diagram V DD 3 Out In 1 GND Stick diagram of inverter From Rabaey 2003 • Dimensionless layout entities • Only topology is important • Final layout generated by “compaction” program

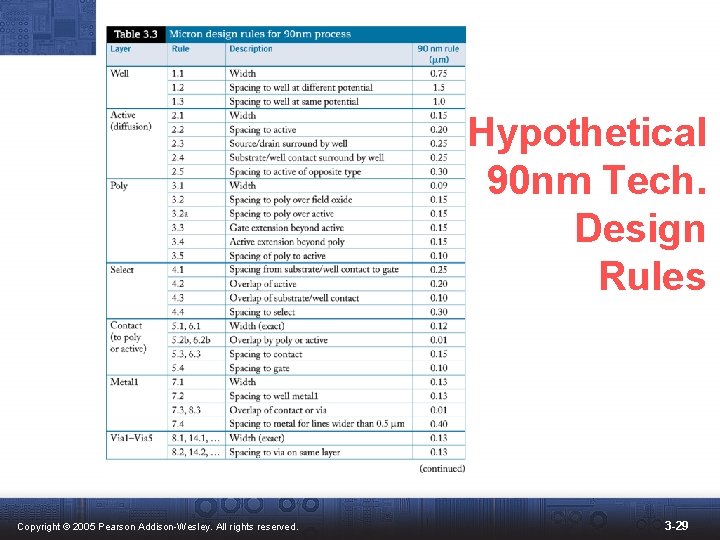

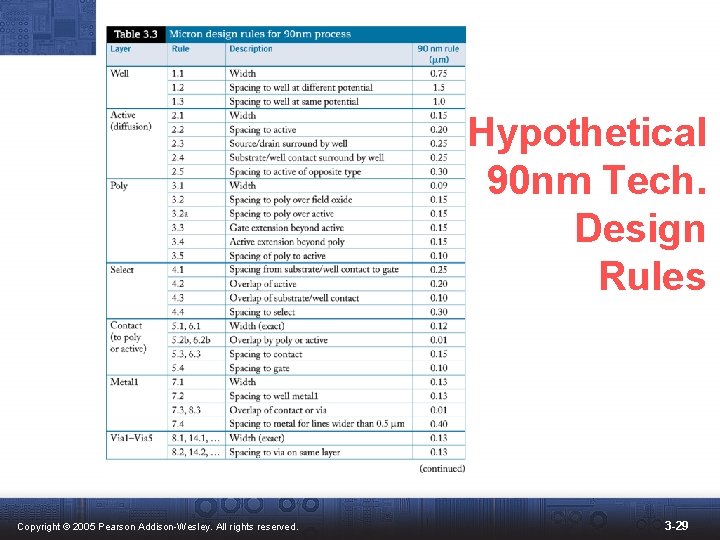

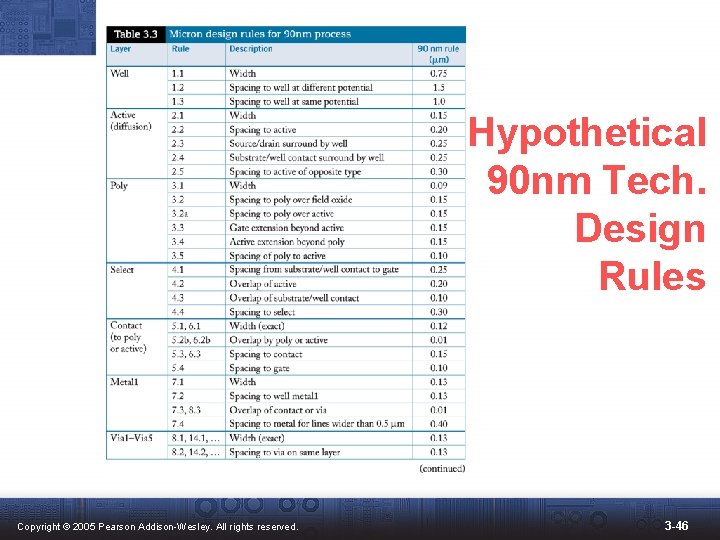

Hypothetical 90 nm Tech. Design Rules Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -29

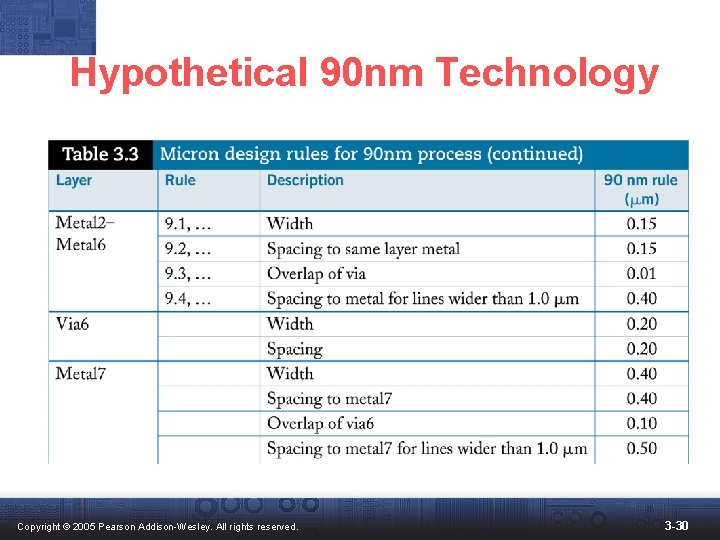

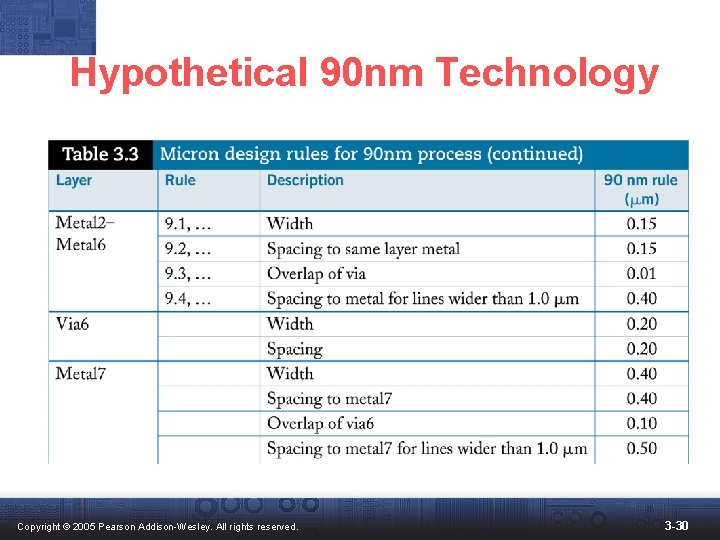

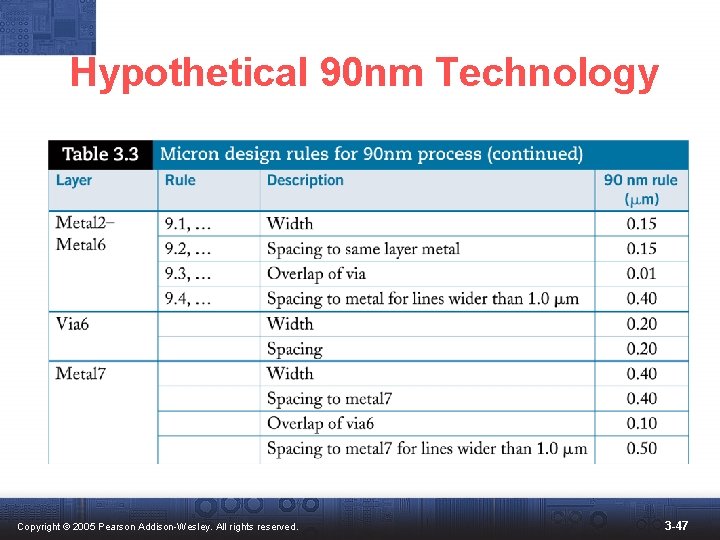

Hypothetical 90 nm Technology Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -30

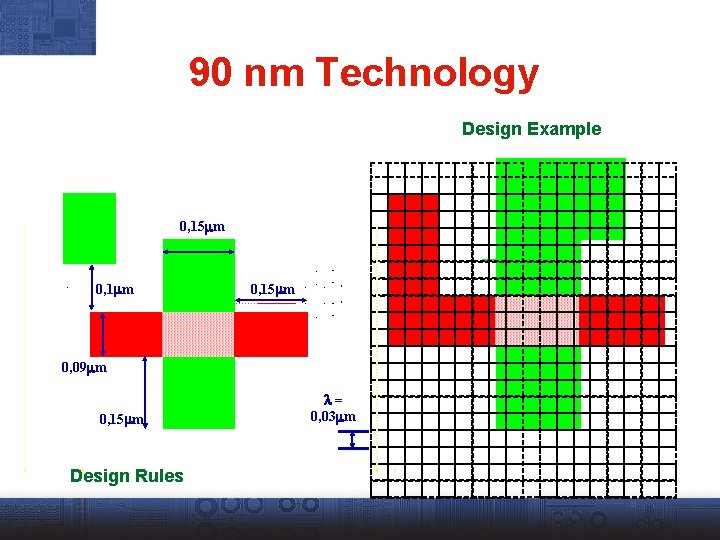

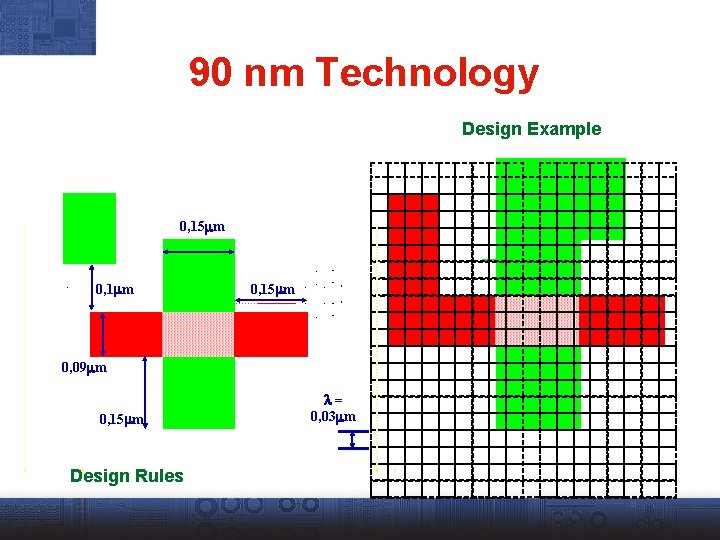

90 nm Technology Design Example 0, 15 mm 0, 09 mm 0, 15 mm Design Rules l= 0, 03 mm

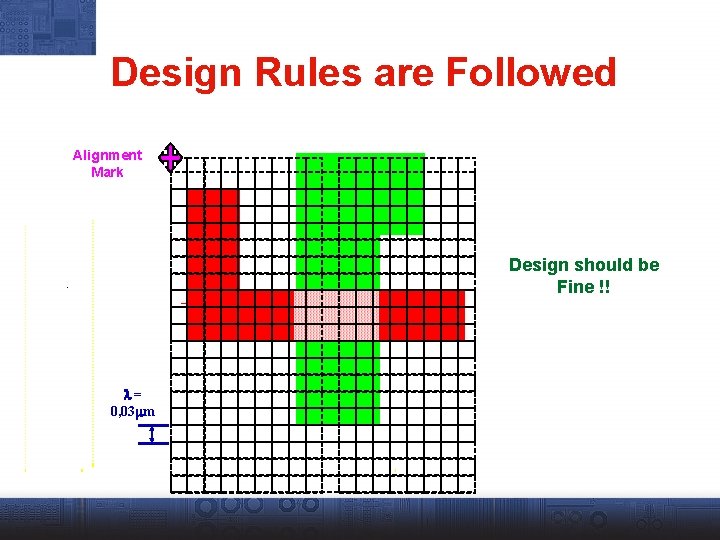

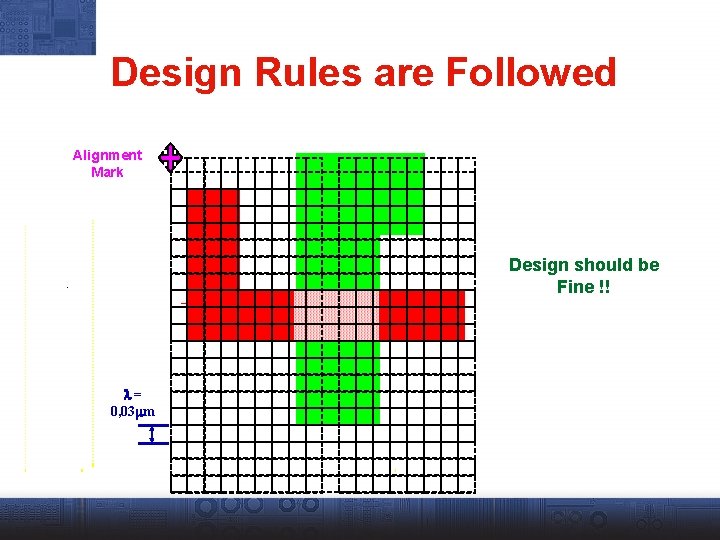

Design Rules are Followed Alignment Mark Design should be Fine !! l= 0, 03 mm

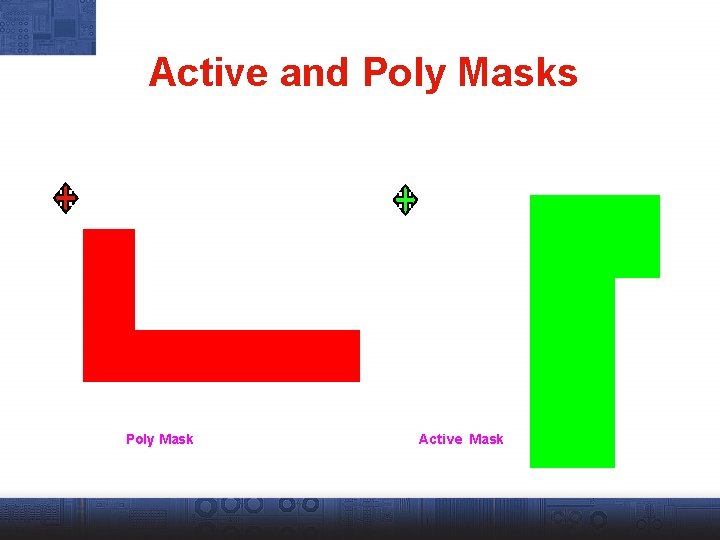

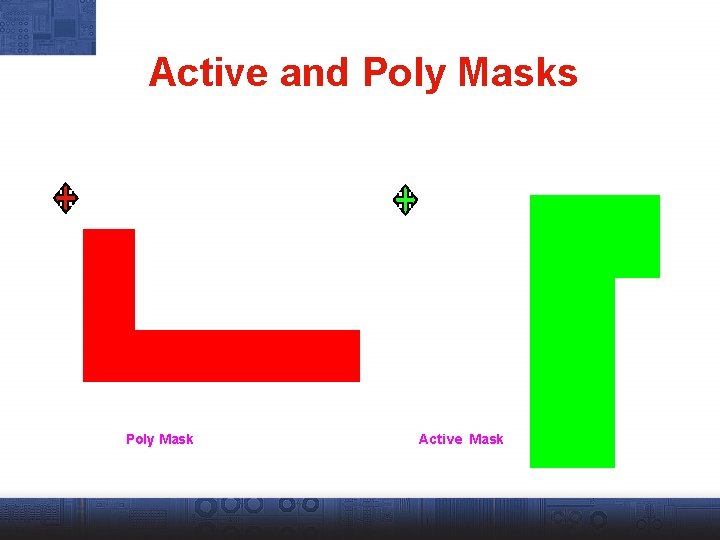

Active and Poly Masks Poly Mask Active Mask

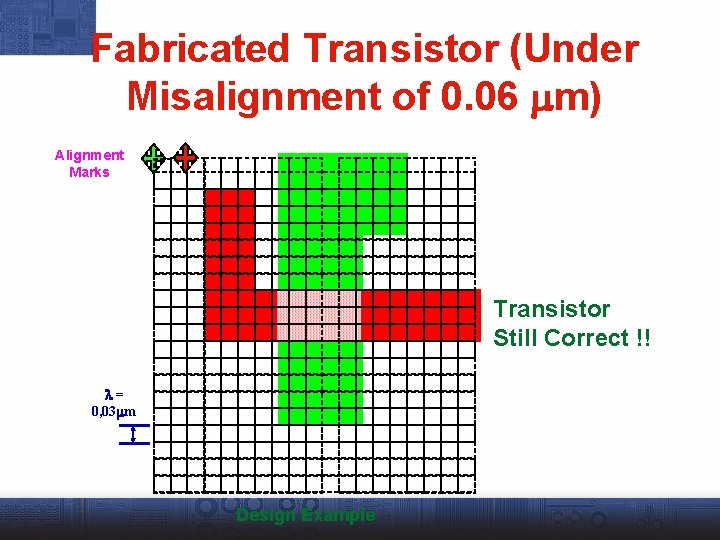

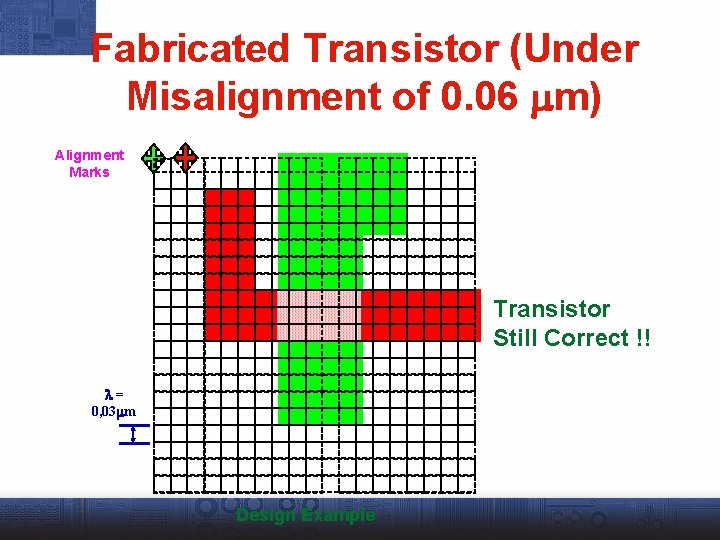

Fabricated Transistor (Under Misalignment of 0. 06 mm) Alignment Marks Transistor Still Correct !! l= 0, 03 mm Design Example

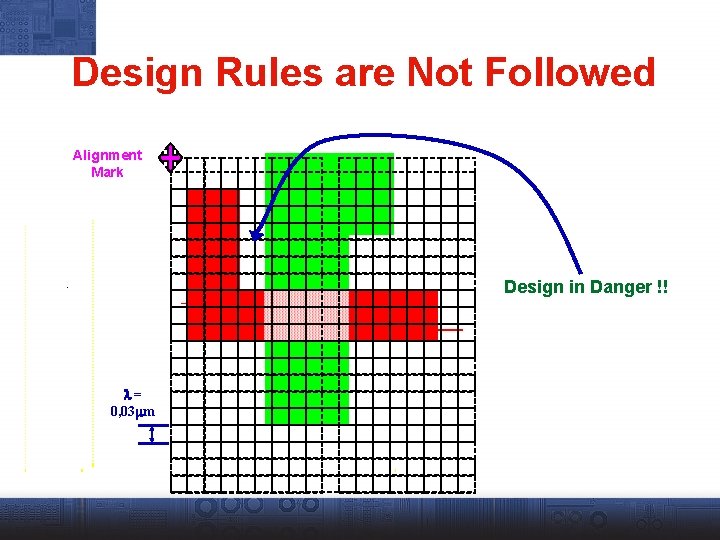

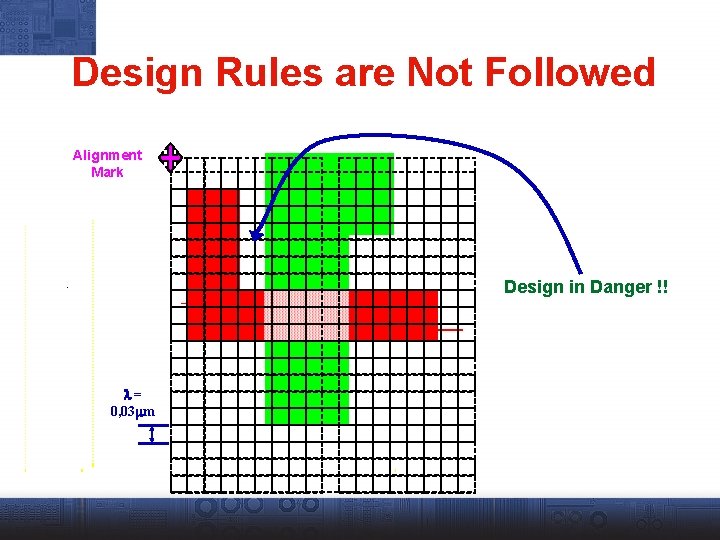

Design Rules are Not Followed Alignment Mark Design in Danger !! l= 0, 03 mm

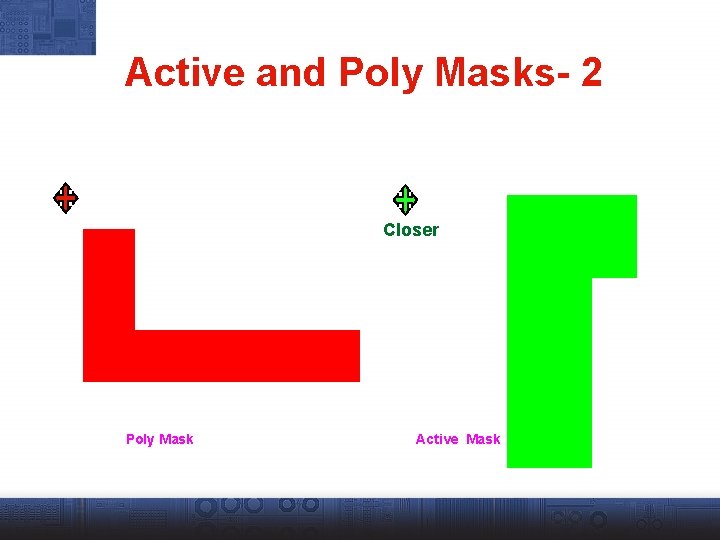

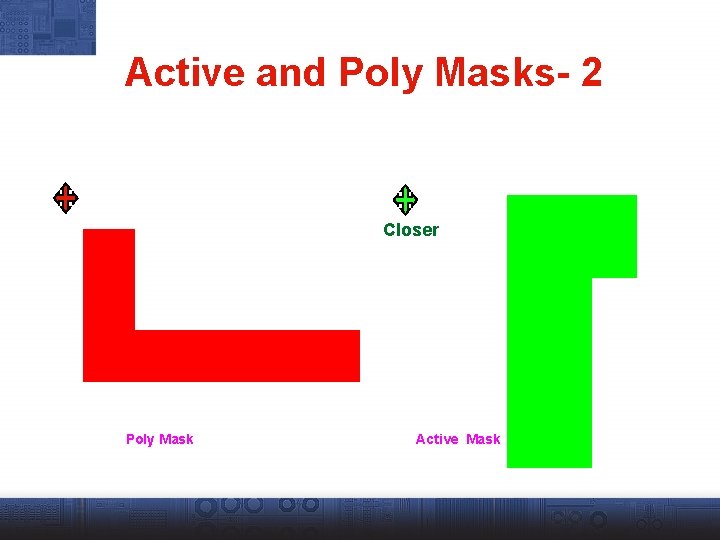

Active and Poly Masks- 2 Closer Poly Mask Active Mask

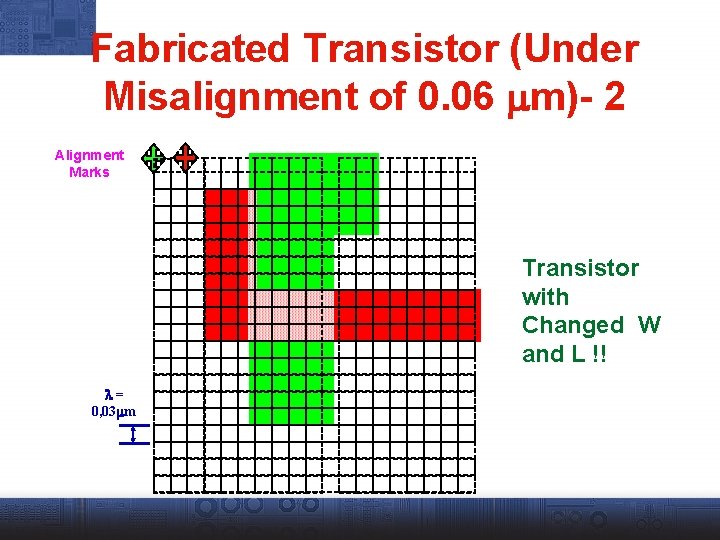

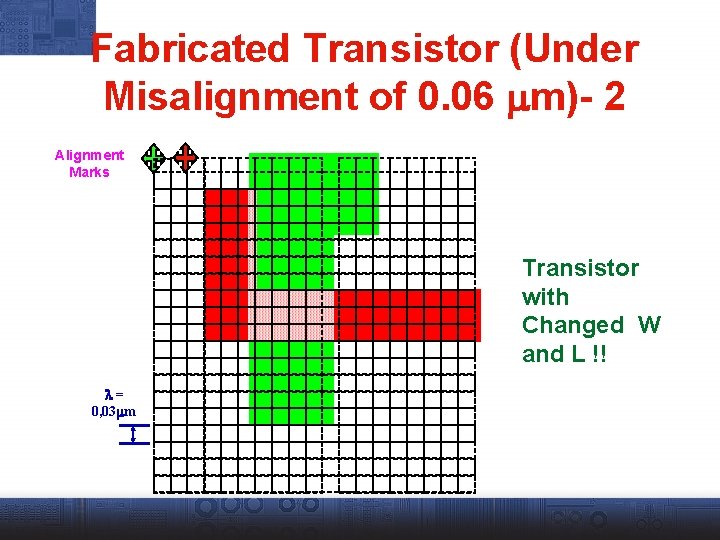

Fabricated Transistor (Under Misalignment of 0. 06 mm)- 2 Alignment Marks Transistor with Changed W and L !! l= 0, 03 mm

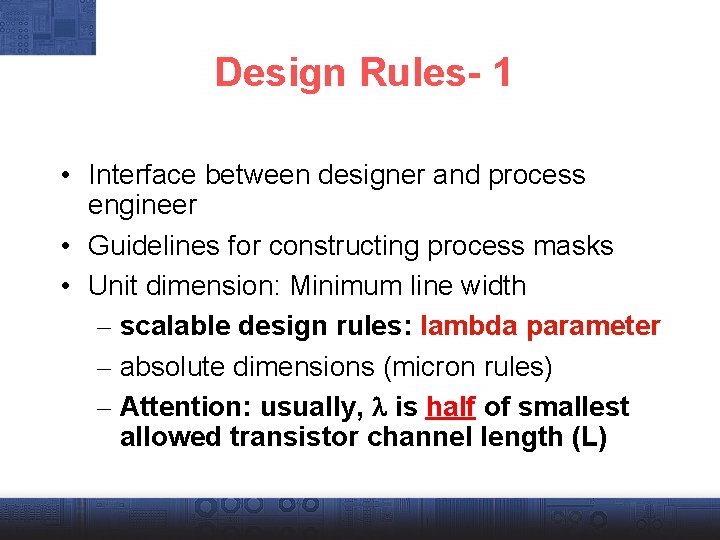

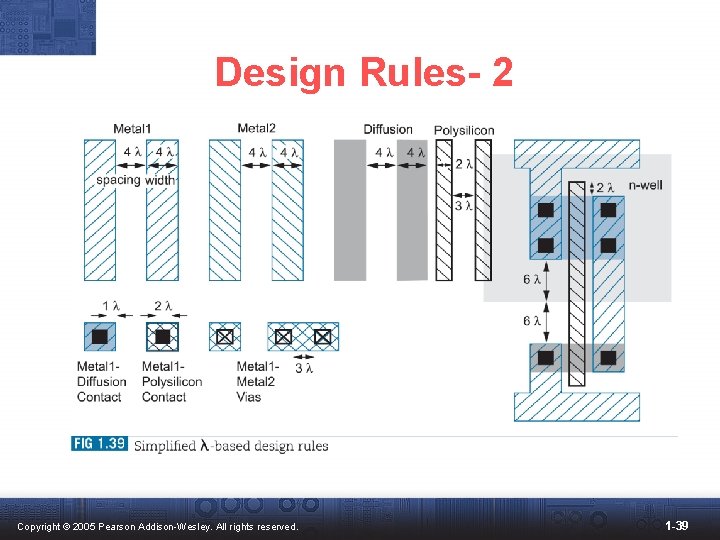

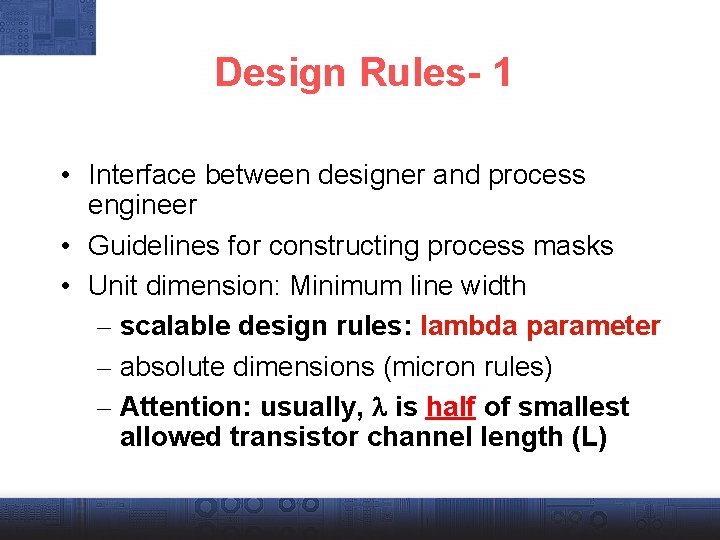

Design Rules- 1 • Interface between designer and process engineer • Guidelines for constructing process masks • Unit dimension: Minimum line width – scalable design rules: lambda parameter – absolute dimensions (micron rules) – Attention: usually, l is half of smallest allowed transistor channel length (L)

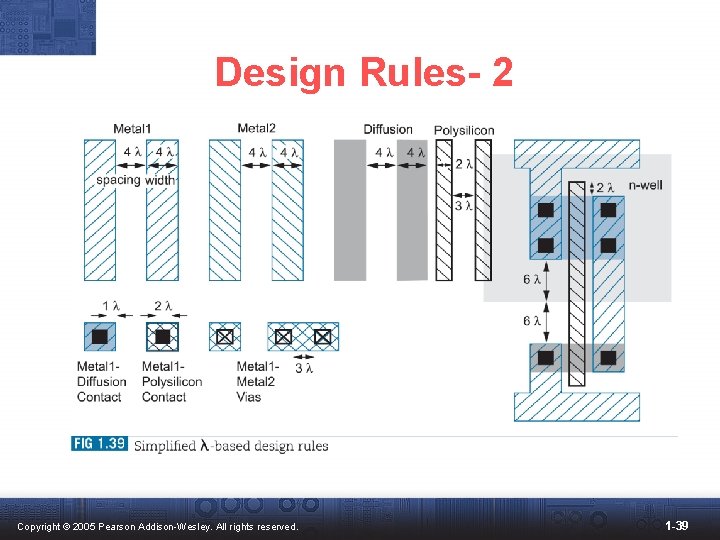

Design Rules- 2 Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -39

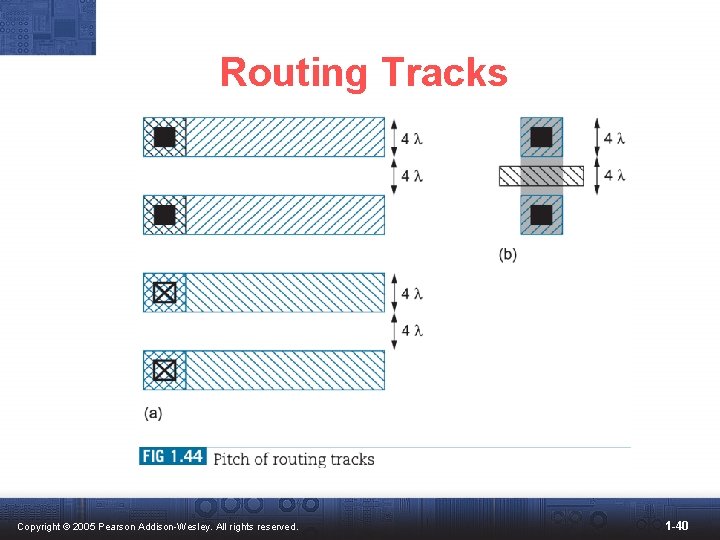

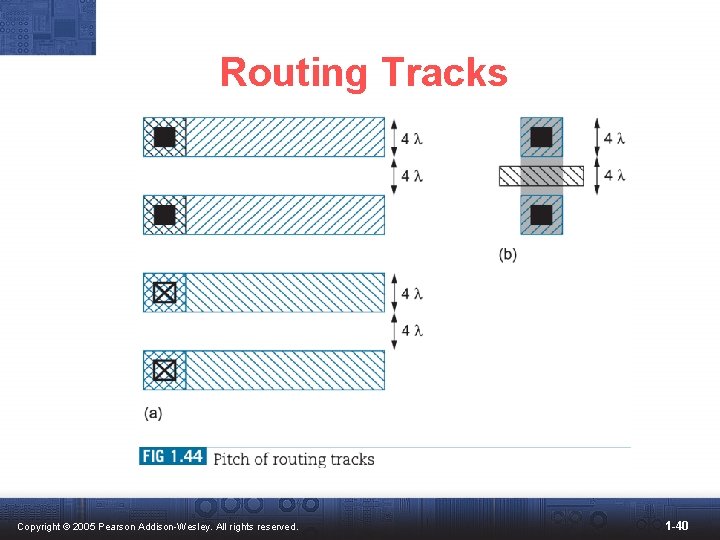

Routing Tracks Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -40

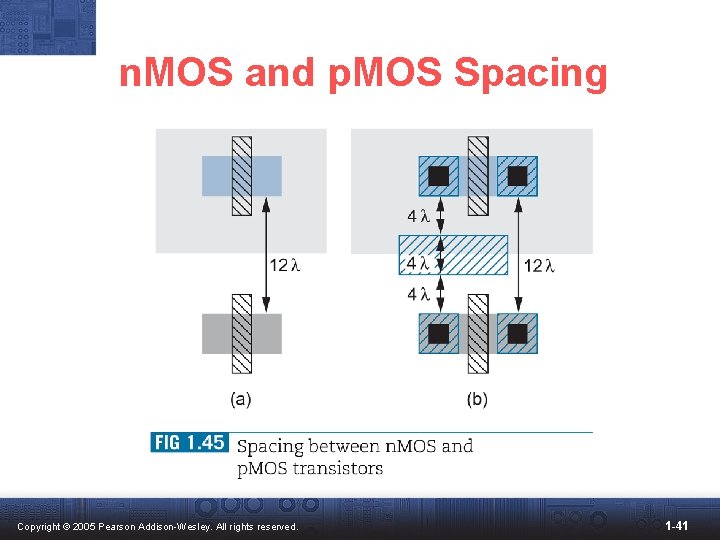

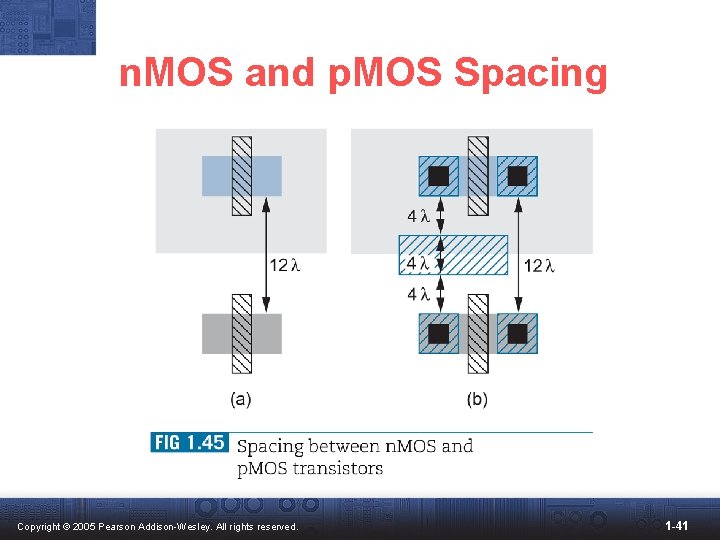

n. MOS and p. MOS Spacing Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 1 -41

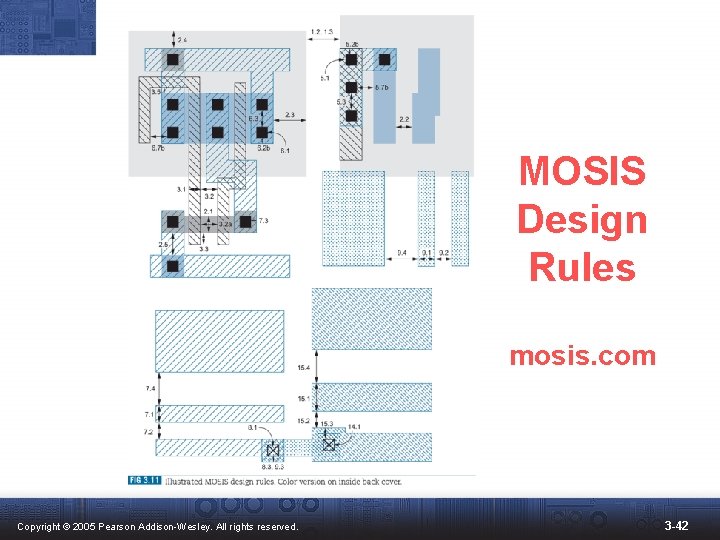

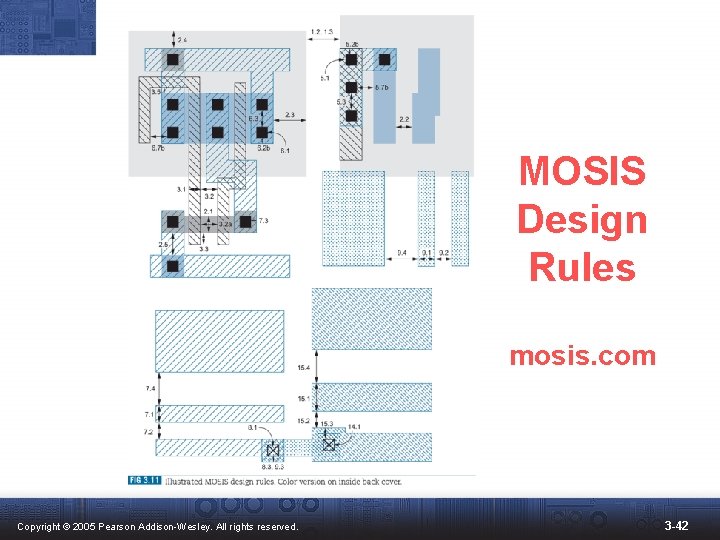

MOSIS Design Rules mosis. com Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -42

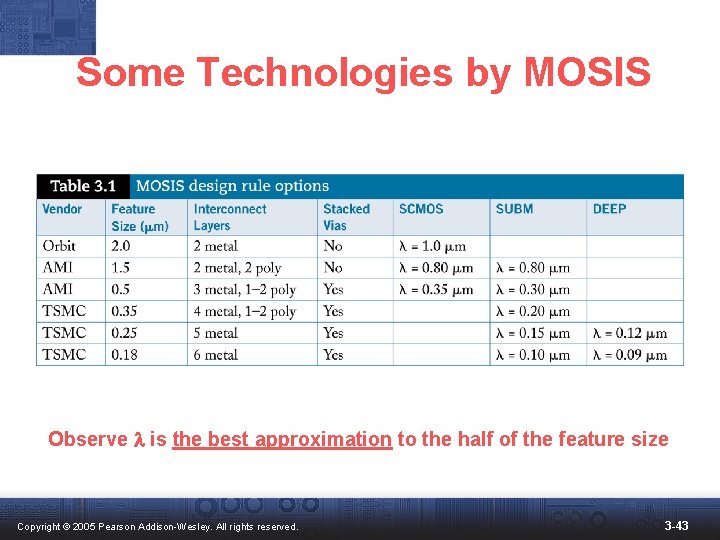

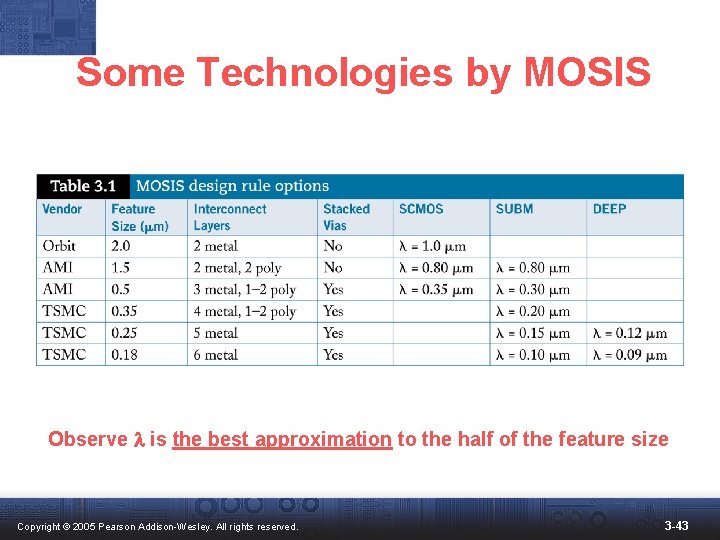

Some Technologies by MOSIS Observe l is the best approximation to the half of the feature size Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -43

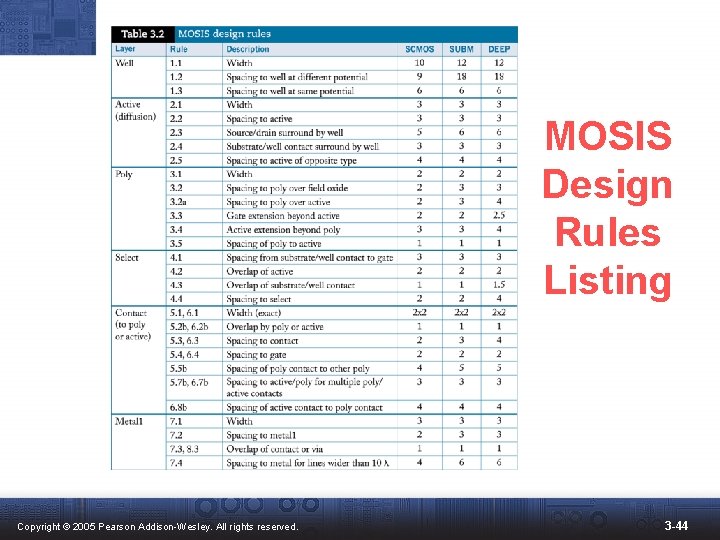

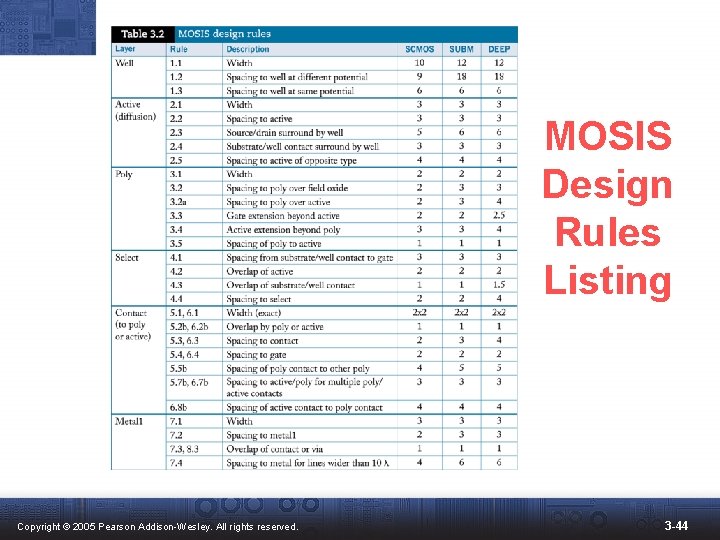

MOSIS Design Rules Listing Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -44

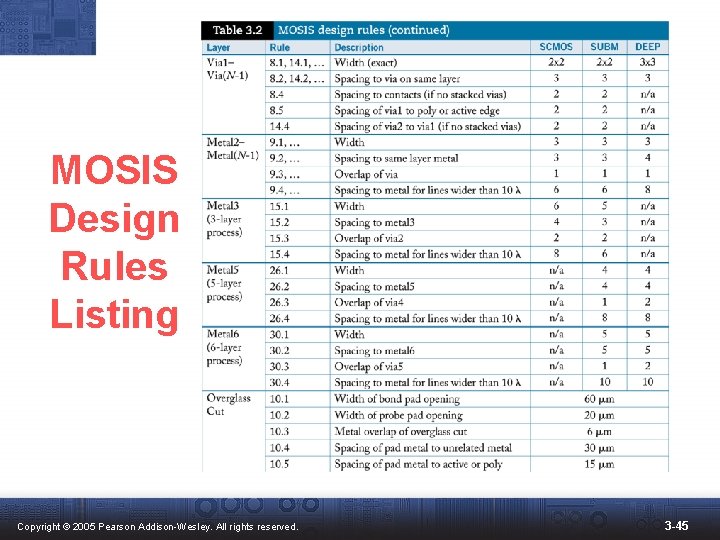

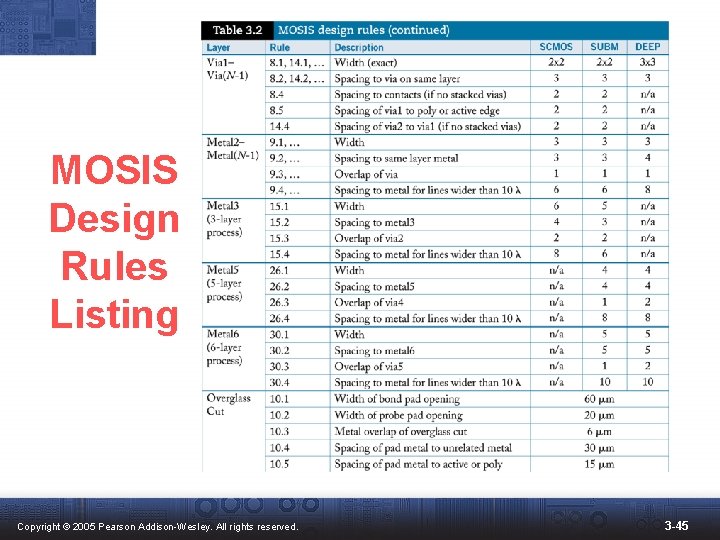

MOSIS Design Rules Listing Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -45

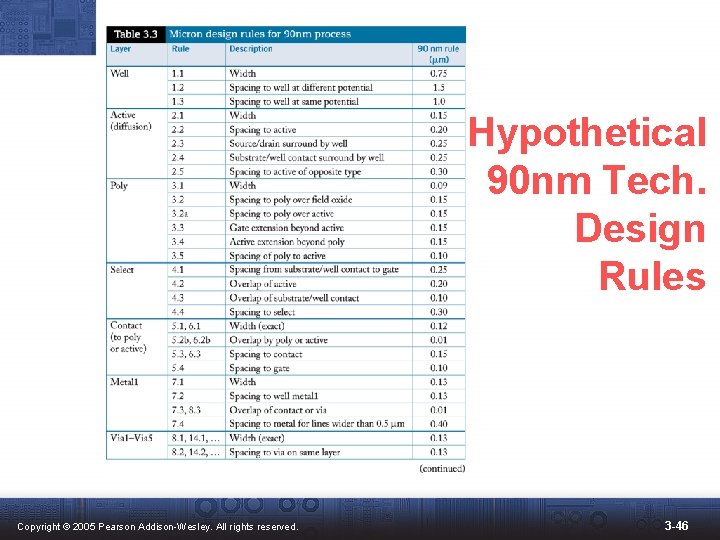

Hypothetical 90 nm Tech. Design Rules Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -46

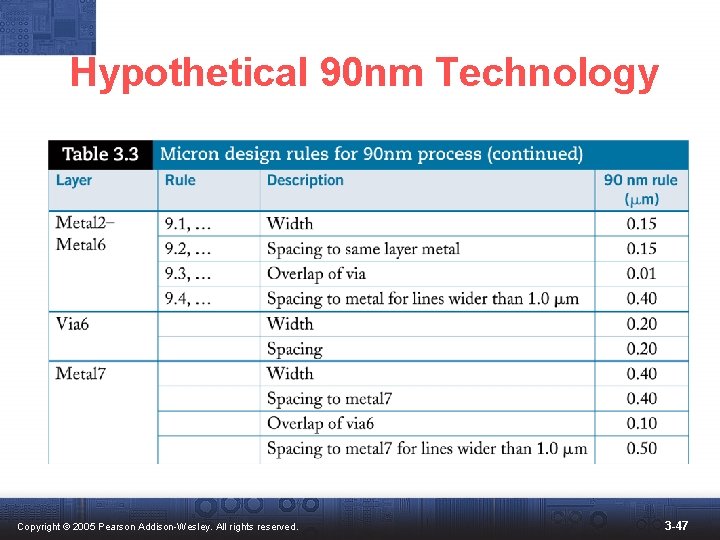

Hypothetical 90 nm Technology Copyright © 2005 Pearson Addison-Wesley. All rights reserved. 3 -47