Chapitre 4 Les circuits combinatoires 1 1 Les

Chapitre 4 Les circuits combinatoires 1

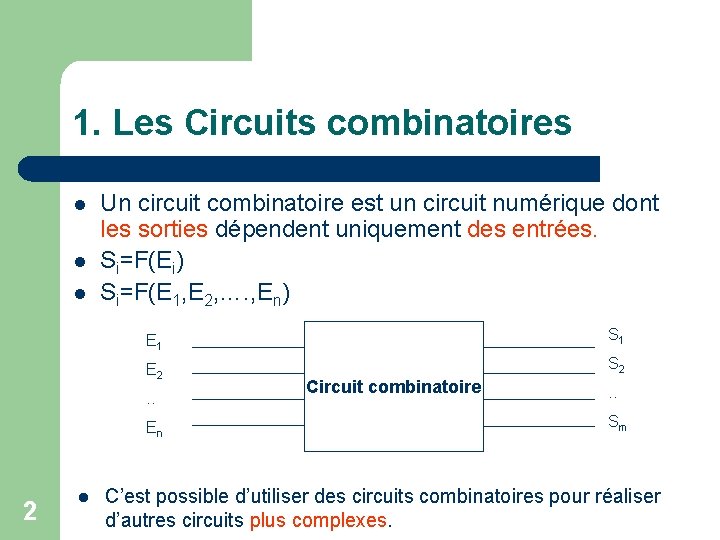

1. Les Circuits combinatoires l l l Un circuit combinatoire est un circuit numérique dont les sorties dépendent uniquement des entrées. Si=F(Ei) Si=F(E 1, E 2, …. , En) E 1 S 1 E 2 S 2 . . En 2 l Circuit combinatoire . . Sm C’est possible d’utiliser des circuits combinatoires pour réaliser d’autres circuits plus complexes.

1. 1 Exemple de Circuits combinatoires l l l l 3 Demi Additionneur complet Comparateur Multiplexeur Demultiplexeur Encodeur Décodeur

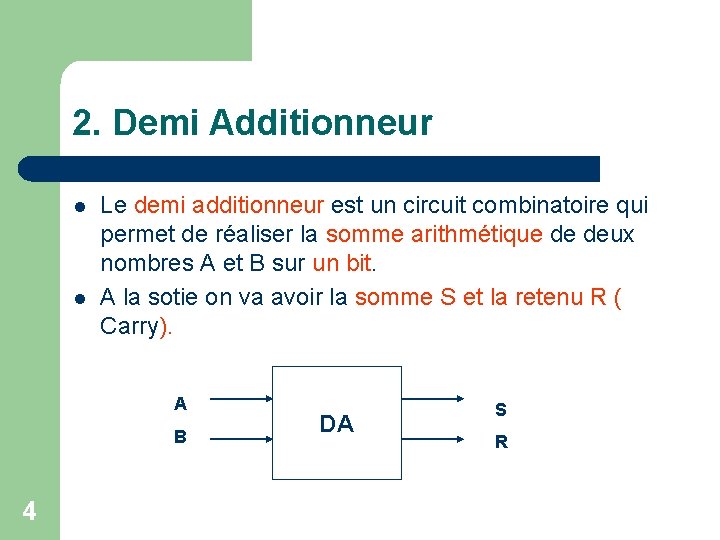

2. Demi Additionneur l l Le demi additionneur est un circuit combinatoire qui permet de réaliser la somme arithmétique de deux nombres A et B sur un bit. A la sotie on va avoir la somme S et la retenu R ( Carry). A B 4 DA S R

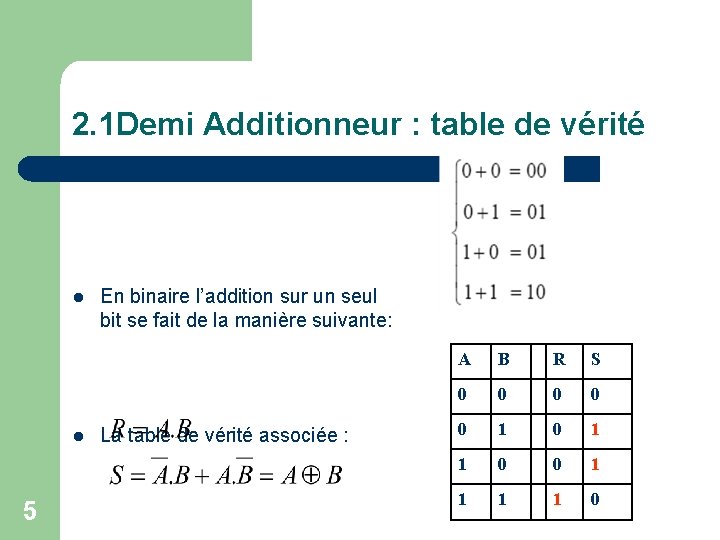

2. 1 Demi Additionneur : table de vérité l l 5 En binaire l’addition sur un seul bit se fait de la manière suivante: La table de vérité associée : A B R S 0 0 0 1 1 0

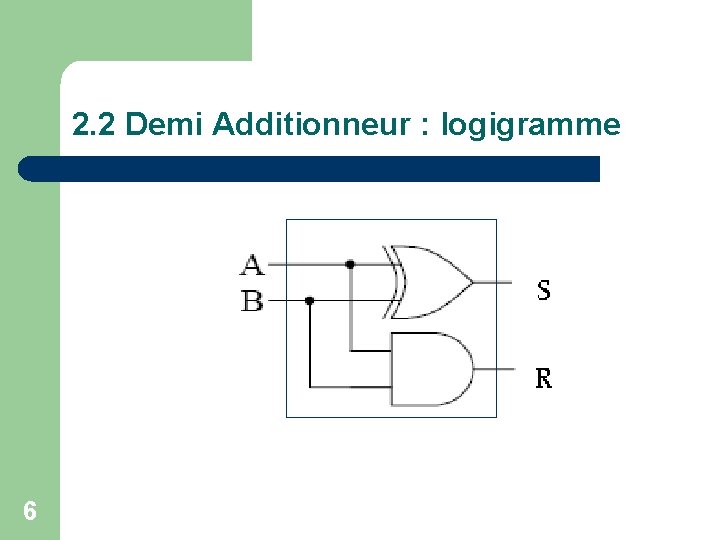

2. 2 Demi Additionneur : logigramme 6

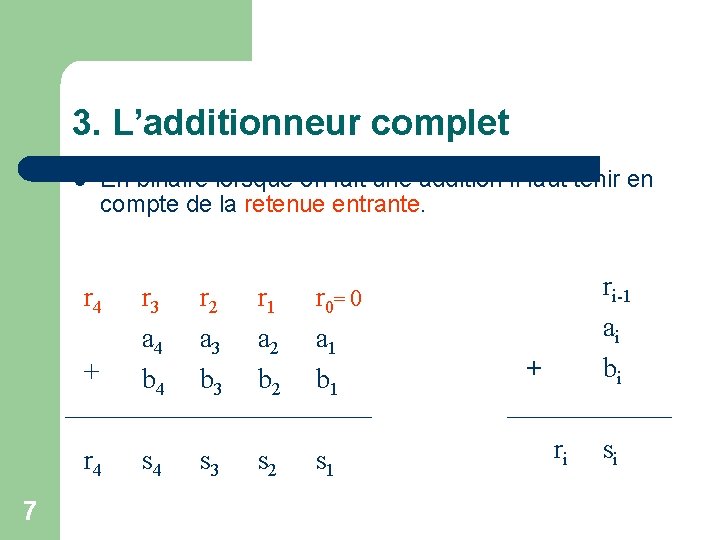

3. L’additionneur complet l En binaire lorsque on fait une addition il faut tenir en compte de la retenue entrante. r 4 7 + r 3 a 4 b 4 r 2 a 3 b 3 r 1 a 2 b 2 r 0= 0 a 1 b 1 r 4 s 3 s 2 s 1 ri-1 ai bi + ri si

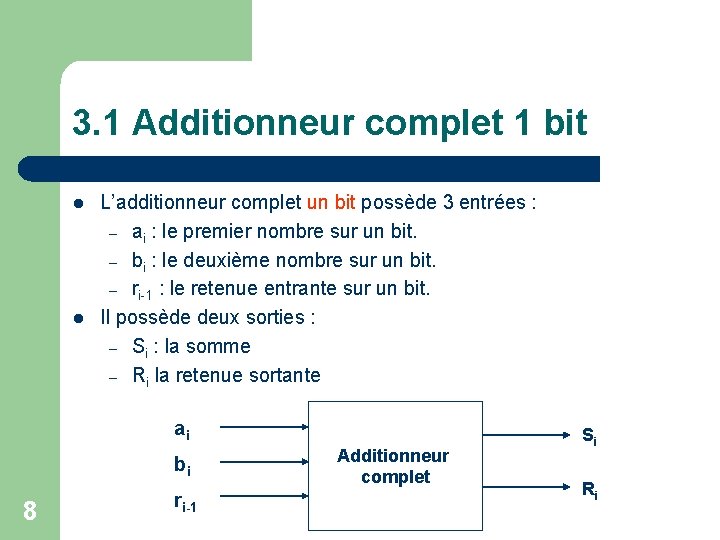

3. 1 Additionneur complet 1 bit l l L’additionneur complet un bit possède 3 entrées : – ai : le premier nombre sur un bit. – bi : le deuxième nombre sur un bit. – ri-1 : le retenue entrante sur un bit. Il possède deux sorties : – Si : la somme – Ri la retenue sortante ai bi 8 ri-1 Additionneur complet Si Ri

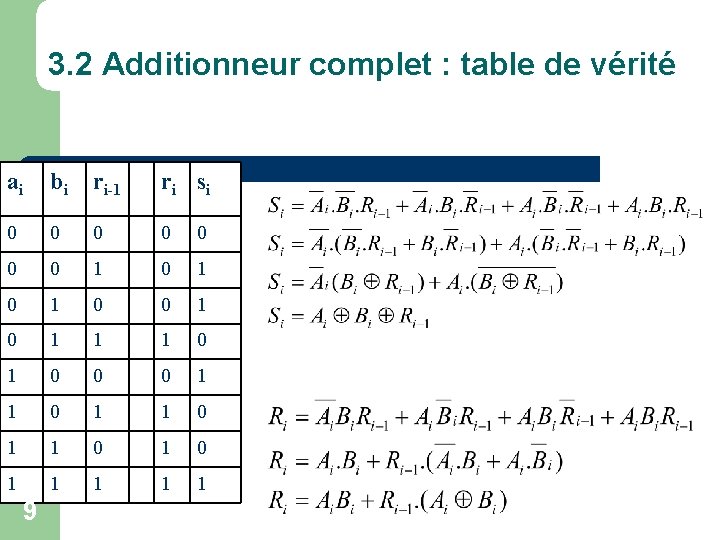

3. 2 Additionneur complet : table de vérité ai bi ri-1 r i si 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 9

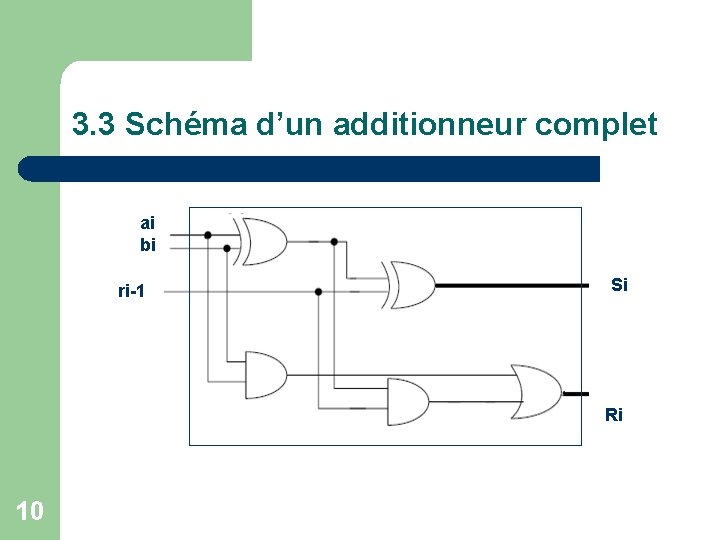

3. 3 Schéma d’un additionneur complet ai bi ri-1 Si Ri 10

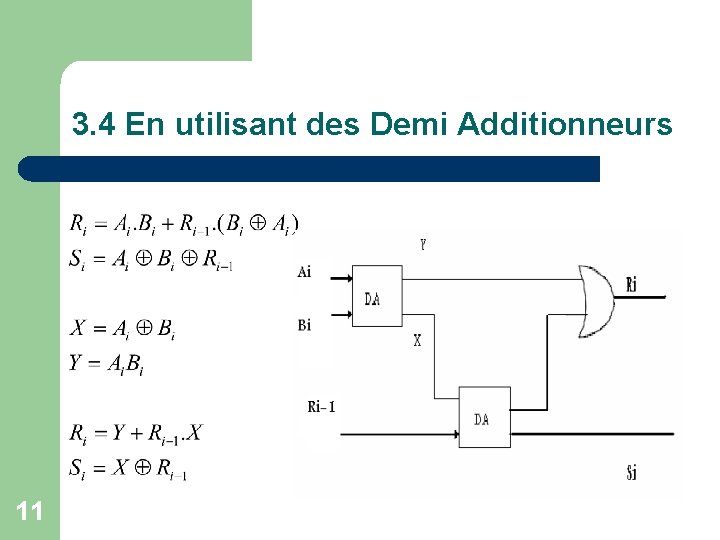

3. 4 En utilisant des Demi Additionneurs 11

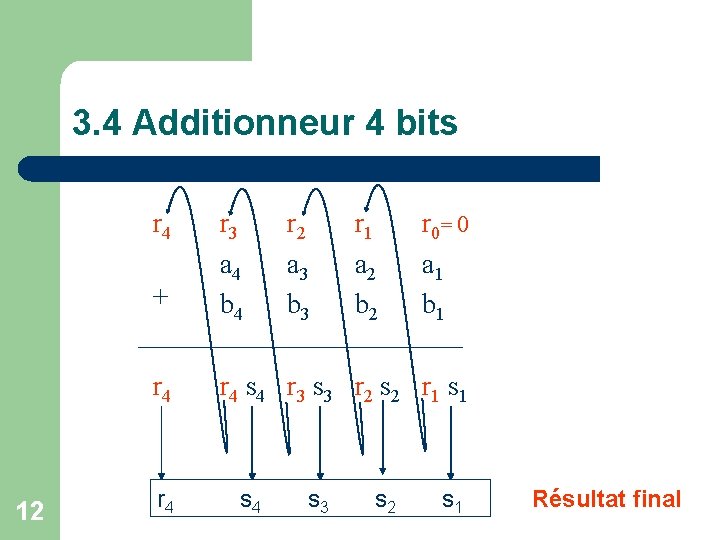

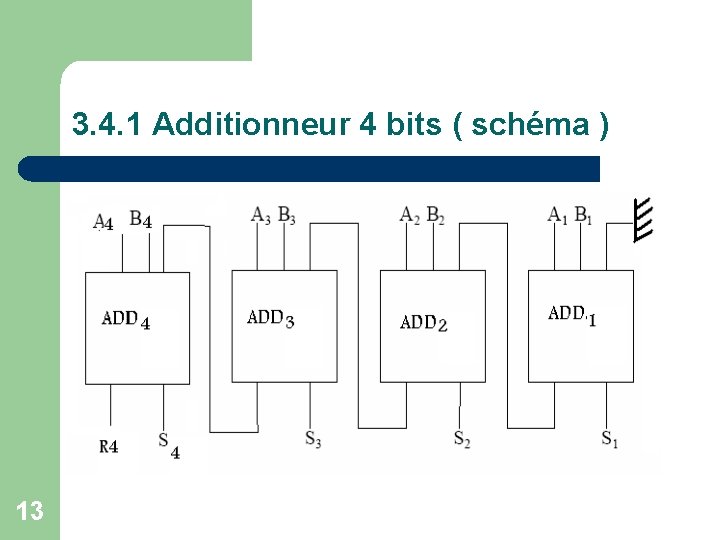

3. 4 Additionneur 4 bits r 4 12 + r 3 a 4 b 4 r 4 s 4 r 3 s 3 r 2 s 2 r 1 s 1 r 4 s 4 r 2 a 3 b 3 s 3 r 1 a 2 b 2 s 2 r 0= 0 a 1 b 1 s 1 Résultat final

3. 4. 1 Additionneur 4 bits ( schéma ) 13

Exercice l 14 Soit une information binaire sur 5 bits ( i 4 i 3 i 2 i 1 i 0). Donner le circuit qui permet de calculer le nombre de 1 dans l’information en entrée en utilisant uniquement des additionneurs complets sur 1 bit?

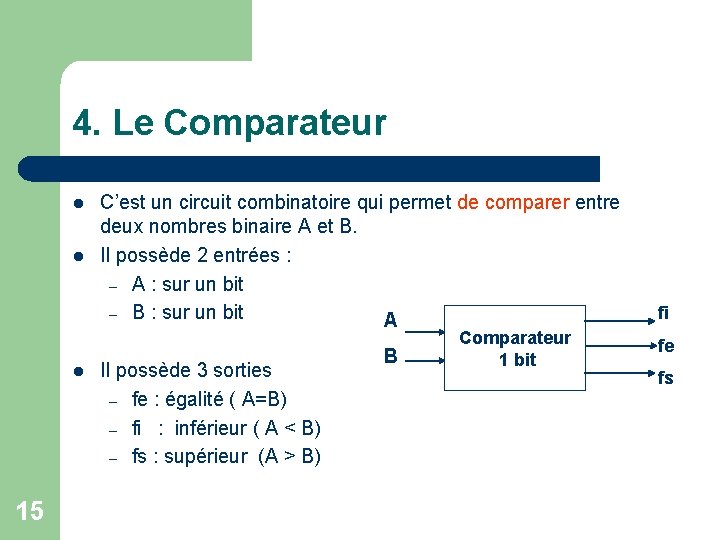

4. Le Comparateur l l l 15 C’est un circuit combinatoire qui permet de comparer entre deux nombres binaire A et B. Il possède 2 entrées : – A : sur un bit – B : sur un bit A Il possède 3 sorties – fe : égalité ( A=B) – fi : inférieur ( A < B) – fs : supérieur (A > B) B Comparateur 1 bit fi fe fs

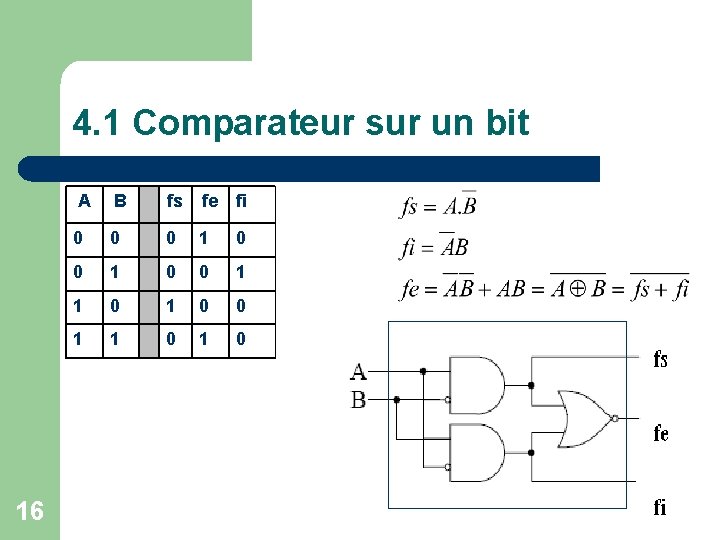

4. 1 Comparateur sur un bit 16 A B fs fe fi 0 0 0 1 1 0 1 0

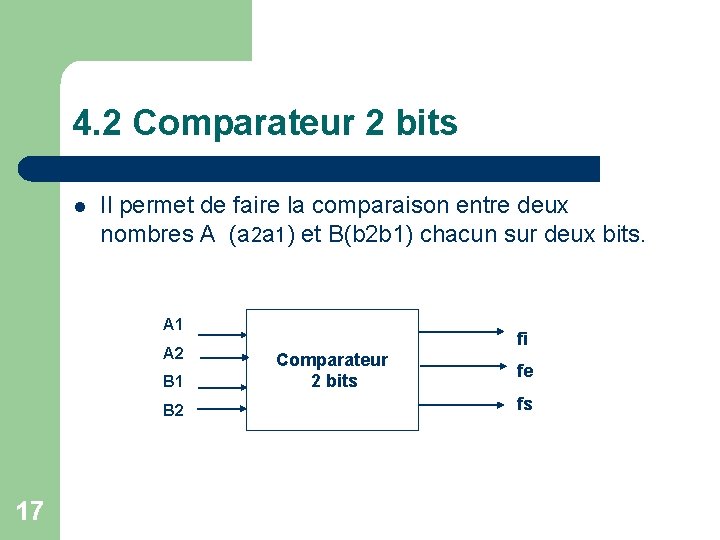

4. 2 Comparateur 2 bits l Il permet de faire la comparaison entre deux nombres A (a 2 a 1) et B(b 2 b 1) chacun sur deux bits. A 1 A 2 B 1 B 2 17 fi Comparateur 2 bits fe fs

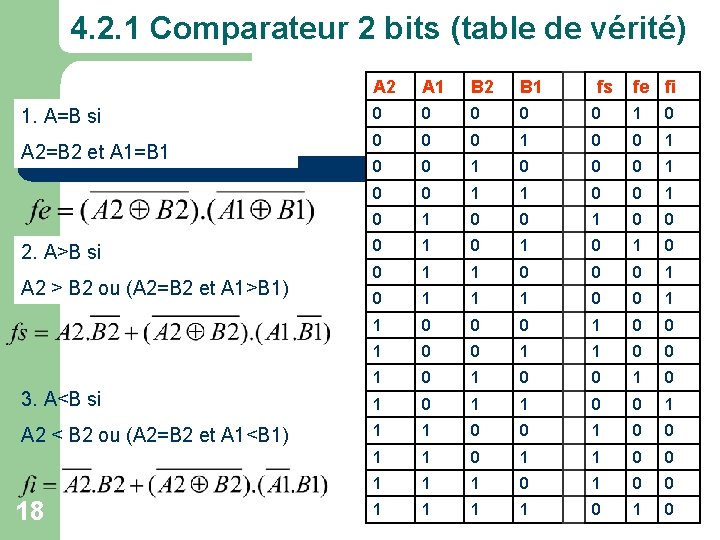

4. 2. 1 Comparateur 2 bits (table de vérité) A 2 A 1 B 2 B 1 0 0 0 1 0 0 1 0 0 0 1 1 0 0 0 1 0 1 0 0 1 1 0 0 0 1 0 0 1 1 0 0 1 0 3. A<B si 1 0 1 1 0 0 1 A 2 < B 2 ou (A 2=B 2 et A 1<B 1) 1 1 0 0 1 1 1 0 0 1 1 0 1. A=B si A 2=B 2 et A 1=B 1 2. A>B si A 2 > B 2 ou (A 2=B 2 et A 1>B 1) 18 fs fe fi

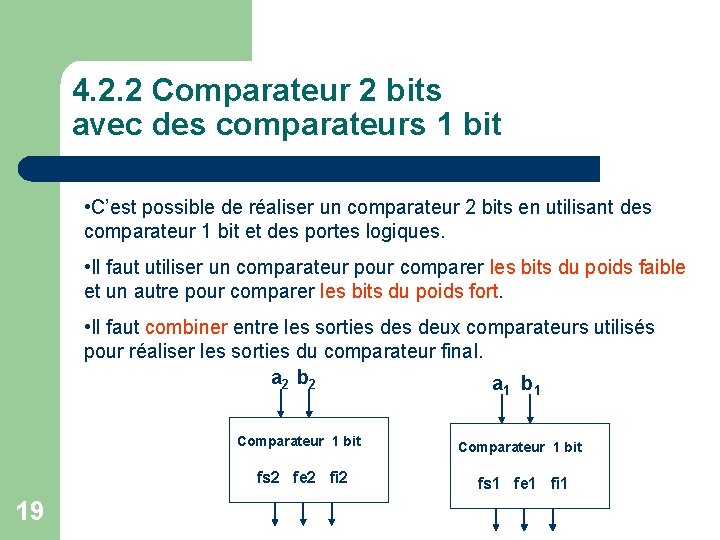

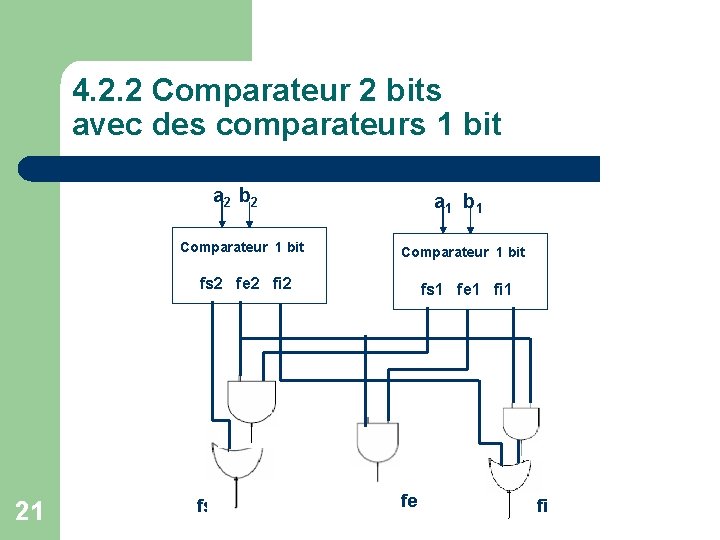

4. 2. 2 Comparateur 2 bits avec des comparateurs 1 bit • C’est possible de réaliser un comparateur 2 bits en utilisant des comparateur 1 bit et des portes logiques. • Il faut utiliser un comparateur pour comparer les bits du poids faible et un autre pour comparer les bits du poids fort. • Il faut combiner entre les sorties deux comparateurs utilisés pour réaliser les sorties du comparateur final. a 2 b 2 a b 1 19 1 Comparateur 1 bit fs 2 fe 2 fi 2 fs 1 fe 1 fi 1

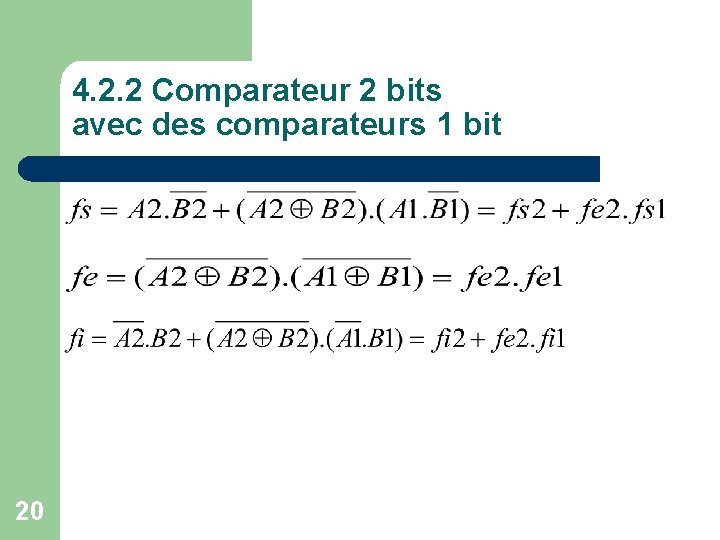

4. 2. 2 Comparateur 2 bits avec des comparateurs 1 bit 20

4. 2. 2 Comparateur 2 bits avec des comparateurs 1 bit a 2 b 2 21 a 1 b 1 Comparateur 1 bit fs 2 fe 2 fi 2 fs 1 fe 1 fi 1 fs fe fi

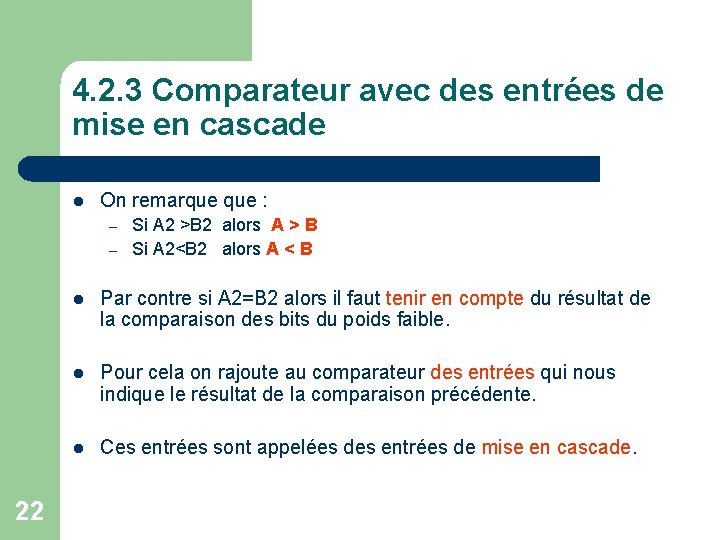

4. 2. 3 Comparateur avec des entrées de mise en cascade l On remarque : – – 22 Si A 2 >B 2 alors A > B Si A 2<B 2 alors A < B l Par contre si A 2=B 2 alors il faut tenir en compte du résultat de la comparaison des bits du poids faible. l Pour cela on rajoute au comparateur des entrées qui nous indique le résultat de la comparaison précédente. l Ces entrées sont appelées des entrées de mise en cascade.

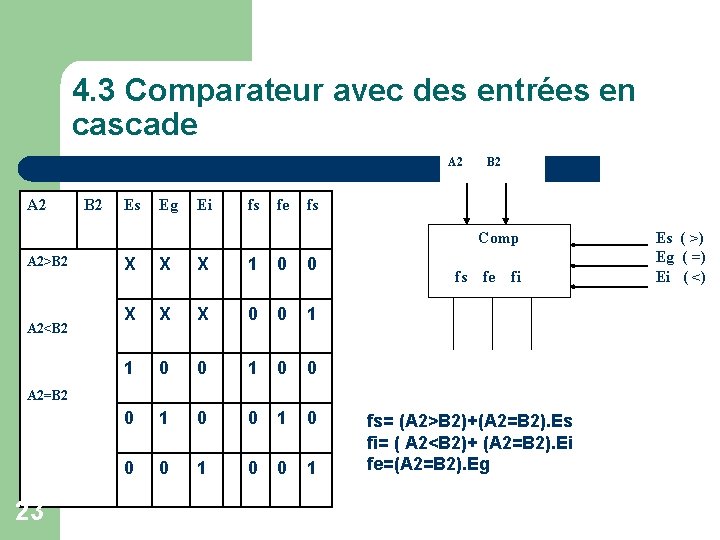

4. 3 Comparateur avec des entrées en cascade A 2 B 2 Es Eg Ei fs fe B 2 fs Comp A 2>B 2 A 2<B 2 X X X 1 0 0 X X X 0 0 1 1 0 0 0 1 0 0 1 fs fe fi A 2=B 2 23 fs= (A 2>B 2)+(A 2=B 2). Es fi= ( A 2<B 2)+ (A 2=B 2). Ei fe=(A 2=B 2). Eg Es ( >) Eg ( =) Ei ( <)

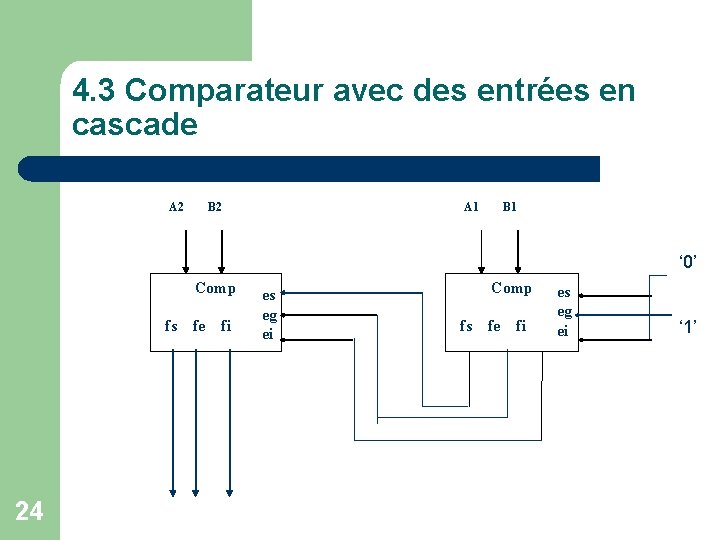

4. 3 Comparateur avec des entrées en cascade A 2 A 1 B 2 B 1 ‘ 0’ Comp fs 24 fe fi es eg ei Comp fs fe fi es eg ei ‘ 1’

Exercice l 25 Réaliser un comparateur 4 bits en utilisant des comparateurs 2 bits avec des entrées de mise en cascade?

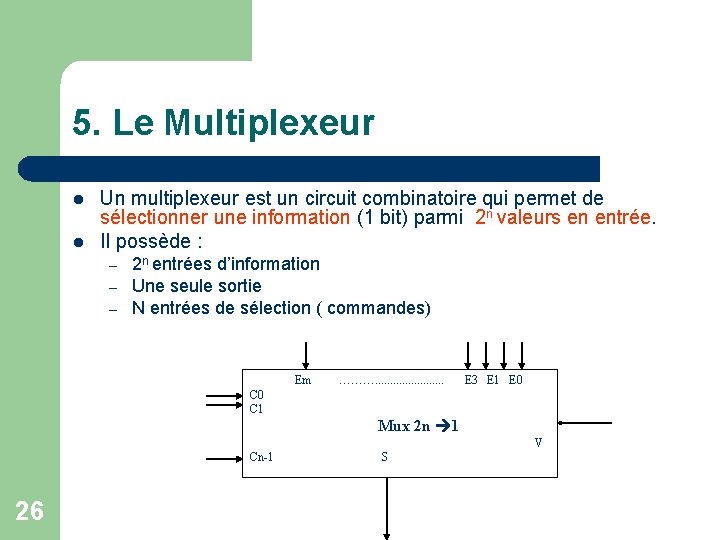

5. Le Multiplexeur l l Un multiplexeur est un circuit combinatoire qui permet de sélectionner une information (1 bit) parmi 2 n valeurs en entrée. Il possède : – – – 2 n entrées d’information Une seule sortie N entrées de sélection ( commandes) Em ………. . . E 3 E 1 E 0 C 1 Mux 2 n 1 V Cn-1 26 S

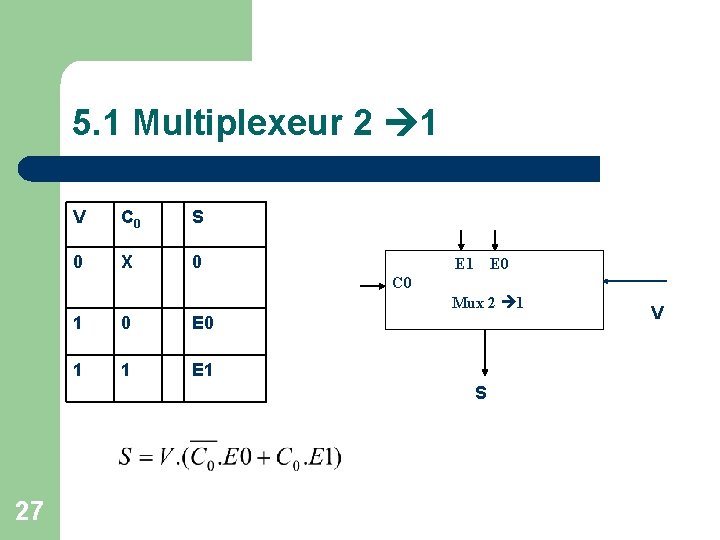

5. 1 Multiplexeur 2 1 V C 0 S 0 X 0 E 1 E 0 C 0 Mux 2 1 1 0 E 0 1 1 E 1 S 27 V

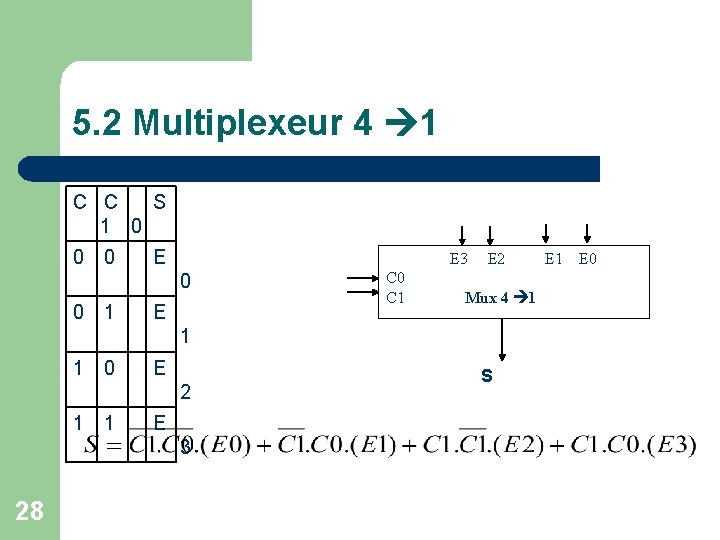

5. 2 Multiplexeur 4 1 C C S 1 0 0 0 E E 3 0 0 1 E C 0 C 1 E 2 Mux 4 1 1 1 0 E 2 1 1 E 3 28 S E 1 E 0

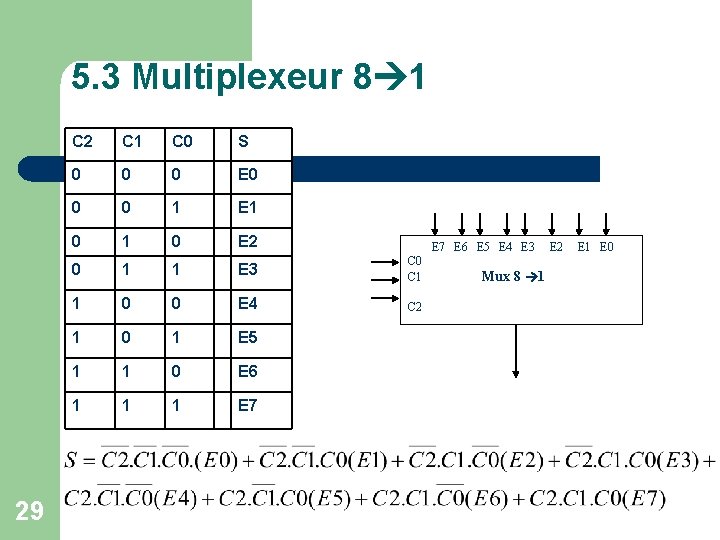

5. 3 Multiplexeur 8 1 29 C 2 C 1 C 0 S 0 0 0 E 0 0 0 1 E 1 0 E 2 0 1 1 E 3 C 0 C 1 1 0 0 E 4 C 2 1 0 1 E 5 1 1 0 E 6 1 1 1 E 7 E 6 E 5 E 4 E 3 Mux 8 1 E 2 E 1 E 0

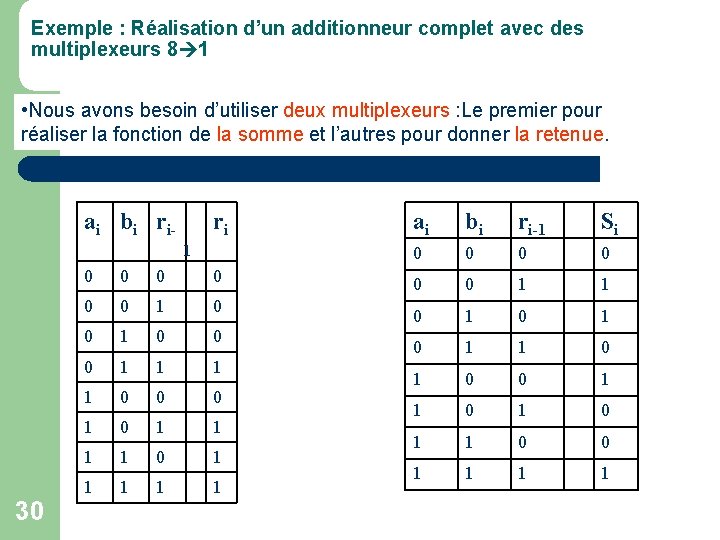

Exemple : Réalisation d’un additionneur complet avec des multiplexeurs 8 1 • Nous avons besoin d’utiliser deux multiplexeurs : Le premier pour réaliser la fonction de la somme et l’autres pour donner la retenue. ai bi ri- ri 1 30 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 1 ai bi ri-1 Si 0 0 0 1 1 0 1 0 1 0 0 1 1 0 0 1 1

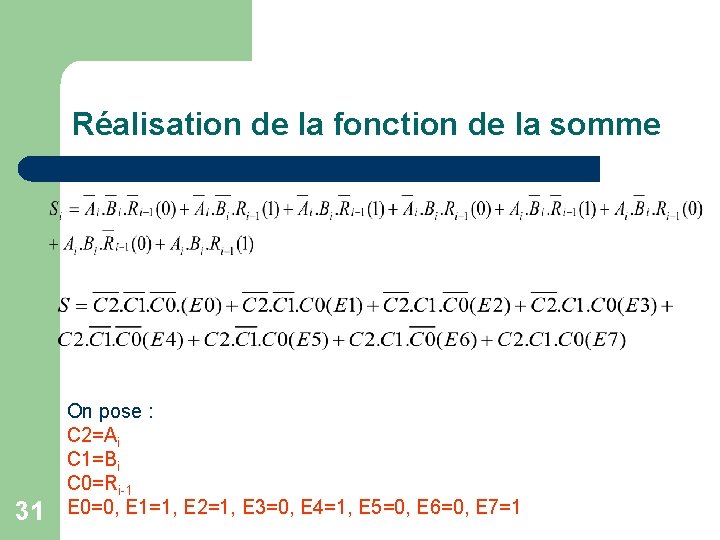

Réalisation de la fonction de la somme 31 On pose : C 2=Ai C 1=Bi C 0=Ri-1 E 0=0, E 1=1, E 2=1, E 3=0, E 4=1, E 5=0, E 6=0, E 7=1

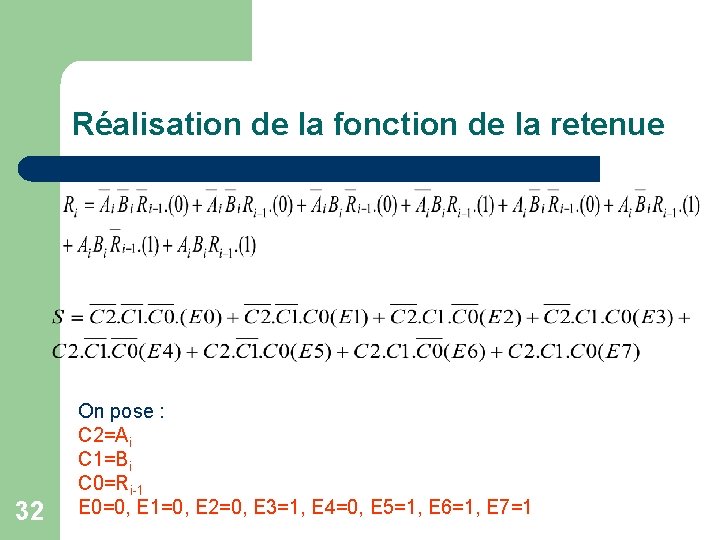

Réalisation de la fonction de la retenue 32 On pose : C 2=Ai C 1=Bi C 0=Ri-1 E 0=0, E 1=0, E 2=0, E 3=1, E 4=0, E 5=1, E 6=1, E 7=1

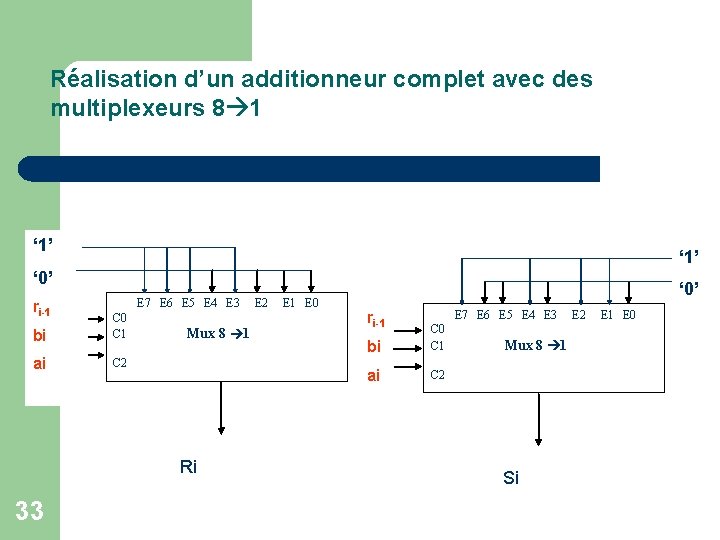

Réalisation d’un additionneur complet avec des multiplexeurs 8 1 ‘ 1’ ‘ 0’ ri-1 E 7 E 6 E 5 E 4 E 3 bi C 0 C 1 ai C 2 Mux 8 1 Ri 33 E 2 E 1 E 0 ‘ 0’ ri-1 E 7 E 6 E 5 E 4 E 3 bi C 0 C 1 ai C 2 Mux 8 1 Si E 2 E 1 E 0

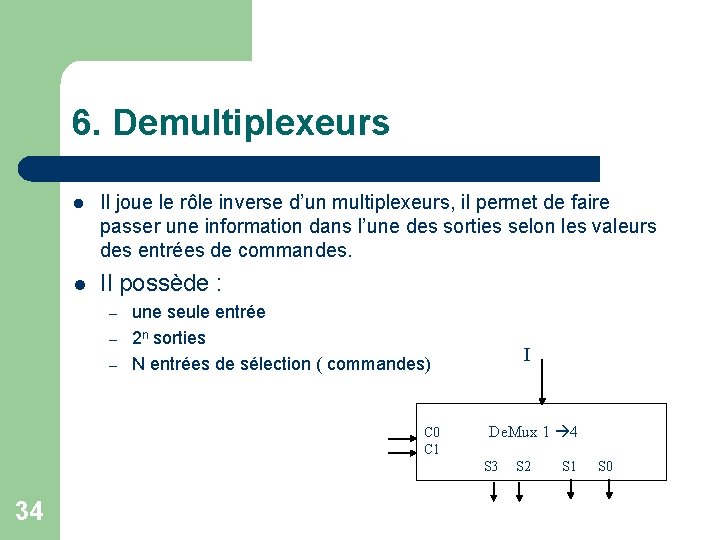

6. Demultiplexeurs l Il joue le rôle inverse d’un multiplexeurs, il permet de faire passer une information dans l’une des sorties selon les valeurs des entrées de commandes. l Il possède : – – – une seule entrée 2 n sorties N entrées de sélection ( commandes) C 0 C 1 I De. Mux 1 4 S 3 34 S 2 S 1 S 0

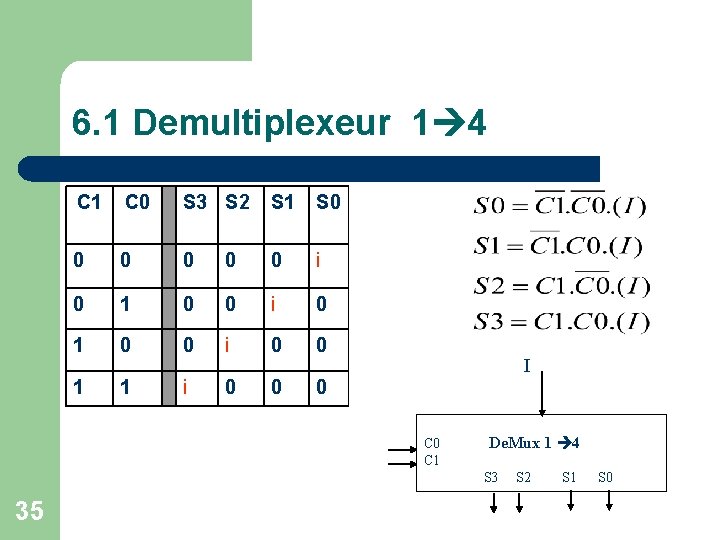

6. 1 Demultiplexeur 1 4 C 1 C 0 S 3 S 2 S 1 S 0 0 0 i 0 1 0 0 i 0 0 1 1 i 0 0 0 I C 0 C 1 De. Mux 1 4 S 3 35 S 2 S 1 S 0

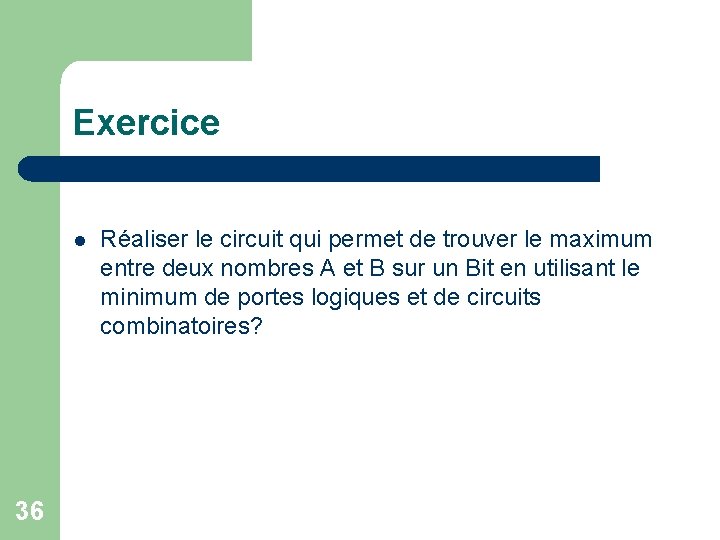

Exercice l 36 Réaliser le circuit qui permet de trouver le maximum entre deux nombres A et B sur un Bit en utilisant le minimum de portes logiques et de circuits combinatoires?

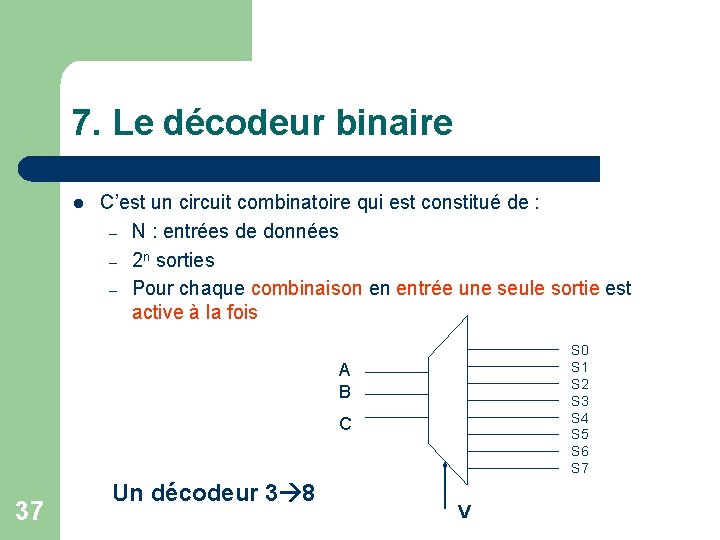

7. Le décodeur binaire l C’est un circuit combinatoire qui est constitué de : – N : entrées de données – 2 n sorties – Pour chaque combinaison en entrée une seule sortie est active à la fois S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 A B C 37 Un décodeur 3 8 V

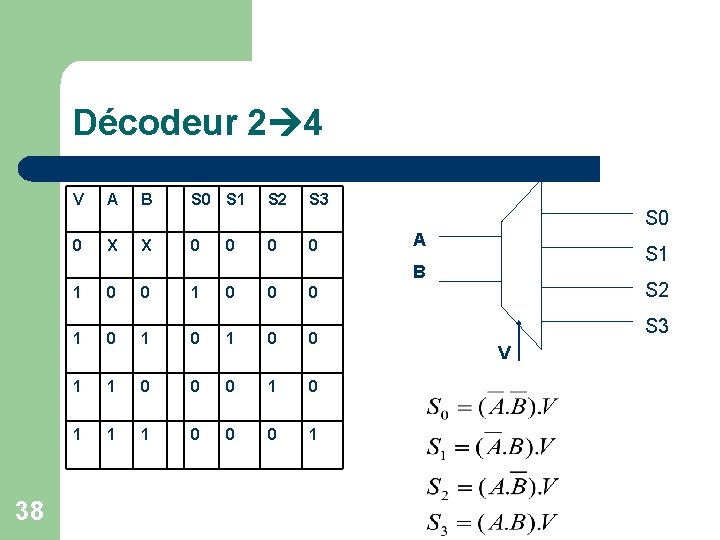

Décodeur 2 4 V A B S 0 S 1 S 2 S 3 0 X X 0 0 S 0 A S 1 B 38 1 0 0 0 1 0 1 0 0 1 1 0 0 0 1 S 2 S 3 V

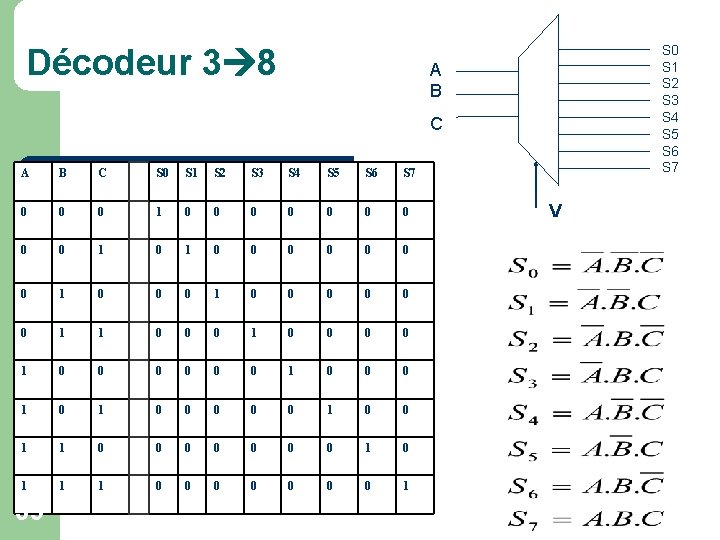

Décodeur 3 8 S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 A B C S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 1 39 V

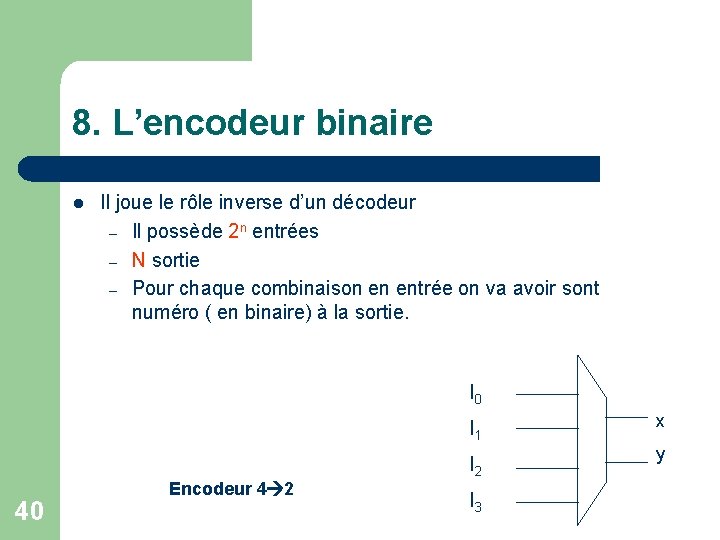

8. L’encodeur binaire l Il joue le rôle inverse d’un décodeur – Il possède 2 n entrées – N sortie – Pour chaque combinaison en entrée on va avoir sont numéro ( en binaire) à la sortie. I 0 I 1 I 2 40 Encodeur 4 2 I 3 x y

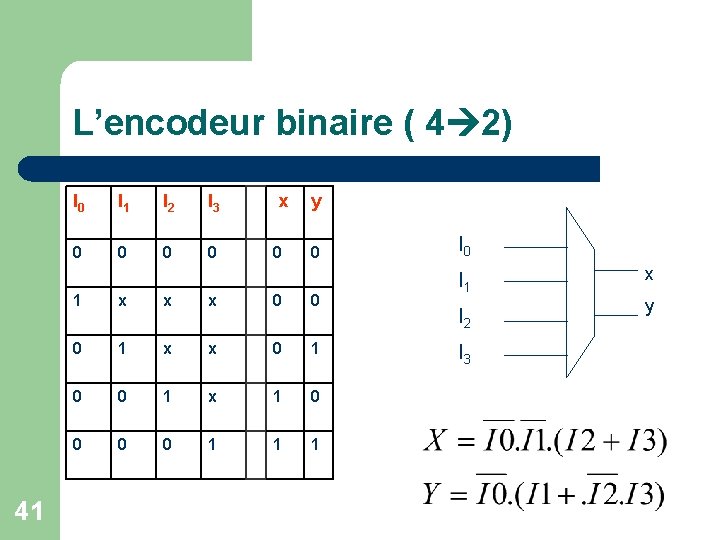

L’encodeur binaire ( 4 2) 41 I 0 I 1 I 2 I 3 0 0 x 0 y 0 1 x x x 0 0 0 1 x x 0 1 0 0 1 x 1 0 0 1 1 1 I 0 I 1 I 2 I 3 x y

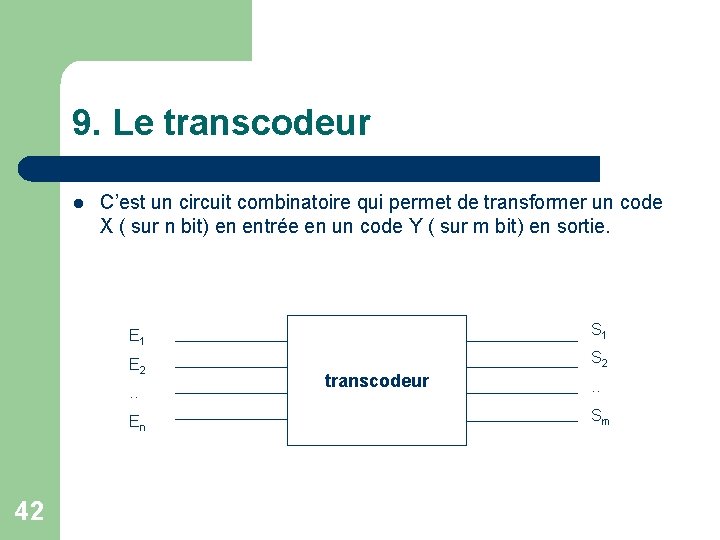

9. Le transcodeur l C’est un circuit combinatoire qui permet de transformer un code X ( sur n bit) en entrée en un code Y ( sur m bit) en sortie. E 1 S 1 E 2 S 2 . . En 42 transcodeur . . Sm

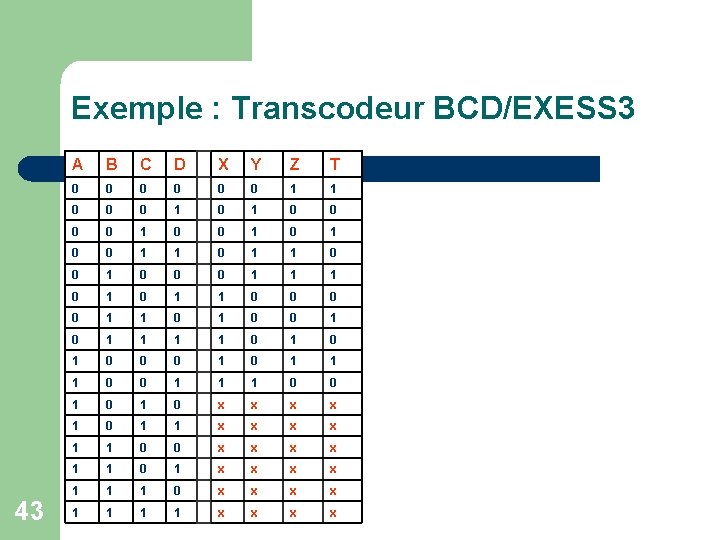

Exemple : Transcodeur BCD/EXESS 3 43 A B C D X Y Z T 0 0 0 1 1 0 0 0 1 0 0 1 1 0 0 0 1 1 1 0 0 1 1 0 0 1 1 1 1 0 1 0 0 0 1 1 1 0 0 1 0 1 0 x x 1 0 1 1 x x 1 1 0 0 x x 1 1 0 1 x x 1 1 1 0 x x 1 1 x x

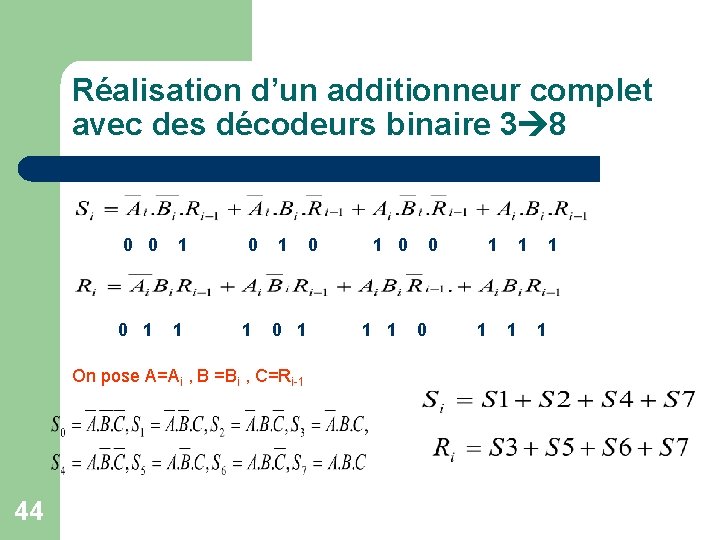

Réalisation d’un additionneur complet avec des décodeurs binaire 3 8 0 0 0 1 1 1 0 1 On pose A=Ai , B =Bi , C=Ri-1 44 0 1 1 0 0 1 1 1

- Slides: 44