Chap 6 3 UART UART Universal Asynchronous ReceiverTransmitter

![UBRRn. L /UBRRn. H - USART Baud Rate Registers UBRRn[11: 0]: USARTn Baud Rate UBRRn. L /UBRRn. H - USART Baud Rate Registers UBRRn[11: 0]: USARTn Baud Rate](https://slidetodoc.com/presentation_image_h/0053de17df16257a9fb4729d90a99390/image-11.jpg)

- Slides: 21

Chap. 6. 3 UART

UART Universal Asynchronous Receiver/Transmitter a piece of computer hardware that translates data between parallel and serial forms Ø parallel : inside computer Ø serial : serial communication USART universal synchronous/asynchronous receiver/transmitter RS-232 C protocol Baud Rate or bps : bits per second stop bit : 1, 1. 5, 2 bit parity : error detecting code data length : number of data bits in a frame incoming Lab.

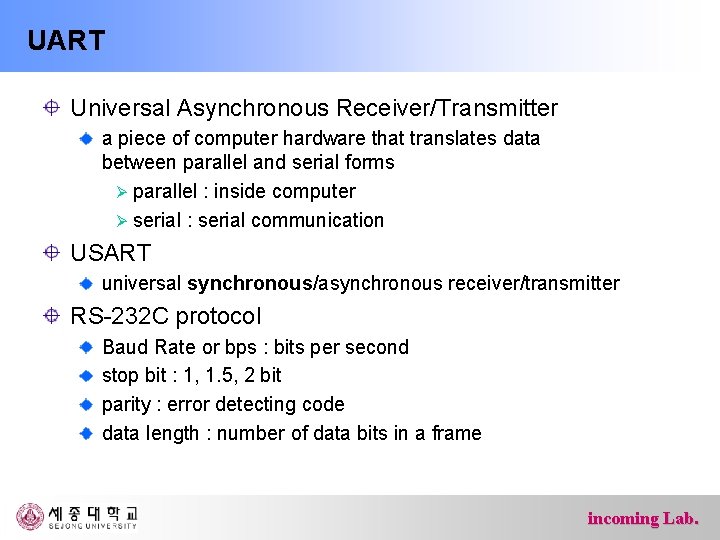

USART in ATmega 128 – Block Diagram : Register : Pin-Out incoming Lab.

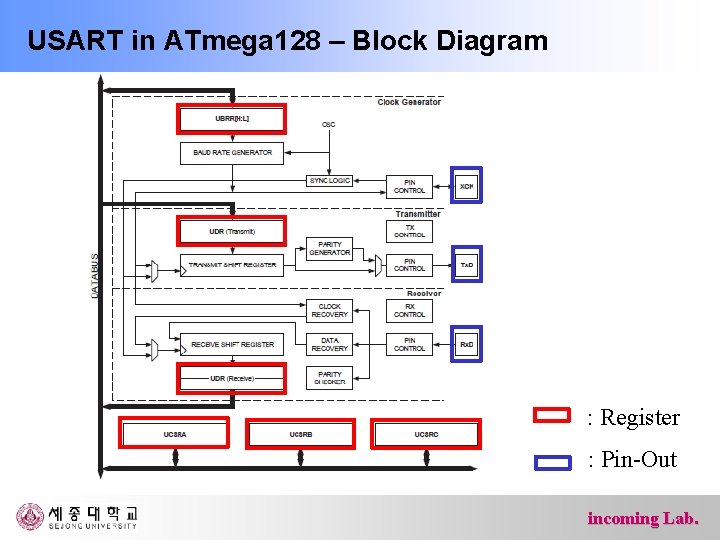

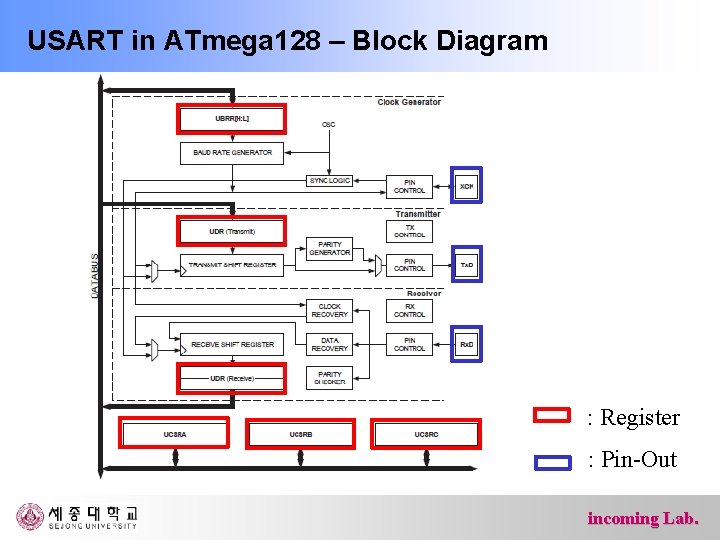

USART in ATmega 128 Frame Formats : 1 start bit 5, 6, 7, 8 or 9 data bits no, even or odd parity bit 1 or 2 stop bits incoming Lab.

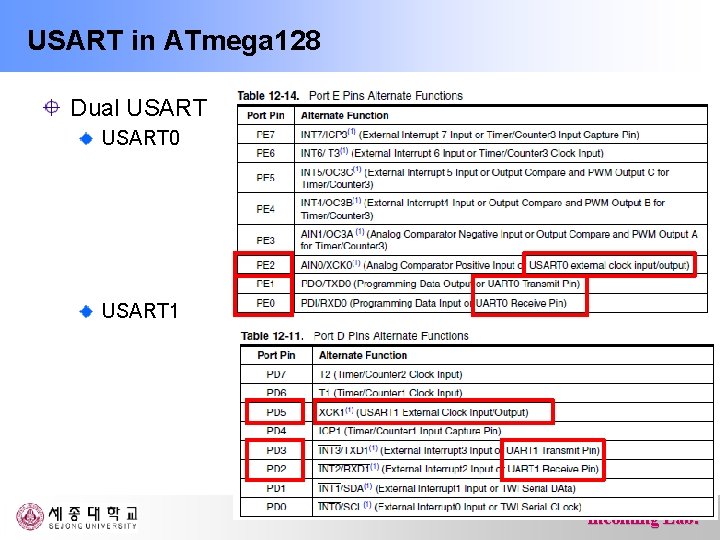

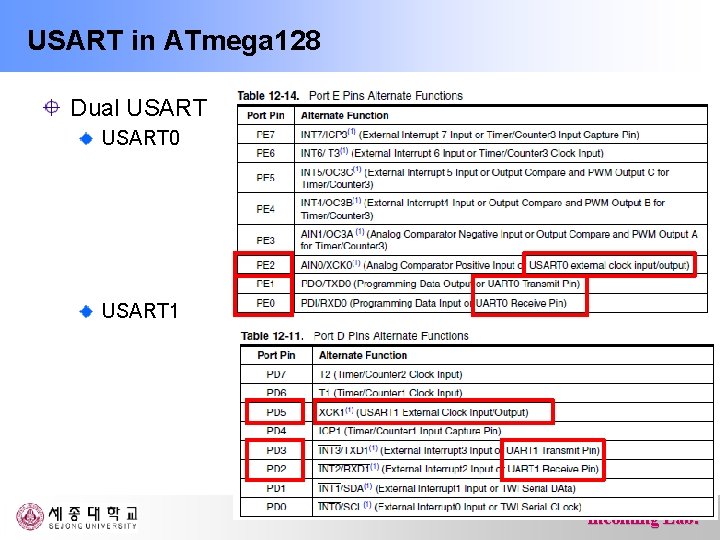

USART in ATmega 128 Dual USART 0 USART 1 incoming Lab.

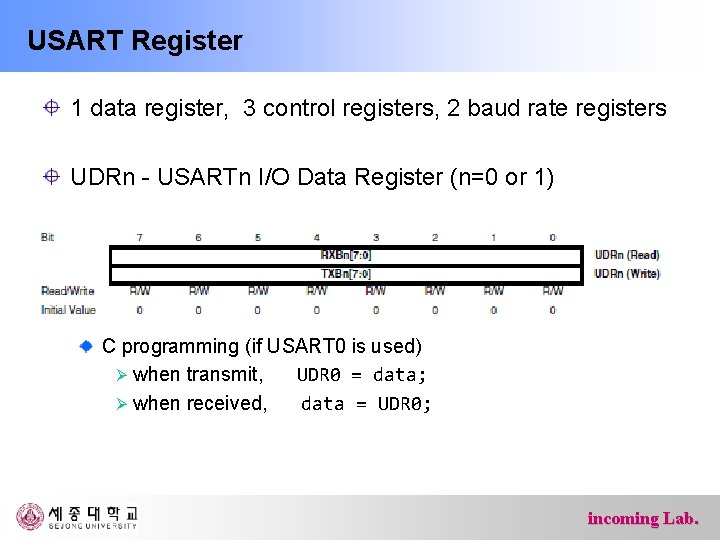

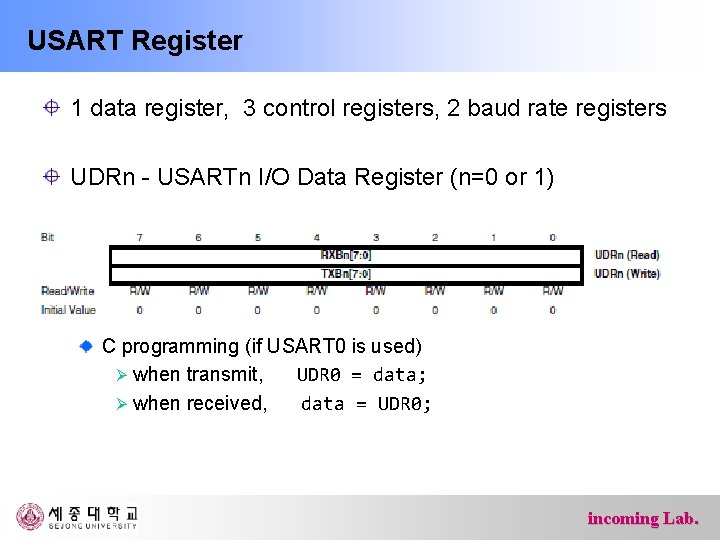

USART Register 1 data register, 3 control registers, 2 baud rate registers UDRn - USARTn I/O Data Register (n=0 or 1) C programming (if USART 0 is used) Ø when transmit, UDR 0 = data; Ø when received, data = UDR 0; incoming Lab.

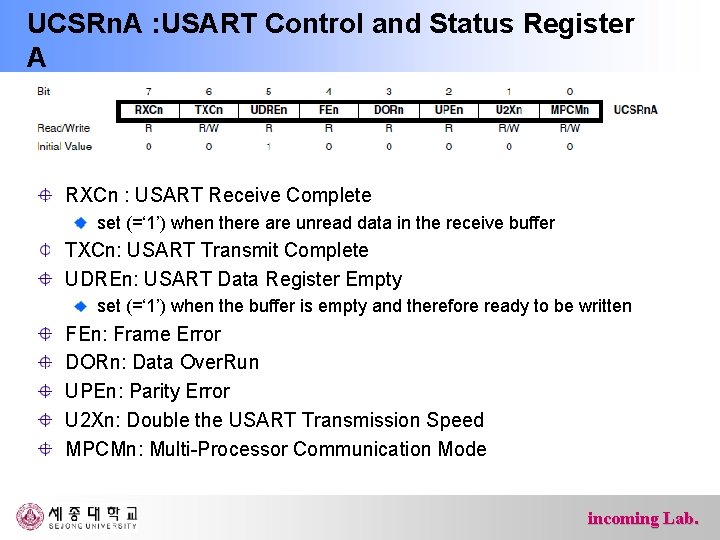

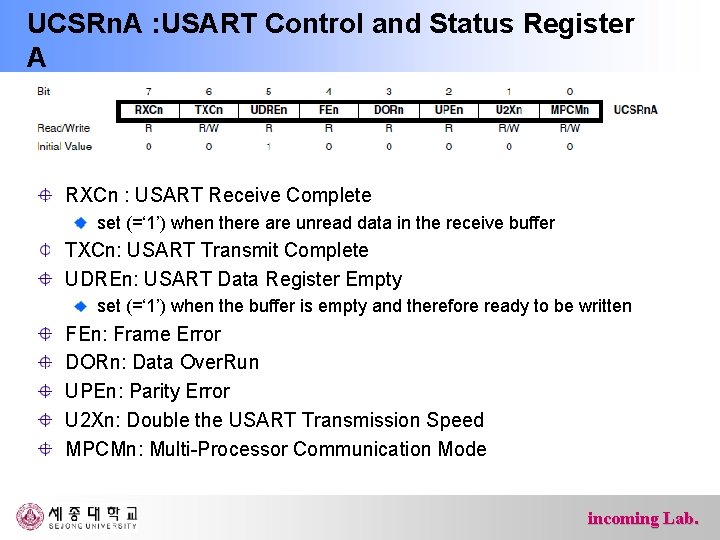

UCSRn. A : USART Control and Status Register A RXCn : USART Receive Complete set (=‘ 1’) when there are unread data in the receive buffer TXCn: USART Transmit Complete UDREn: USART Data Register Empty set (=‘ 1’) when the buffer is empty and therefore ready to be written FEn: Frame Error DORn: Data Over. Run UPEn: Parity Error U 2 Xn: Double the USART Transmission Speed MPCMn: Multi-Processor Communication Mode incoming Lab.

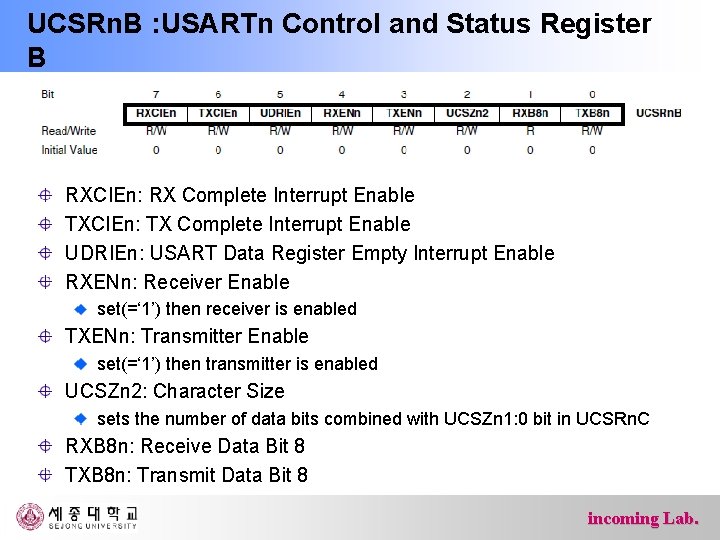

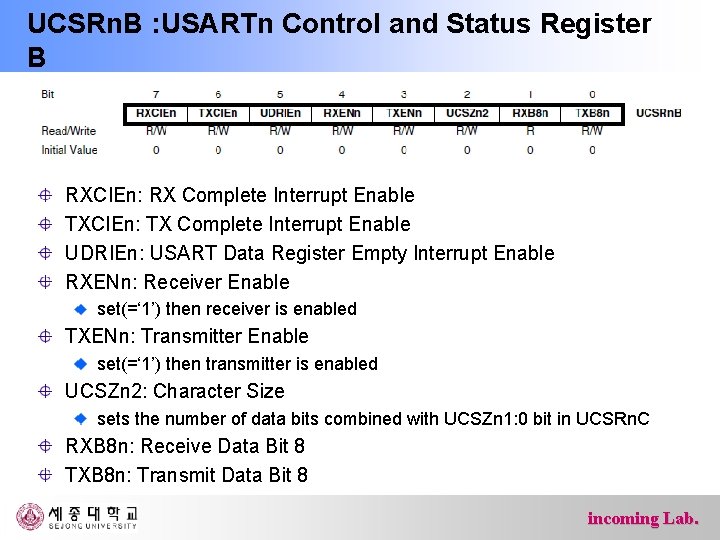

UCSRn. B : USARTn Control and Status Register B RXCIEn: RX Complete Interrupt Enable TXCIEn: TX Complete Interrupt Enable UDRIEn: USART Data Register Empty Interrupt Enable RXENn: Receiver Enable set(=‘ 1’) then receiver is enabled TXENn: Transmitter Enable set(=‘ 1’) then transmitter is enabled UCSZn 2: Character Size sets the number of data bits combined with UCSZn 1: 0 bit in UCSRn. C RXB 8 n: Receive Data Bit 8 TXB 8 n: Transmit Data Bit 8 incoming Lab.

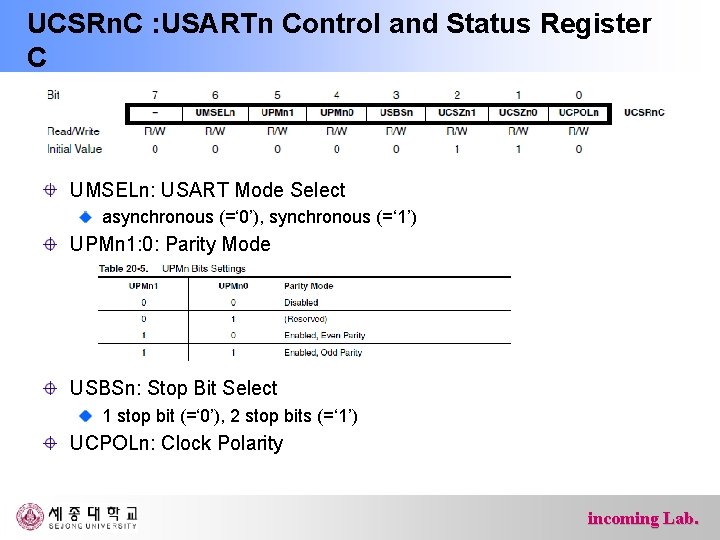

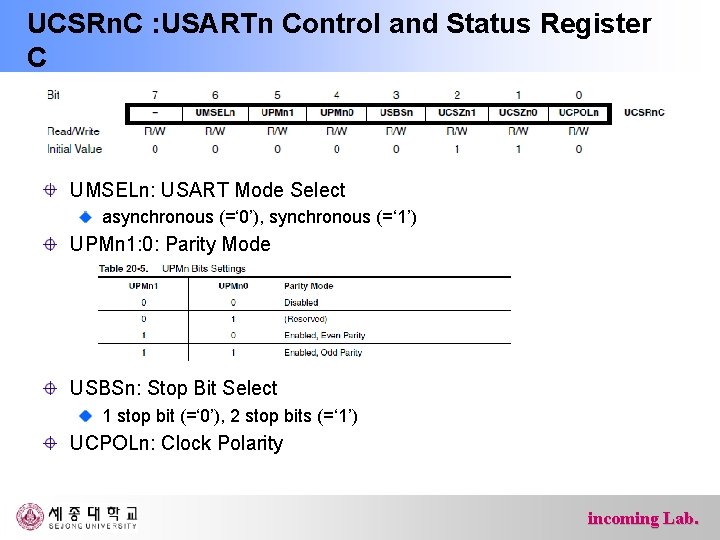

UCSRn. C : USARTn Control and Status Register C UMSELn: USART Mode Select asynchronous (=‘ 0’), synchronous (=‘ 1’) UPMn 1: 0: Parity Mode USBSn: Stop Bit Select 1 stop bit (=‘ 0’), 2 stop bits (=‘ 1’) UCPOLn: Clock Polarity incoming Lab.

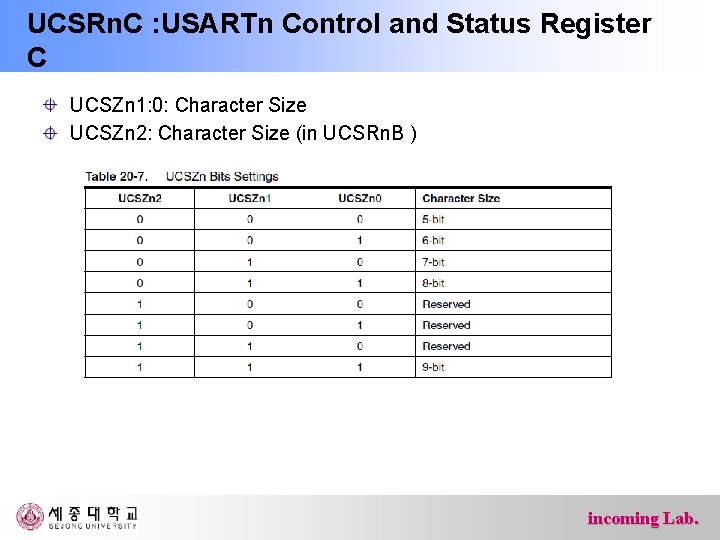

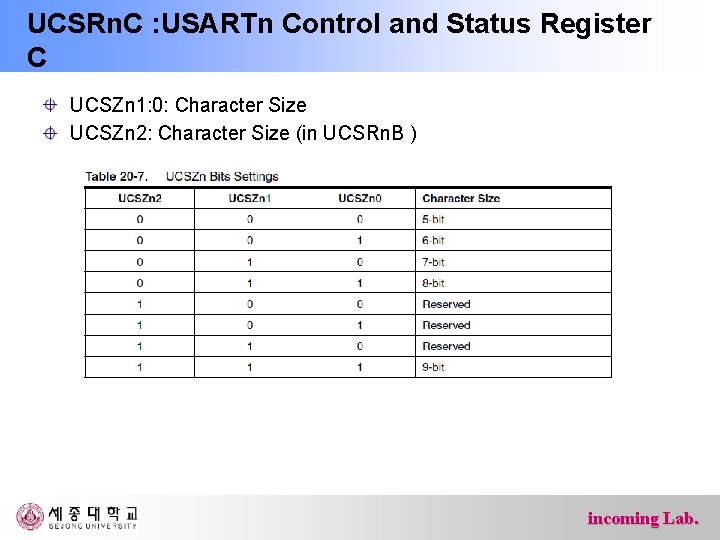

UCSRn. C : USARTn Control and Status Register C UCSZn 1: 0: Character Size UCSZn 2: Character Size (in UCSRn. B ) incoming Lab.

![UBRRn L UBRRn H USART Baud Rate Registers UBRRn11 0 USARTn Baud Rate UBRRn. L /UBRRn. H - USART Baud Rate Registers UBRRn[11: 0]: USARTn Baud Rate](https://slidetodoc.com/presentation_image_h/0053de17df16257a9fb4729d90a99390/image-11.jpg)

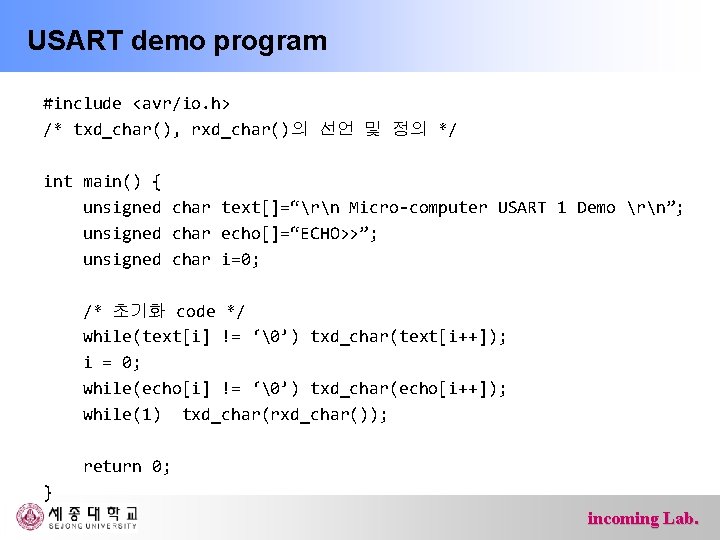

UBRRn. L /UBRRn. H - USART Baud Rate Registers UBRRn[11: 0]: USARTn Baud Rate Register % fosc = system clock freq. incoming Lab.

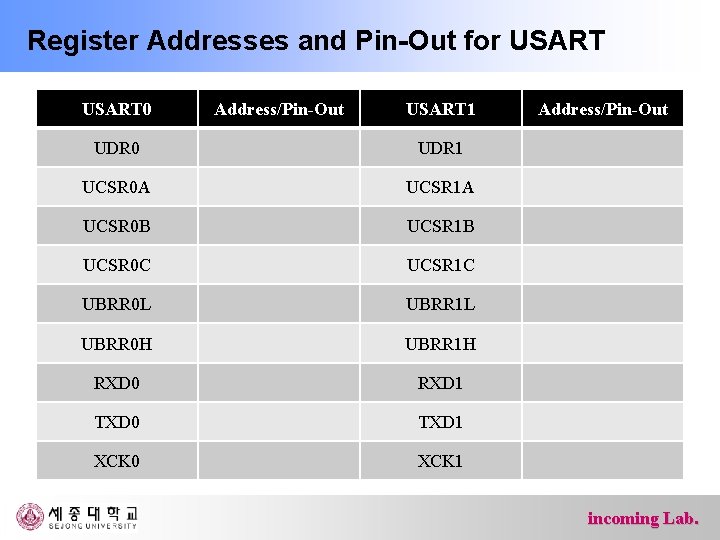

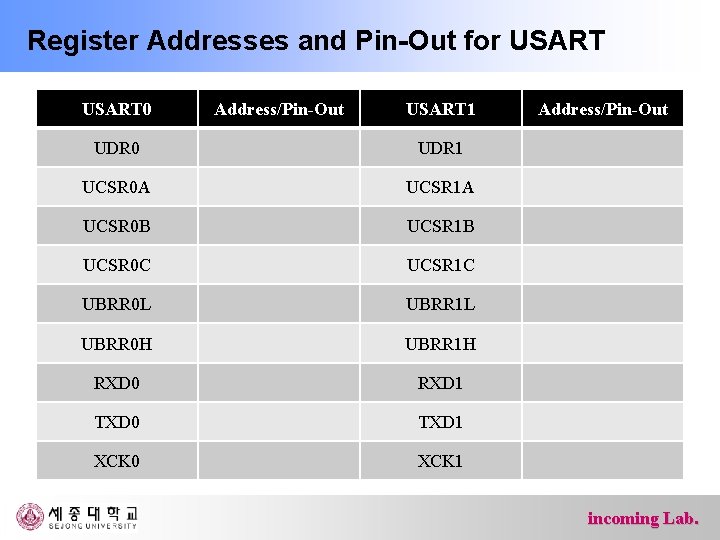

Register Addresses and Pin-Out for USART 0 Address/Pin-Out USART 1 UDR 0 UDR 1 UCSR 0 A UCSR 1 A UCSR 0 B UCSR 1 B UCSR 0 C UCSR 1 C UBRR 0 L UBRR 1 L UBRR 0 H UBRR 1 H RXD 0 RXD 1 TXD 0 TXD 1 XCK 0 XCK 1 Address/Pin-Out incoming Lab.

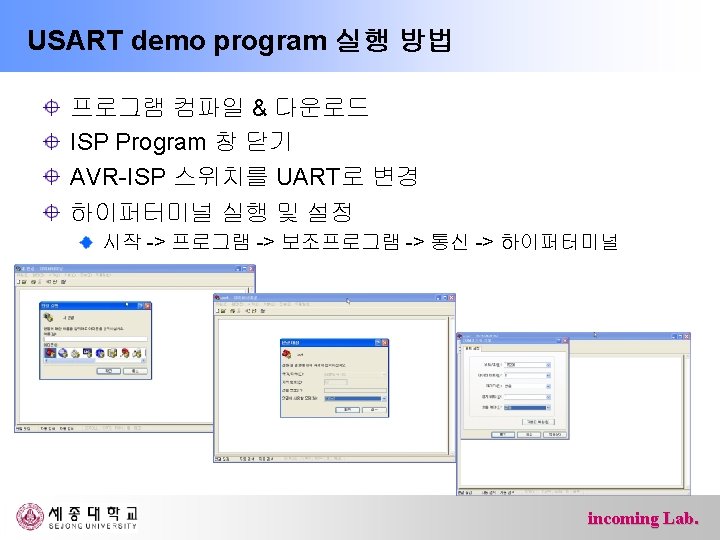

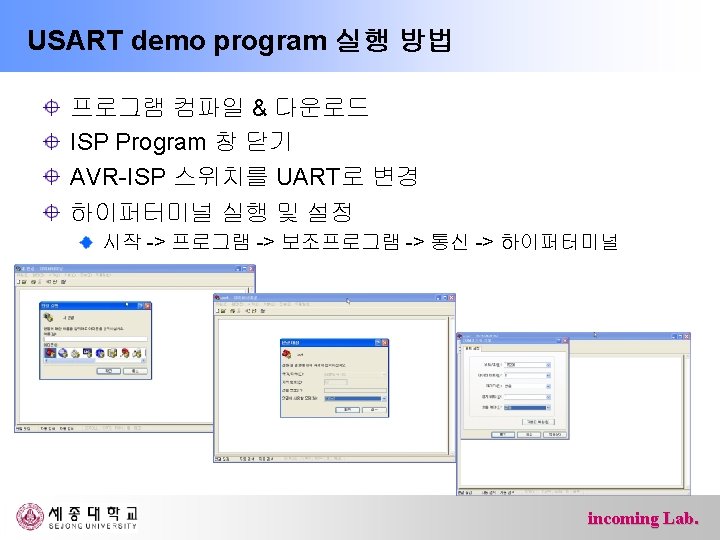

USART Demo Program USART 통신 하이퍼 터미널 Demo program Key Board incoming Lab.

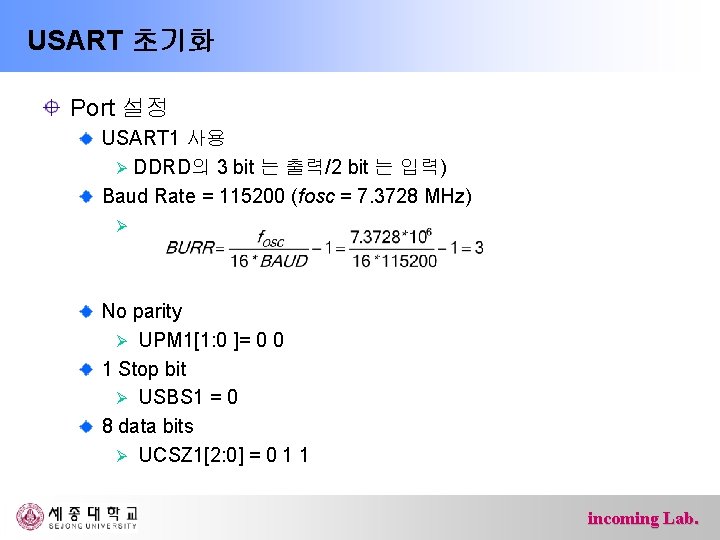

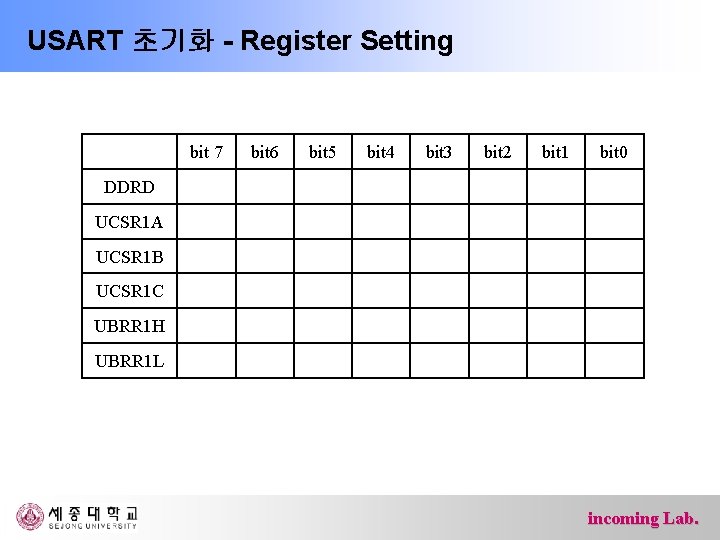

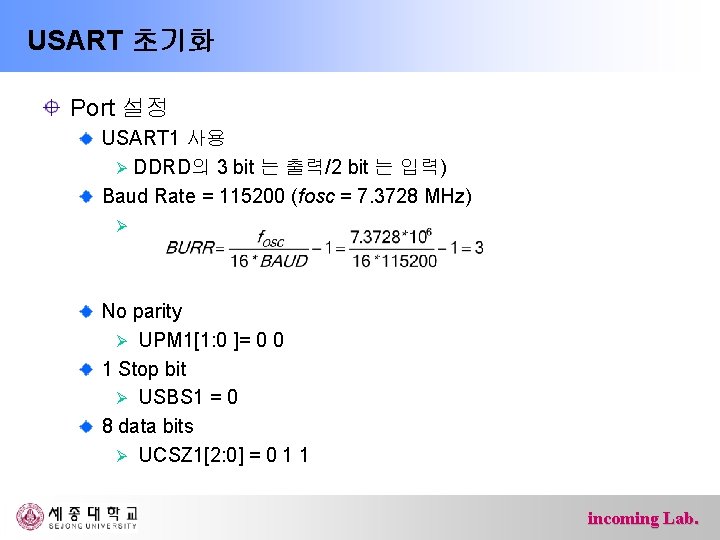

USART 초기화 Port 설정 USART 1 사용 Ø DDRD의 3 bit 는 출력/2 bit 는 입력) Baud Rate = 115200 (fosc = 7. 3728 MHz) Ø No parity Ø UPM 1[1: 0 ]= 0 0 1 Stop bit Ø USBS 1 = 0 8 data bits Ø UCSZ 1[2: 0] = 0 1 1 incoming Lab.

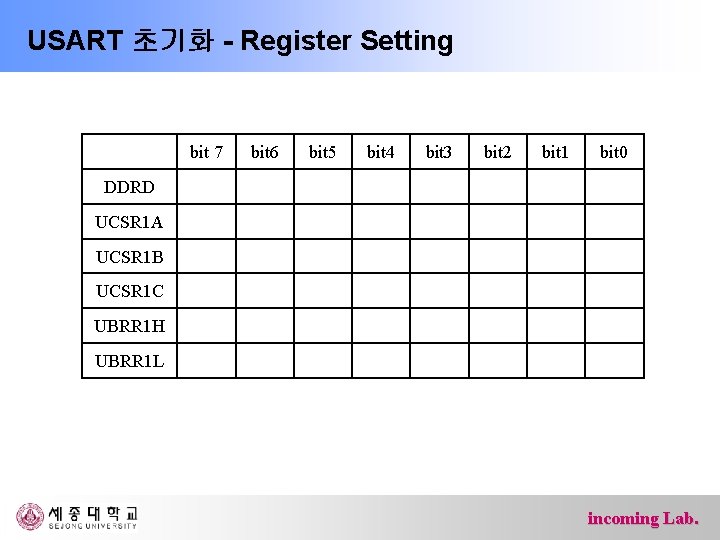

USART 초기화 - Register Setting bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 DDRD UCSR 1 A UCSR 1 B UCSR 1 C UBRR 1 H UBRR 1 L incoming Lab.

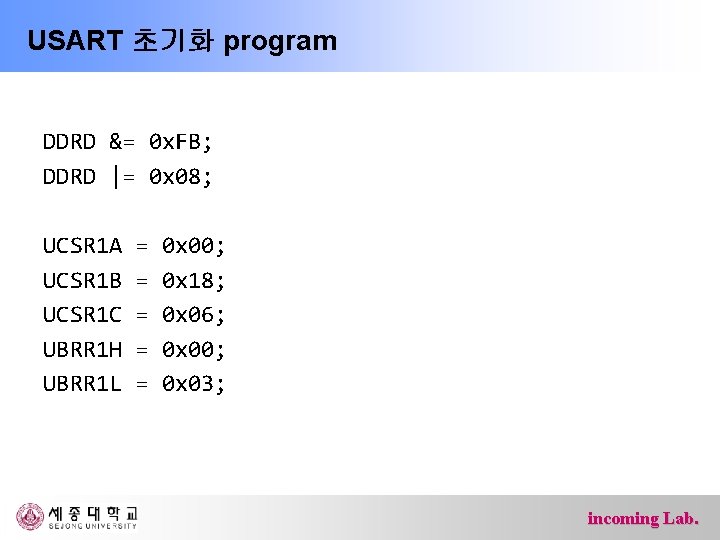

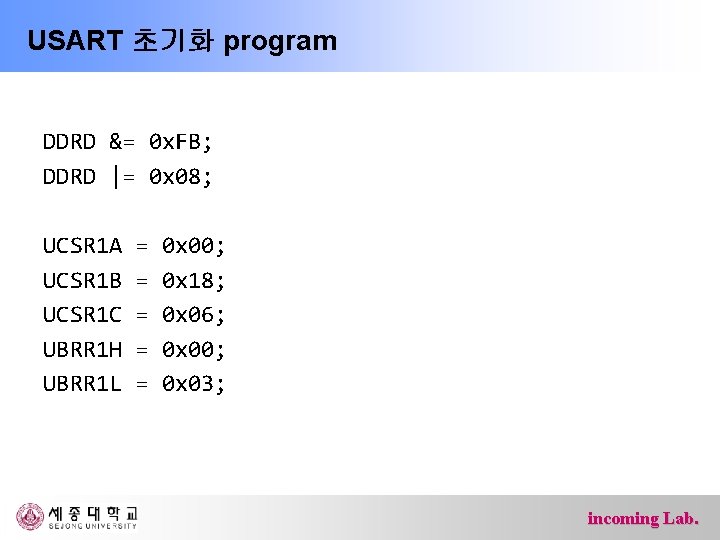

USART 초기화 program DDRD &= 0 x. FB; DDRD |= 0 x 08; UCSR 1 A UCSR 1 B UCSR 1 C UBRR 1 H UBRR 1 L = = = 0 x 00; 0 x 18; 0 x 06; 0 x 00; 0 x 03; incoming Lab.

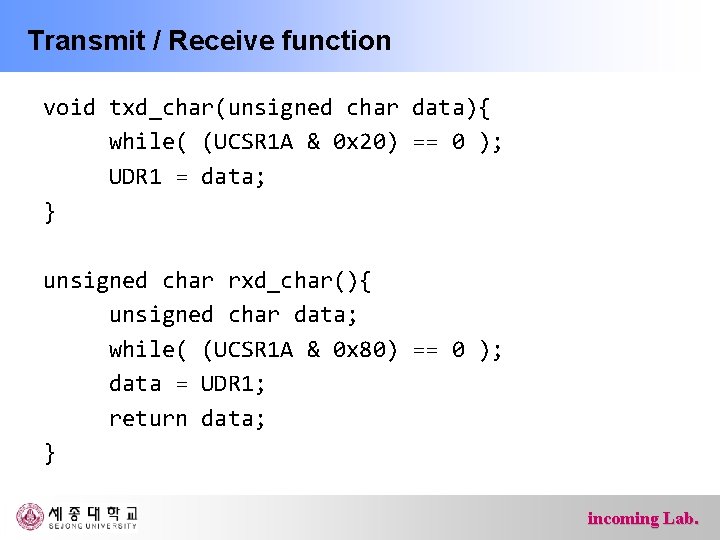

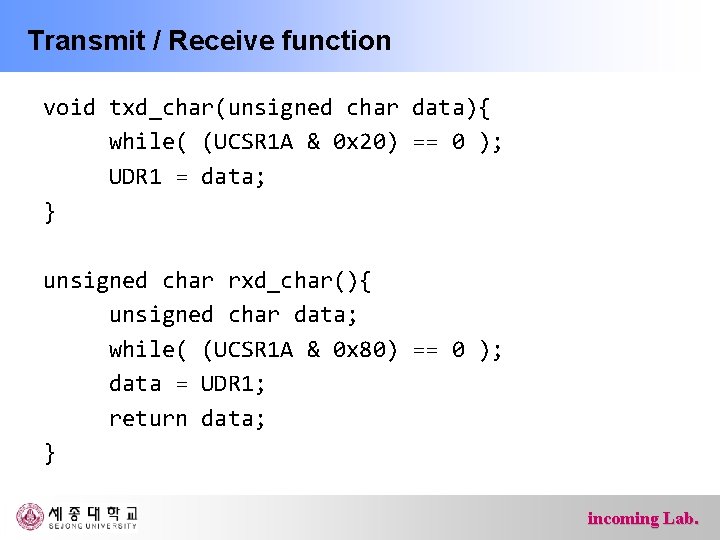

Transmit / Receive function void txd_char(unsigned char data){ while( (UCSR 1 A & 0 x 20) == 0 ); UDR 1 = data; } unsigned char rxd_char(){ unsigned char data; while( (UCSR 1 A & 0 x 80) == 0 ); data = UDR 1; return data; } incoming Lab.

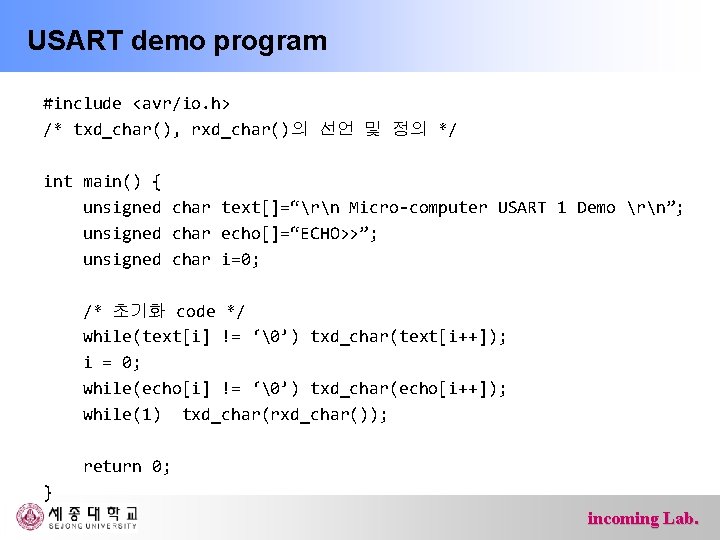

USART demo program #include <avr/io. h> /* txd_char(), rxd_char()의 선언 및 정의 */ int main() { unsigned char text[]=“rn Micro-computer USART 1 Demo rn”; unsigned char echo[]=“ECHO>>”; unsigned char i=0; /* 초기화 code */ while(text[i] != ‘�’) txd_char(text[i++]); i = 0; while(echo[i] != ‘�’) txd_char(echo[i++]); while(1) txd_char(rxd_char()); return 0; } incoming Lab.

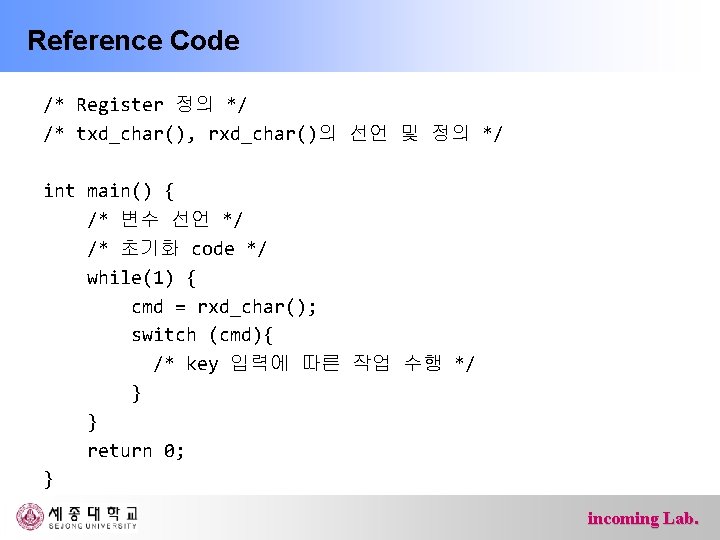

Reference Code /* Register 정의 */ /* txd_char(), rxd_char()의 선언 및 정의 */ int main() { /* 변수 선언 */ /* 초기화 code */ while(1) { cmd = rxd_char(); switch (cmd){ /* key 입력에 따른 작업 수행 */ } } return 0; } incoming Lab.