Ch 2 Introduction to HDLs Typical Circuit Design

- Slides: 12

Ch. 2 – Introduction to HDLs • Typical Circuit Design Flow – Figure 2. 1 (p. 32) – – – – 6/9/2021 Design Specification High-Level Design Develop Test Bench Simulation -- Functional Verification Gate-Level or Transistor-Level Design Simulation -- Timing Verification Implementation (board, FPGA, ASIC) Prototype Testing Advanced Digital Logic Design 1

Hardware Description Language • Similar to a Programming Language – Customized for description of digital hardware – Important difference: hardware is inherently parallel • Hardware Description Methods – Behavioral description • Procedural description of how device should operate – Structural description • Specifies how device is connected internally – Mixed behavioral/structural description • Major Hardware Description Languages (HDLs) – VHDL – Verilog HDL – System C 6/9/2021 Advanced Digital Logic Design 2

Synthesis • Automatic generation of logic from HDL code • Must understand what types of logic circuits are synthesized form what types of HDL code • Example: 3 possible ways to write Verilog code for a counter – Draw schematic, then convert schematic to Verilog • If it is a binary counter, then use the CB 4 CE library part – For other types of counters, more parts may be necessary – Design counter using FSM method, then write structural HDL code based on that design – Write high-level behavioral HDL code (BEST method) 6/9/2021 Advanced Digital Logic Design 3

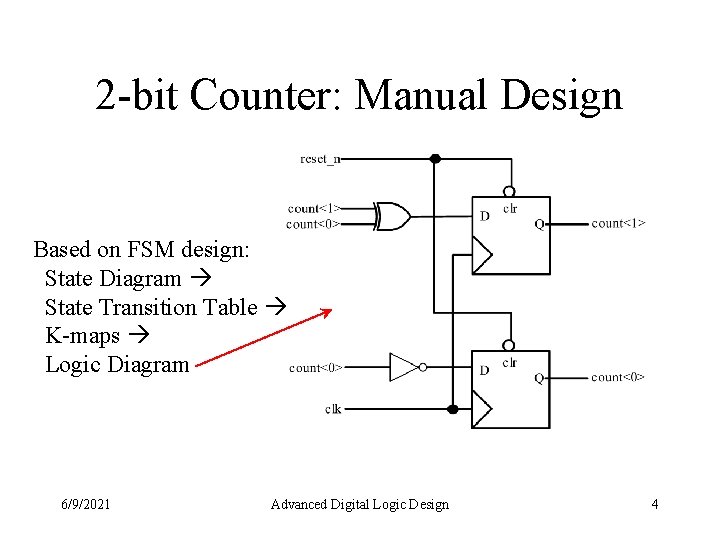

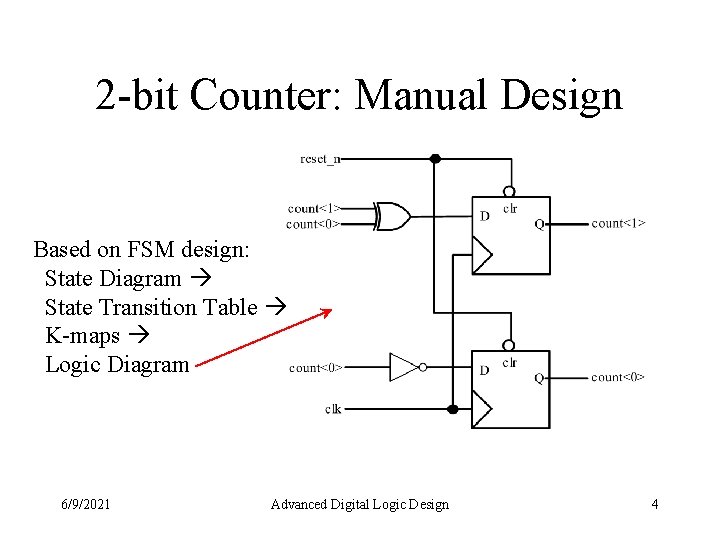

2 -bit Counter: Manual Design Based on FSM design: State Diagram State Transition Table K-maps Logic Diagram 6/9/2021 Advanced Digital Logic Design 4

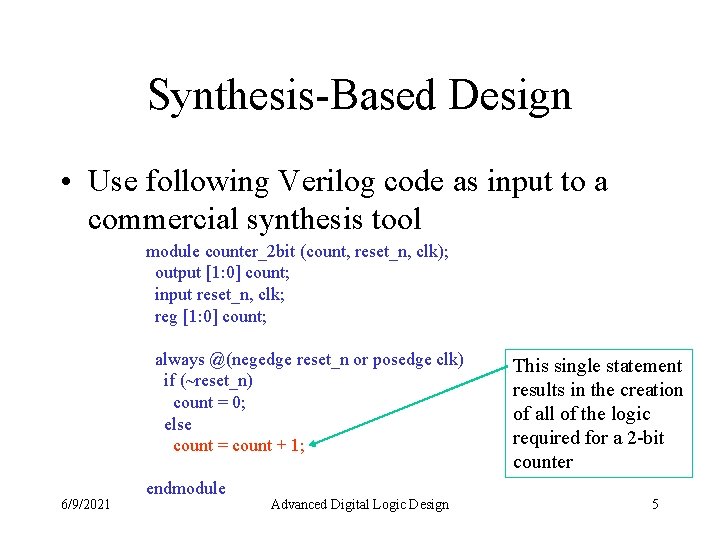

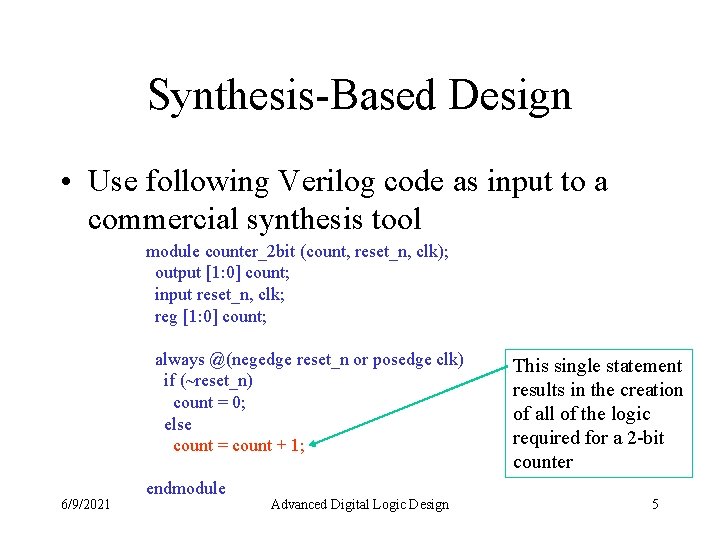

Synthesis-Based Design • Use following Verilog code as input to a commercial synthesis tool module counter_2 bit (count, reset_n, clk); output [1: 0] count; input reset_n, clk; reg [1: 0] count; always @(negedge reset_n or posedge clk) if (~reset_n) count = 0; else count = count + 1; 6/9/2021 endmodule Advanced Digital Logic Design This single statement results in the creation of all of the logic required for a 2 -bit counter 5

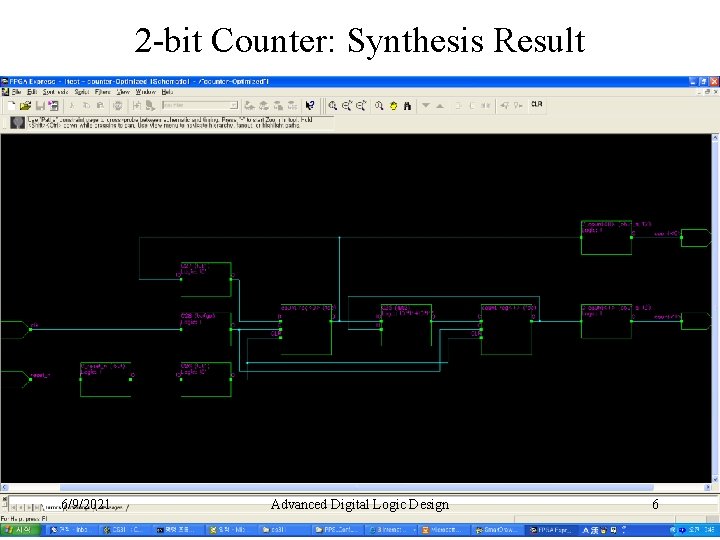

2 -bit Counter: Synthesis Result 6/9/2021 Advanced Digital Logic Design 6

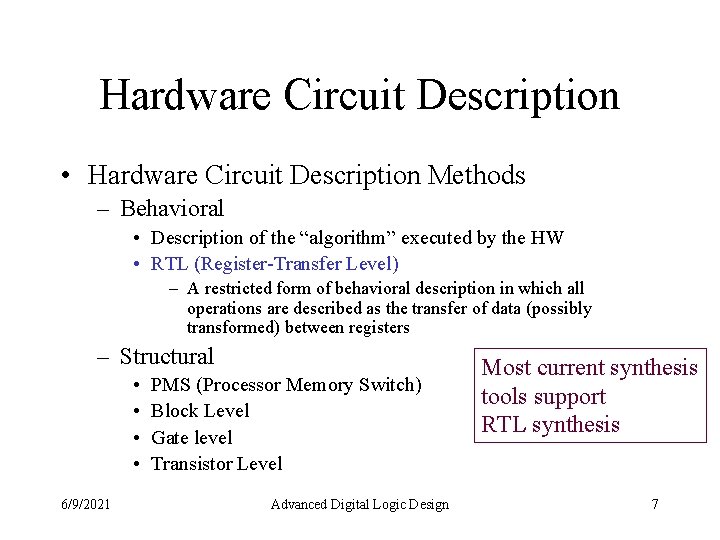

Hardware Circuit Description • Hardware Circuit Description Methods – Behavioral • Description of the “algorithm” executed by the HW • RTL (Register-Transfer Level) – A restricted form of behavioral description in which all operations are described as the transfer of data (possibly transformed) between registers – Structural • • 6/9/2021 PMS (Processor Memory Switch) Block Level Gate level Transistor Level Advanced Digital Logic Design Most current synthesis tools support RTL synthesis 7

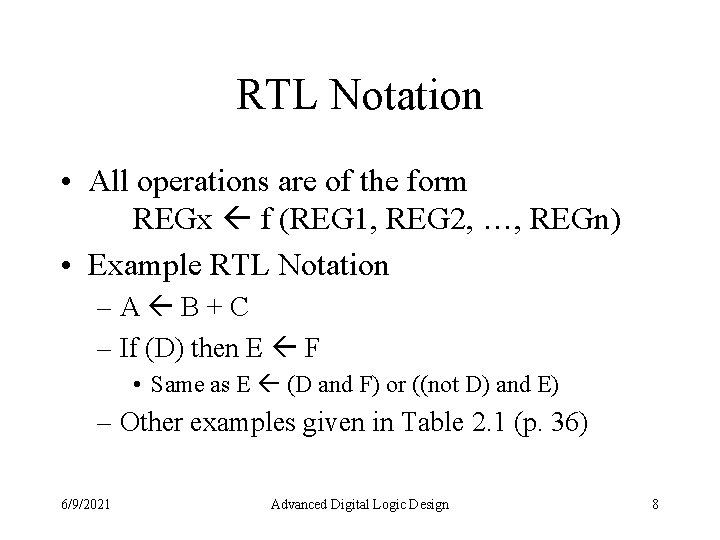

RTL Notation • All operations are of the form REGx f (REG 1, REG 2, …, REGn) • Example RTL Notation –A B+C – If (D) then E F • Same as E (D and F) or ((not D) and E) – Other examples given in Table 2. 1 (p. 36) 6/9/2021 Advanced Digital Logic Design 8

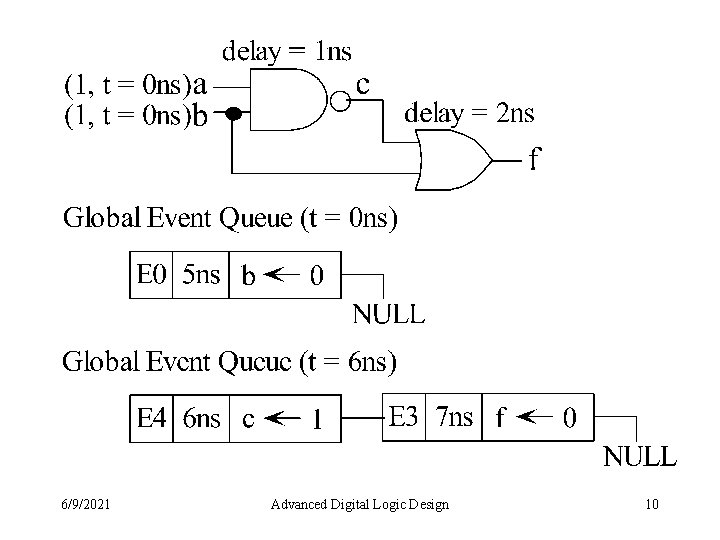

Logic Simulation • How is HDL code simulated? • Simulation Methods – Time-driven simulation • Global clock progresses at steady rate • Events are simulated when its “execution time” arrives – Event-driven simulation (discrete event simulation) • Method used by most logic simulation tools • Based on a global queue of time-ordered events • Time progresses according to the time of the event at the head of the global event queue 6/9/2021 Advanced Digital Logic Design 9

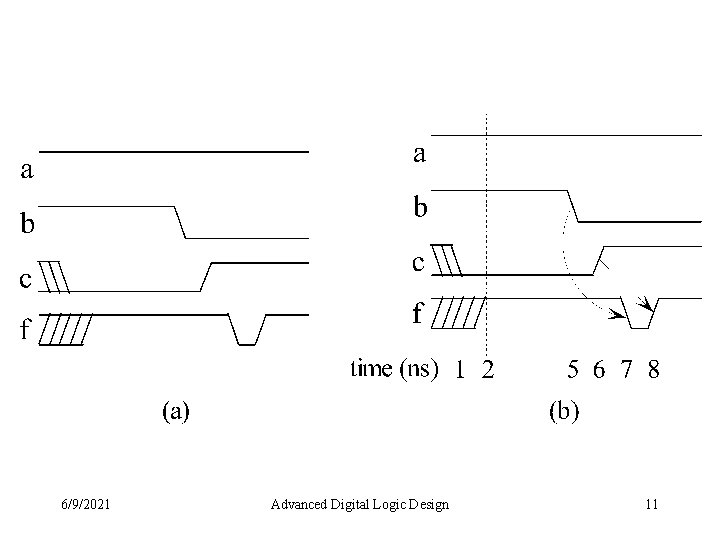

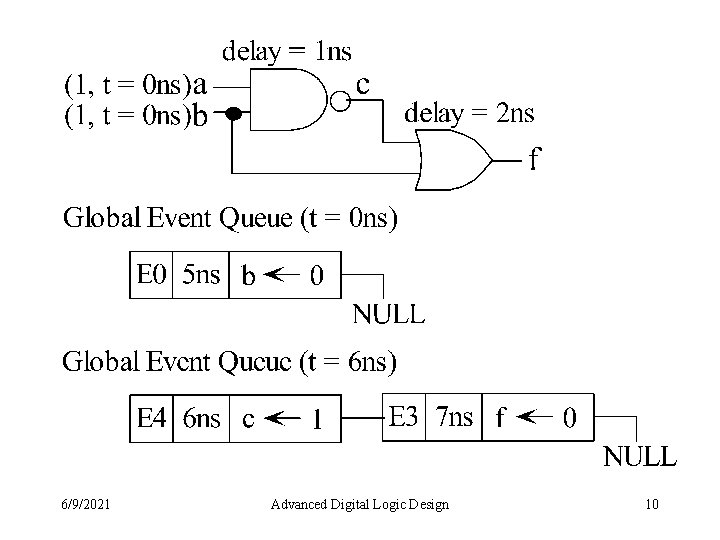

6/9/2021 Advanced Digital Logic Design 10

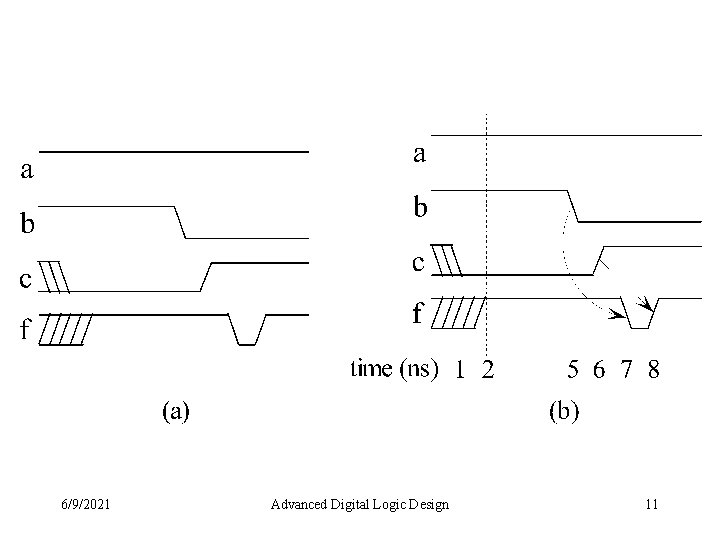

6/9/2021 Advanced Digital Logic Design 11

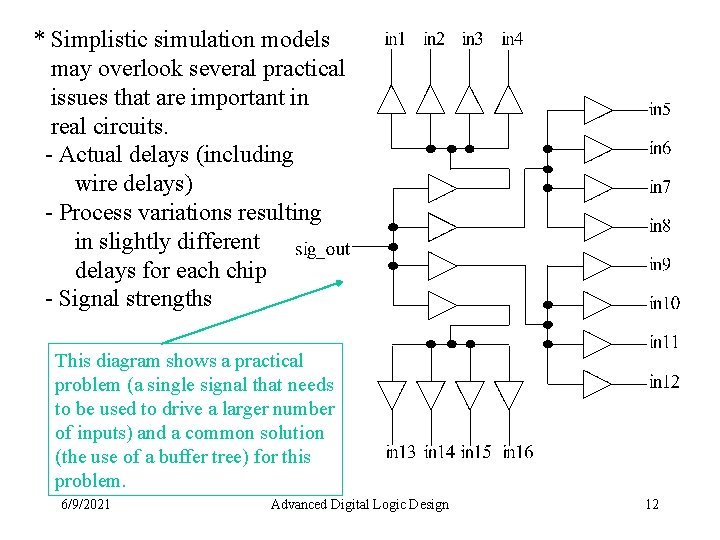

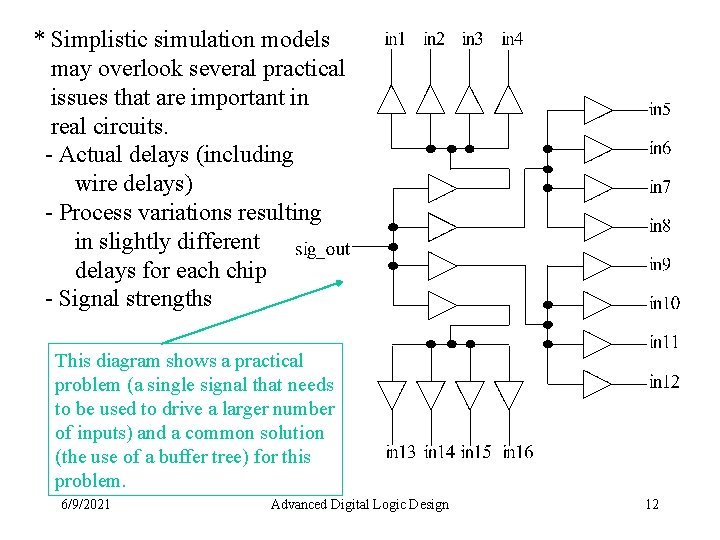

* Simplistic simulation models may overlook several practical issues that are important in real circuits. - Actual delays (including wire delays) - Process variations resulting in slightly different delays for each chip - Signal strengths This diagram shows a practical problem (a single signal that needs to be used to drive a larger number of inputs) and a common solution (the use of a buffer tree) for this problem. 6/9/2021 Advanced Digital Logic Design 12