Ch 2 1 VHDL Introduction 1 VHDL 2

- Slides: 14

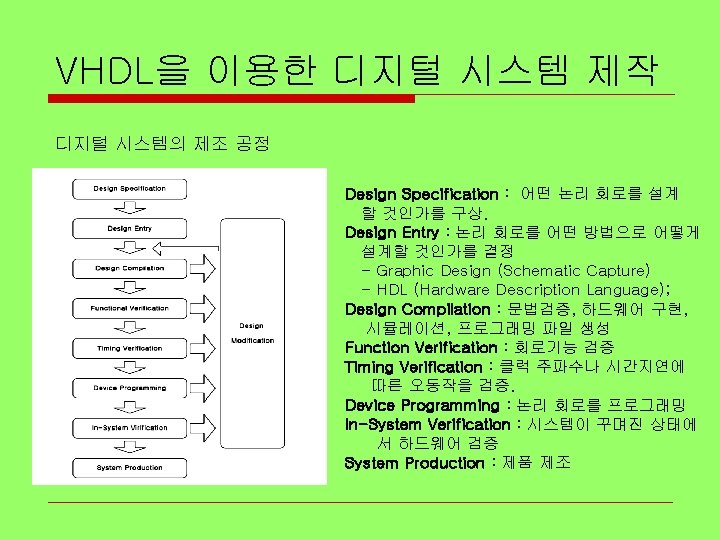

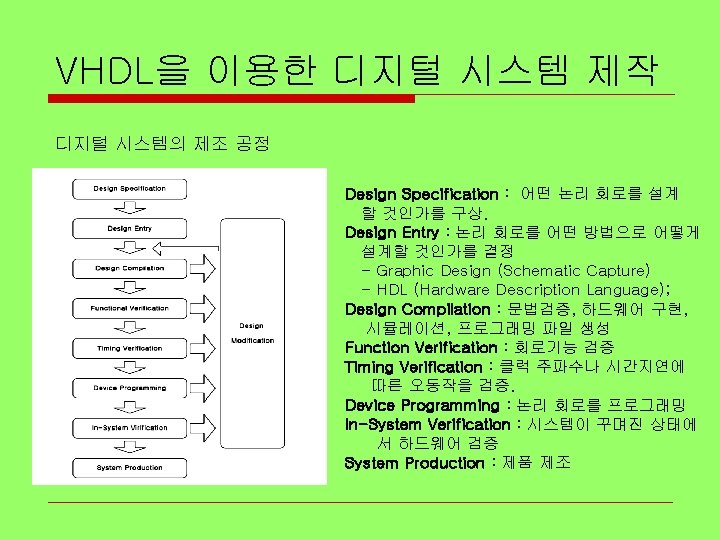

Ch 2 -1. VHDL Introduction 1. VHDL 정의 2. VHDL의 역사 3. VHDL의 장점 4. HDL의 종류 5. VHDL 모델링 6. VHDL in MAX-Plus. II

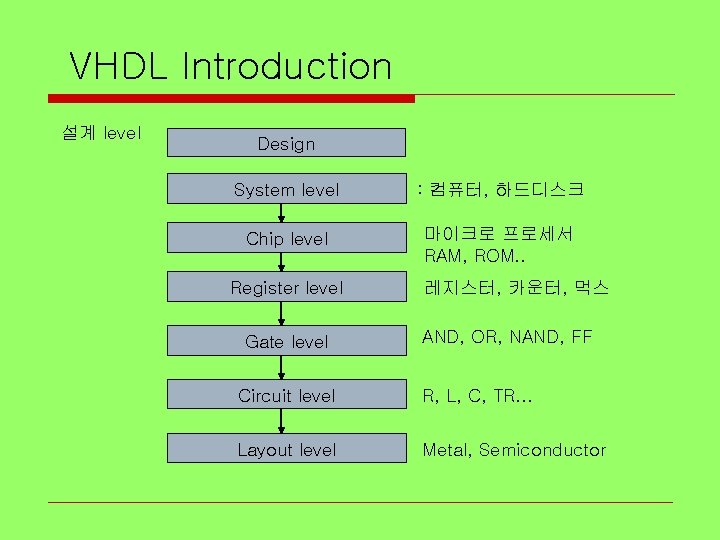

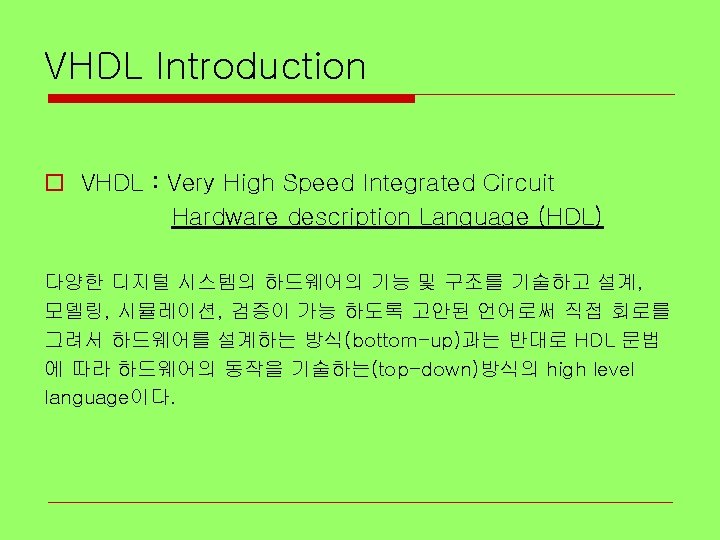

VHDL Introduction 설계 level Design System level : 컴퓨터, 하드디스크 Chip level 마이크로 프로세서 RAM, ROM. . Register level Gate level 레지스터, 카운터, 먹스 AND, OR, NAND, FF Circuit level R, L, C, TR… Layout level Metal, Semiconductor

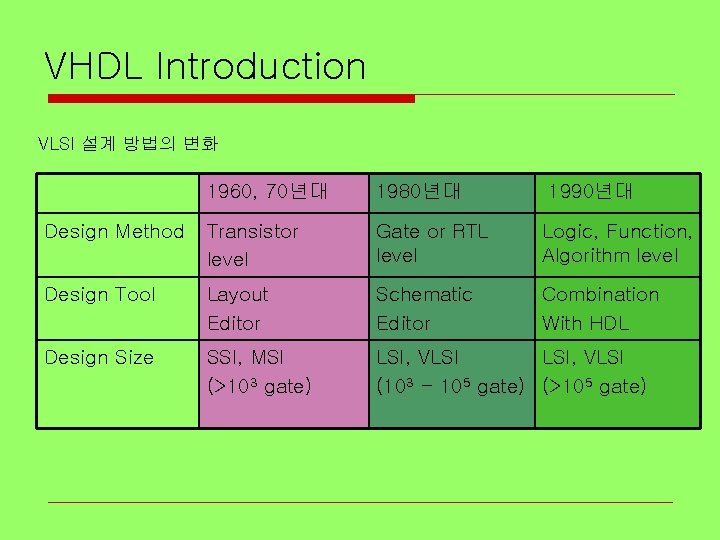

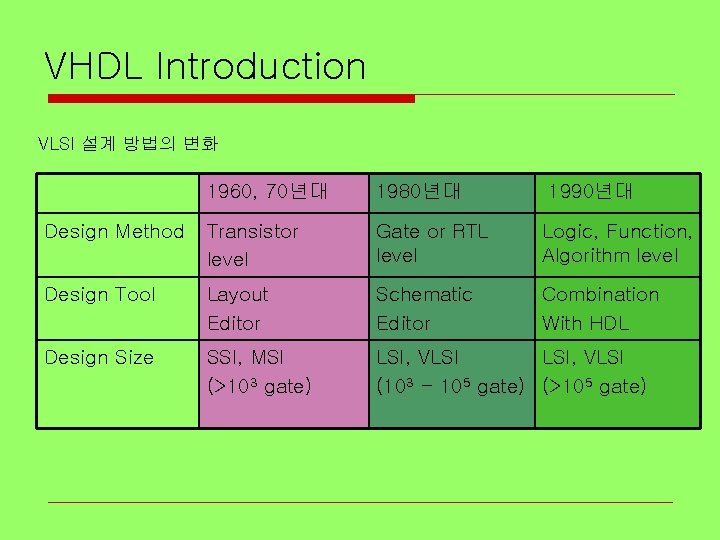

VHDL Introduction VLSI 설계 방법의 변화 1960, 70년대 1980년대 1990년대 Design Method Transistor level Gate or RTL level Logic, Function, Algorithm level Design Tool Layout Editor Schematic Editor Combination With HDL Design Size SSI, MSI (>103 gate) LSI, VLSI (103 - 105 gate) (>105 gate)

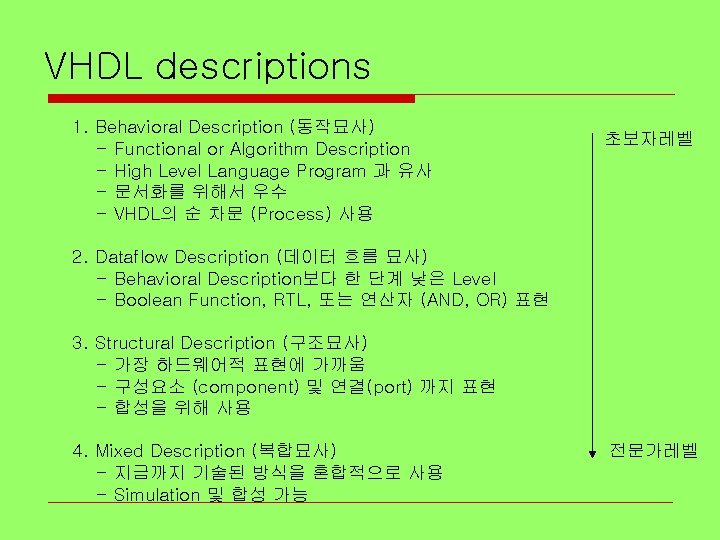

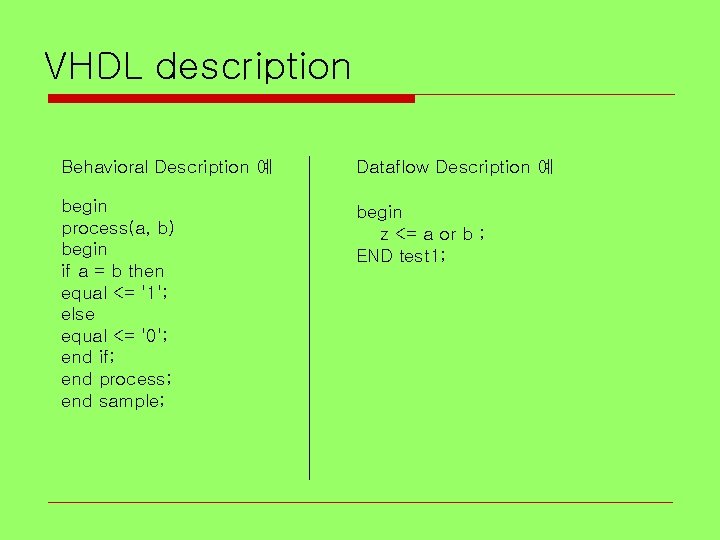

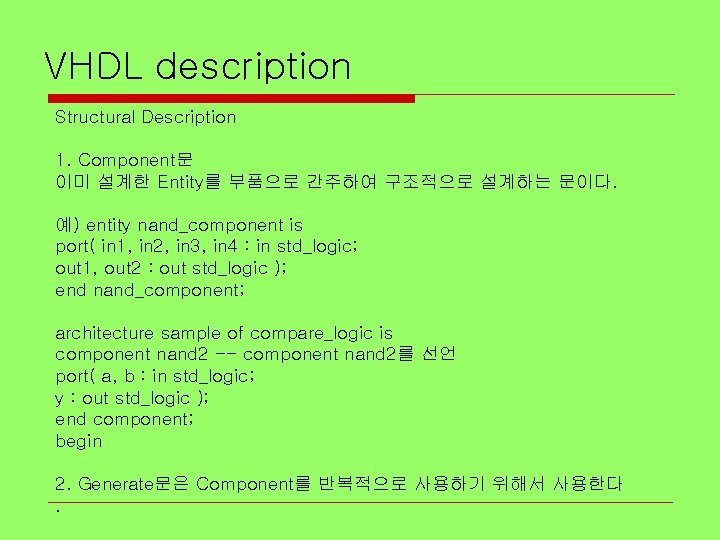

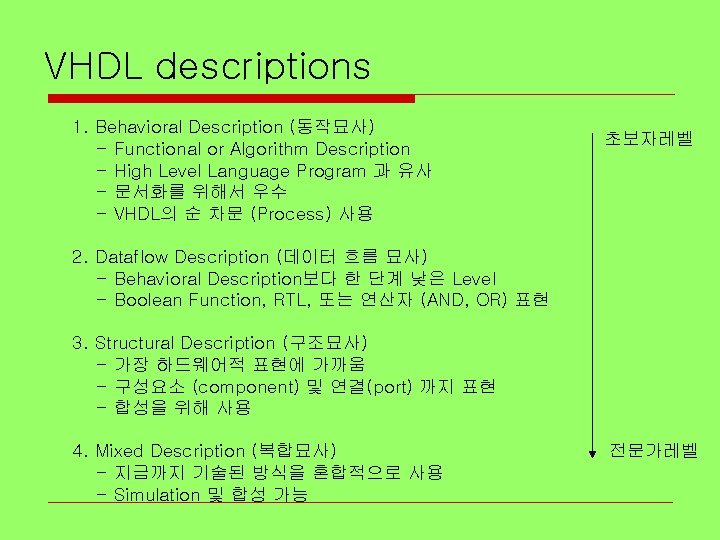

VHDL descriptions 1. Behavioral Description (동작묘사) - Functional or Algorithm Description - High Level Language Program 과 유사 - 문서화를 위해서 우수 - VHDL의 순 차문 (Process) 사용 초보자레벨 2. Dataflow Description (데이터 흐름 묘사) - Behavioral Description보다 한 단계 낮은 Level - Boolean Function, RTL, 또는 연산자 (AND, OR) 표현 3. Structural Description (구조묘사) - 가장 하드웨어적 표현에 가까움 - 구성요소 (component) 및 연결(port) 까지 표현 - 합성을 위해 사용 4. Mixed Description (복합묘사) - 지금까지 기술된 방식을 혼합적으로 사용 - Simulation 및 합성 가능 전문가레벨

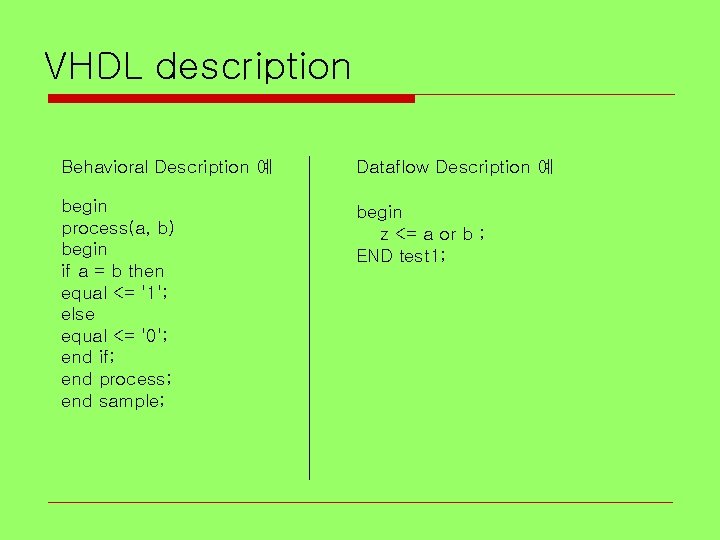

VHDL description Behavioral Description 예 Dataflow Description 예 begin process(a, b) begin if a = b then equal <= '1'; else equal <= '0'; end if; end process; end sample; begin z <= a or b ; END test 1;

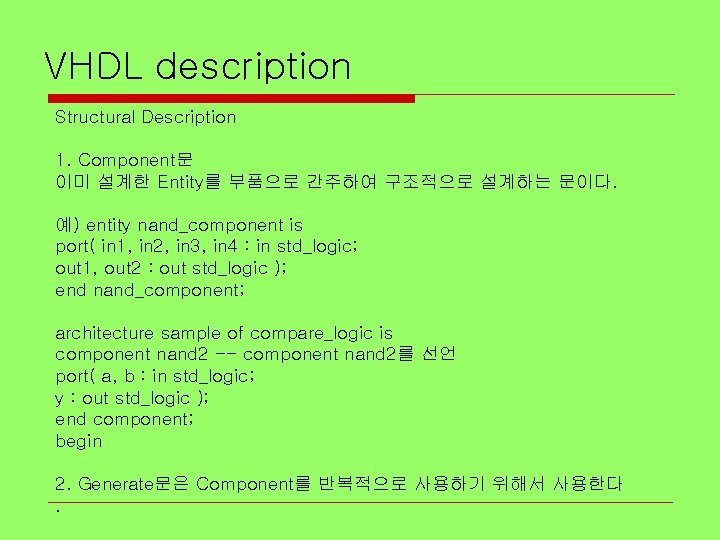

VHDL description Structural Description 1. Component문 이미 설계한 Entity를 부품으로 간주하여 구조적으로 설계하는 문이다. 예) entity nand_component is port( in 1, in 2, in 3, in 4 : in std_logic; out 1, out 2 : out std_logic ); end nand_component; architecture sample of compare_logic is component nand 2 -- component nand 2를 선언 port( a, b : in std_logic; y : out std_logic ); end component; begin 2. Generate문은 Component를 반복적으로 사용하기 위해서 사용한다.

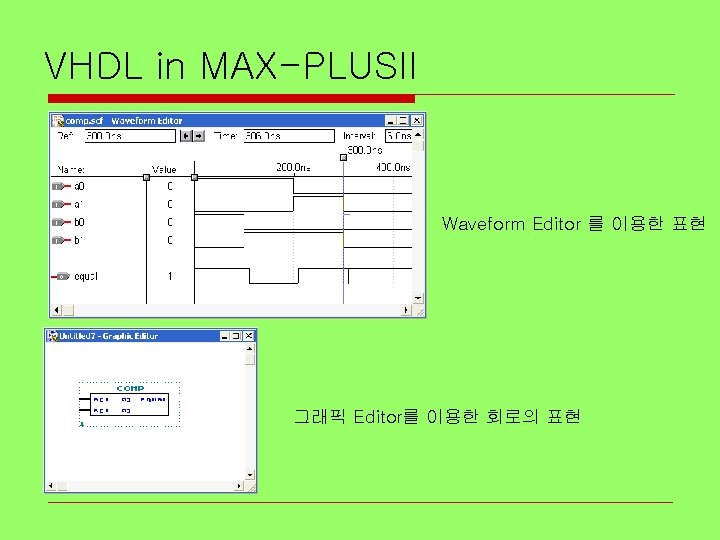

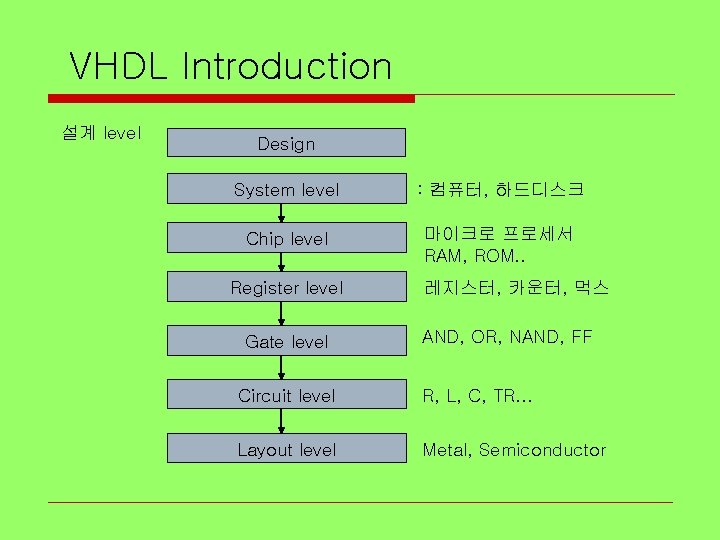

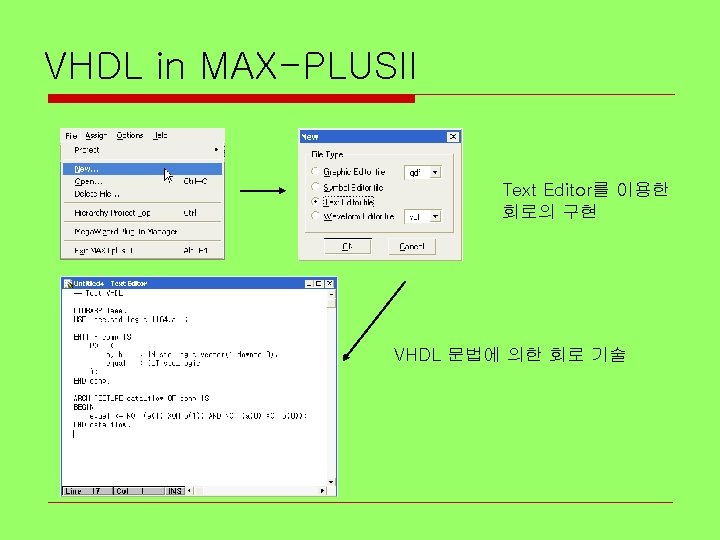

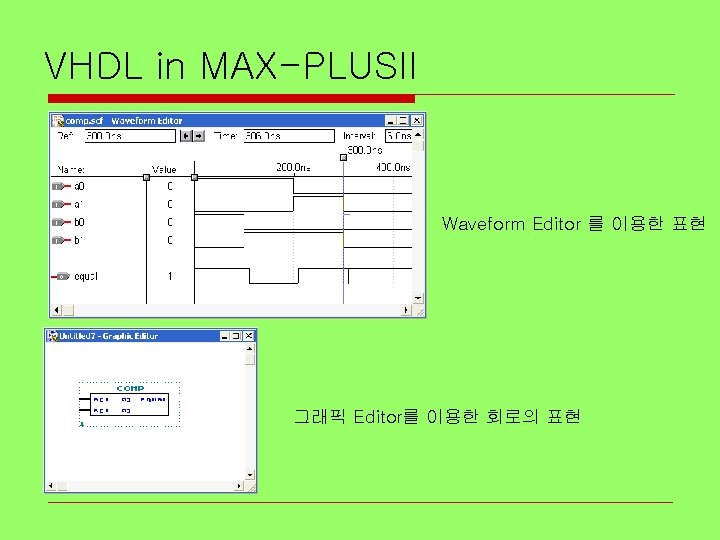

VHDL in MAX-PLUSII Waveform Editor 를 이용한 표현 그래픽 Editor를 이용한 회로의 표현

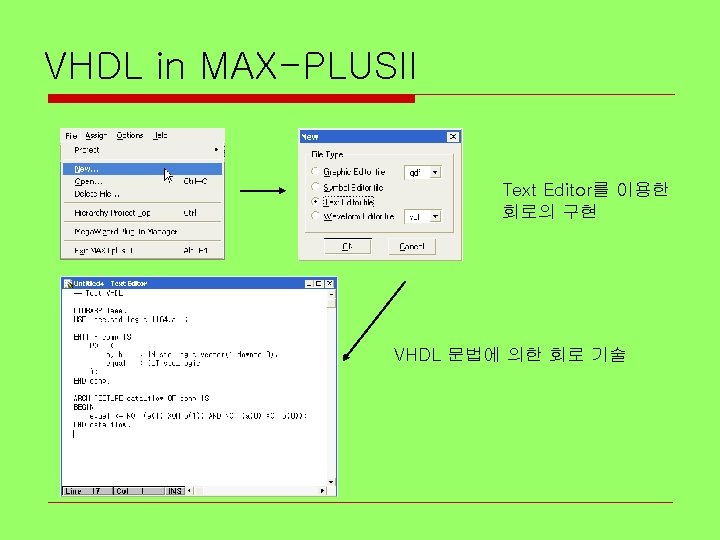

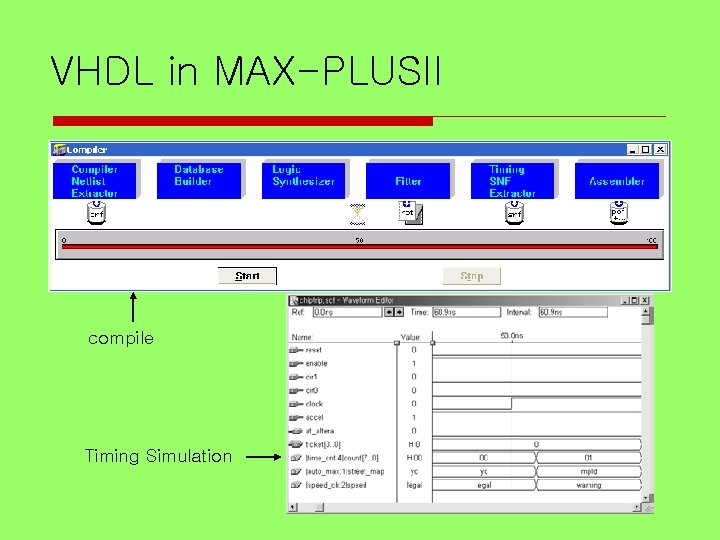

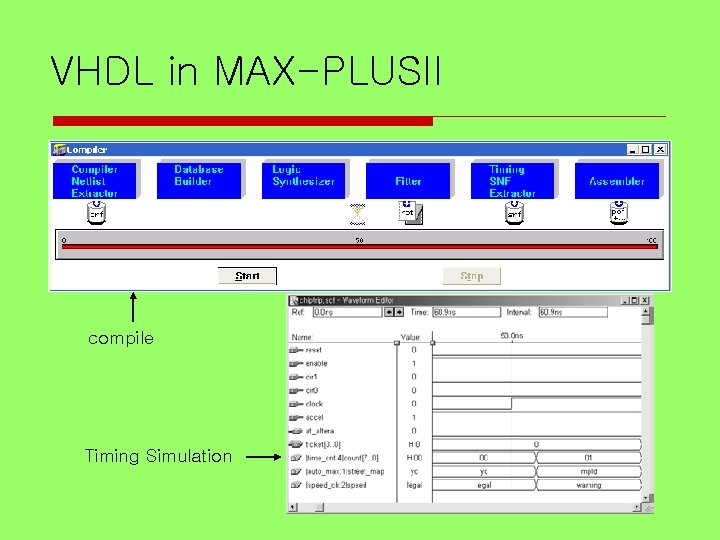

VHDL in MAX-PLUSII compile Timing Simulation