Ch 11 Bipolar Transistors and Digital Circuits 2

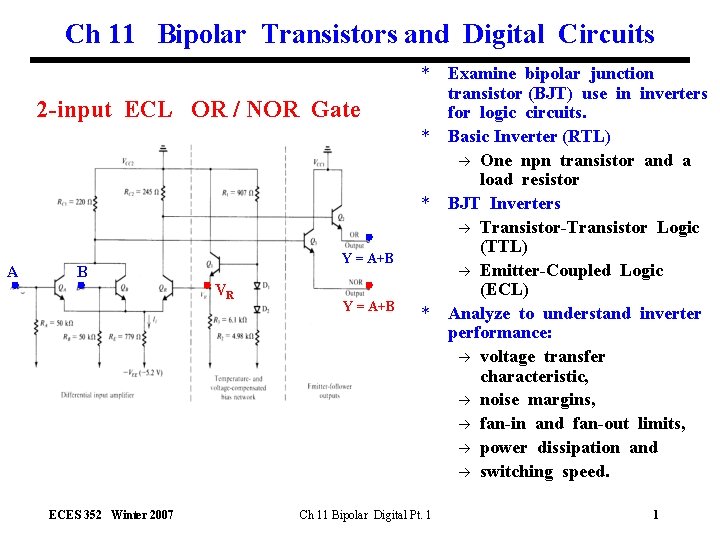

Ch 11 Bipolar Transistors and Digital Circuits 2 -input ECL OR / NOR Gate A Y = A+B B VR ECES 352 Winter 2007 Y = A+B * Examine bipolar junction transistor (BJT) use in inverters for logic circuits. * Basic Inverter (RTL) à One npn transistor and a load resistor * BJT Inverters à Transistor-Transistor Logic (TTL) à Emitter-Coupled Logic (ECL) * Analyze to understand inverter performance: à voltage transfer characteristic, à noise margins, à fan-in and fan-out limits, à power dissipation and à switching speed. Ch 11 Bipolar Digital Pt. 1 1

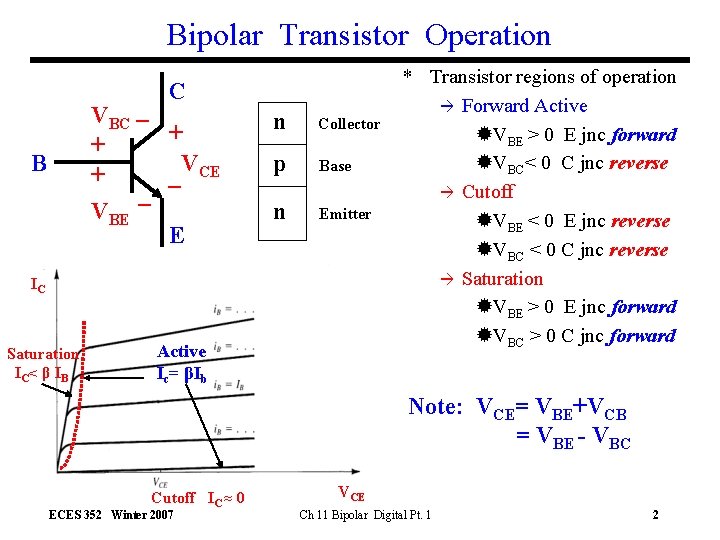

Bipolar Transistor Operation C VBC _ + + + _VCE _ VBE E B n Collector p Base n Emitter IC Saturation I C< β I B Active Ic= βIb * Transistor regions of operation à Forward Active ®VBE > 0 E jnc forward ®VBC< 0 C jnc reverse à Cutoff ®VBE < 0 E jnc reverse ®VBC < 0 C jnc reverse à Saturation ®VBE > 0 E jnc forward ®VBC > 0 C jnc forward Note: VCE= VBE+VCB = VBE - VBC Cutoff IC ≈ 0 ECES 352 Winter 2007 VCE Ch 11 Bipolar Digital Pt. 1 2

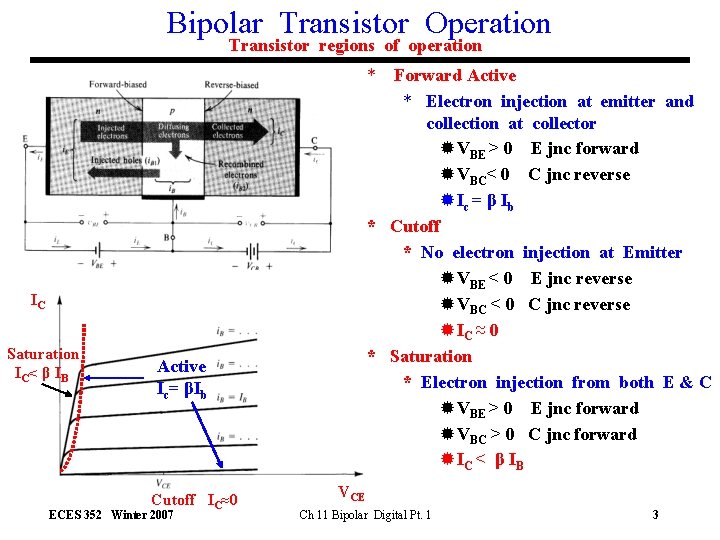

Bipolar Transistor Operation Transistor regions of operation * Forward Active * Electron injection at emitter and collection at collector ® VBE > 0 E jnc forward ® VBC< 0 C jnc reverse ® Ic = β Ib * Cutoff * No electron injection at Emitter ® VBE < 0 E jnc reverse ® VBC < 0 C jnc reverse ® IC ≈ 0 * Saturation * Electron injection from both E & C ® VBE > 0 E jnc forward ® VBC > 0 C jnc forward ® IC < β IB IC Saturation I C< β I B Active Ic= βIb Cutoff IC≈0 ECES 352 Winter 2007 VCE Ch 11 Bipolar Digital Pt. 1 3

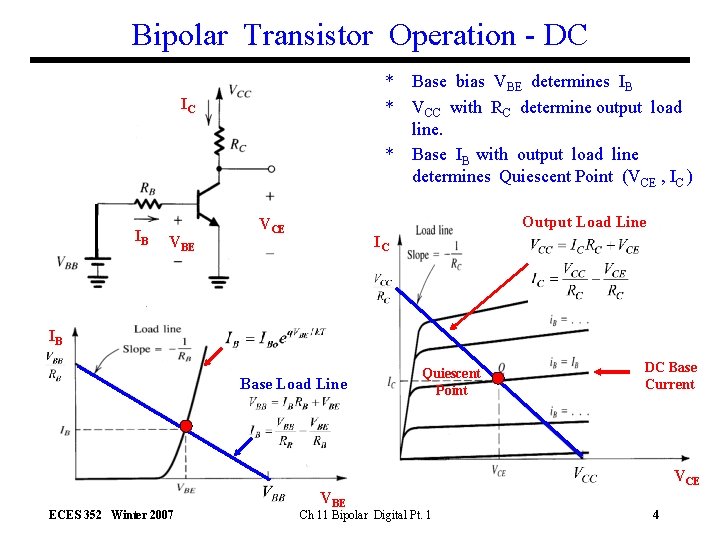

Bipolar Transistor Operation - DC * Base bias VBE determines IB * VCC with RC determine output load line. * Base IB with output load line determines Quiescent Point (VCE , IC ) IC IB VBE Output Load Line VCE IC IB Base Load Line Quiescent Point DC Base Current VCE ECES 352 Winter 2007 VBE Ch 11 Bipolar Digital Pt. 1 4

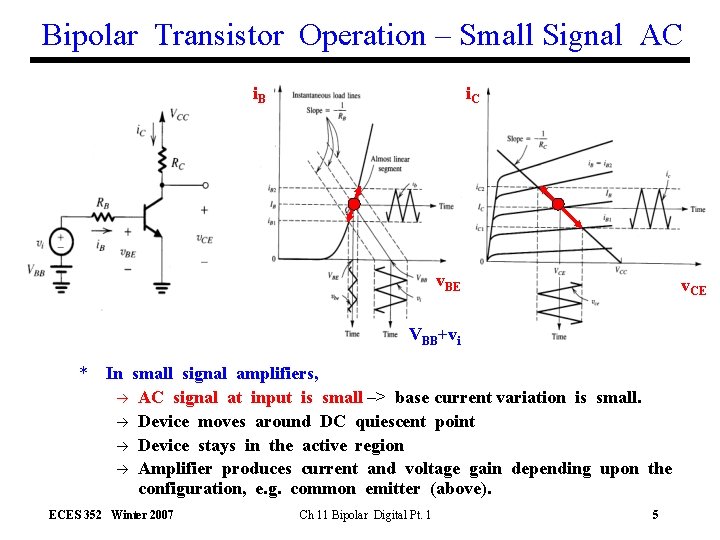

Bipolar Transistor Operation – Small Signal AC i. B i. C v. BE v. CE VBB+vi * In small signal amplifiers, à AC signal at input is small –> base current variation is small. à Device moves around DC quiescent point à Device stays in the active region à Amplifier produces current and voltage gain depending upon the configuration, e. g. common emitter (above). ECES 352 Winter 2007 Ch 11 Bipolar Digital Pt. 1 5

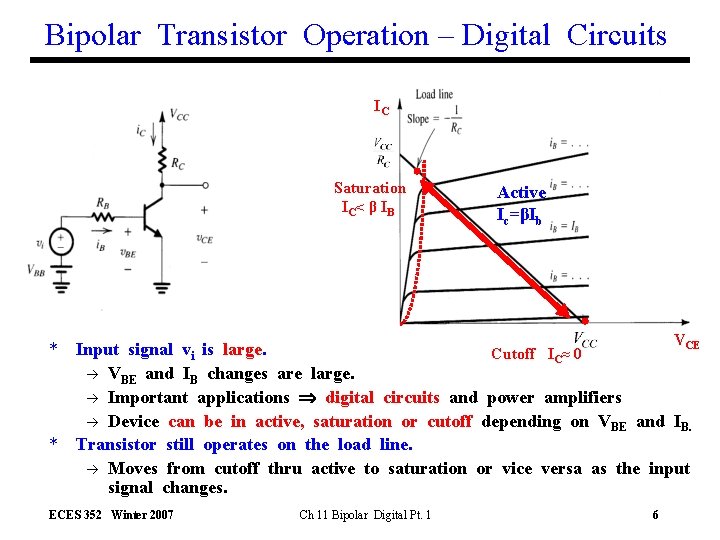

Bipolar Transistor Operation – Digital Circuits IC Saturation I C< β I B Active Ic=βIb V CE * Input signal vi is large. Cutoff IC≈ 0 à VBE and IB changes are large. à Important applications digital circuits and power amplifiers à Device can be in active, saturation or cutoff depending on VBE and IB. * Transistor still operates on the load line. à Moves from cutoff thru active to saturation or vice versa as the input signal changes. ECES 352 Winter 2007 Ch 11 Bipolar Digital Pt. 1 6

Bipolar Transistor Operation - Characteristics * IC Saturation I C< β I B * ~ 0. 2 V IB * Active Ic= βIb VCE Cutoff IC 0 0. 7 V 0. 8 V ECES 352 Winter 2007 VBE * Each region of device operation has its own unique characteristics Active à Current gain Ic= β Ib à VBE = VBE, active ≈ 0. 7 V (typical value) à VCE, active ≈ ? , NO typical value! Saturation à Reduced current gain IC< β IB à VBE = VBE, sat ≈ 0. 8 V (typical value) à VCE = VCE, sat ≈ 0. 2 V (typical value) Cutoff à No current gain IC ≈ 0, IB ≈ 0 à VBE < O à VCE, cutoff ≈ ? , NO typical value! Ch 11 Bipolar Digital Pt. 1 7

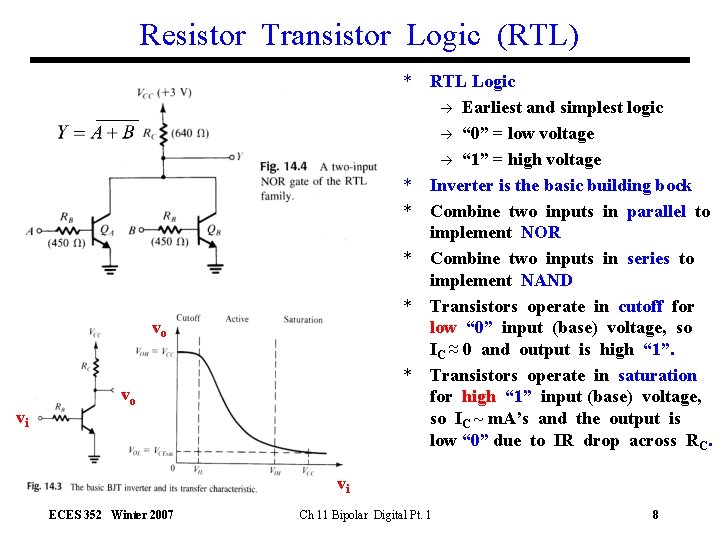

Resistor Transistor Logic (RTL) * RTL Logic à Earliest and simplest logic à “ 0” = low voltage à “ 1” = high voltage * Inverter is the basic building bock * Combine two inputs in parallel to implement NOR * Combine two inputs in series to implement NAND * Transistors operate in cutoff for low “ 0” input (base) voltage, so IC ≈ 0 and output is high “ 1”. * Transistors operate in saturation for high “ 1” input (base) voltage, so IC ~ m. A’s and the output is low “ 0” due to IR drop across RC. vo vi ECES 352 Winter 2007 Ch 11 Bipolar Digital Pt. 1 8

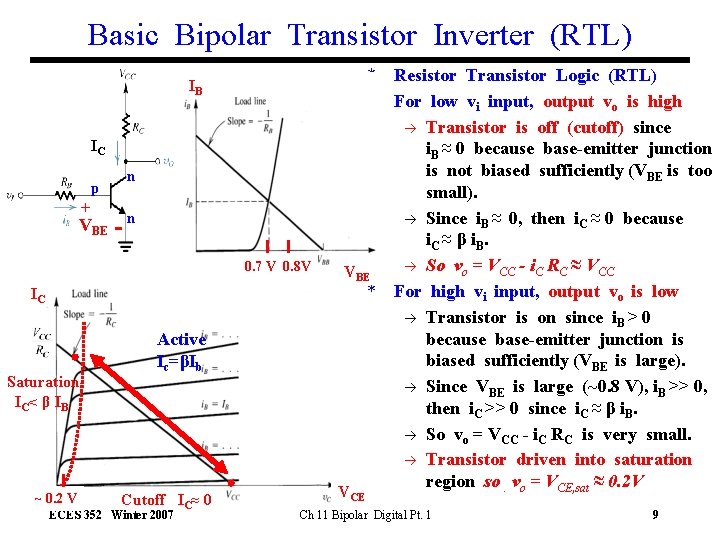

Basic Bipolar Transistor Inverter (RTL) IB IC p + VBE n n 0. 7 V 0. 8 V IC Saturation I C< β I B ~ 0. 2 V Active Ic=βIb Cutoff IC≈ 0 ECES 352 Winter 2007 * Resistor Transistor Logic (RTL) * For low vi input, output vo is high à Transistor is off (cutoff) since i. B ≈ 0 because base-emitter junction is not biased sufficiently (VBE is too small). à Since i. B ≈ 0, then i. C ≈ 0 because i. C ≈ β i. B. à So vo = VCC - i. C RC ≈ VCC VBE * For high vi input, output vo is low à Transistor is on since i. B > 0 because base-emitter junction is biased sufficiently (VBE is large). à Since VBE is large (~0. 8 V), i. B >> 0, then i. C >> 0 since i. C ≈ β i. B. à So vo = VCC - i. C RC is very small. à Transistor driven into saturation region so. vo = VCE, sat ≈ 0. 2 V VCE Ch 11 Bipolar Digital Pt. 1 9

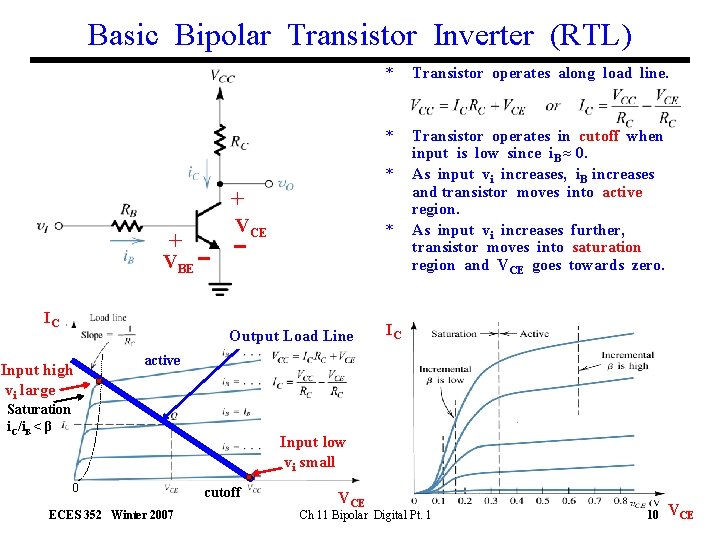

Basic Bipolar Transistor Inverter (RTL) * Transistor operates along load line. * Transistor operates in cutoff when input is low since i. B ≈ 0. As input vi increases, i. B increases and transistor moves into active region. As input vi increases further, transistor moves into saturation region and VCE goes towards zero. * + + VCE * VBE IC Output Load Line Input high vi large IC active Saturation i. C/i. B < β Input low vi small 0 ECES 352 Winter 2007 cutoff VCE Ch 11 Bipolar Digital Pt. 1 10 VCE

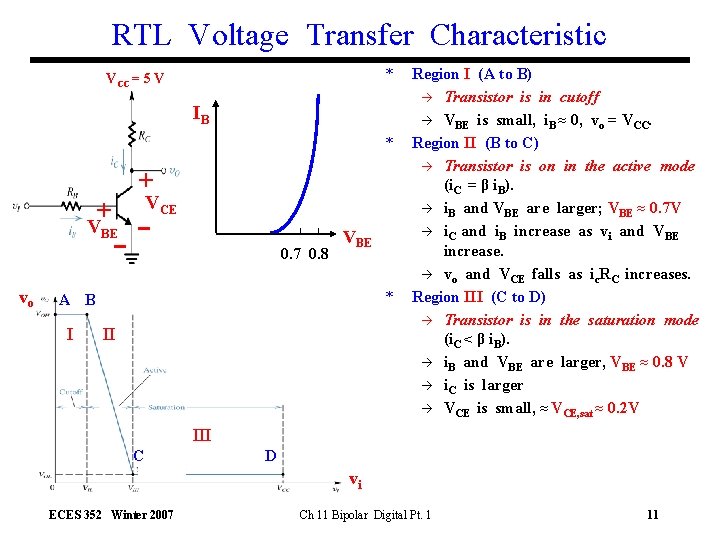

RTL Voltage Transfer Characteristic * VCC = 5 V IB * + VCE + VBE 0. 7 0. 8 vo VBE * A B I II Region I (A to B) à Transistor is in cutoff à VBE is small, i. B ≈ 0, vo = VCC. Region II (B to C) à Transistor is on in the active mode (i. C = β i. B). à i. B and VBE are larger; VBE ≈ 0. 7 V à i. C and i. B increase as vi and VBE increase. à vo and VCE falls as ic. RC increases. Region III (C to D) à Transistor is in the saturation mode (i. C < β i. B). à i. B and VBE are larger, VBE ≈ 0. 8 V à i. C is larger à VCE is small, ≈ VCE, sat ≈ 0. 2 V III C D vi ECES 352 Winter 2007 Ch 11 Bipolar Digital Pt. 1 11

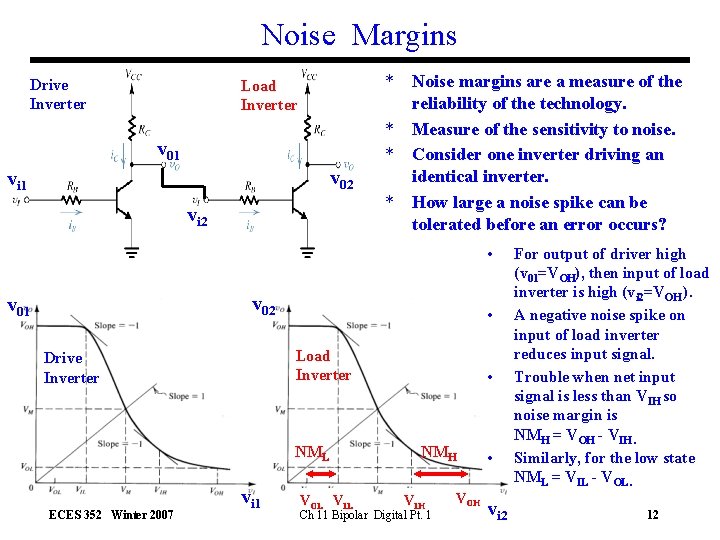

Noise Margins Drive Inverter Load Inverter v 01 v 02 vi 1 vi 2 * Noise margins are a measure of the reliability of the technology. * Measure of the sensitivity to noise. * Consider one inverter driving an identical inverter. * How large a noise spike can be tolerated before an error occurs? • v 02 v 01 • Load Inverter Drive Inverter NML ECES 352 Winter 2007 vi 1 VOL VIL • NMH VIH Ch 11 Bipolar Digital Pt. 1 • VOH vi 2 For output of driver high (v 01=VOH), then input of load inverter is high (vi 2=VOH ). A negative noise spike on input of load inverter reduces input signal. Trouble when net input signal is less than VIH so noise margin is NMH = VOH - VIH. Similarly, for the low state NML = VIL - VOL. 12

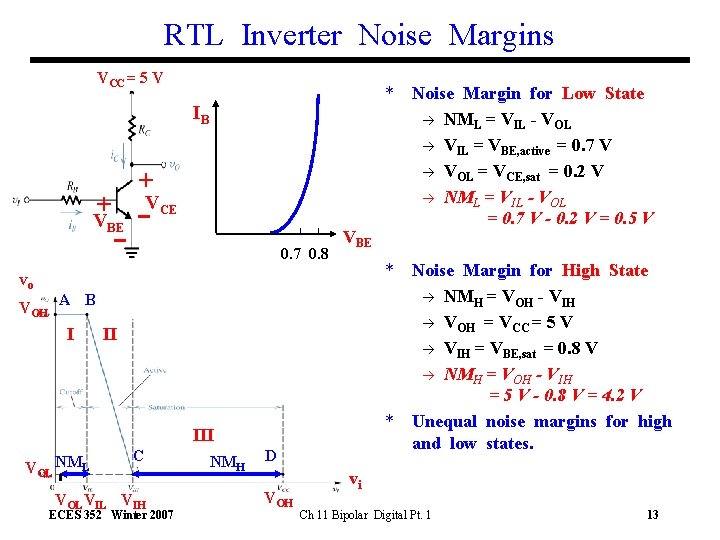

RTL Inverter Noise Margins VCC = 5 V IB + + VCE VBE 0. 7 0. 8 vo VOH VBE * Noise Margin for High State à NMH = VOH - VIH à VOH = VCC = 5 V à VIH = VBE, sat = 0. 8 V à NMH = VOH - VIH = 5 V - 0. 8 V = 4. 2 V * Unequal noise margins for high and low states. A B I II III VOL NML C VOL VIH ECES 352 Winter 2007 NMH D VOH * Noise Margin for Low State à NML = VIL - VOL à VIL = VBE, active = 0. 7 V à VOL = VCE, sat = 0. 2 V à NML = VIL - VOL = 0. 7 V - 0. 2 V = 0. 5 V vi Ch 11 Bipolar Digital Pt. 1 13

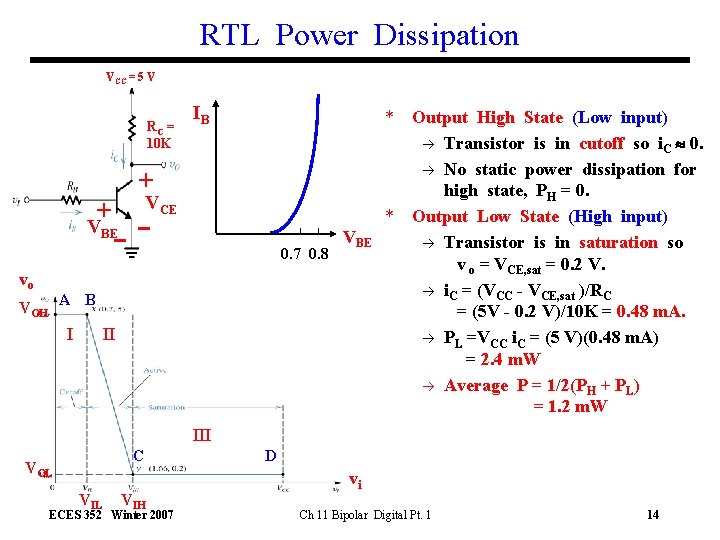

RTL Power Dissipation VCC = 5 V RC = 10 K IB + VCE + VBE 0. 7 0. 8 vo VBE A B VOH I II * Output High State (Low input) à Transistor is in cutoff so i. C 0. à No static power dissipation for high state, PH = 0. * Output Low State (High input) à Transistor is in saturation so v o = VCE, sat = 0. 2 V. à i. C = (VCC - VCE, sat )/RC = (5 V - 0. 2 V)/10 K = 0. 48 m. A. à PL =VCC i. C = (5 V)(0. 48 m. A) = 2. 4 m. W à Average P = 1/2(PH + PL) = 1. 2 m. W III C VOL VIH ECES 352 Winter 2007 D vi Ch 11 Bipolar Digital Pt. 1 14

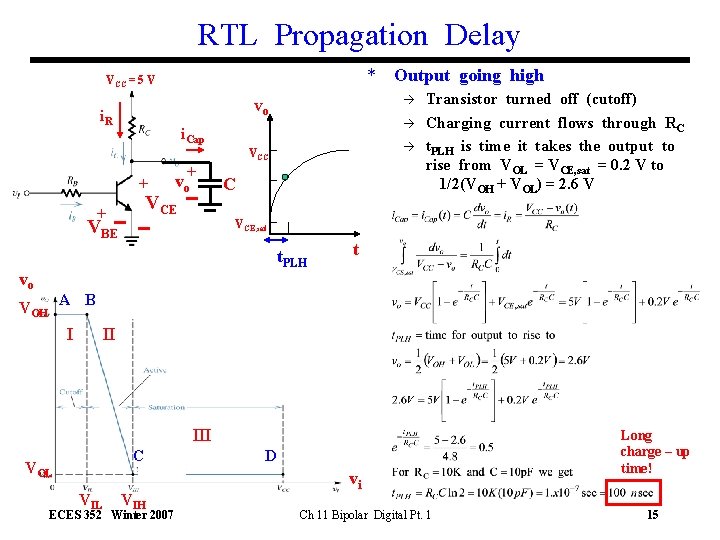

RTL Propagation Delay * Output going high VCC = 5 V à vo i. R à i. Cap + + vo VCE + VBE à VCC C VCE, sat t. PLH vo Transistor turned off (cutoff) Charging current flows through RC t. PLH is time it takes the output to rise from VOL = VCE, sat = 0. 2 V to 1/2(VOH + VOL) = 2. 6 V t A B VOH I II III C VOL VIH ECES 352 Winter 2007 D vi Ch 11 Bipolar Digital Pt. 1 Long charge – up time! 15

RTL Propagation Delay * Output going high VCC=5 V à vo i. R à i. Cap + + vo VCE + à VCC C VCE, sat VBE t. PLH vo Transistor turned off (cutoff) (M N) Charging current flows through RC t. PLH is time it takes the output to rise from VOL = VCE, sat = 0. 2 V to 1/2(VOH + VOL) = 2. 6 V (N O) t Transient Response M N O A B VOH I IC II M III C VOL VIH ECES 352 Winter 2007 D vi P N Ch 11 Bipolar Digital Pt. 1 O 16 VCE

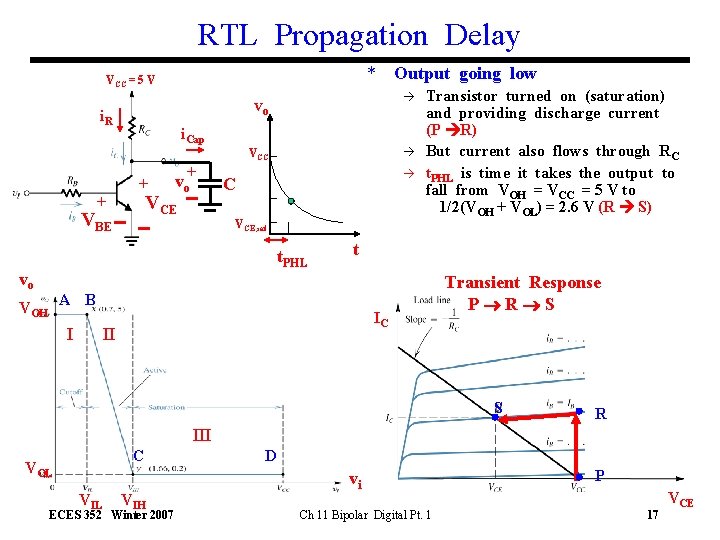

RTL Propagation Delay * Output going low VCC = 5 V i. R + vo à VCC à i. Cap + + vo VCE VBE à C VCE, sat t. PHL vo Transistor turned on (saturation) and providing discharge current (P R) But current also flows through RC t. PHL is time it takes the output to fall from VOH = VCC = 5 V to 1/2(VOH + VOL) = 2. 6 V (R S) t A B VOH I IC II Transient Response P R S S R III C VOL VIH ECES 352 Winter 2007 D vi Ch 11 Bipolar Digital Pt. 1 P 17 VCE

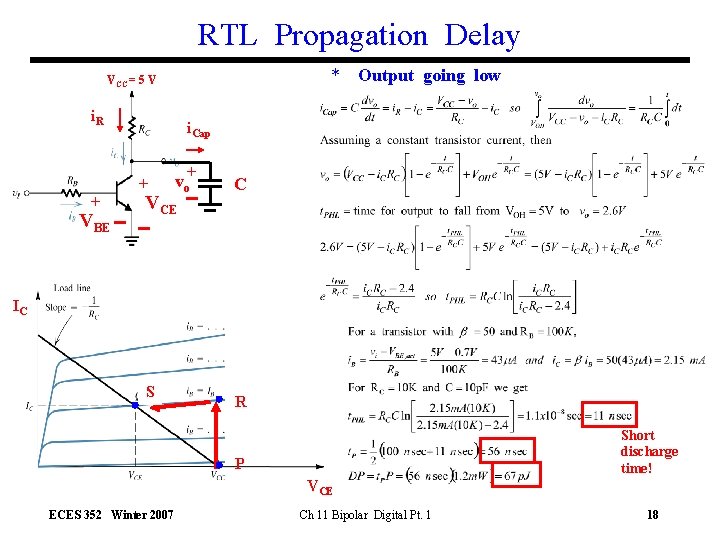

RTL Propagation Delay * Output going low VCC = 5 V i. R + VBE i. Cap + + vo VCE C IC S R Short discharge time! P VCE ECES 352 Winter 2007 Ch 11 Bipolar Digital Pt. 1 18

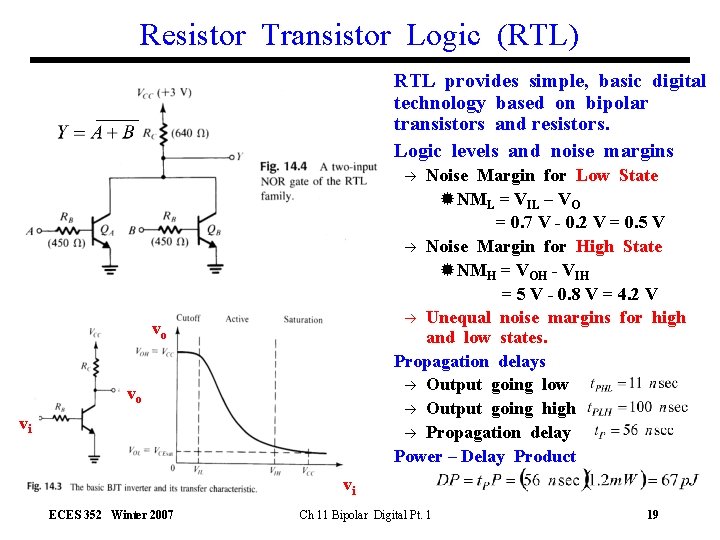

Resistor Transistor Logic (RTL) * RTL provides simple, basic digital technology based on bipolar transistors and resistors. • Logic levels and noise margins Noise Margin for Low State ® NML = VIL – VO = 0. 7 V - 0. 2 V = 0. 5 V à Noise Margin for High State ® NMH = VOH - VIH = 5 V - 0. 8 V = 4. 2 V à Unequal noise margins for high and low states. * Propagation delays à Output going low à Output going high à Propagation delay * Power – Delay Product à vo vo vi vi ECES 352 Winter 2007 Ch 11 Bipolar Digital Pt. 1 19

- Slides: 19