CENTRE UNIVERSITAIRE DE MILA INSTITUT DES SCIENCES ET

- Slides: 36

CENTRE UNIVERSITAIRE DE MILA INSTITUT DES SCIENCES ET DE LA TECHNOLOGIE 1 ere année MI Architecture des ordinateurs Chapitre 04 Les circuits séquentiels

PLAN Introduction Bascules Registres Compteurs DU CHAPITRE 2

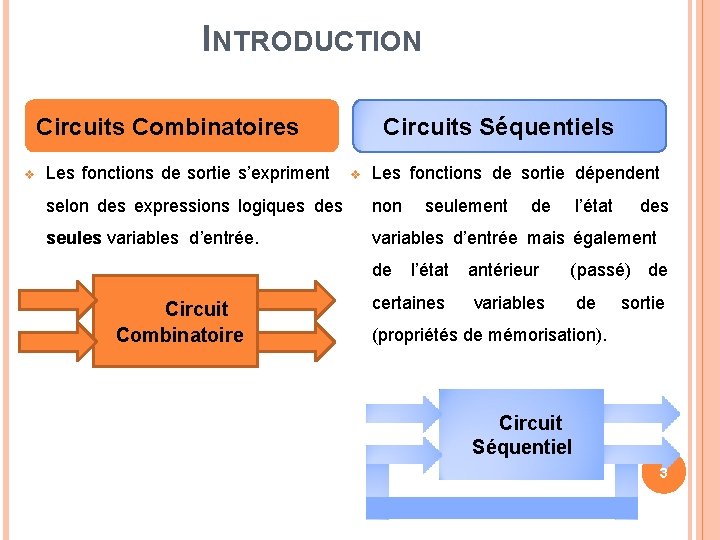

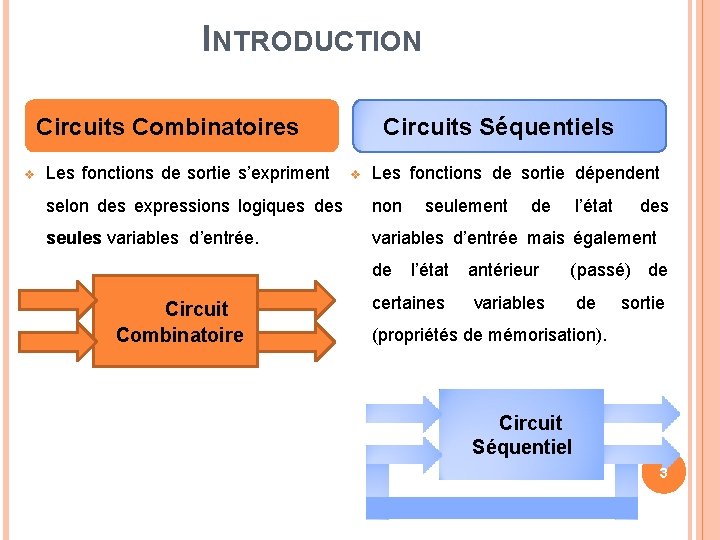

INTRODUCTION Circuits Combinatoires Les fonctions de sortie s’expriment Circuits Séquentiels Les fonctions de sortie dépendent selon des expressions logiques des non seules variables d’entrée mais également de Circuit Combinatoire seulement l’état certaines de l’état des antérieur (passé) de variables de sortie (propriétés de mémorisation). Circuit Séquentiel 3

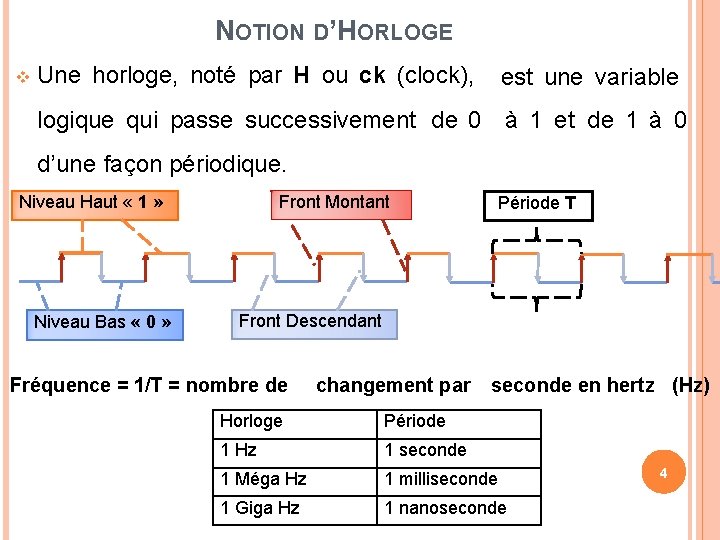

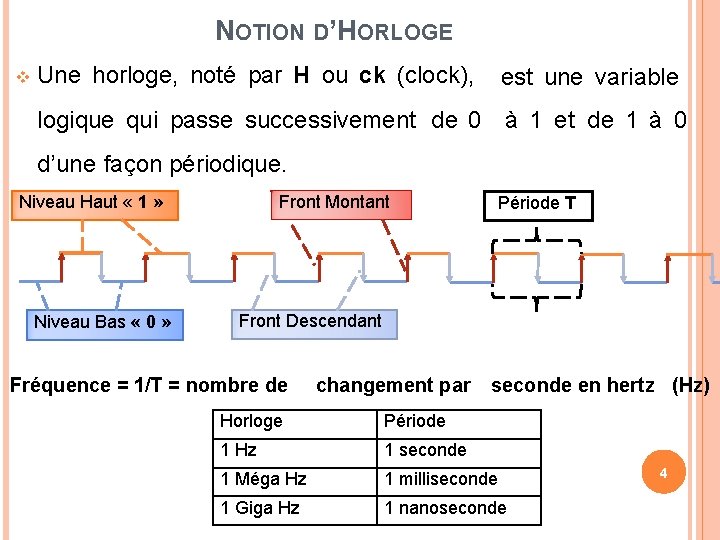

NOTION D’HORLOGE Une horloge, noté par H ou ck (clock), est une variable logique qui passe successivement de 0 à 1 et de 1 à 0 d’une façon périodique. Front Montant Niveau Haut « 1 » Niveau Bas « 0 » Période T Front Descendant Fréquence = 1/T = nombre de changement par seconde en hertz (Hz) Horloge Période 1 Hz 1 seconde 1 Méga Hz 1 milliseconde 1 Giga Hz 1 nanoseconde 4

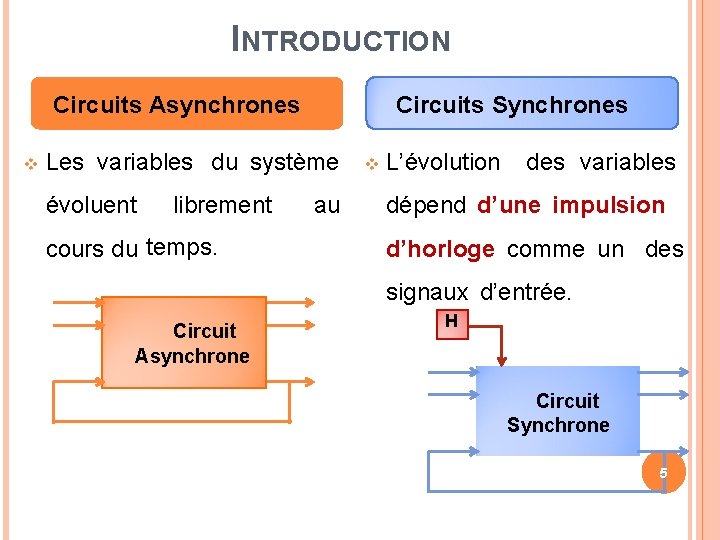

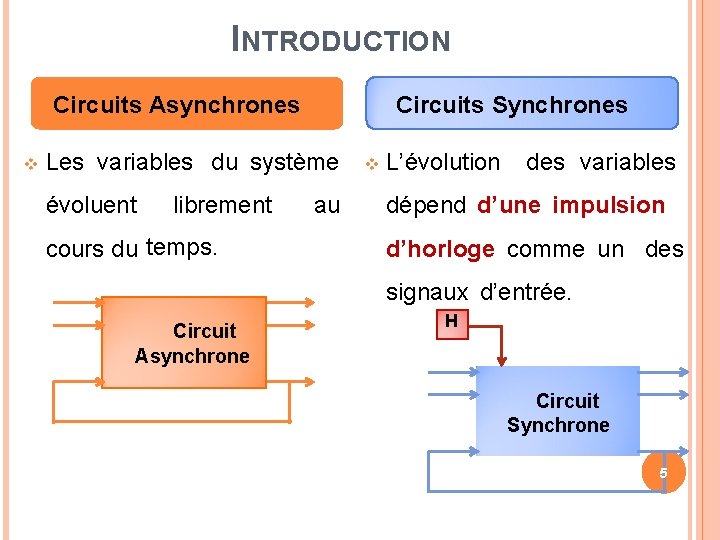

INTRODUCTION Circuits Asynchrones Circuits Synchrones Les variables du système évoluent librement cours du temps. au L’évolution des variables dépend d’une impulsion d’horloge comme un des signaux d’entrée. Circuit Asynchrone H Circuit Synchrone 5

PARTIE 1: 6 BASCULES

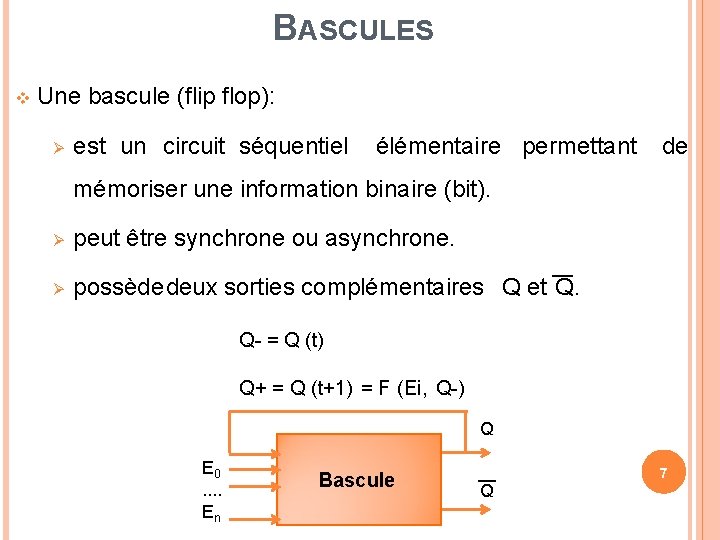

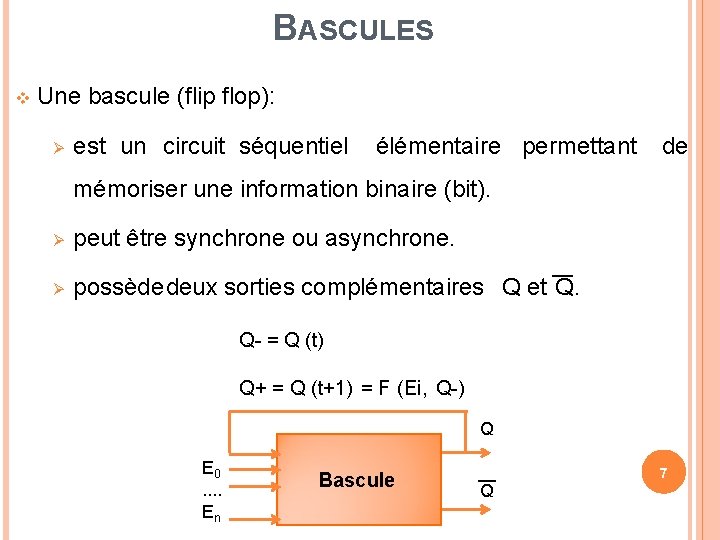

BASCULES Une bascule (flip flop): est un circuit séquentiel élémentaire permettant de mémoriser une information binaire (bit). peut être synchrone ou asynchrone. possèdedeux sorties complémentaires Q et Q. Q- = Q (t) Q+ = Q (t+1) = F (Ei, Q-) Q E 0. . En Bascule Q 7

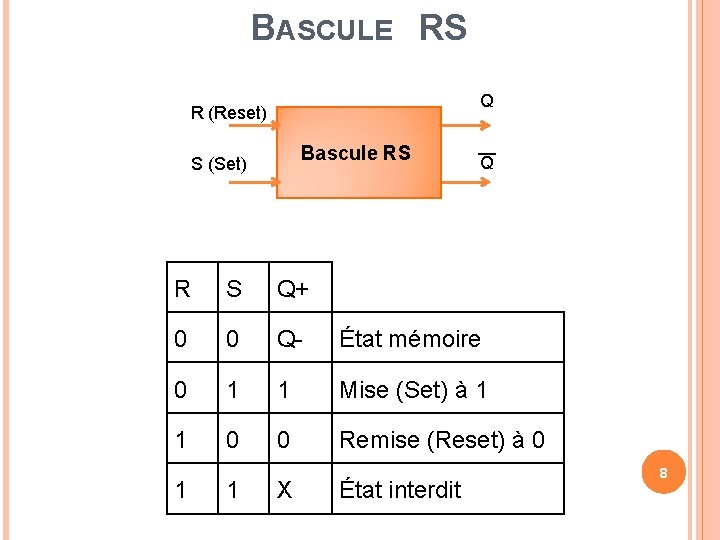

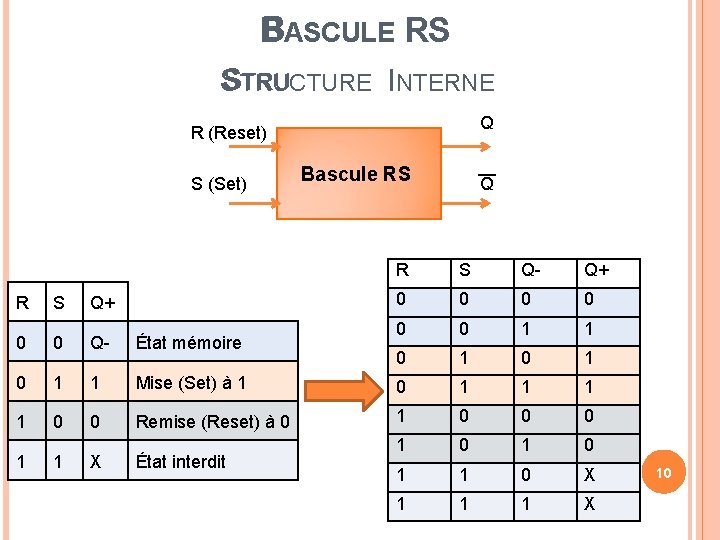

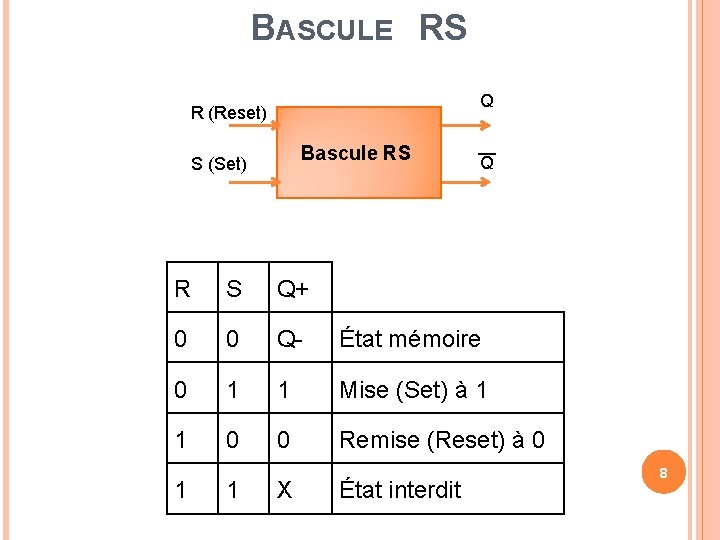

BASCULE RS Q R (Reset) Bascule RS S (Set) Q R S Q+ 0 0 Q- État mémoire 0 1 1 Mise (Set) à 1 1 0 0 Remise (Reset) à 0 1 1 X État interdit 8

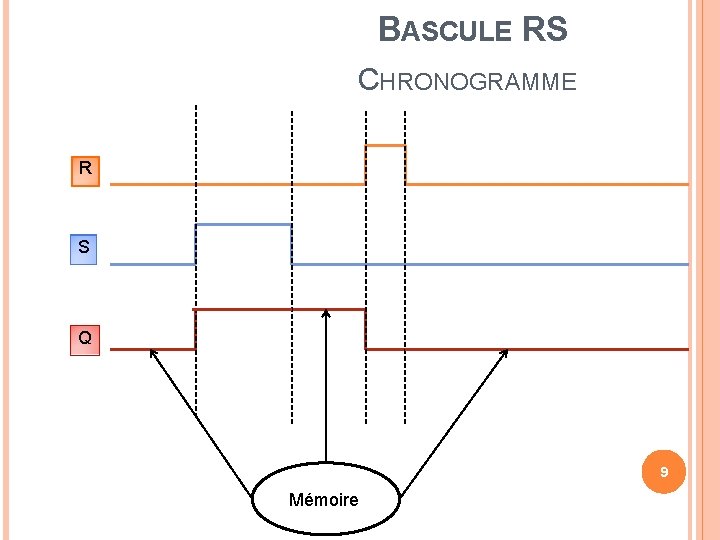

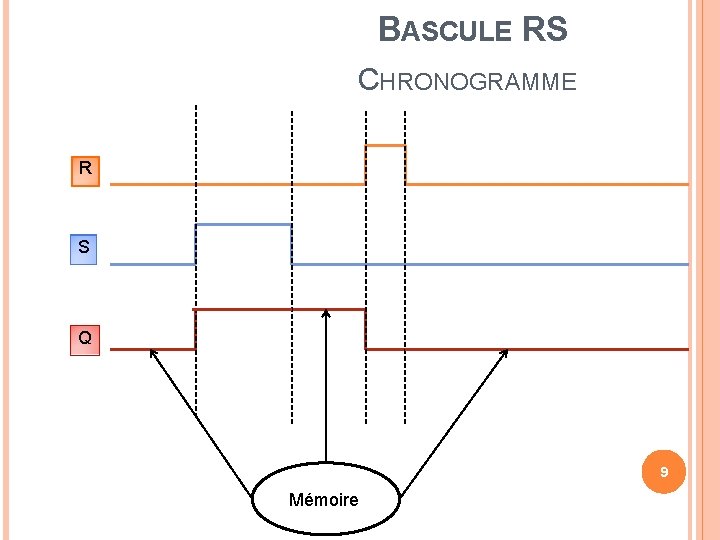

BASCULE RS CHRONOGRAMME R S Q 9 Mémoire

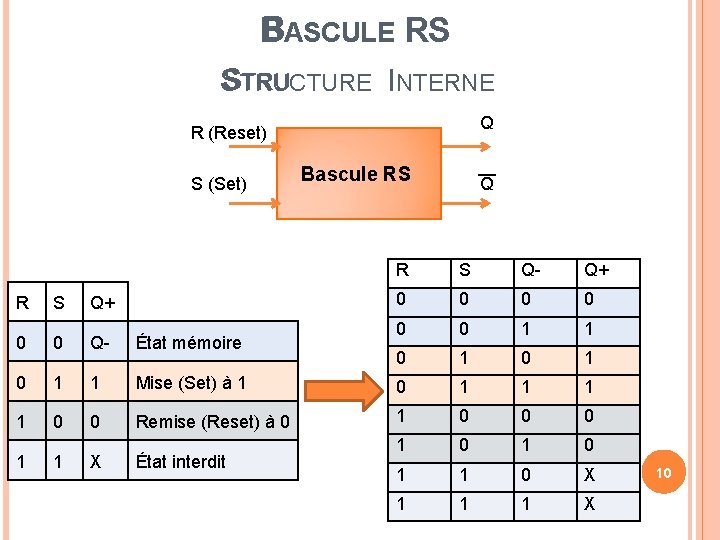

BASCULE RS TRU STRUCTURE INTERNE Q R (Reset) S (Set) R S Q+ Bascule RS Q R S Q- Q+ 0 0 0 1 1 0 1 0 0 Q- État mémoire 0 1 1 Mise (Set) à 1 0 1 1 0 0 Remise (Reset) à 0 1 0 0 0 1 0 1 1 0 X 1 1 1 X État interdit 10

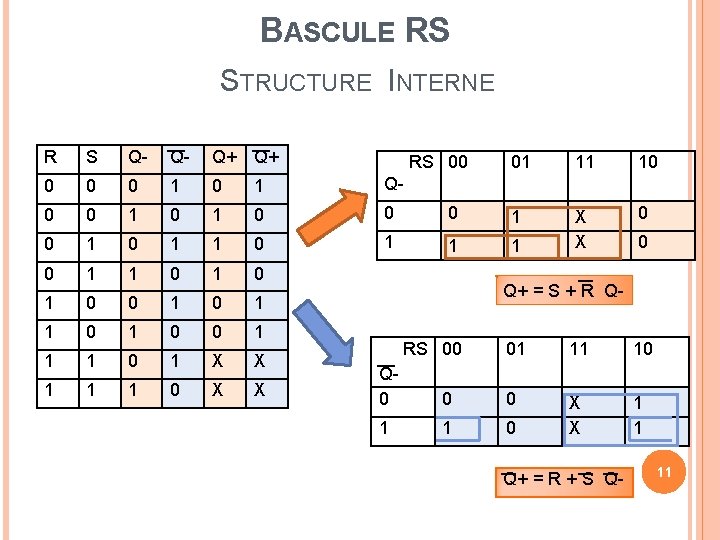

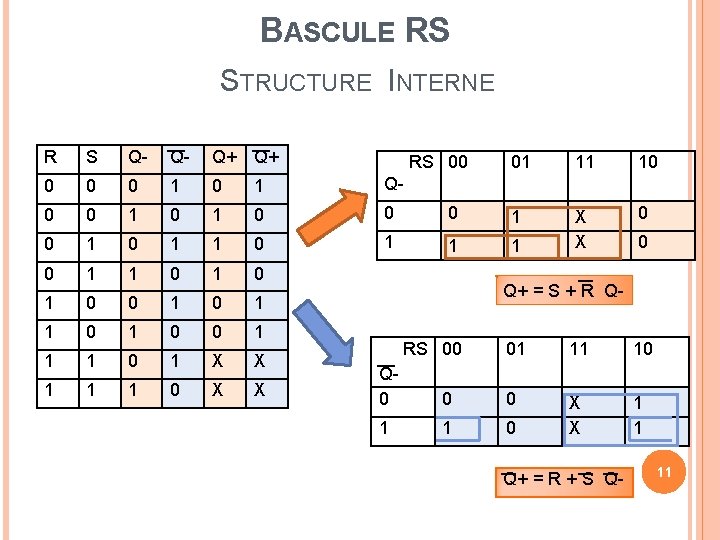

BASCULE RS STRUCTURE INTERNE R S Q- Q- Q+ Q+ 0 0 0 1 Q- 0 0 1 0 1 1 0 1 0 0 1 1 1 0 1 X X 1 1 1 0 X X RS 00 01 11 10 0 1 1 X X 0 Q+ = S + R QRS 00 01 11 10 X X 1 1 Q 0 0 0 1 1 0 Q+ = R + S Q- 11

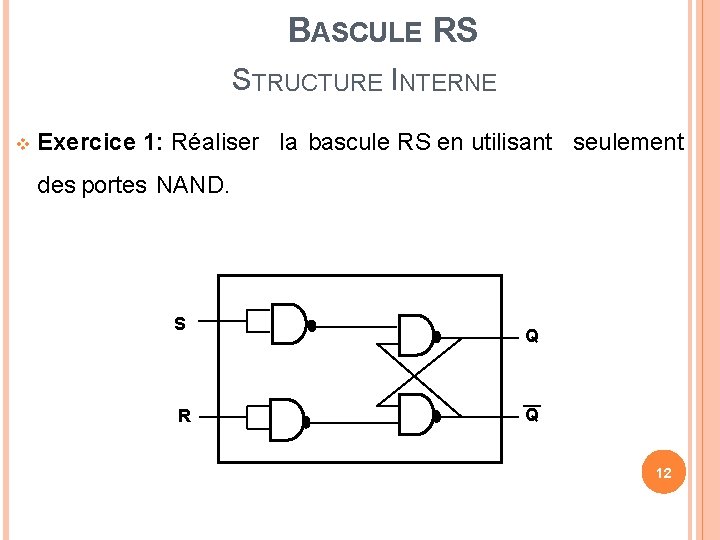

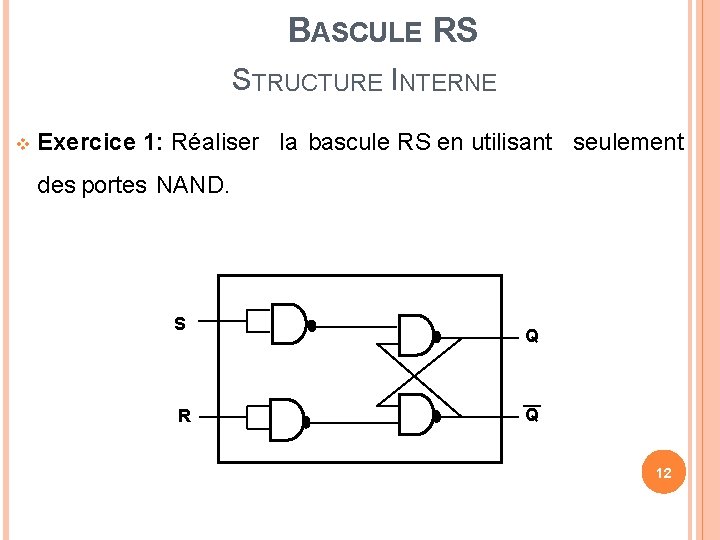

BASCULE RS STRUCTURE INTERNE Exercice 1: Réaliser la bascule RS en utilisant seulement des portes NAND. S R Q Q 12

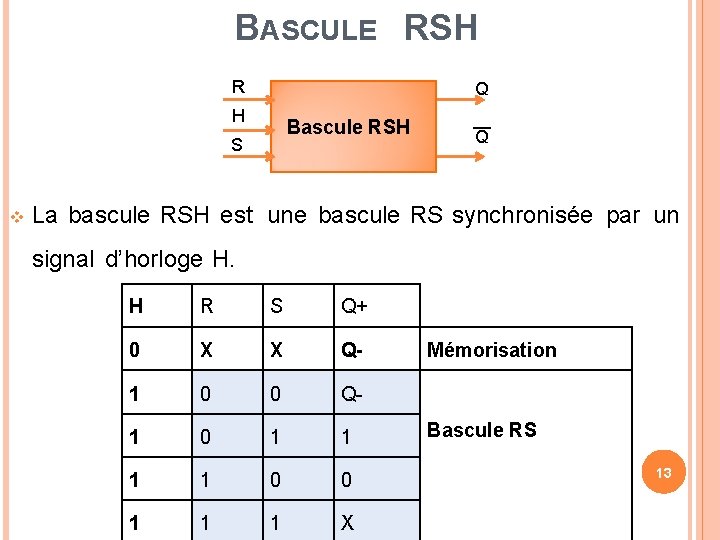

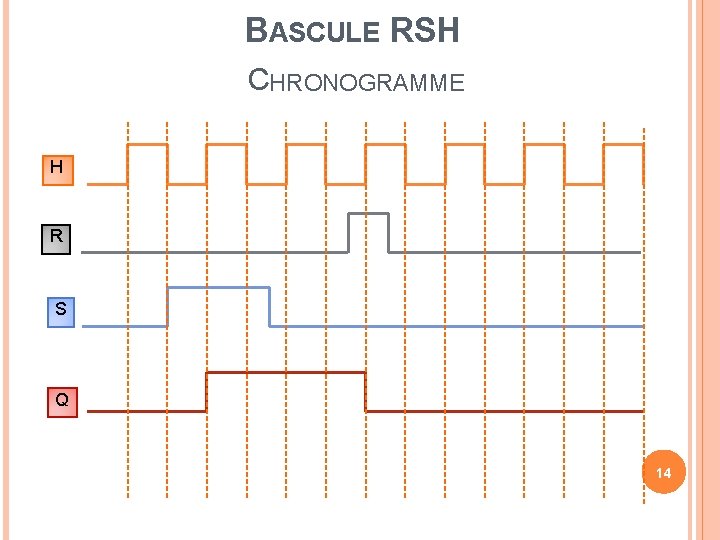

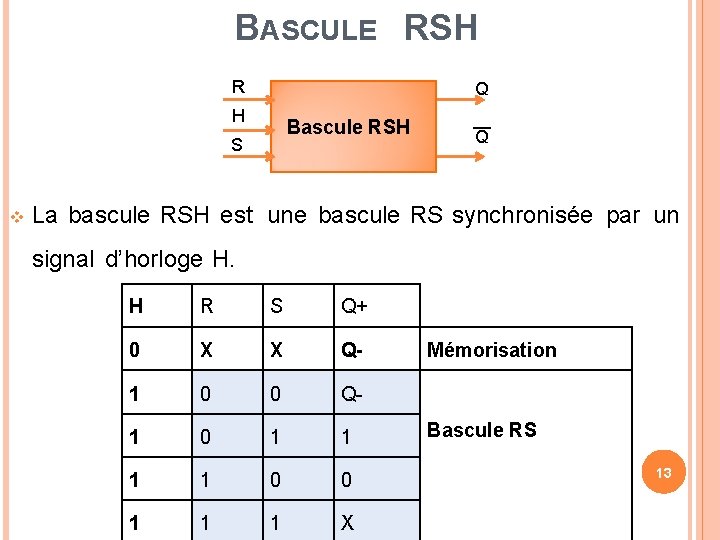

BASCULE RSH R Q H Bascule RSH S Q La bascule RSH est une bascule RS synchronisée par un signal d’horloge H. H R S Q+ 0 X X Q- 1 0 0 Q- 1 0 1 1 0 0 1 1 1 X Mémorisation Bascule RS 13

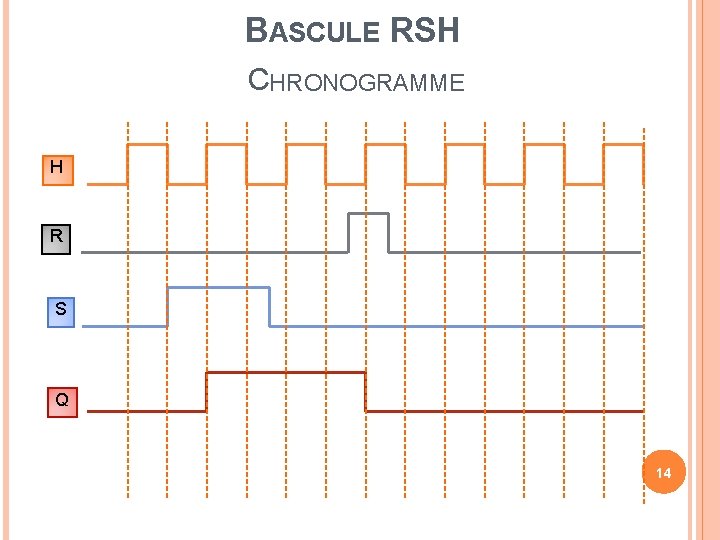

BASCULE RSH CHRONOGRAMME H R S Q 14

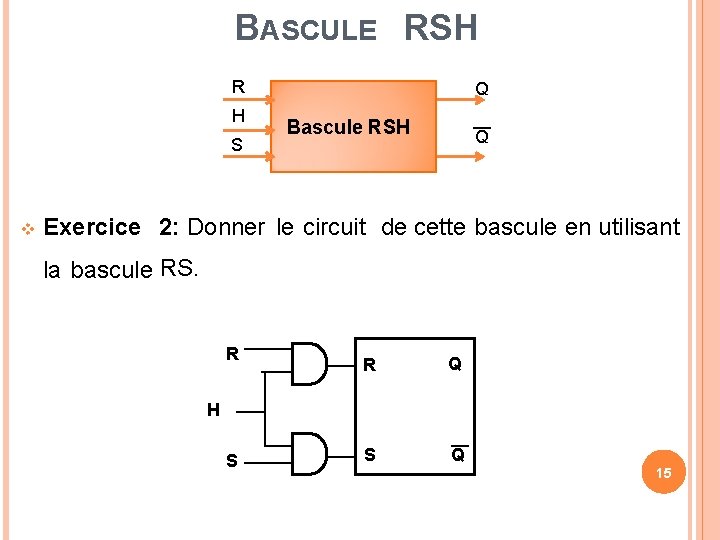

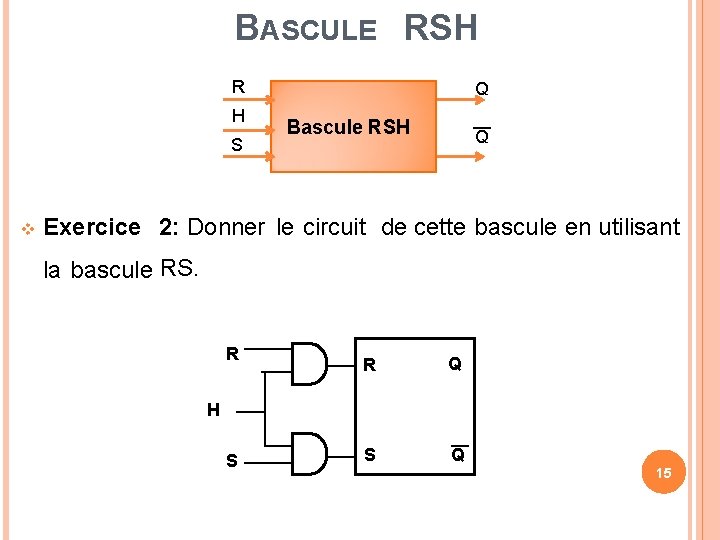

BASCULE RSH R H S Q Bascule RSH Q Exercice 2: Donner le circuit de cette bascule en utilisant la bascule RS. R R Q S Q H S 15

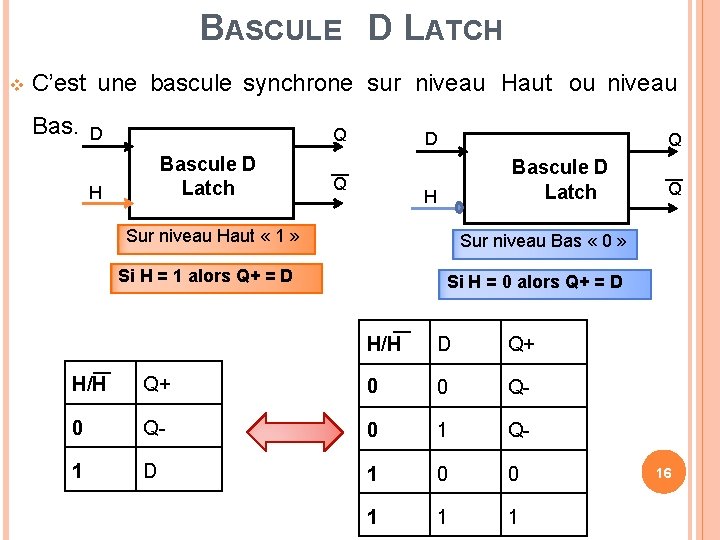

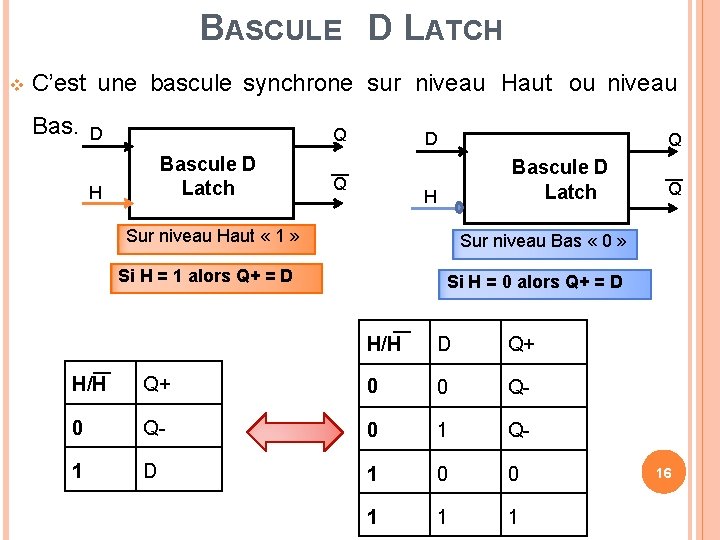

BASCULE D LATCH C’est une bascule synchrone sur niveau Haut ou niveau Bas. D Q Bascule D Latch H D Q Q Bascule D Latch H Sur niveau Haut « 1 » Q Sur niveau Bas « 0 » Si H = 1 alors Q+ = D Si H = 0 alors Q+ = D H/H D Q+ H/H Q+ 0 0 Q- 0 1 Q- 1 D 1 0 0 1 16

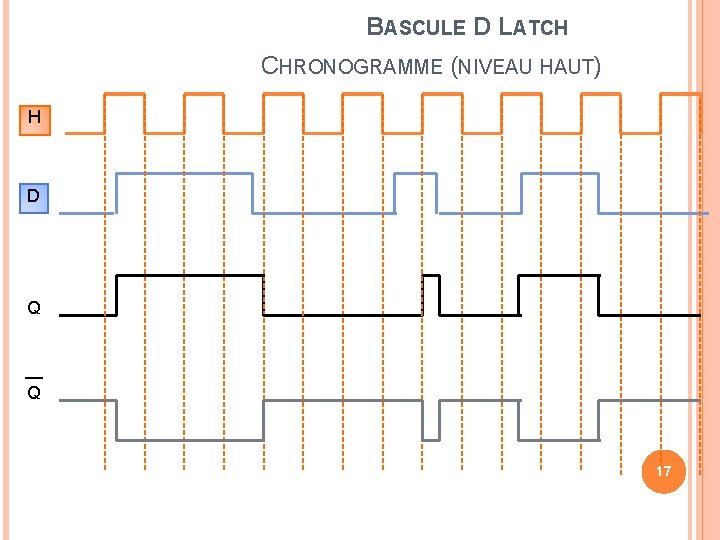

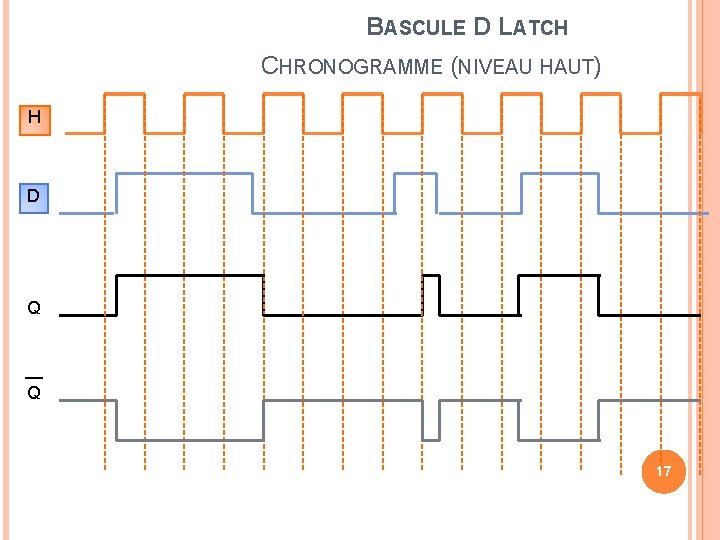

BASCULE D LATCH CHRONOGRAMME (NIVEAU HAUT) H D Q Q 17

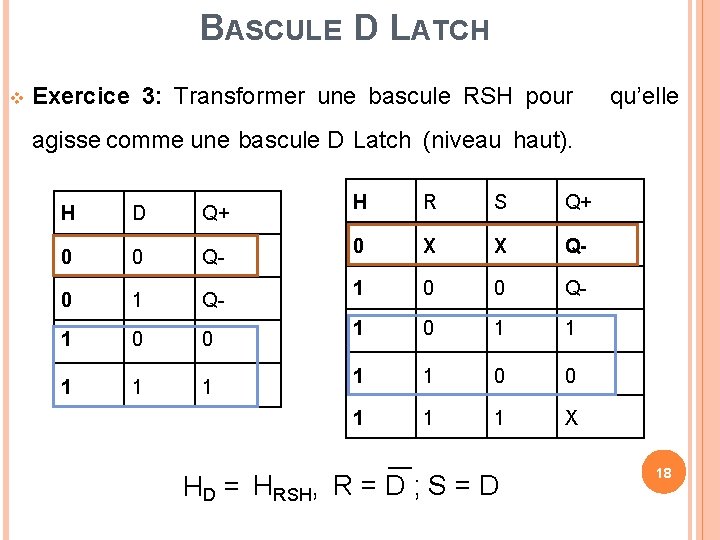

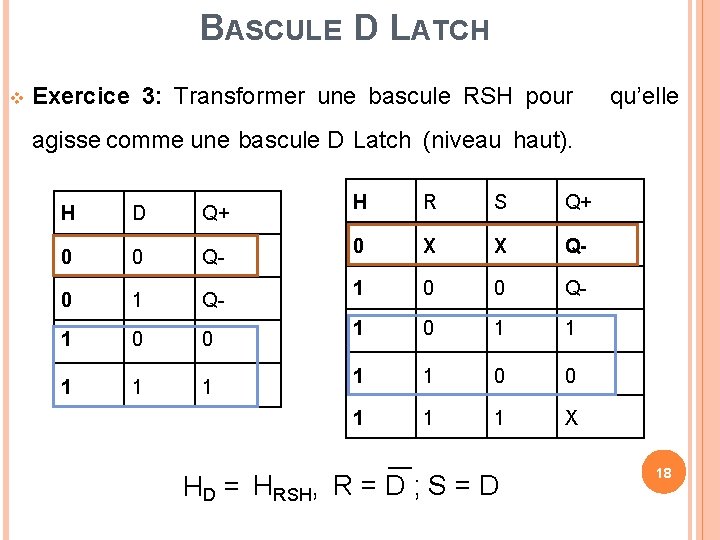

BASCULE D LATCH Exercice 3: Transformer une bascule RSH pour qu’elle agisse comme une bascule D Latch (niveau haut). H D Q+ 0 0 Q- 0 1 Q- 1 0 0 1 1 1 H R S Q+ 0 X X Q- 1 0 0 Q- 1 0 1 1 0 0 1 1 1 X HD = HRSH, R = D ; S = D 18

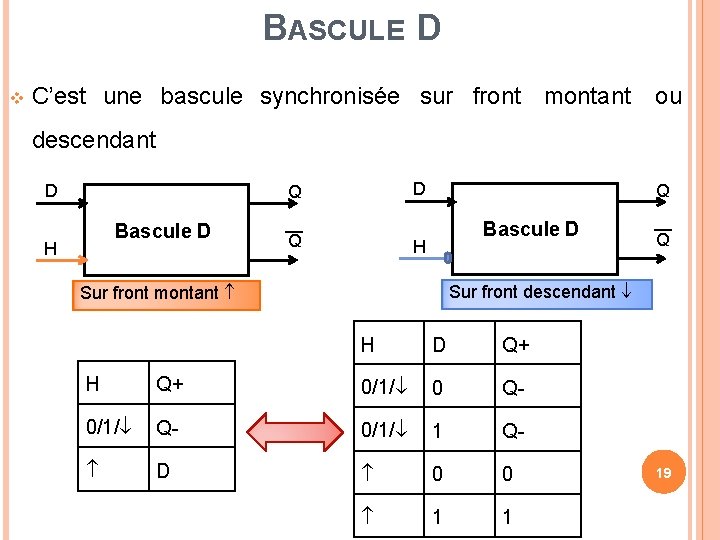

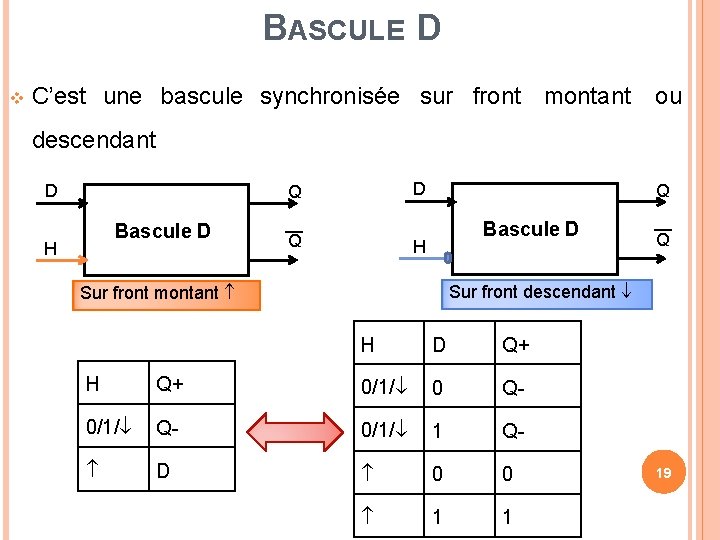

BASCULE D C’est une bascule synchronisée sur front montant ou descendant D D Q Bascule D H Q Sur front descendant Sur front montant H D Q+ H Q+ 0/1/ 0 Q- 0/1/ 1 Q- D 0 0 1 1 19

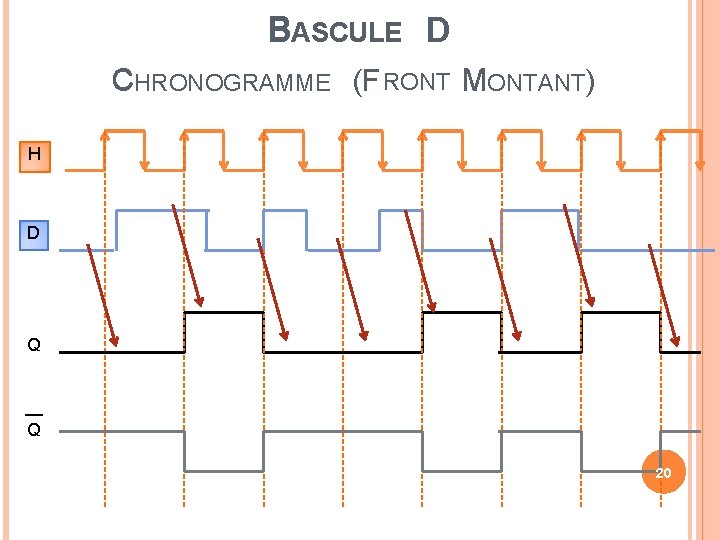

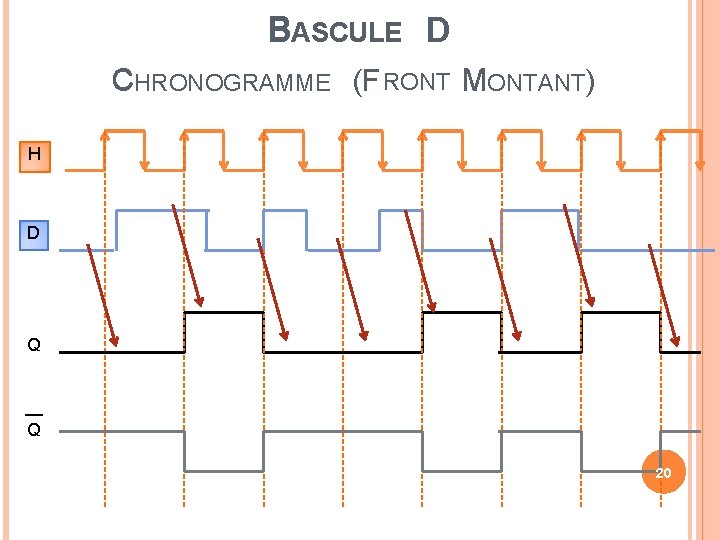

BASCULE D CHRONOGRAMME (F RONT MONTANT) H D Q Q 20

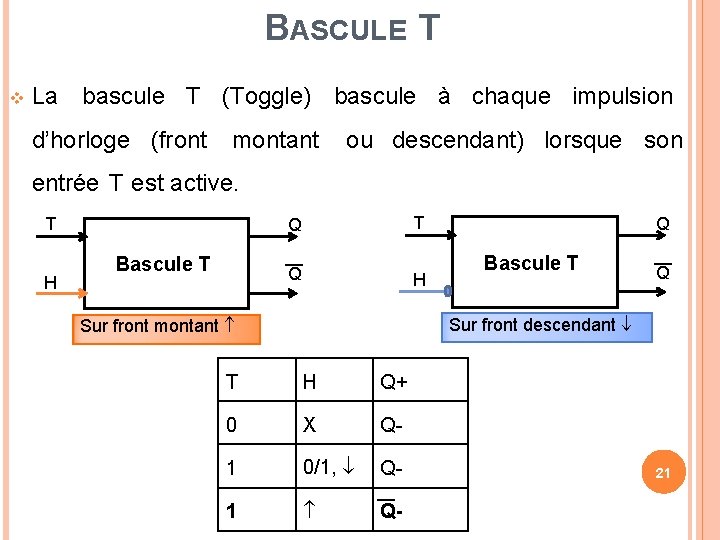

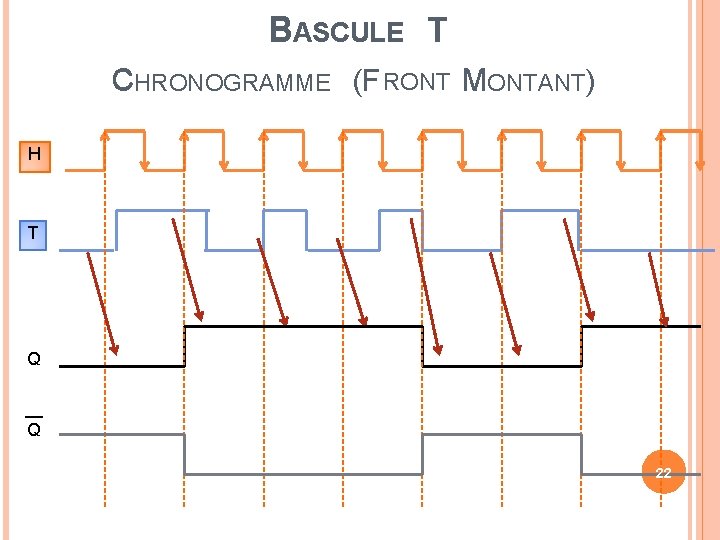

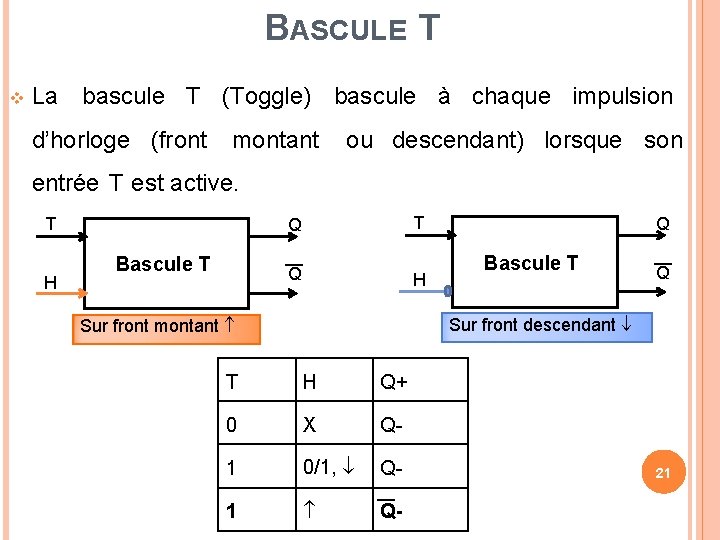

BASCULE T La bascule T (Toggle) bascule à chaque impulsion d’horloge (front montant ou descendant) lorsque son entrée T est active. T H T Q Bascule T Q H Q Bascule T Q Sur front descendant Sur front montant T H Q+ 0 X Q- 1 0/1, Q- 1 Q- 21

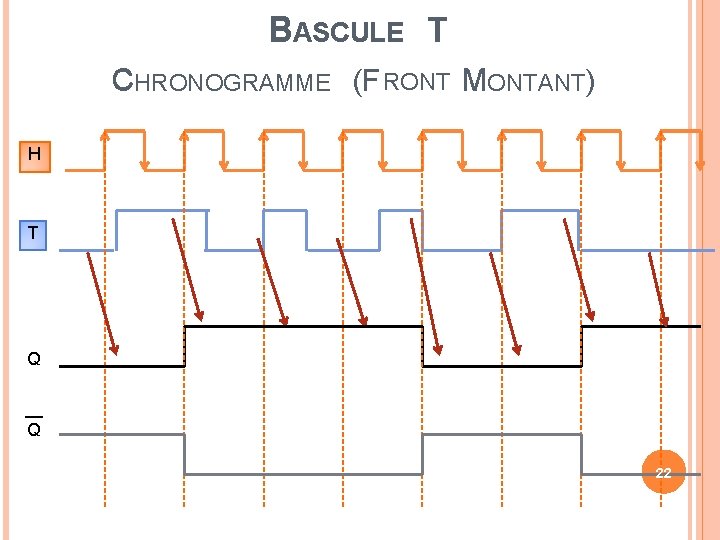

BASCULE T CHRONOGRAMME (F RONT MONTANT) H T Q Q 22

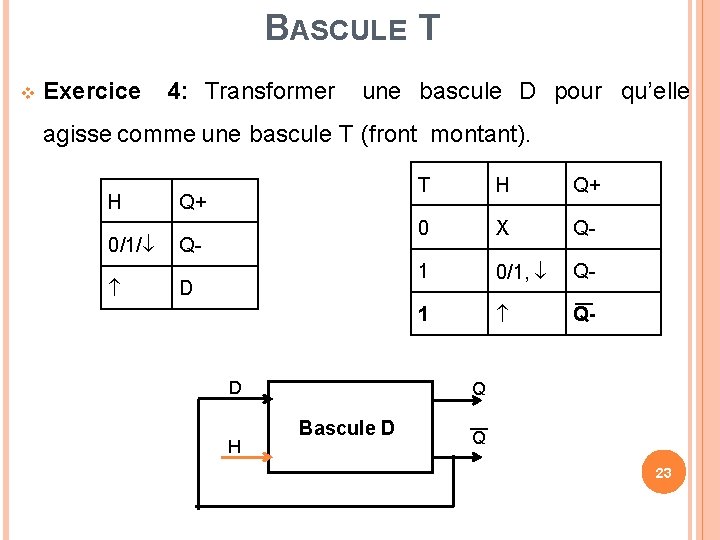

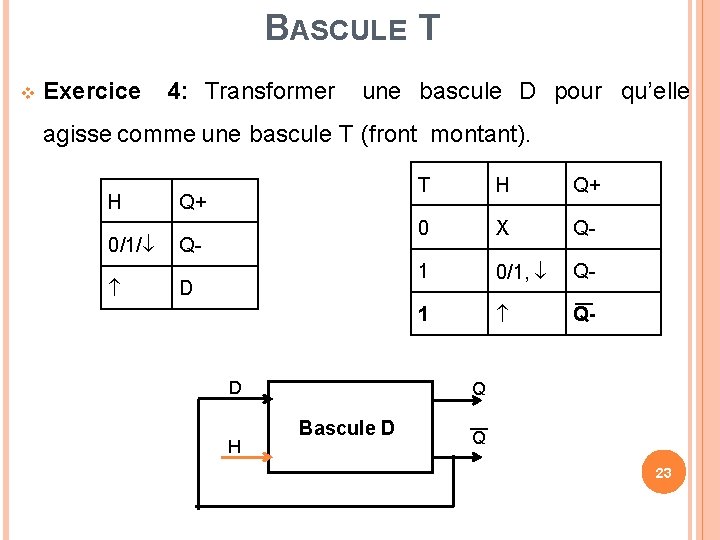

BASCULE T Exercice 4: Transformer une bascule D pour qu’elle agisse comme une bascule T (front montant). H 0/1/ Q+ QD D H T H Q+ 0 X Q- 1 0/1, Q- 1 Q- Q Bascule D Q 23

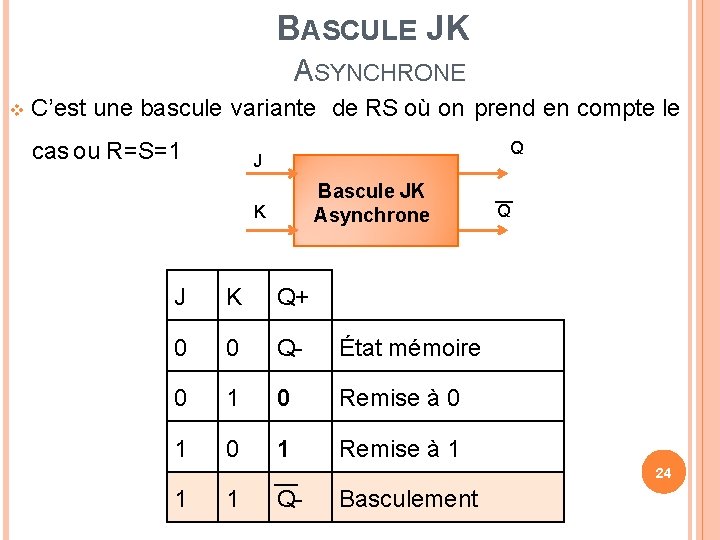

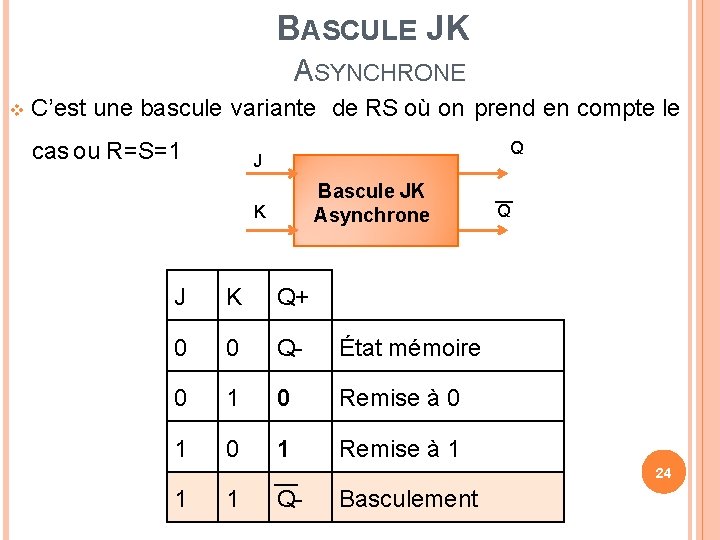

BASCULE JK ASYNCHRONE C’est une bascule variante de RS où on prend en compte le cas ou R=S=1 Q J Bascule JK Asynchrone K J K Q+ 0 0 Q- État mémoire 0 1 0 Remise à 0 1 Remise à 1 Q 24 1 1 Q- Basculement

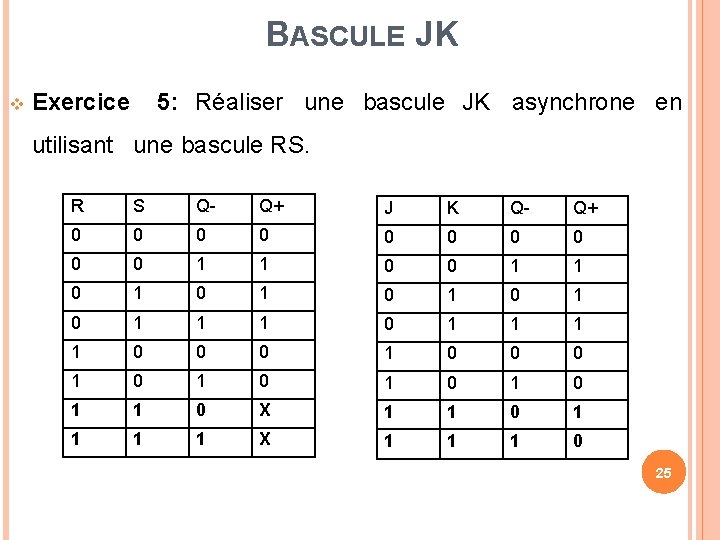

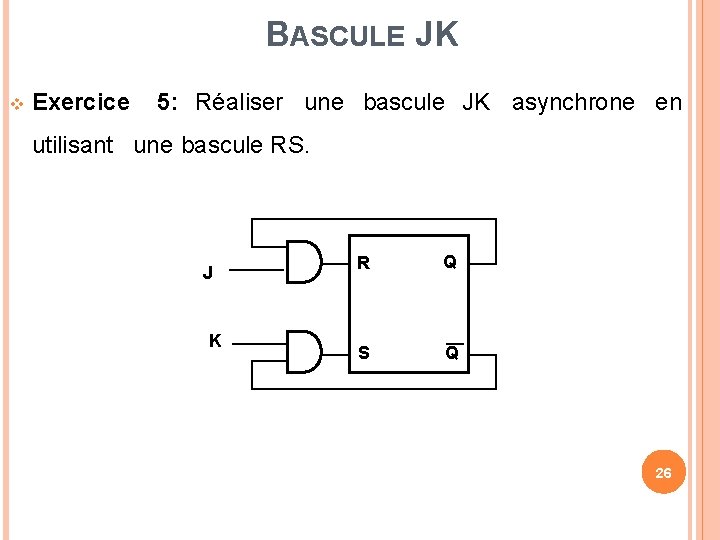

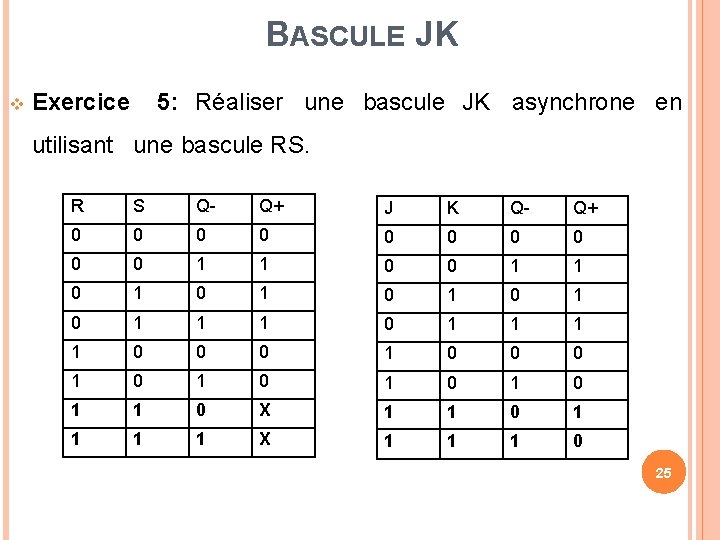

BASCULE JK Exercice 5: Réaliser une bascule JK asynchrone en utilisant une bascule RS. R S Q- Q+ J K Q- Q+ 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 X 1 1 0 1 1 X 1 1 1 0 25

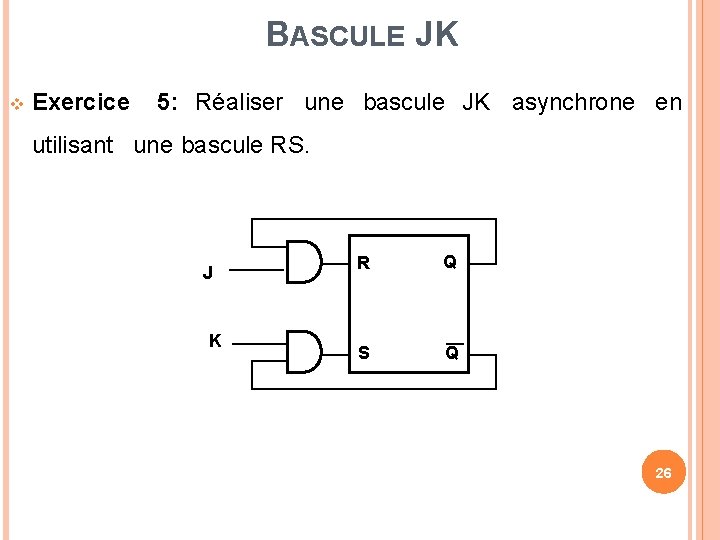

BASCULE JK Exercice 5: Réaliser une bascule JK asynchrone en utilisant une bascule RS. J K R Q S Q 26

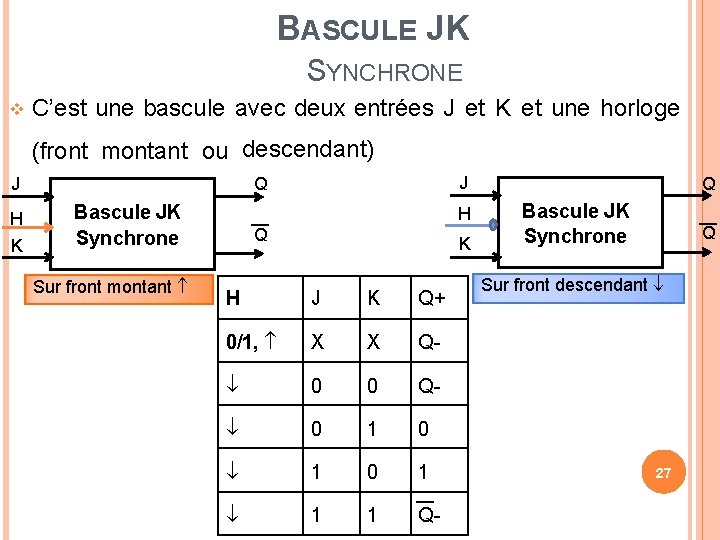

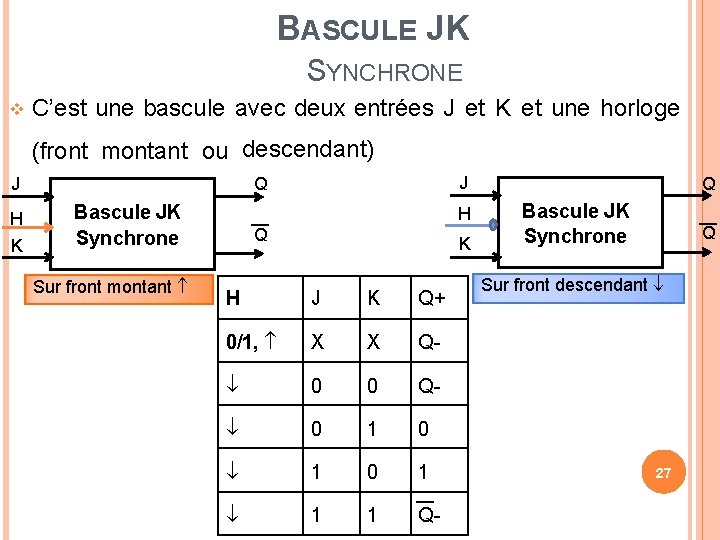

BASCULE JK SYNCHRONE C’est une bascule avec deux entrées J et K et une horloge (front montant ou descendant) H K J Q J Bascule JK Synchrone Sur front montant H Q K H J K Q+ 0/1, X X Q- 0 0 Q- 0 1 0 1 1 1 Q- Q Bascule JK Synchrone Q Sur front descendant 27

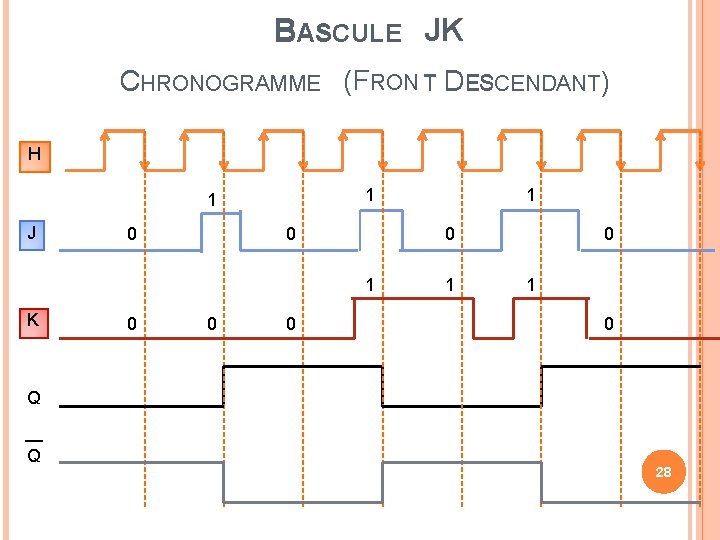

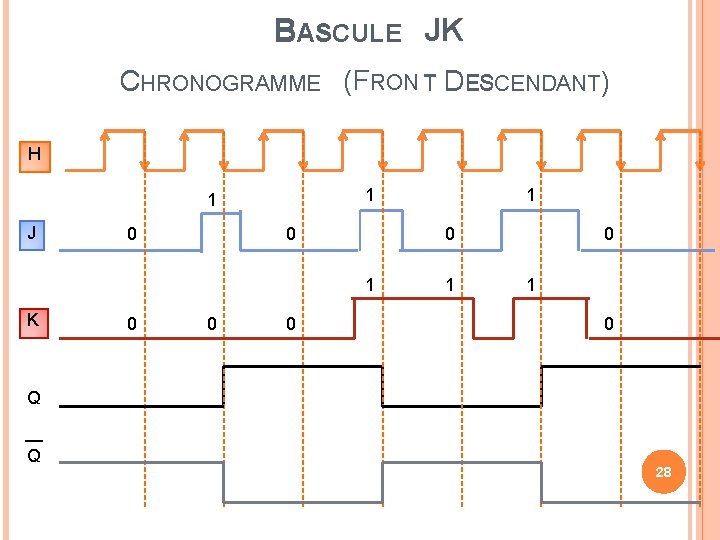

BAS ASCULE JK CHRONOGRAMME (FRON T DES ESCENDANT) H 1 1 J 0 0 0 1 K 0 0 0 1 1 0 Q Q 28

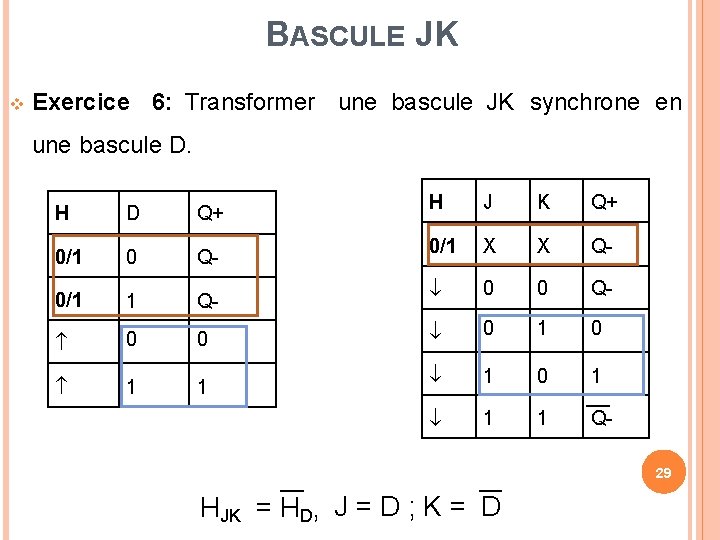

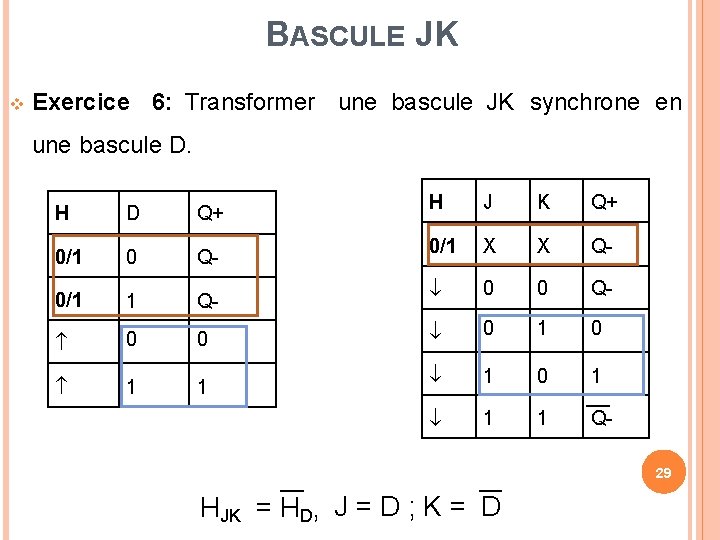

BASCULE JK Exercice 6: Transformer une bascule JK synchrone en une bascule D. H D Q+ 0/1 0 Q- 0/1 1 Q- 0 0 1 1 H J K Q+ 0/1 X X Q- 0 0 Q- 0 1 0 1 1 1 Q 29 HJK = HD, J = D ; K = D

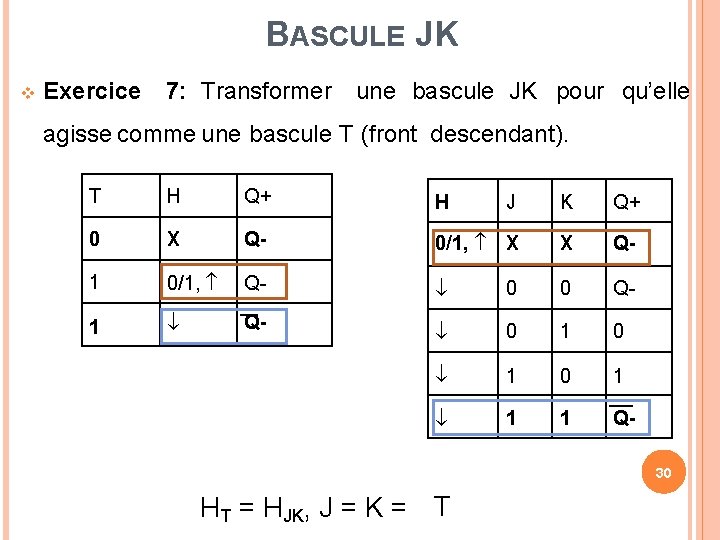

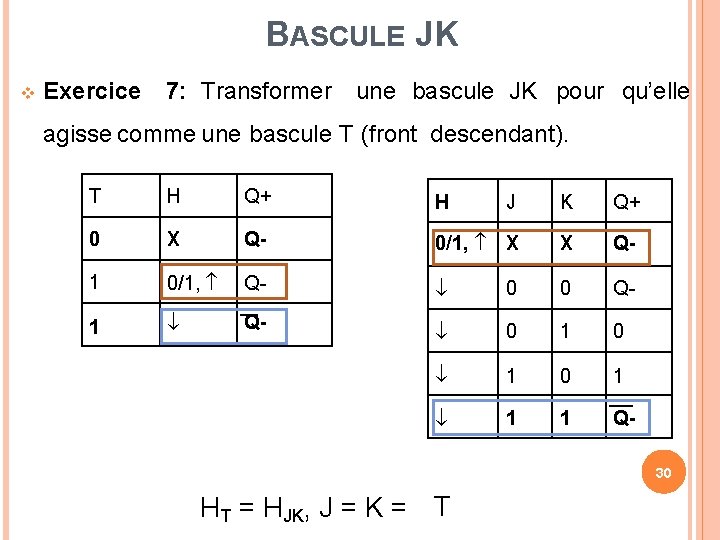

BASCULE JK Exercice 7: Transformer une bascule JK pour qu’elle agisse comme une bascule T (front descendant). T H Q+ H J K Q+ 0 X Q- 0/1, X X Q- 1 0/1, Q- 0 0 Q- 1 Q- 0 1 0 1 1 1 Q 30 HT = HJK, J = K = T

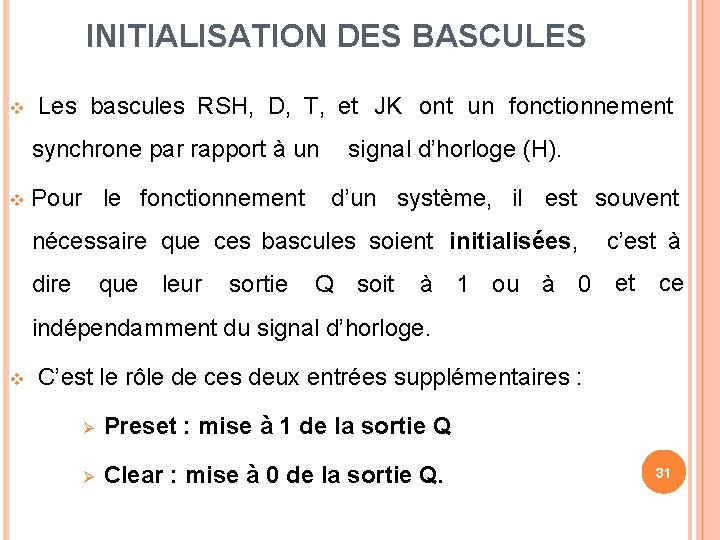

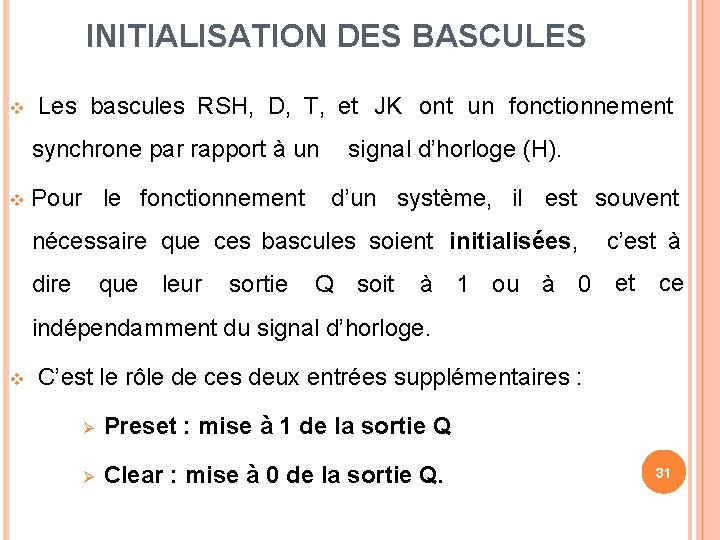

INITIALISATION DES BASCULES Les bascules RSH, D, T, et JK ont un fonctionnement synchrone par rapport à un Pour le fonctionnement signal d’horloge (H). d’un système, il est souvent nécessaire que ces bascules soient initialisées, dire que leur sortie Q soit c’est à à 1 ou à 0 et ce indépendamment du signal d’horloge. C’est le rôle de ces deux entrées supplémentaires : Preset : mise à 1 de la sortie Q Clear : mise à 0 de la sortie Q. 31

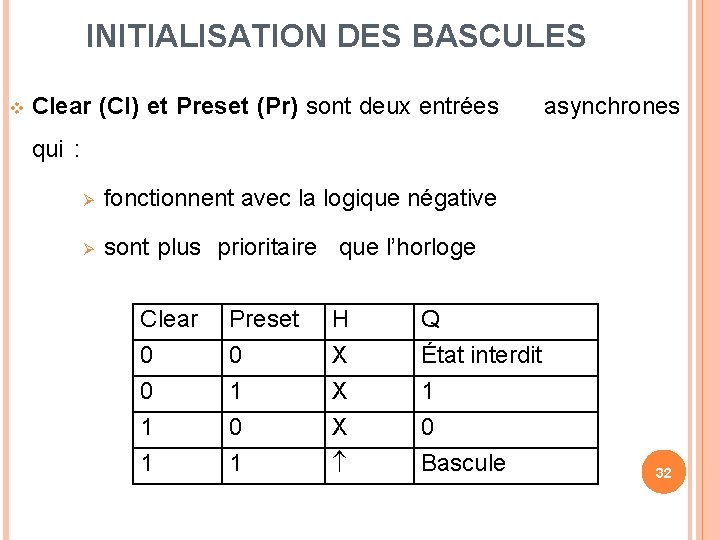

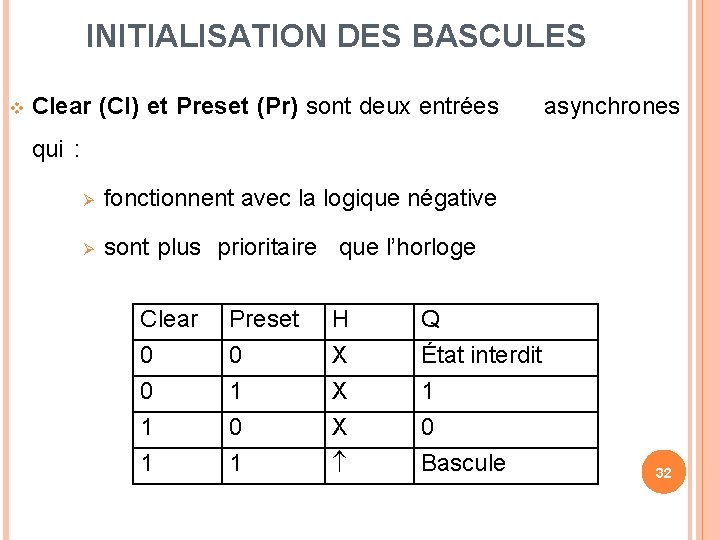

INITIALISATION DES BASCULES Clear (Cl) et Preset (Pr) sont deux entrées asynchrones qui : fonctionnent avec la logique négative sont plus prioritaire que l’horloge Clear 0 0 1 1 Preset 0 1 H X X X Q État interdit 1 0 Bascule 32

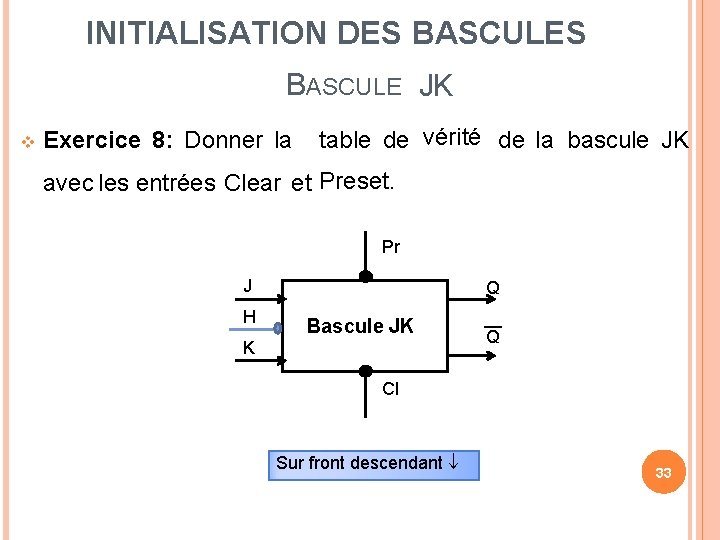

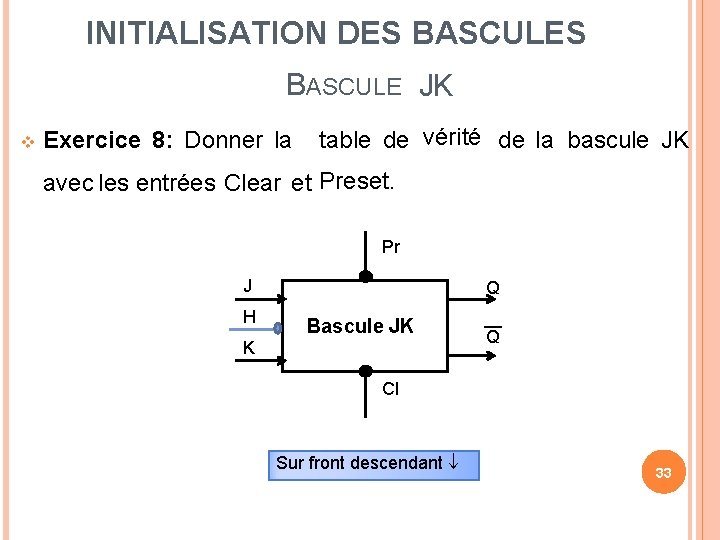

INITIALISATION DES BASCULE JK Exercice 8: Donner la table de vérité de la bascule JK avec les entrées Clear et Preset. Pr J H K Q Bascule JK Q Cl Sur front descendant 33

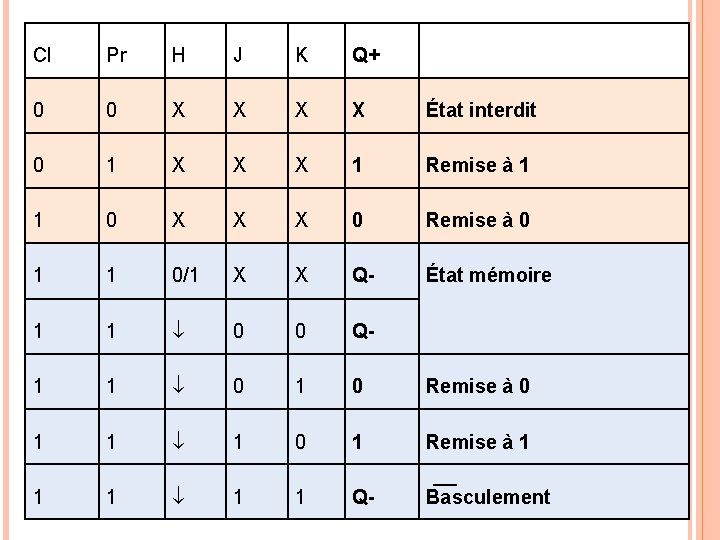

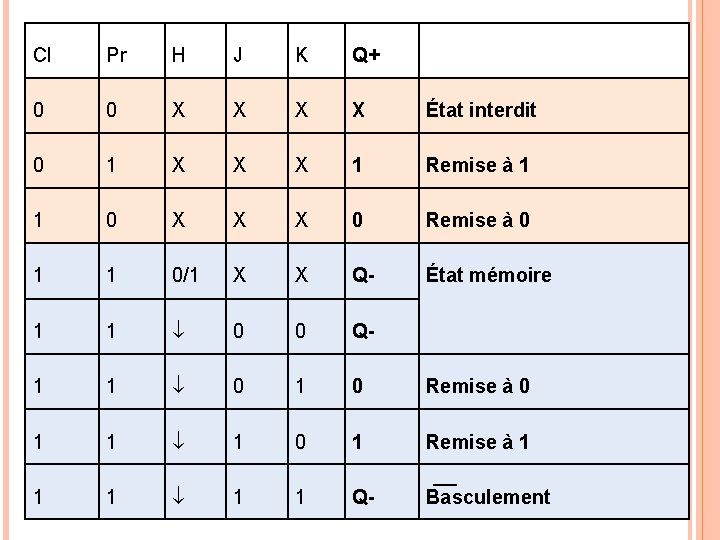

Cl Pr H J K Q+ 0 0 X X État interdit 0 1 X X X 1 Remise à 1 1 0 X X X 0 Remise à 0 1 1 0/1 X X Q- État mémoire 1 1 0 0 Q- 1 1 0 Remise à 0 1 1 1 0 1 Remise à 1 34 1 1 Q- Basculement

La partie 2 du chapitres 3 concerne les registres

SOURCES DE CE COURS Amrouche Hakim, nationale Cours d’Architecture Supérieure d’Informatique des ordinateurs, (ESI), Alger, École Année universitaire 2011/2012. 101