Central Processing Unit 1 Lecture 27 Program Control

- Slides: 5

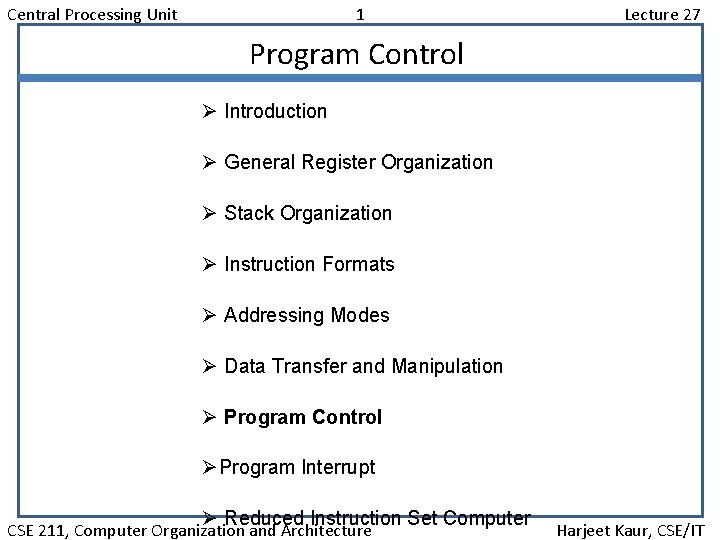

Central Processing Unit 1 Lecture 27 Program Control Ø Introduction Ø General Register Organization Ø Stack Organization Ø Instruction Formats Ø Addressing Modes Ø Data Transfer and Manipulation Ø Program Control ØProgram Interrupt Ø Reduced Instruction Set Computer CSE 211, Computer Organization and Architecture Harjeet Kaur, CSE/IT

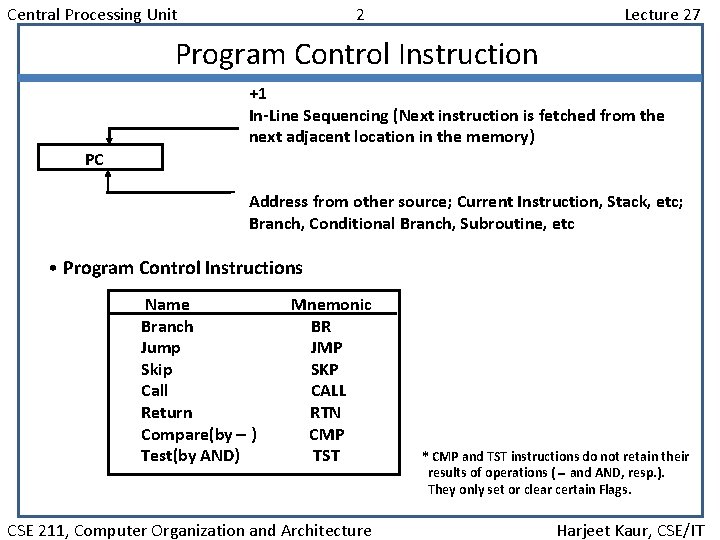

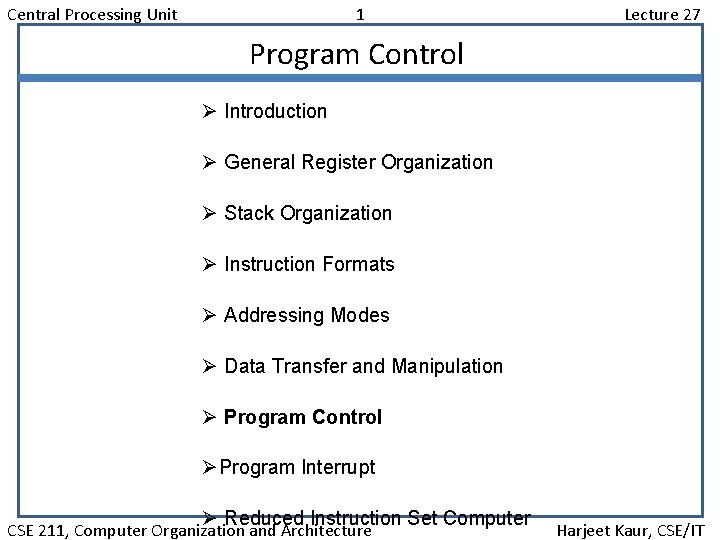

Central Processing Unit 2 Lecture 27 Program Control Instruction +1 In-Line Sequencing (Next instruction is fetched from the next adjacent location in the memory) PC Address from other source; Current Instruction, Stack, etc; Branch, Conditional Branch, Subroutine, etc • Program Control Instructions Name Branch Jump Skip Call Return Compare(by ) Test(by AND) Mnemonic BR JMP SKP CALL RTN CMP TST CSE 211, Computer Organization and Architecture * CMP and TST instructions do not retain their results of operations ( and AND, resp. ). They only set or clear certain Flags. Harjeet Kaur, CSE/IT

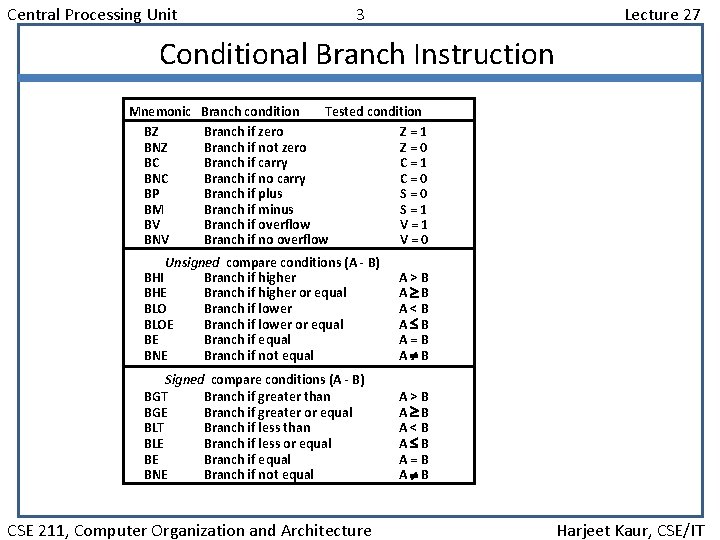

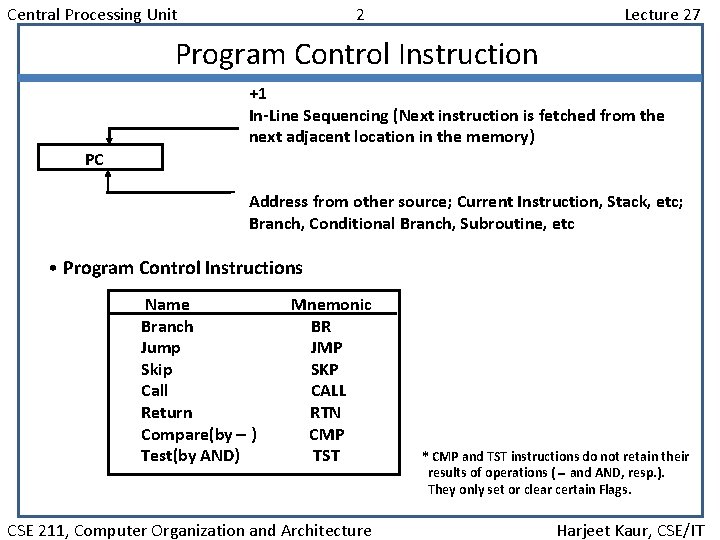

Central Processing Unit 3 Lecture 27 Conditional Branch Instruction Mnemonic BZ BNZ BC BNC BP BM BV BNV Branch condition Tested condition Branch if zero Z=1 Branch if not zero Z=0 Branch if carry C=1 Branch if no carry C=0 Branch if plus S=0 Branch if minus S=1 Branch if overflow V=1 Branch if no overflow V=0 Unsigned compare conditions (A - B) BHI Branch if higher BHE Branch if higher or equal BLO Branch if lower BLOE Branch if lower or equal BE Branch if equal BNE Branch if not equal A>B A B A<B A B A=B A B Signed compare conditions (A - B) BGT Branch if greater than BGE Branch if greater or equal BLT Branch if less than BLE Branch if less or equal BE Branch if equal BNE Branch if not equal A>B A B A<B A B A=B A B CSE 211, Computer Organization and Architecture Harjeet Kaur, CSE/IT

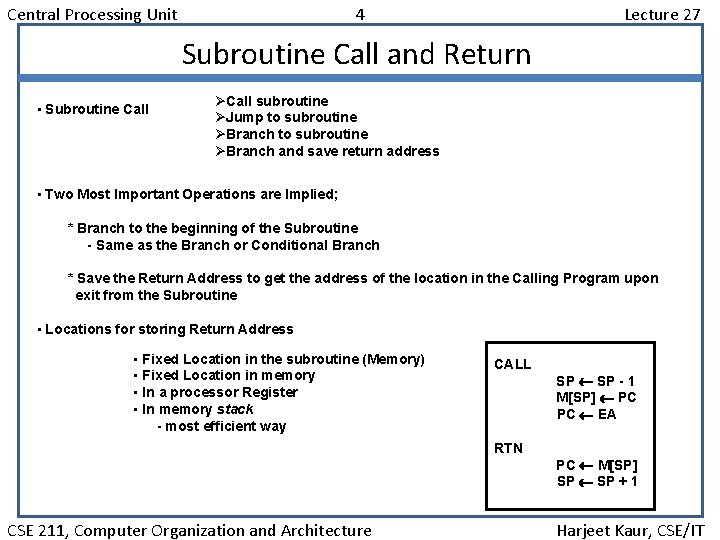

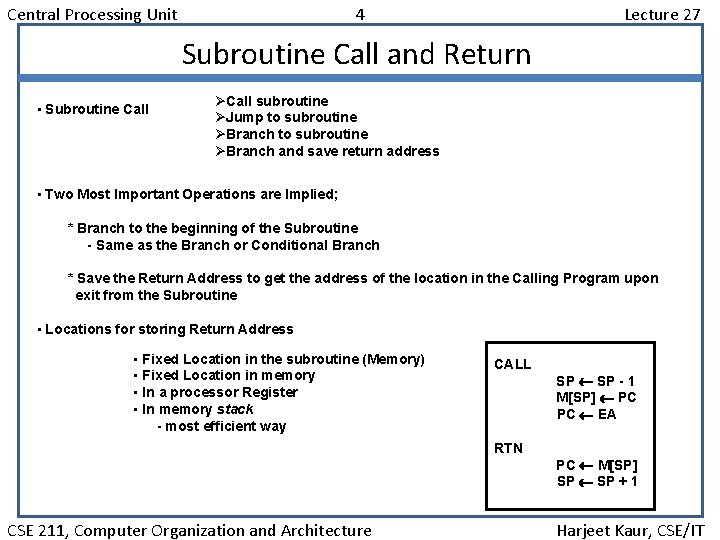

Central Processing Unit 4 Lecture 27 Subroutine Call and Return • Subroutine Call ØCall subroutine ØJump to subroutine ØBranch and save return address • Two Most Important Operations are Implied; * Branch to the beginning of the Subroutine - Same as the Branch or Conditional Branch * Save the Return Address to get the address of the location in the Calling Program upon exit from the Subroutine • Locations for storing Return Address • Fixed Location in the subroutine (Memory) • Fixed Location in memory • In a processor Register • In memory stack - most efficient way CALL RTN CSE 211, Computer Organization and Architecture SP - 1 M[SP] PC PC EA PC M[SP] SP + 1 Harjeet Kaur, CSE/IT

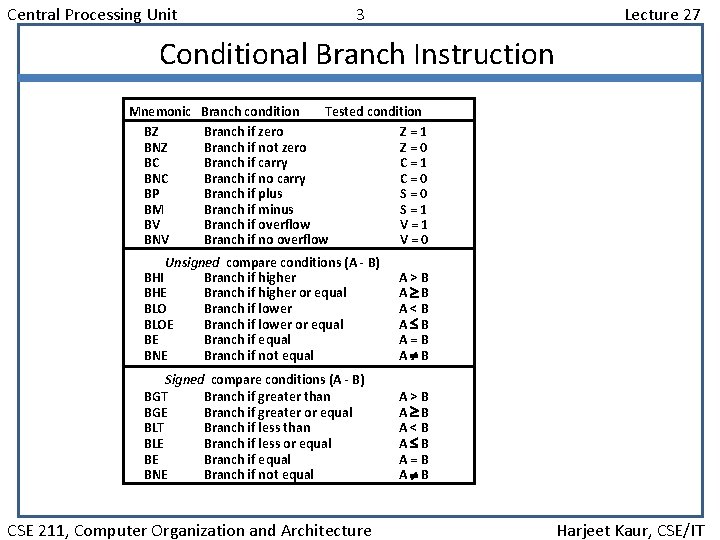

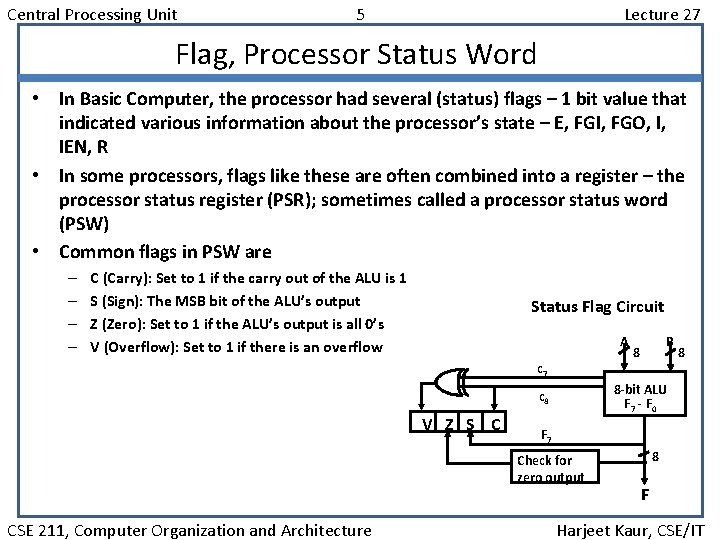

Central Processing Unit 5 Lecture 27 Flag, Processor Status Word • In Basic Computer, the processor had several (status) flags – 1 bit value that indicated various information about the processor’s state – E, FGI, FGO, I, IEN, R • In some processors, flags like these are often combined into a register – the processor status register (PSR); sometimes called a processor status word (PSW) • Common flags in PSW are – – C (Carry): Set to 1 if the carry out of the ALU is 1 S (Sign): The MSB bit of the ALU’s output Z (Zero): Set to 1 if the ALU’s output is all 0’s V (Overflow): Set to 1 if there is an overflow Status Flag Circuit A c 7 F 7 Check for zero output CSE 211, Computer Organization and Architecture 8 8 -bit ALU F 7 - F 0 c 8 V Z S C B 8 8 F Harjeet Kaur, CSE/IT