CENG 311 Computer Architecture Kayhan Erciyes CS 231

![Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1] Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1]](https://slidetodoc.com/presentation_image_h2/3accde8d7ea5ded871e7a90e78711f70/image-13.jpg)

![Instruction Set Architecture. . . the attributes of a [computing] system as seen by Instruction Set Architecture. . . the attributes of a [computing] system as seen by](https://slidetodoc.com/presentation_image_h2/3accde8d7ea5ded871e7a90e78711f70/image-15.jpg)

- Slides: 28

CENG 311 Computer Architecture Kayhan Erciyes

CS 231 Assembly language and Digital Circuits Instructor: Kayhan Erciyes kayhanerciyes@iyte. edu. tr Office: 214 Office Hours: T 16: 00 -17: 00 or by appt. Lab Instructors: Burak Aslan, Ozgur Tutum Office: TBA Office Hours: TBA Text: Computer Organization & Design: The Hardware / Software Interface (2 nd edition), Patterson and Hennesy. Web page: http: //arf. iyte. edu. tr/~kerciyes/CENG 311 Newsgroup: TBA

Course Outline: ® 1. Introduction to Computer Organization (1 -2 weeks) t t t ® 2. Instruction Set Architecture (3 -4 weeks) t t t ® What is in the box. Integer and Floating point representation. Basic data structures. The MIPS Processor. Assembly level programming. Instructions and data types representations. Branching and Jumps Addressing, procedure calls and Exceptions. Linking & Loading. 3. Review of Digital Logic ( 1 week) t t Introduction: Digital Gates and Boolean Algebra. Arithmetic and Logic circuits, Other Functional Units Flip-flops, Registers and Tristate drivers

Course Outline (continue): ® 4. Single t t t ® ® Cycle Per Instruction Processor (2 weeks) The Datapath. Executing Instructions Control 5. Multiycle processor ( 2 weeks) 6. Pipelining ( 2 weeks) 6. Input/Output and Interrupts. ( 1 week) 7. The Memory Hierarchy ( 1 week) Cache Memory. t Virtual Memory and Paging. t

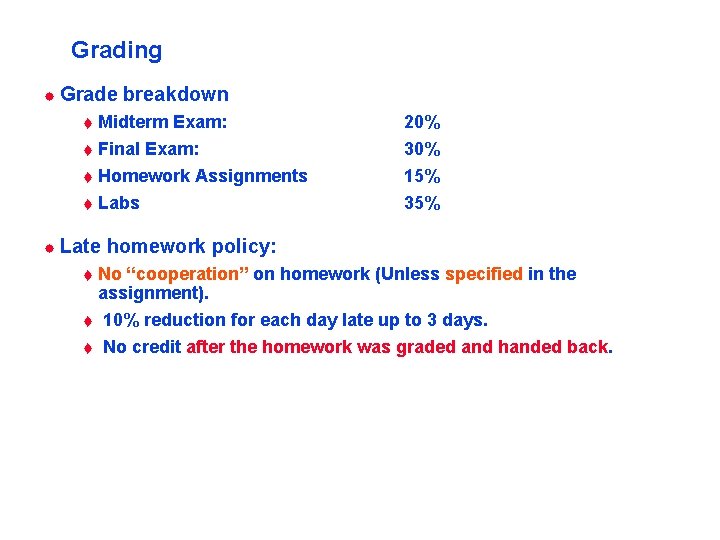

Grading ® Grade t breakdown Midterm Exam: Final Exam: t Homework Assignments t Labs t ® Late 20% 30% 15% 35% homework policy: No “cooperation” on homework (Unless specified in the assignment). t 10% reduction for each day late up to 3 days. t No credit after the homework was graded and handed back. t

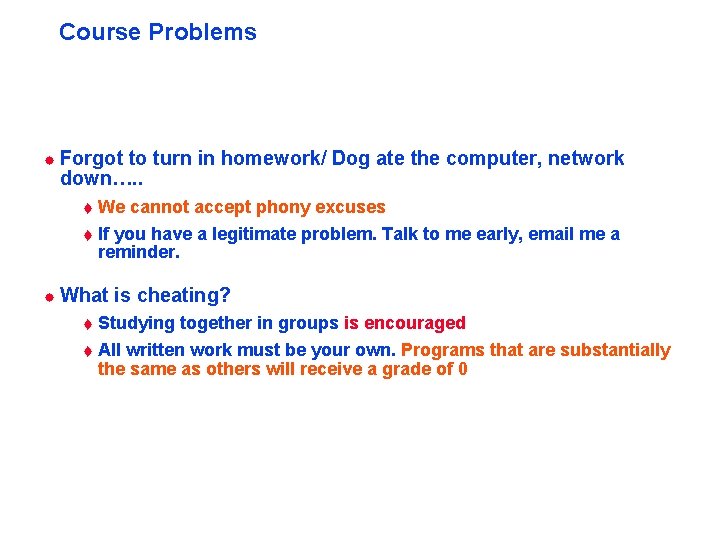

Course Problems ® Forgot to turn in homework/ Dog ate the computer, network down…. . t We cannot accept phony excuses t If you have a legitimate problem. Talk to me early, email me a reminder. ® What is cheating? Studying together in groups is encouraged t All written work must be your own. Programs that are substantially the same as others will receive a grade of 0 t

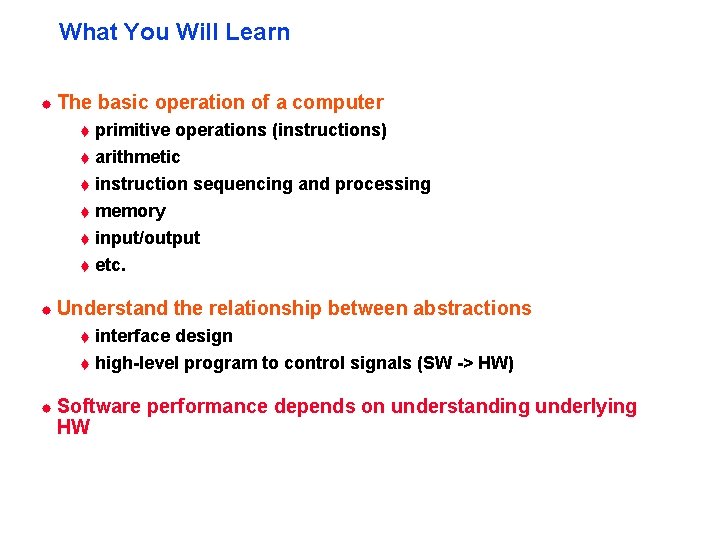

What You Will Learn ® The basic operation of a computer t primitive operations (instructions) arithmetic t instruction sequencing and processing t memory t input/output t etc. t ® Understand the relationship between abstractions t interface design t high-level program to control signals (SW -> HW) ® Software HW performance depends on understanding underlying

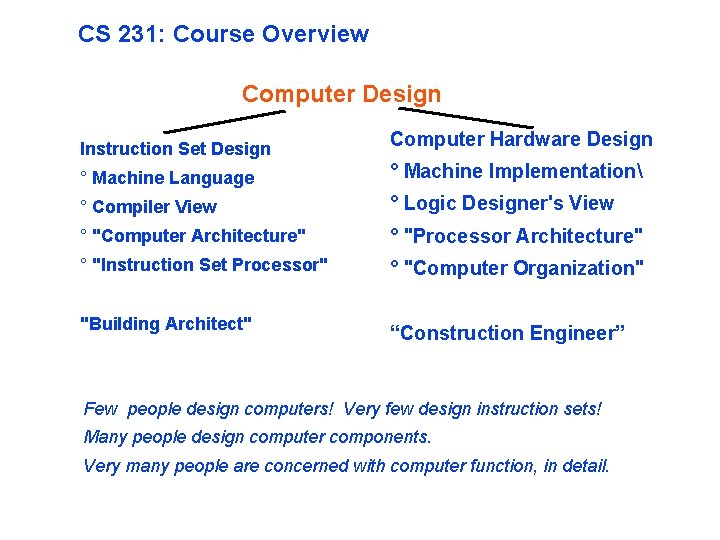

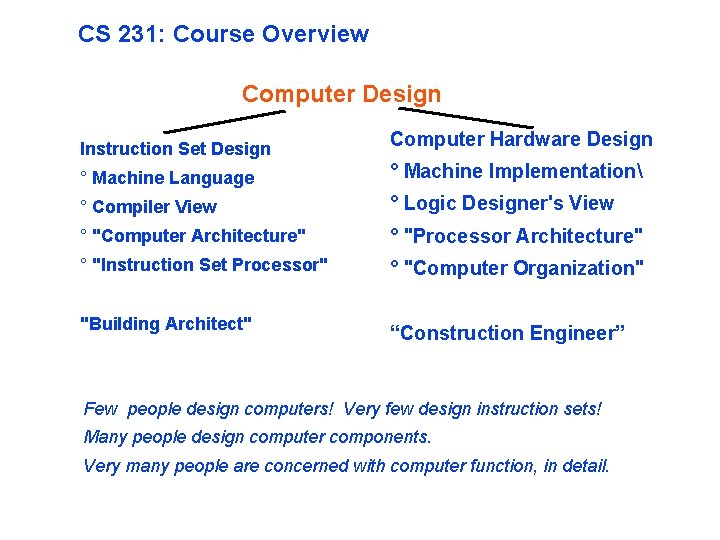

CS 231: Course Overview Computer Design Instruction Set Design Computer Hardware Design ° Machine Language ° Machine Implementation ° Compiler View ° Logic Designer's View ° "Computer Architecture" ° "Processor Architecture" ° "Instruction Set Processor" ° "Computer Organization" "Building Architect" “Construction Engineer” Few people design computers! Very few design instruction sets! Many people design computer components. Very many people are concerned with computer function, in detail.

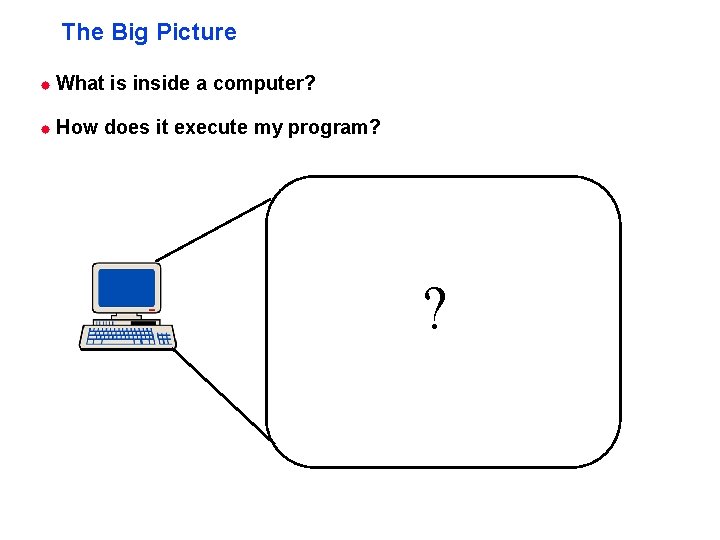

The Big Picture ® What ® How is inside a computer? does it execute my program? ?

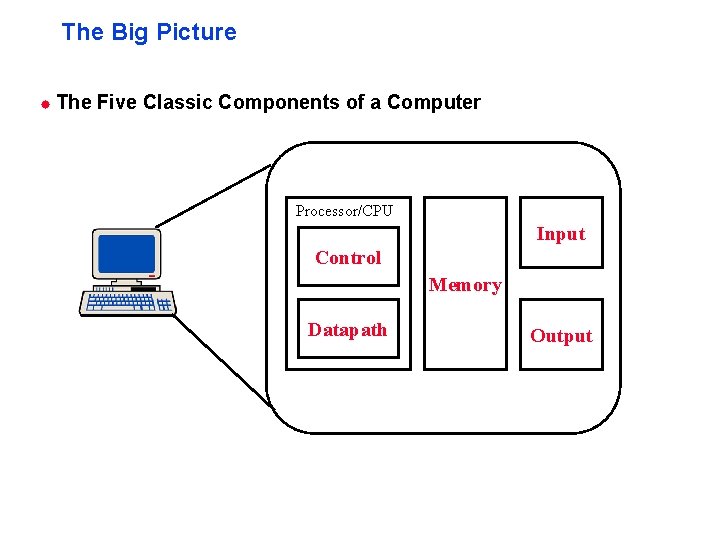

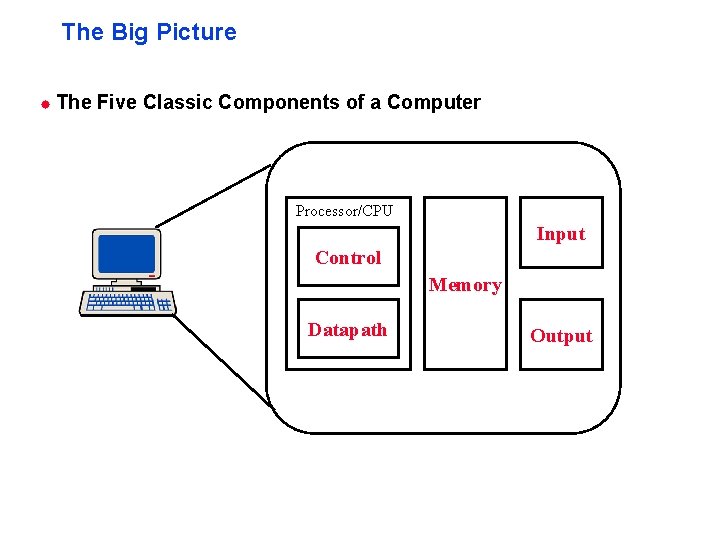

The Big Picture ® The Five Classic Components of a Computer Processor/CPU Input Control Memory Datapath Output

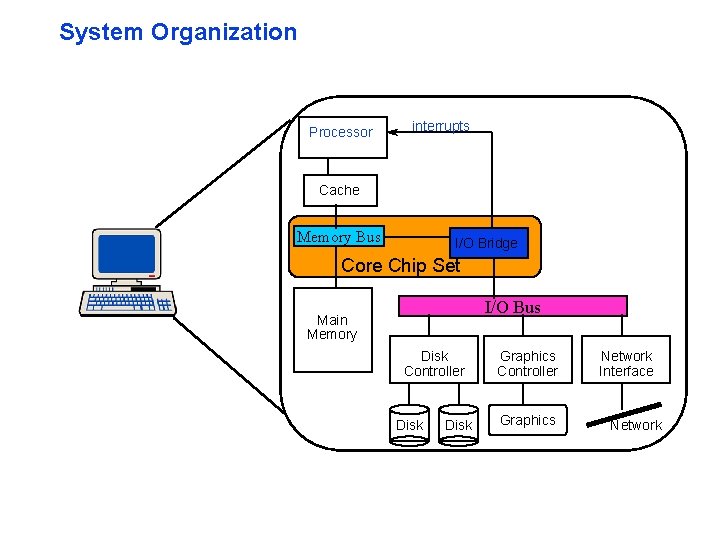

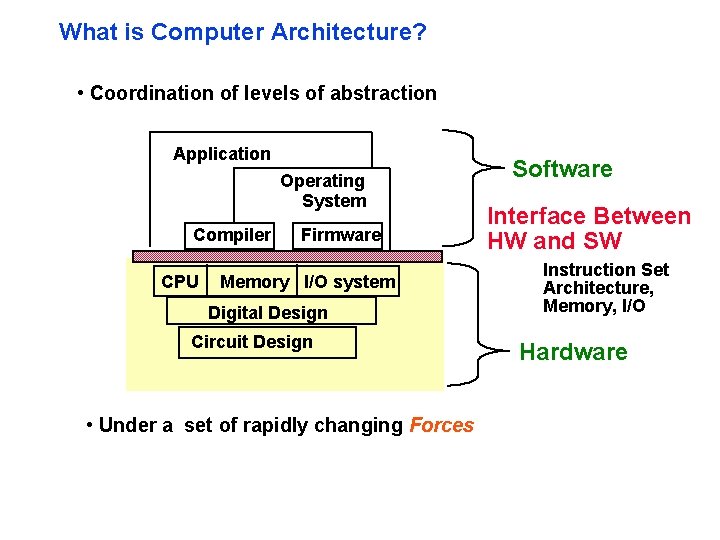

System Organization Processor interrupts Cache Memory Bus I/O Bridge Core Chip Set I/O Bus Main Memory Disk Controller Disk Graphics Controller Graphics Network Interface Network

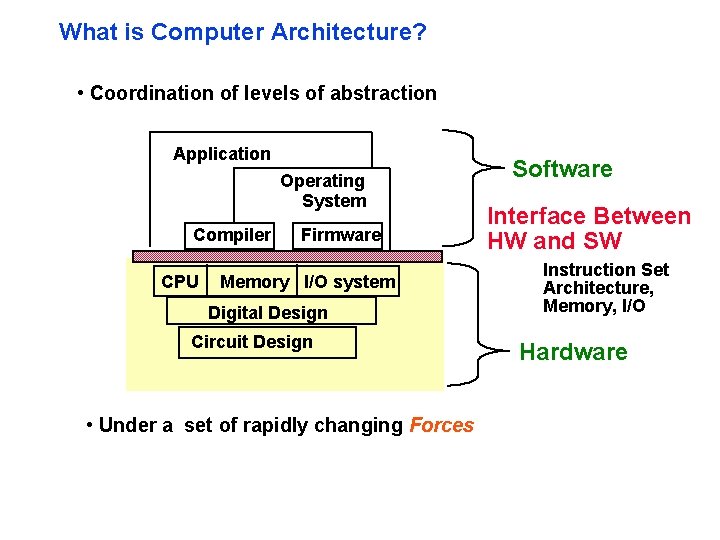

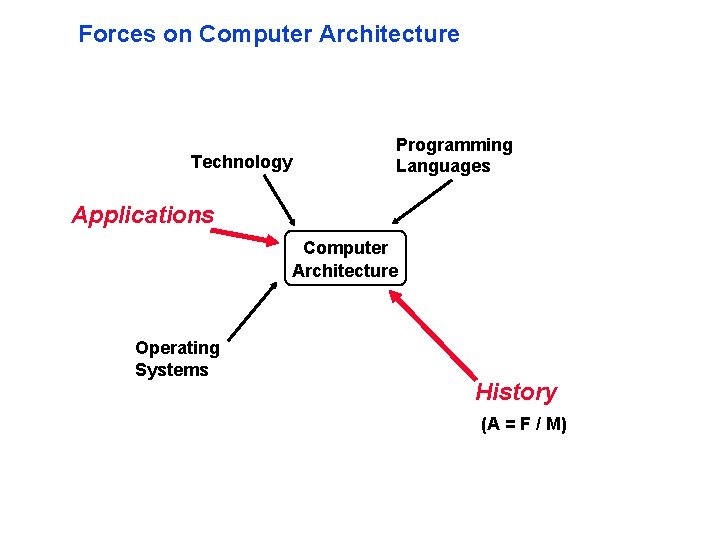

What is Computer Architecture? • Coordination of levels of abstraction Application Operating System Compiler CPU Firmware Memory I/O system Digital Design Circuit Design • Under a set of rapidly changing Forces Software Interface Between HW and SW Instruction Set Architecture, Memory, I/O Hardware

![Levels of Representation temp vk High Level Language Program vk vk1 vk1 Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1]](https://slidetodoc.com/presentation_image_h2/3accde8d7ea5ded871e7a90e78711f70/image-13.jpg)

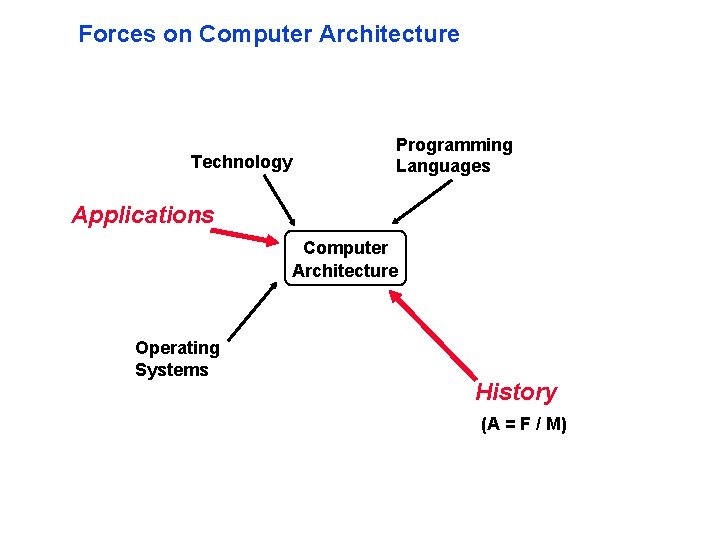

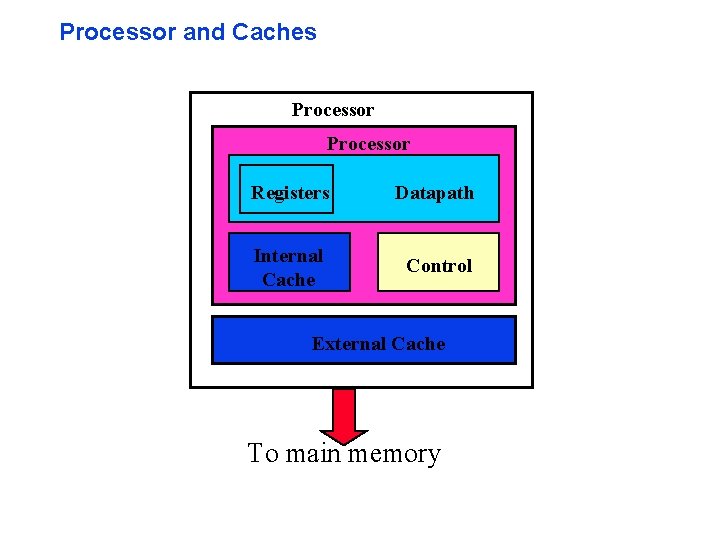

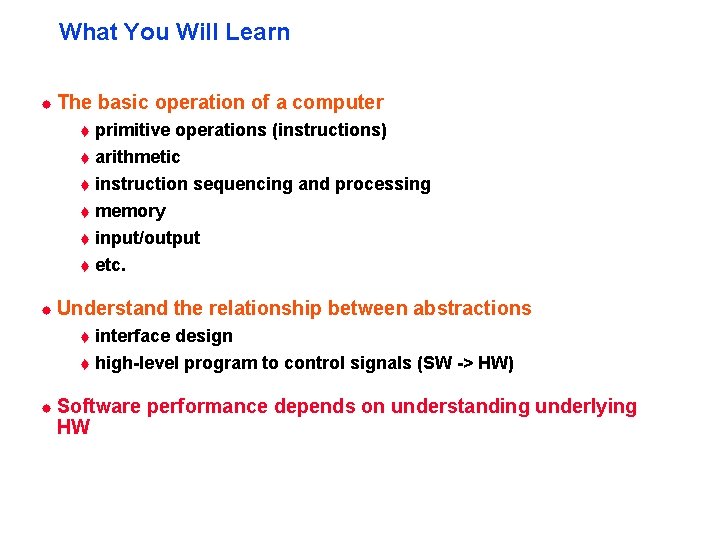

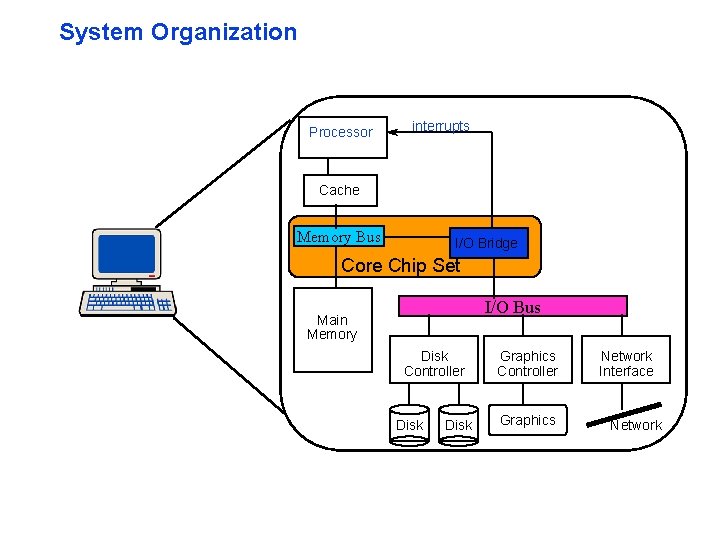

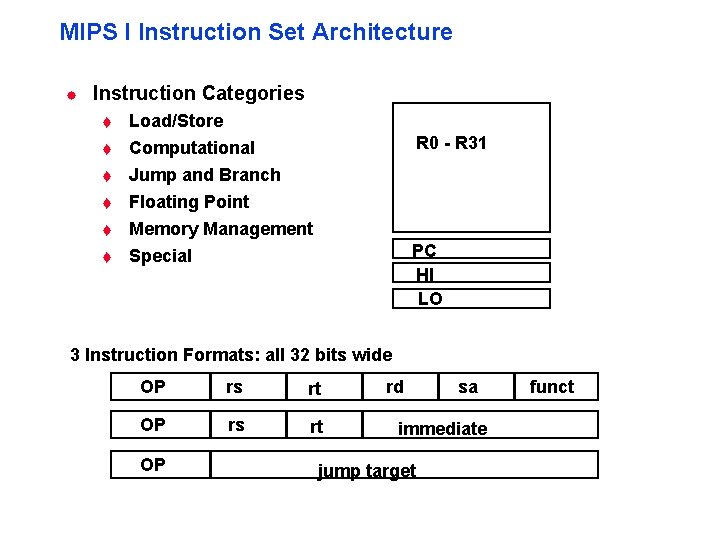

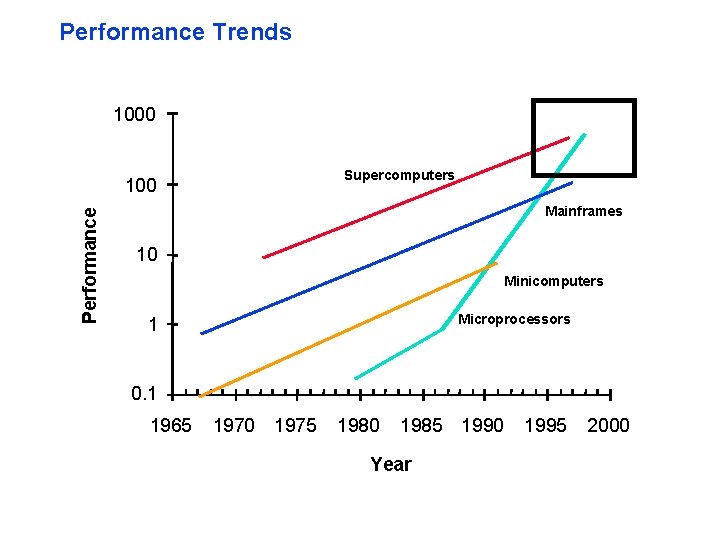

Levels of Representation temp = v[k]; High Level Language Program v[k] = v[k+1]; v[k+1] = temp; Compiler lw $15, lw $16, sw$15, Assembly Language Program Assembler Machine Language Program 0000 1010 1100 0101 Machine Interpretation Control Signal Specification 1001 1111 0110 1000 1100 0101 1010 0000 0($2) 4($2) 0110 1000 1111 1001 1010 0000 0101 1100 1111 1000 0110 0101 1100 0000 1010 1000 0110 1001 1111

Forces on Computer Architecture Technology Programming Languages Applications Computer Architecture Operating Systems History (A = F / M)

![Instruction Set Architecture the attributes of a computing system as seen by Instruction Set Architecture. . . the attributes of a [computing] system as seen by](https://slidetodoc.com/presentation_image_h2/3accde8d7ea5ded871e7a90e78711f70/image-15.jpg)

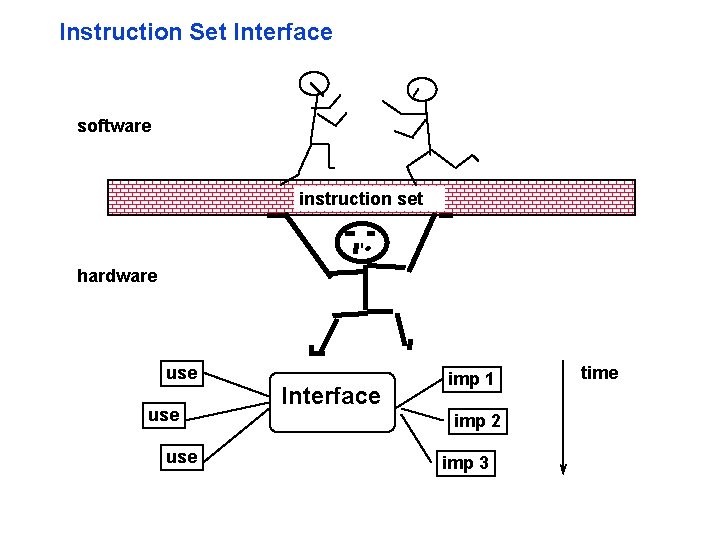

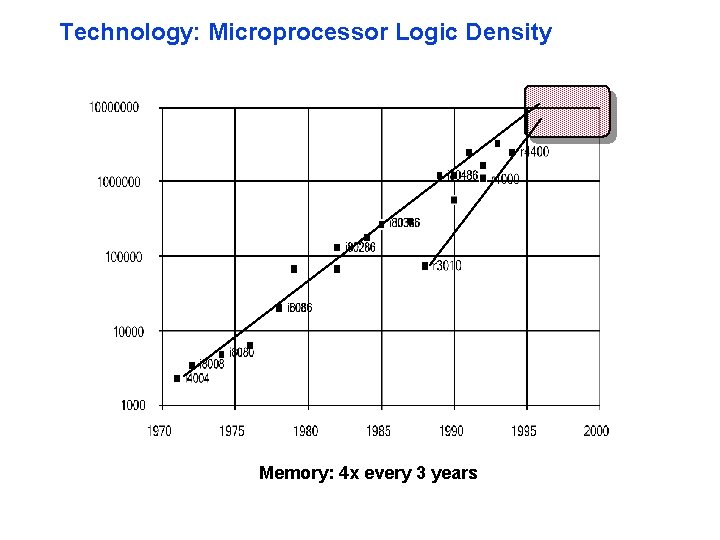

Instruction Set Architecture. . . the attributes of a [computing] system as seen by the programmer, i. e. the conceptual structure and functional behavior, as distinct from the organization of the data flows and controls the logic design, and the physical implementation. Amdahl, Blaaw, and Brooks, 1964 SOFTWARE -- Organization of Programmable Storage -- Data Types & Data Structures: Encoding & Representations -- Instruction Formats -- Instruction (or Operation Code) Set -- Modes of Addressing and Accessing Data Items and Instructions -- Exceptional Conditions

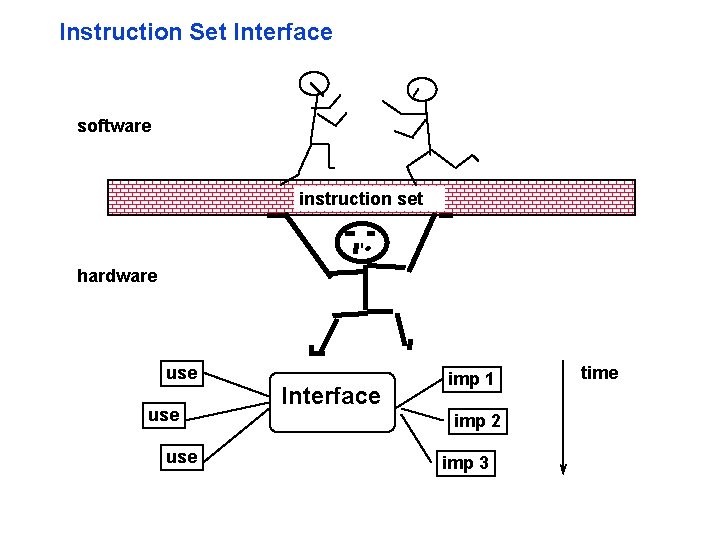

Instruction Set Interface software instruction set hardware use use Interface imp 1 imp 2 imp 3 time

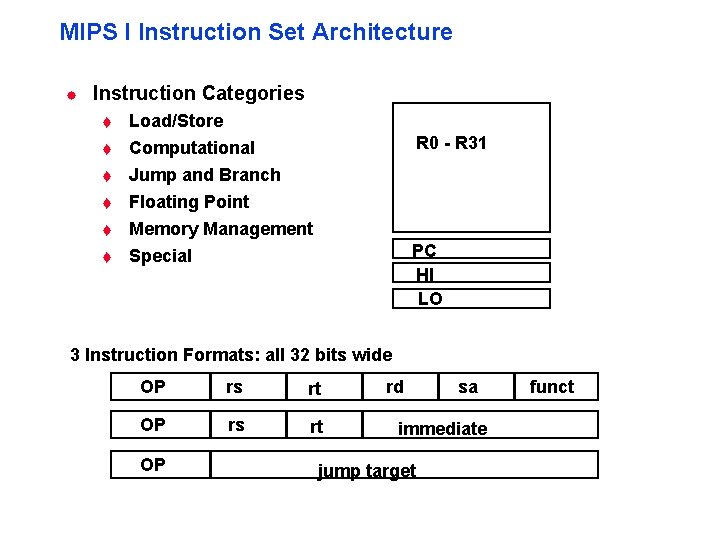

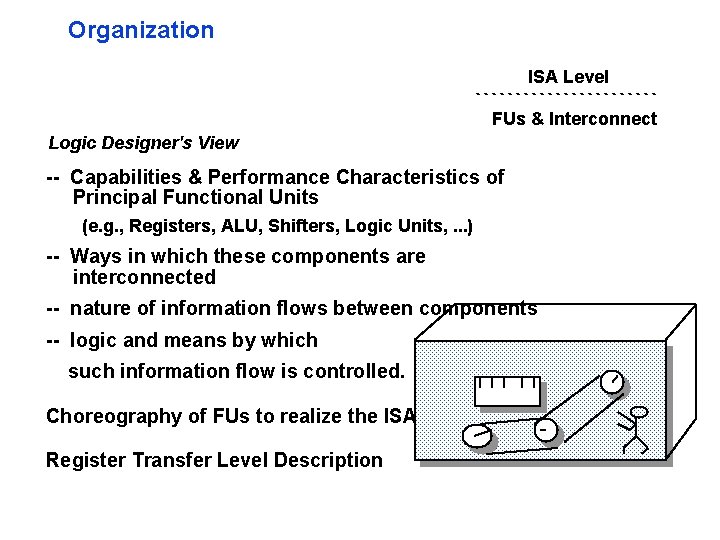

MIPS I Instruction Set Architecture ® Instruction Categories t Load/Store t Computational Jump and Branch Floating Point t t R 0 - R 31 Memory Management Special PC HI LO 3 Instruction Formats: all 32 bits wide OP rs rt OP rd sa immediate jump target funct

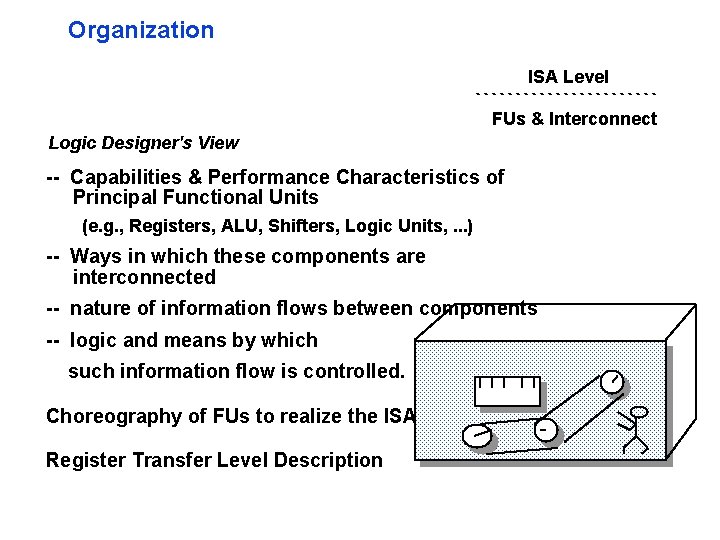

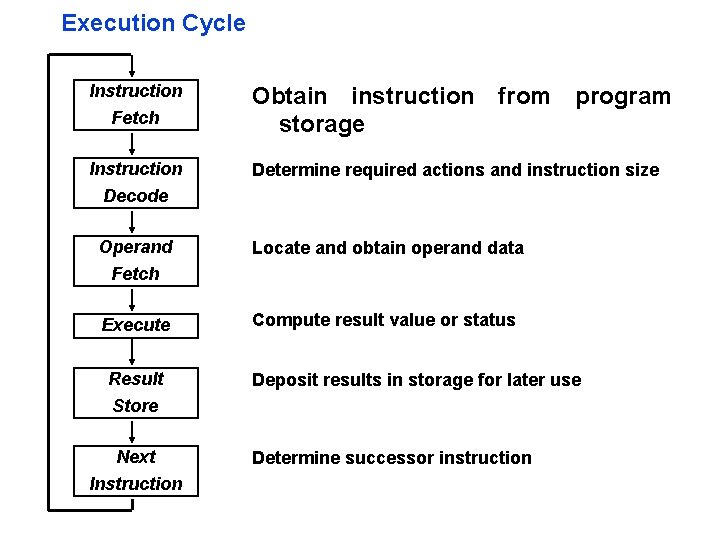

Organization ISA Level FUs & Interconnect Logic Designer's View -- Capabilities & Performance Characteristics of Principal Functional Units (e. g. , Registers, ALU, Shifters, Logic Units, . . . ) -- Ways in which these components are interconnected -- nature of information flows between components -- logic and means by which such information flow is controlled. Choreography of FUs to realize the ISA Register Transfer Level Description

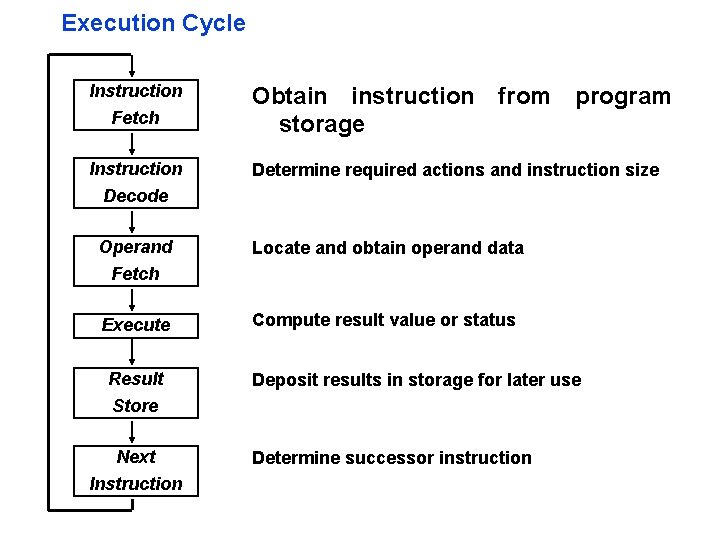

Execution Cycle Instruction Fetch Instruction Obtain instruction from program storage Determine required actions and instruction size Decode Operand Locate and obtain operand data Fetch Execute Result Compute result value or status Deposit results in storage for later use Store Next Instruction Determine successor instruction

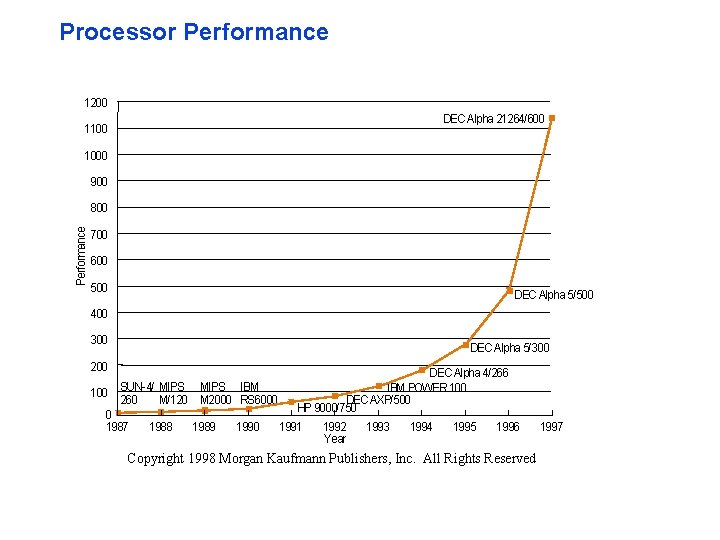

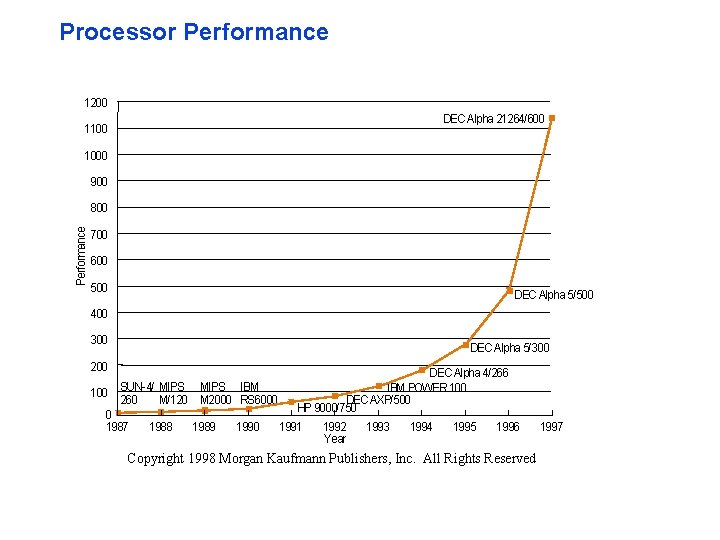

Processor Performance 1200 1100 DEC Alpha 21264/600 1000 900 Performance 800 700 600 500 DEC Alpha 5/500 400 300 DEC Alpha 5/300 200 DEC Alpha 4/266 SUN-4/ MIPS IBM POWER 100 260 M 2000 RS 6000 DEC AXP/500 M/120 HP 9000/750 0 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 Year Copyright 1998 Morgan Kaufmann Publishers, Inc. All Rights Reserved 1997

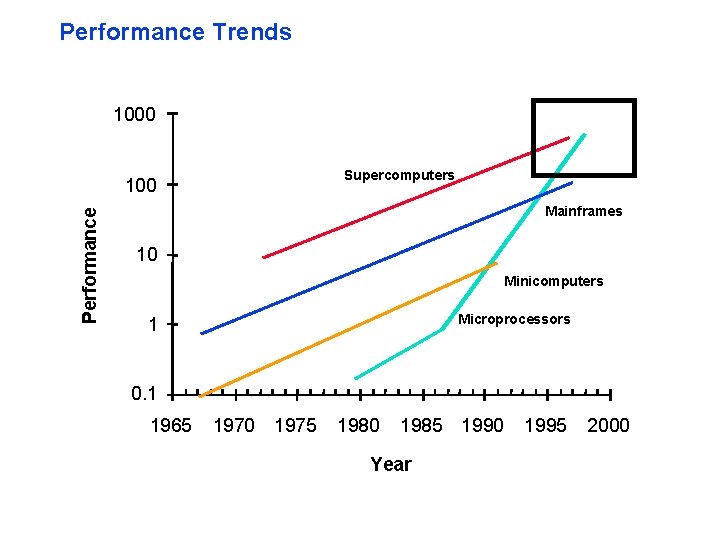

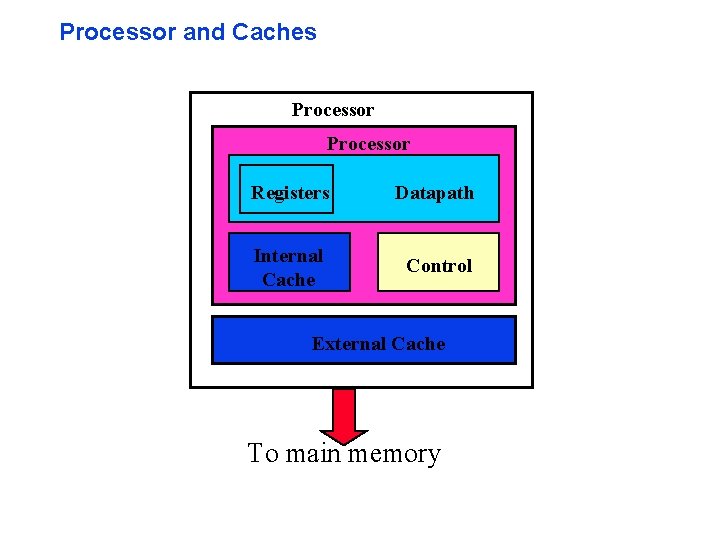

Performance Trends 1000 Supercomputers Performance 100 Mainframes 10 Minicomputers Microprocessors 1 0. 1 1965 1970 1975 1980 1985 Year 1990 1995 2000

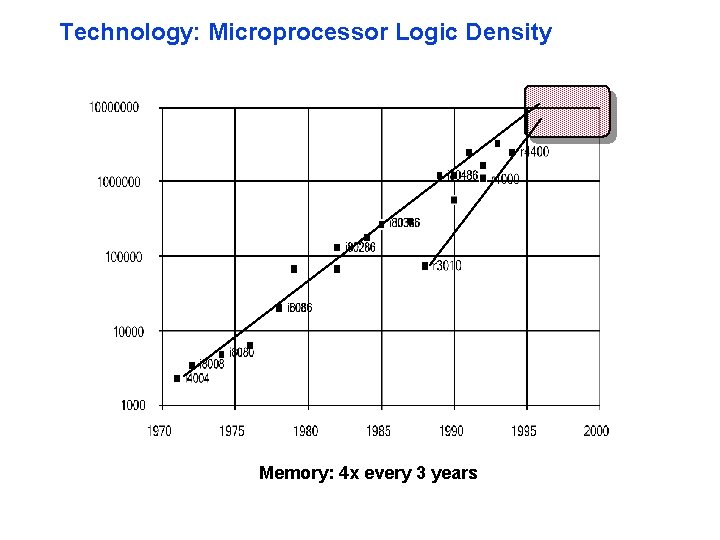

Technology: Microprocessor Logic Density Memory: 4 x every 3 years

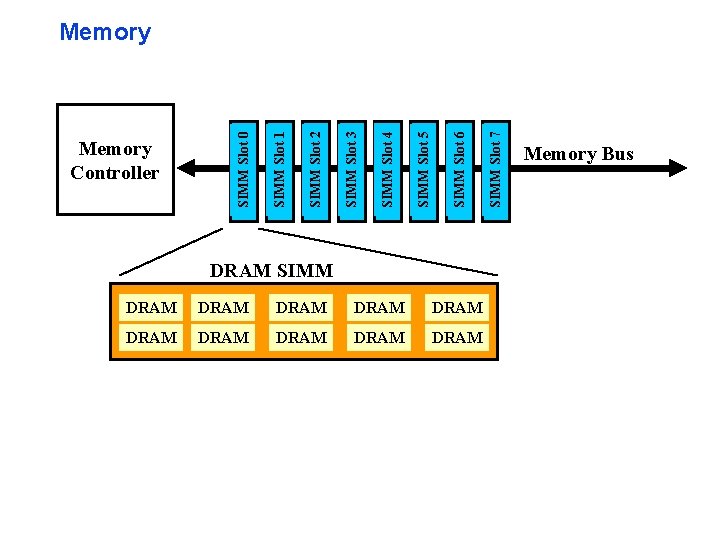

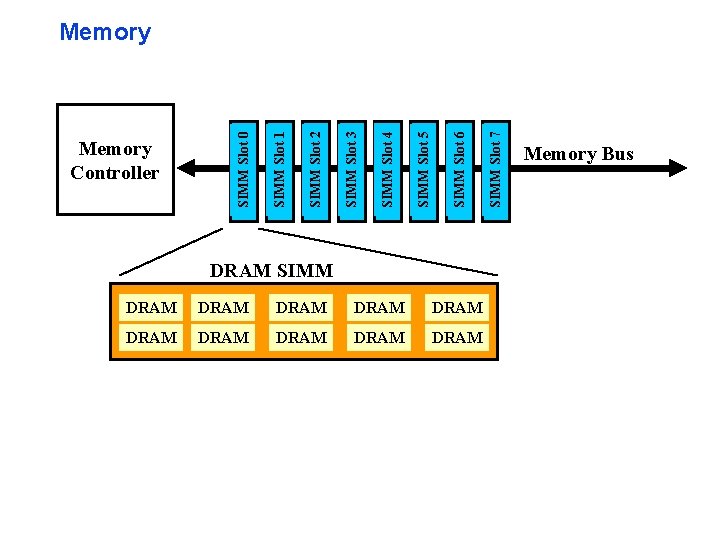

Processor and Caches Processor Module Processor Registers Datapath Internal Cache Control External Cache To main memory

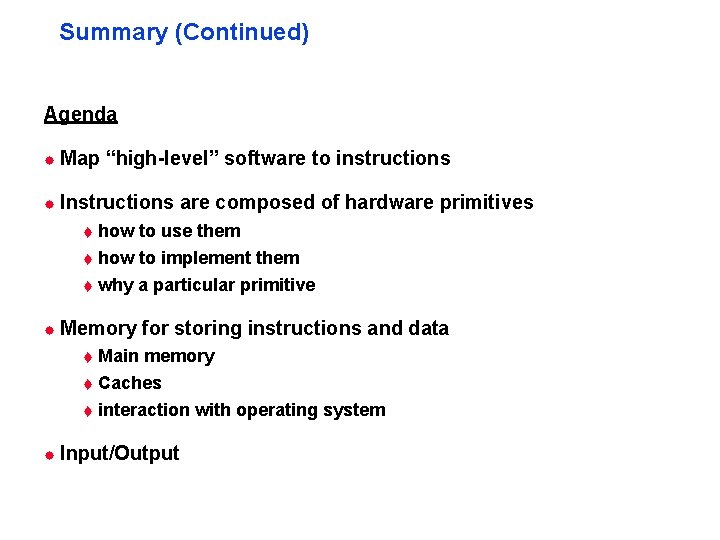

Memory Controller DRAM SIMM DRAM DRAM DRAM SIMM Slot 7 SIMM Slot 6 SIMM Slot 5 SIMM Slot 4 SIMM Slot 3 SIMM Slot 2 SIMM Slot 1 SIMM Slot 0 Memory Bus

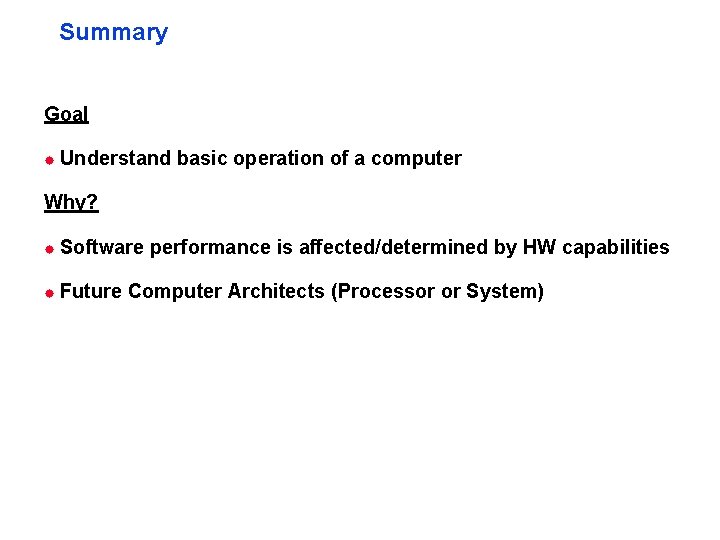

Summary Goal ® Understand basic operation of a computer Why? ® Software ® Future performance is affected/determined by HW capabilities Computer Architects (Processor or System)

Summary (Continued) Agenda ® Map “high-level” software to instructions ® Instructions are composed of hardware primitives how to use them t how to implement them t why a particular primitive t ® Memory for storing instructions and data t Main memory t Caches t interaction with operating system ® Input/Output

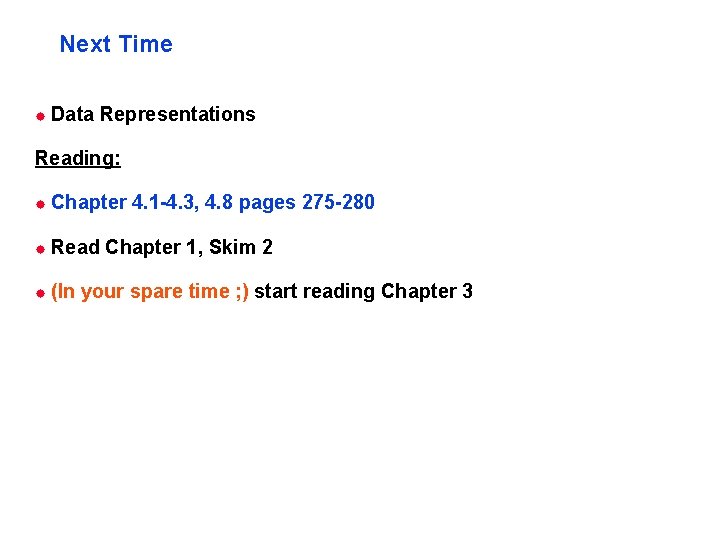

Summary (Continued) ® All computers consist of five components t Processor: (1) datapath and (2) control (3) Memory t (4) Input devices and (5) Output devices t ® Not all “memory” created equally Cache: fast (expensive, small) memory close to the processor t Main memory: slower, cheaper, larger memory farther from processor t ® Input and output (I/O) devices has the messiest organization t Wide range of speed: graphics vs. keyboard t Wide range of requirements: speed, standard, cost. . . etc.

Next Time ® Data Representations Reading: ® Chapter ® Read ® (In 4. 1 -4. 3, 4. 8 pages 275 -280 Chapter 1, Skim 2 your spare time ; ) start reading Chapter 3