CELL Processor An overview By Andy P and

CELL Processor An overview. By Andy P. and Gene D.

The Cell

Table of Contents • • Motivation Context Architecture Developing Environment

Motivation • Rising power needs are limiting the increases in speed. • Transistors can no long handle the heat generated by the power demands. • Intel and AMD have already introduced dual-core processor.

Context • Multiprocessors are the way of the future • The Cell is a unique approach – Nine cores. – 1 Power Processing Unit (PPU) – 8 Synergistic Processing Units (SPU) – Elements connected together by the Internal Element Interconnect Bus (EIB)

PPU • • Dual-threaded 64 -Bit Power PC core. L 2 512 kb Cache. Direct access to system memory. Responsible for running the OS and coordination of the SPUs.

SPUs • Synergistic Processing Units • 256 kb of local store, no cache. • Access to system memory must be handled through DMA via the Memory Flow Controller (MFC).

CELL Architecture Overview

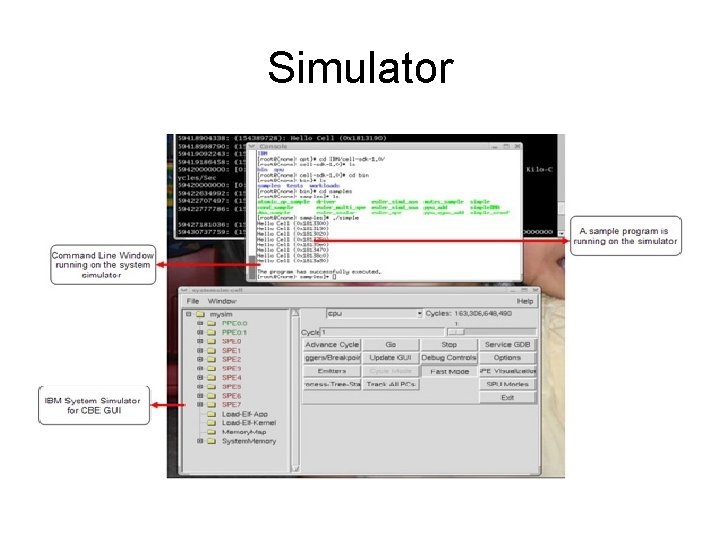

CELL Simulator • IBM produced a program which simulates the CELL processor. • Runs on Red. Hat Fedora. • It’s FREE. • Language – C

Simulator

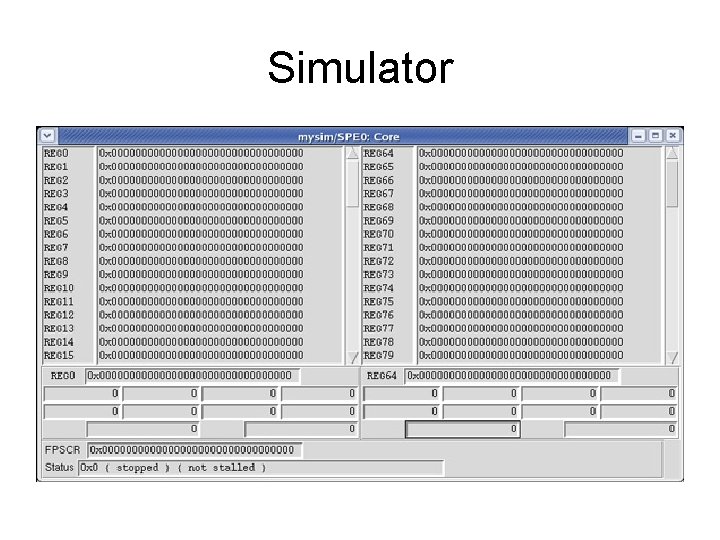

Simulator

FFTs on the CELL • The CELL environment offers up the potential for strong use of parallelization. • FFTs have the potential to take advantage of this attribute if the algorithm is modified correctly.

Questions?

- Slides: 13