CDC aware power reduction for Soft IPs Ritesh

- Slides: 11

CDC aware power reduction for Soft IPs Ritesh Agarwal (Freescale™) Amit Goldie (Atrenta) Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2006. DAC 2014 - IP Track Submission

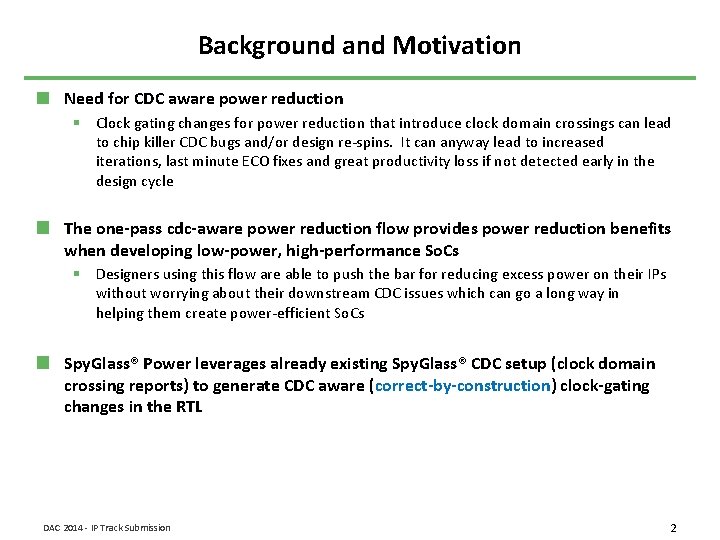

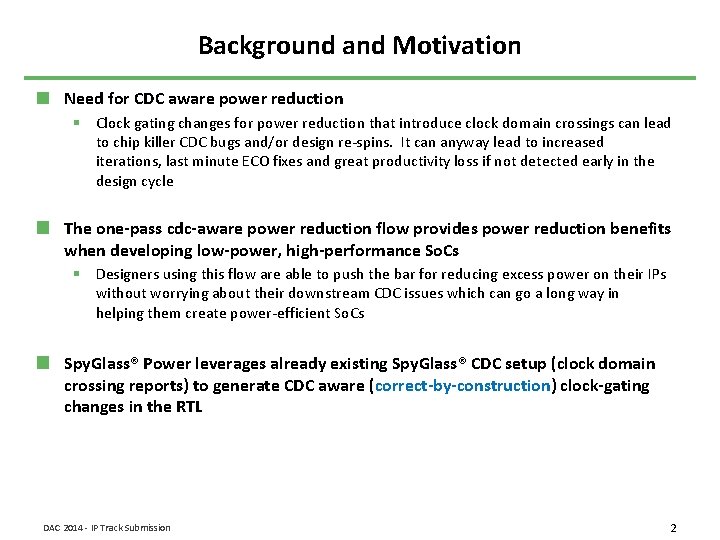

Background and Motivation Need for CDC aware power reduction § Clock gating changes for power reduction that introduce clock domain crossings can lead to chip killer CDC bugs and/or design re-spins. It can anyway lead to increased iterations, last minute ECO fixes and great productivity loss if not detected early in the design cycle The one-pass cdc-aware power reduction flow provides power reduction benefits when developing low-power, high-performance So. Cs § Designers using this flow are able to push the bar for reducing excess power on their IPs without worrying about their downstream CDC issues which can go a long way in helping them create power-efficient So. Cs Spy. Glass® Power leverages already existing Spy. Glass® CDC setup (clock domain crossing reports) to generate CDC aware (correct-by-construction) clock-gating changes in the RTL DAC 2014 - IP Track Submission 2

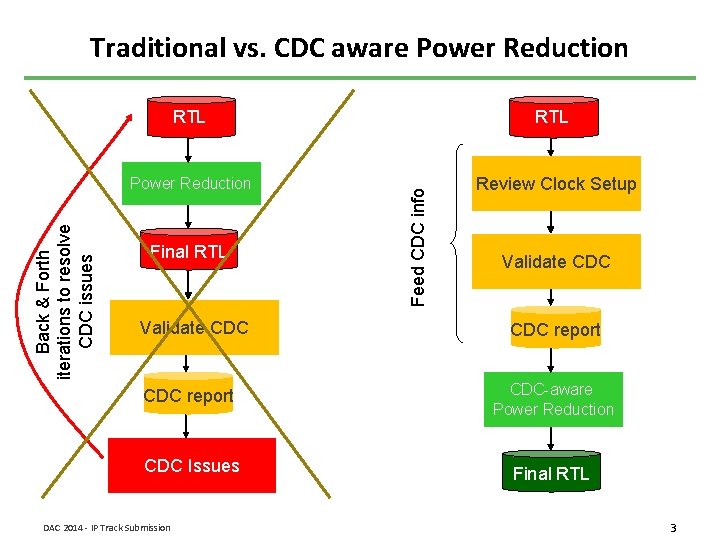

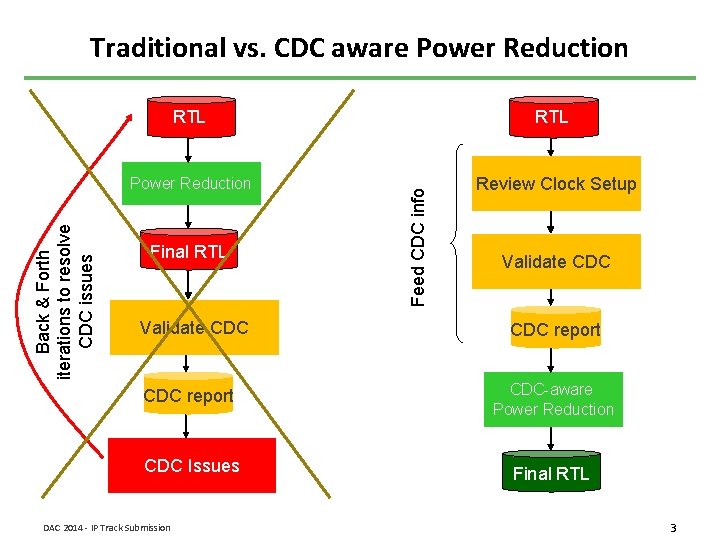

Traditional vs. CDC aware Power Reduction Back & Forth iterations to resolve CDC issues Power Reduction Final RTL Validate CDC RTL Feed CDC info RTL Review Clock Setup Validate CDC report CDC-aware Power Reduction CDC Issues Final RTL DAC 2014 - IP Track Submission 3

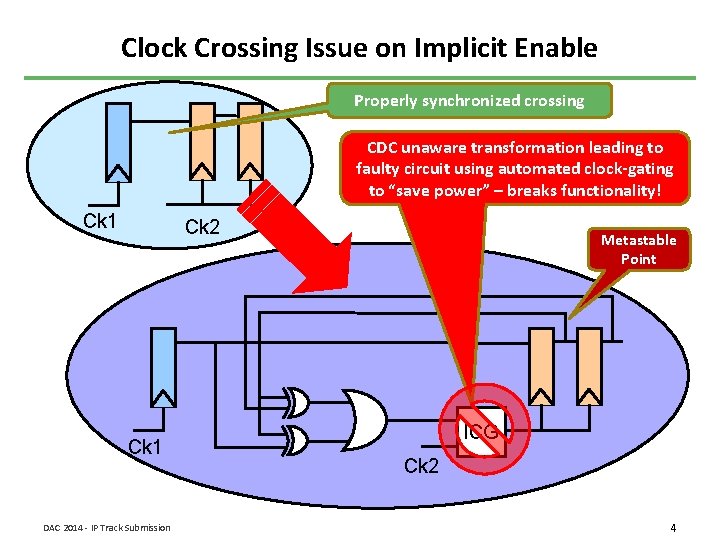

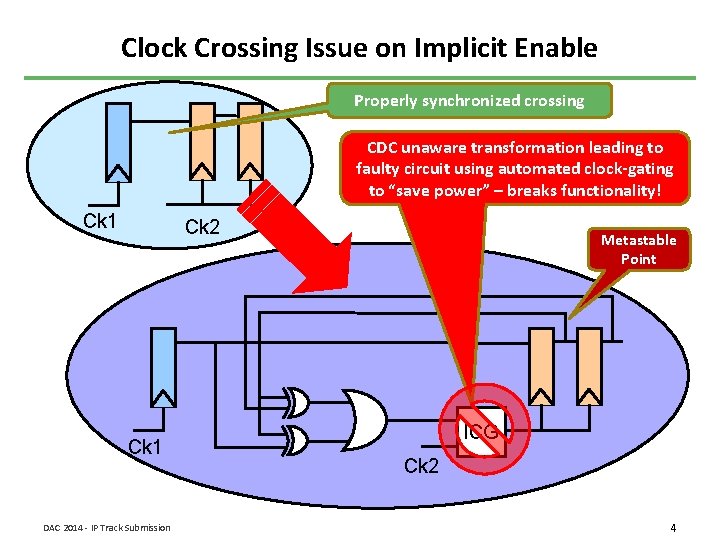

Clock Crossing Issue on Implicit Enable Properly synchronized crossing CDC unaware transformation leading to faulty circuit using automated clock-gating to “save power” – breaks functionality! Ck 1 Ck 2 Ck 1 DAC 2014 - IP Track Submission Metastable Point ICG Ck 2 4

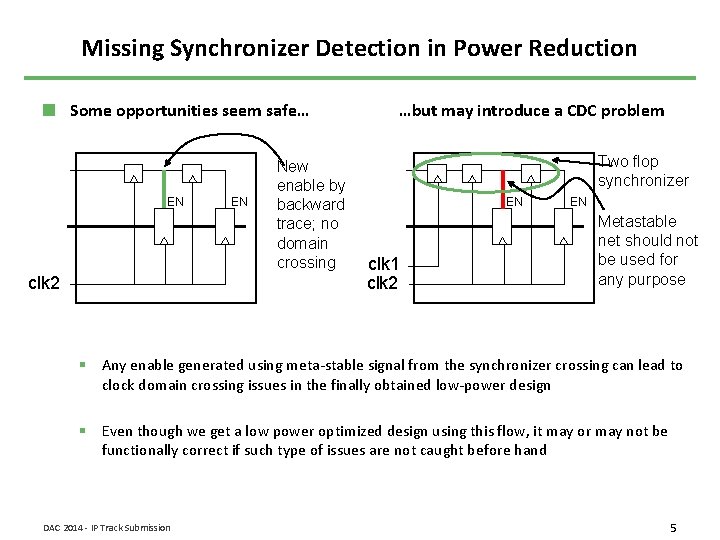

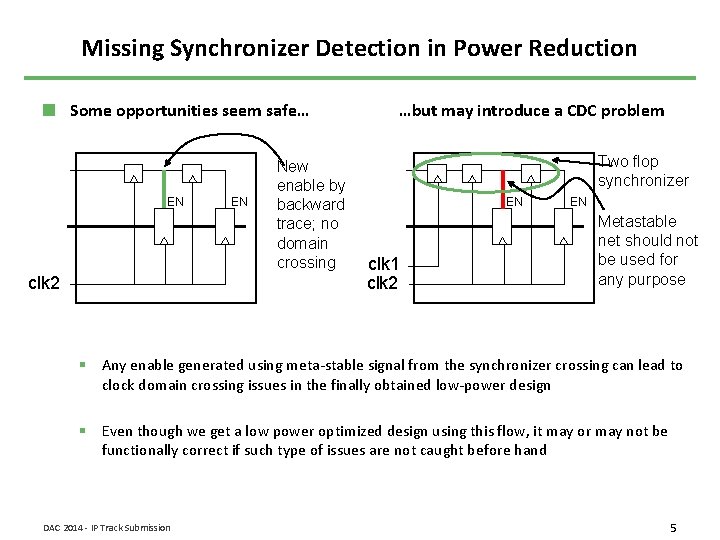

Missing Synchronizer Detection in Power Reduction Some opportunities seem safe… EN clk 2 EN New enable by backward trace; no domain crossing …but may introduce a CDC problem Two flop synchronizer EN clk 1 clk 2 EN Metastable net should not be used for any purpose § Any enable generated using meta-stable signal from the synchronizer crossing can lead to clock domain crossing issues in the finally obtained low-power design § Even though we get a low power optimized design using this flow, it may or may not be functionally correct if such type of issues are not caught before hand DAC 2014 - IP Track Submission 5

Enabling CDC-aware Power Reduction Flow Feed CDC info RTL Review Clock Setup Validate CDC report CDC-aware Power Reduction Scenario where meta-stable net is suitable for a new enable is uncommon, but not impossible Spy. Glass® CDC detects common synchronizers with no additional setup With proper CDC setup, tool can detect any custom/unusual synchronizer such as mux -based, enable-based synchronizers etc Spy. Glass® Power can make use of CDC reports to identify low power, CDC safe gating opportunities Final RTL DAC 2014 - IP Track Submission 6

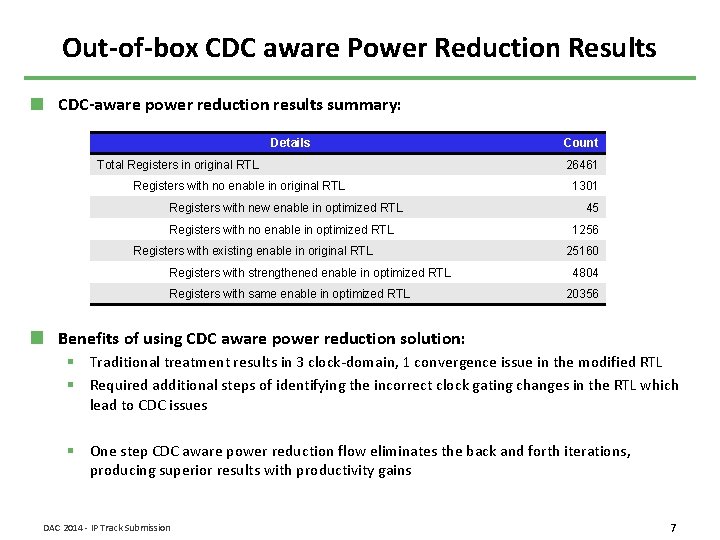

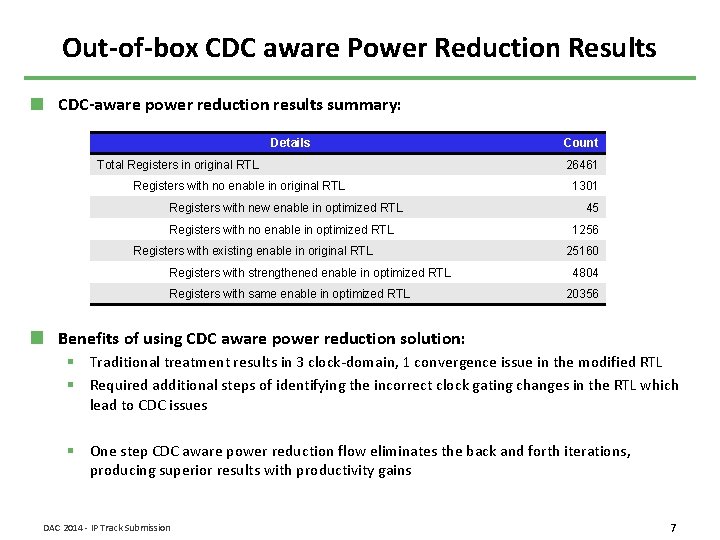

Out-of-box CDC aware Power Reduction Results CDC-aware power reduction results summary: Details Total Registers in original RTL Registers with no enable in original RTL Registers with new enable in optimized RTL Registers with no enable in optimized RTL Registers with existing enable in original RTL Registers with strengthened enable in optimized RTL Registers with same enable in optimized RTL Count 26461 1301 45 1256 25160 4804 20356 Benefits of using CDC aware power reduction solution: § Traditional treatment results in 3 clock-domain, 1 convergence issue in the modified RTL § Required additional steps of identifying the incorrect clock gating changes in the RTL which lead to CDC issues § One step CDC aware power reduction flow eliminates the back and forth iterations, producing superior results with productivity gains DAC 2014 - IP Track Submission 7

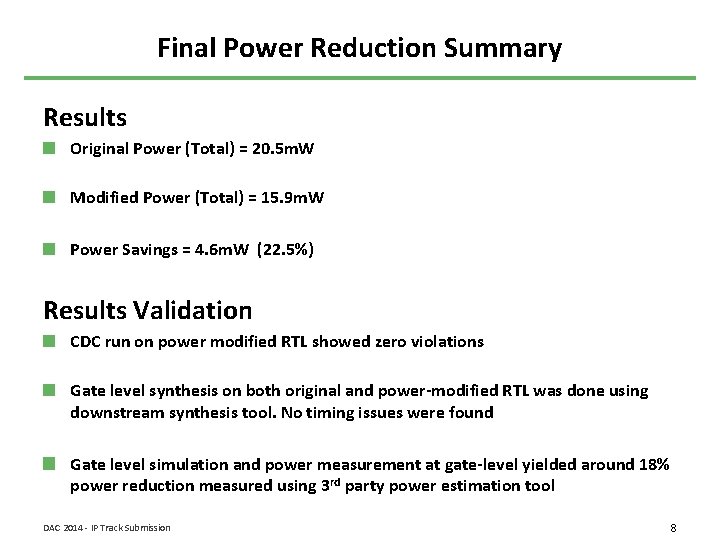

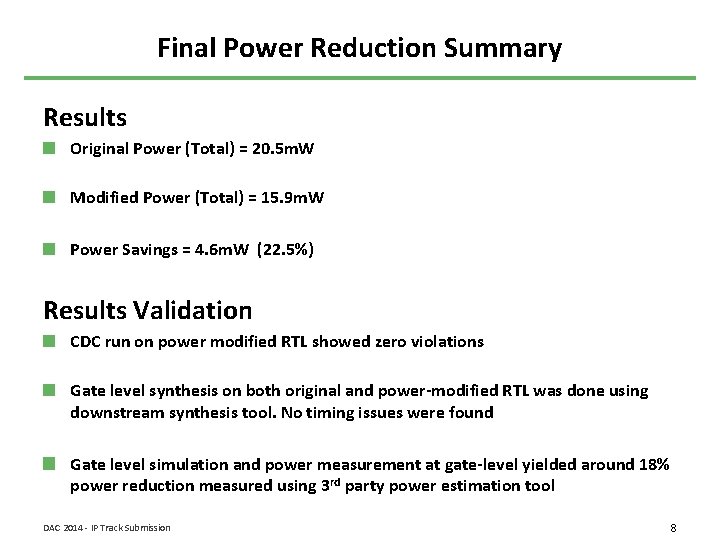

Final Power Reduction Summary Results Original Power (Total) = 20. 5 m. W Modified Power (Total) = 15. 9 m. W Power Savings = 4. 6 m. W (22. 5%) Results Validation CDC run on power modified RTL showed zero violations Gate level synthesis on both original and power-modified RTL was done using downstream synthesis tool. No timing issues were found Gate level simulation and power measurement at gate-level yielded around 18% power reduction measured using 3 rd party power estimation tool DAC 2014 - IP Track Submission 8

Conclusion One-pass cdc-aware power reduction flow generates correct-by-construction clock-gating changes in the RTL to deliver smart and reliable power savings Need for several back-and-forth design iterations can be completely avoided usingle pass cdc-aware power reduction methodology as described earlier Leads to greater designer confidence on the clock-gating changes recommended by the tool With power efficient IPs, creating low-power, high performance So. Cs becomes increasingly viable DAC 2014 - IP Track Submission 9

Future Work Automatically detect reset crossings from existing Spy. Glass® CDC reports § Exclude meta-stable reset signals from participating in generation of clock-gating enable logic Not using asynchronous resets as a part of clock-gating enable equations for Observability based clock-gating power reduction changes DAC 2014 - IP Track Submission 10

Thanks DAC 2014 - IP Track Submission 11