CDA 3101 Spring 2016 Introduction to Computer Organization

![New Topic: Exceptions Definition: Event causes unexpected transfer of control Types: (1) Exception [overflow] New Topic: Exceptions Definition: Event causes unexpected transfer of control Types: (1) Exception [overflow]](https://slidetodoc.com/presentation_image_h2/93583398047f0ca8f728eadf3a6a440c/image-12.jpg)

![Exception Detection • Undefined Instruction: 1. Add State 10 [Exception] to Finite-State Control 2. Exception Detection • Undefined Instruction: 1. Add State 10 [Exception] to Finite-State Control 2.](https://slidetodoc.com/presentation_image_h2/93583398047f0ca8f728eadf3a6a440c/image-13.jpg)

- Slides: 21

CDA 3101 Spring 2016 Introduction to Computer Organization Microprogramming and Exceptions 08 March 2016

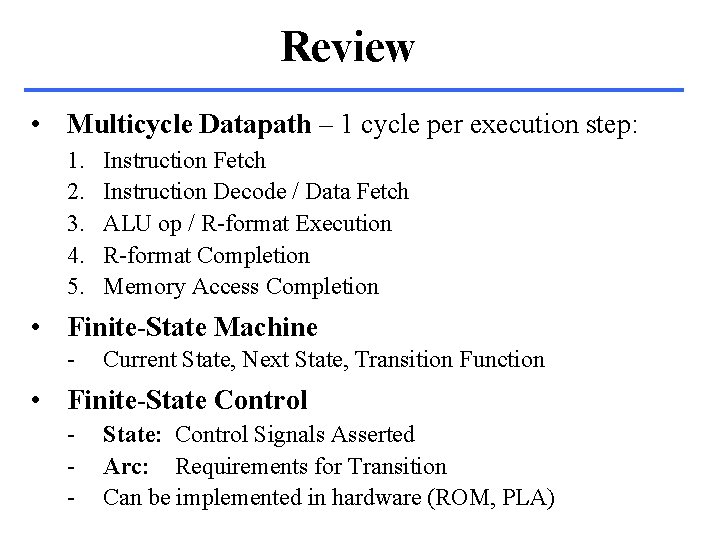

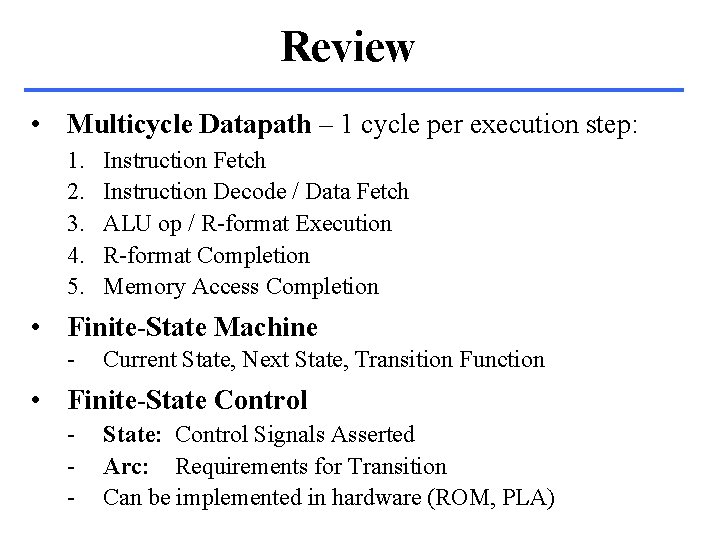

Review • Multicycle Datapath – 1 cycle per execution step: 1. 2. 3. 4. 5. Instruction Fetch Instruction Decode / Data Fetch ALU op / R-format Execution R-format Completion Memory Access Completion • Finite-State Machine - Current State, Next State, Transition Function • Finite-State Control - State: Control Signals Asserted Arc: Requirements for Transition Can be implemented in hardware (ROM, PLA)

Overview • Problems with Finite-State Control - Real processors have Hundreds of States - Thousands of interactions between states - FSC graphical design too small for realistic architectures • Solution: Microprogramming - Software-based control design - Control signals => fields in microinstruction - Sequence microinstructions => microprogram • Challenges of Microprogramming - Microinstruction design and sequencing - Exception handling

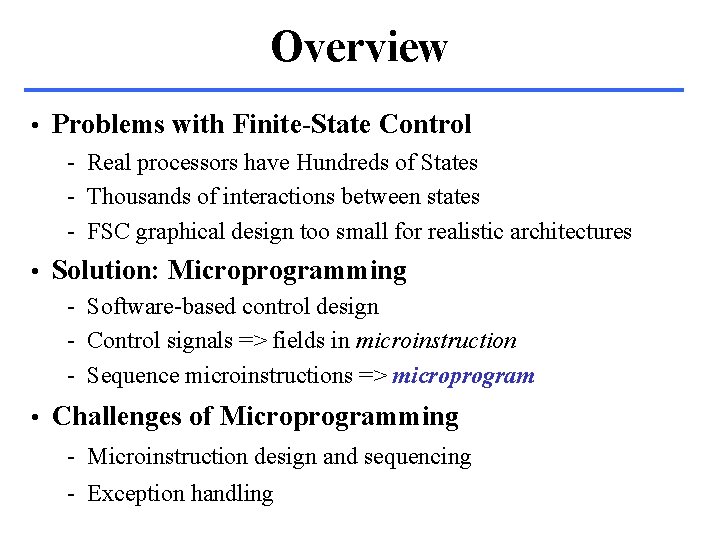

MIPS Microinstruction Format Microinstruction: Abstraction of datapath control Field Specifies • ALU control ALUop for this clock cycle • SRC 1 Source for first ALU operand • SRC 2 Source for second ALU operand • Register Control Register read/write, data value written • Memory read/write, data value written Destination register for Mem. Read • PCWrite control Source for PC (PC+4, BTA, JTA) • Sequencing How to choose next microinstruction

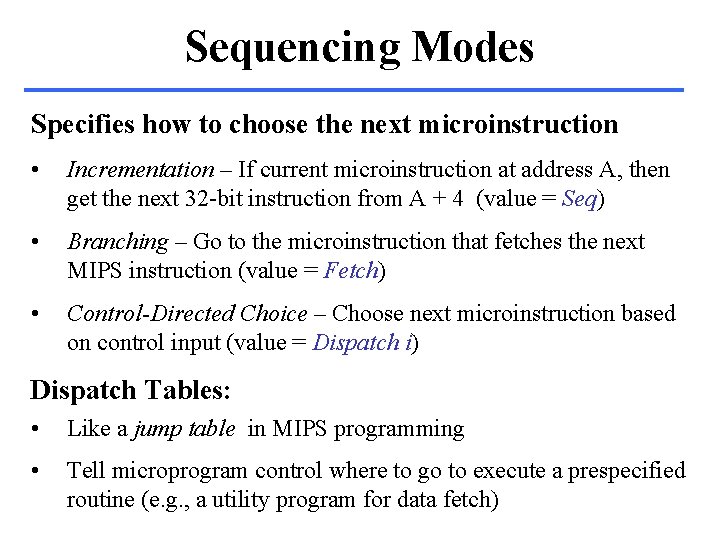

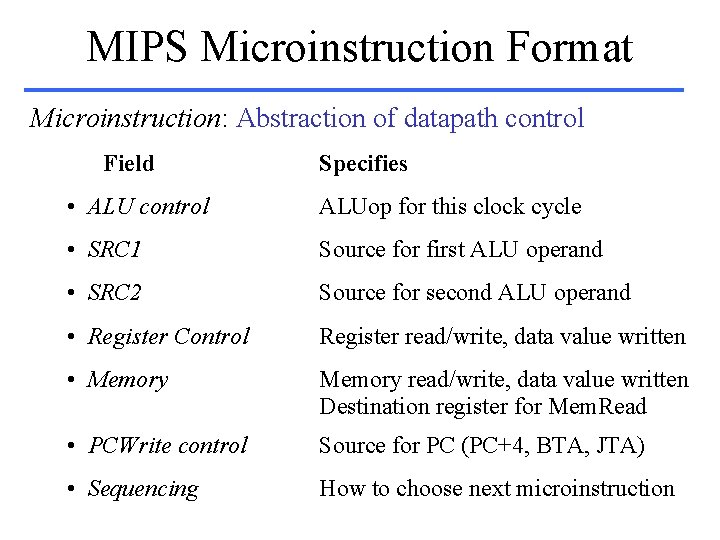

Sequencing Modes Specifies how to choose the next microinstruction • Incrementation – If current microinstruction at address A, then get the next 32 -bit instruction from A + 4 (value = Seq) • Branching – Go to the microinstruction that fetches the next MIPS instruction (value = Fetch) • Control-Directed Choice – Choose next microinstruction based on control input (value = Dispatch i) Dispatch Tables: • Like a jump table in MIPS programming • Tell microprogram control where to go to execute a prespecified routine (e. g. , a utility program for data fetch)

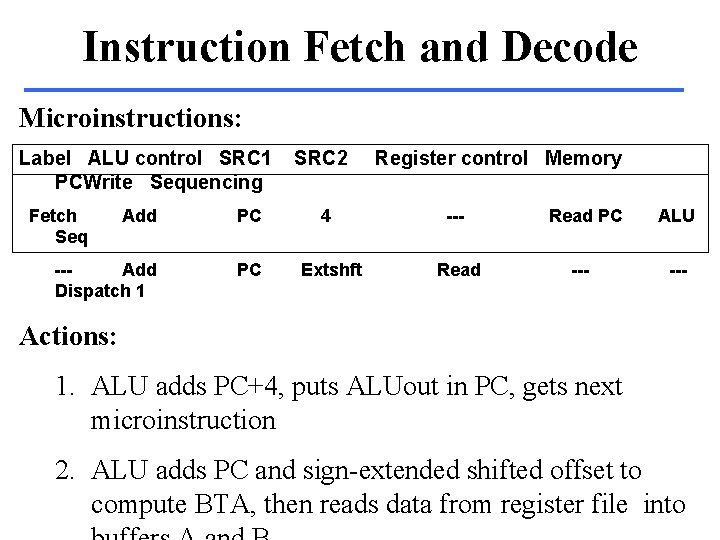

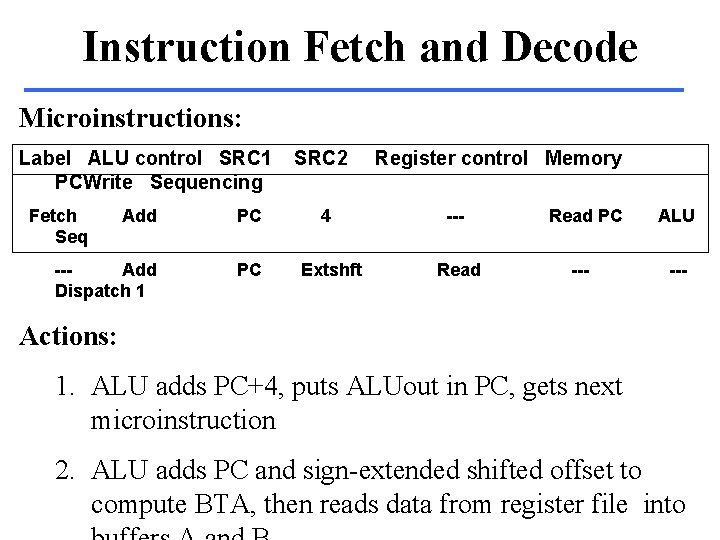

Instruction Fetch and Decode Microinstructions: Label ALU control SRC 1 PCWrite Sequencing Fetch Seq Add PC --Add Dispatch 1 PC SRC 2 4 Extshft Register control Memory --Read PC --- ALU --- Actions: 1. ALU adds PC+4, puts ALUout in PC, gets next microinstruction 2. ALU adds PC and sign-extended shifted offset to compute BTA, then reads data from register file into

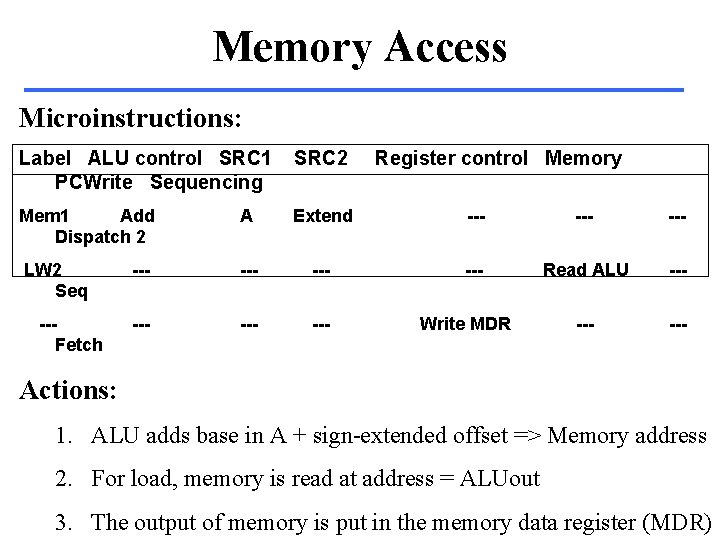

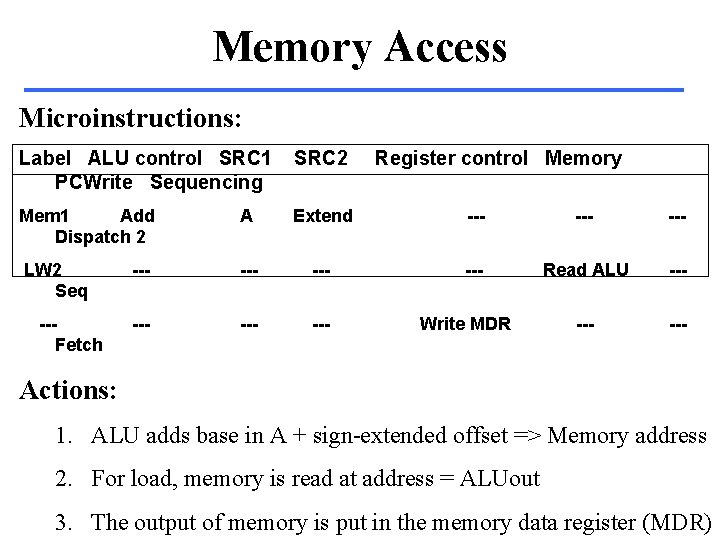

Memory Access Microinstructions: Label ALU control SRC 1 PCWrite Sequencing SRC 2 Mem 1 Add Dispatch 2 A Extend --- --- LW 2 Seq --- --- Read ALU --- --- --- --Fetch Register control Memory Write MDR Actions: 1. ALU adds base in A + sign-extended offset => Memory address 2. For load, memory is read at address = ALUout 3. The output of memory is put in the memory data register (MDR)

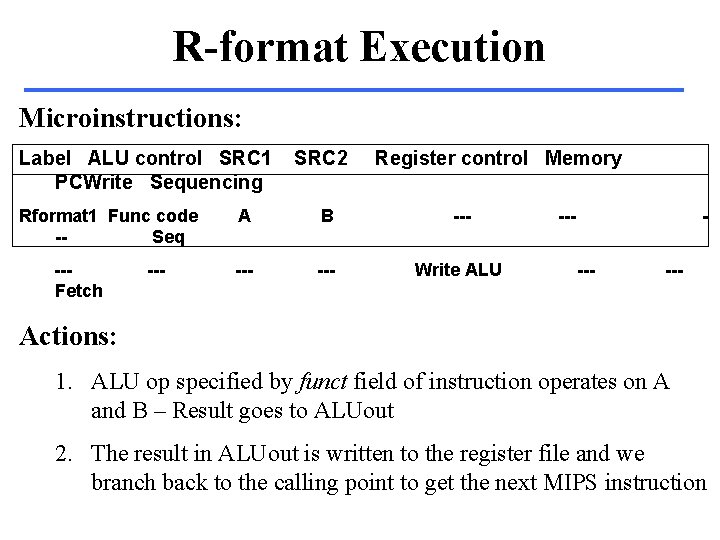

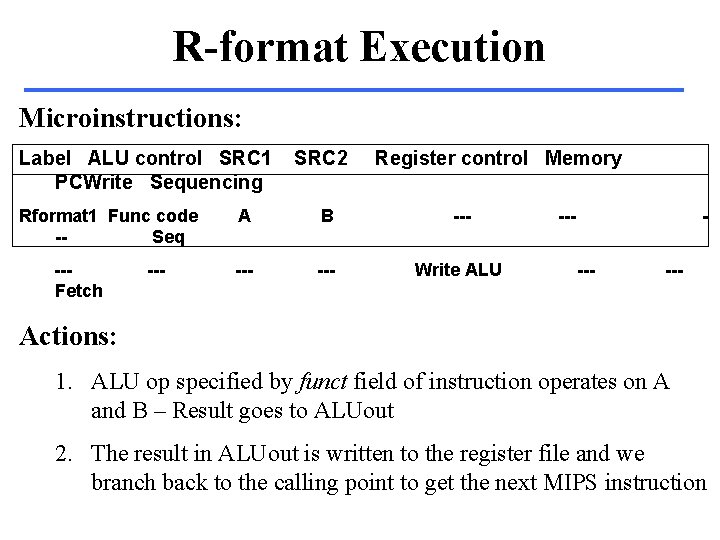

R-format Execution Microinstructions: Label ALU control SRC 1 PCWrite Sequencing Rformat 1 Func code -Seq --Fetch --- SRC 2 Register control Memory A B --- --- Write ALU --- --- Actions: 1. ALU op specified by funct field of instruction operates on A and B – Result goes to ALUout 2. The result in ALUout is written to the register file and we branch back to the calling point to get the next MIPS instruction

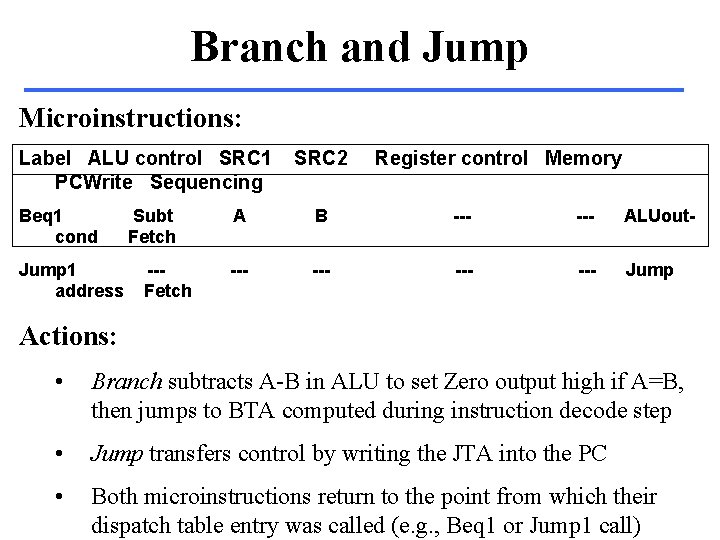

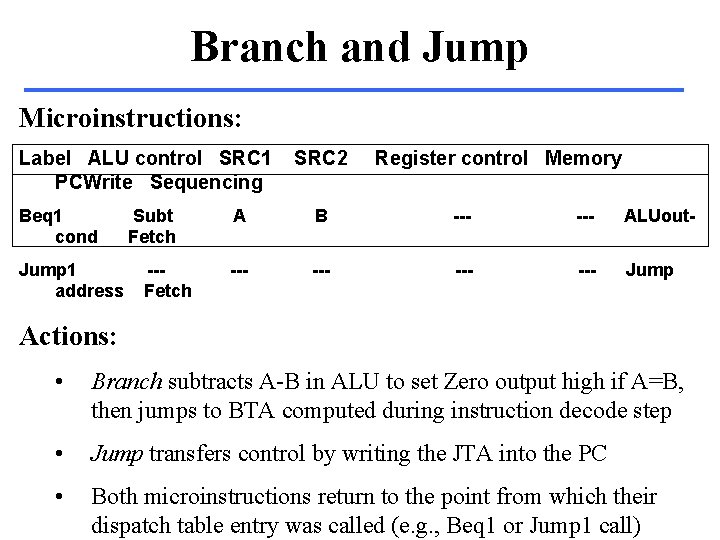

Branch and Jump Microinstructions: Label ALU control SRC 1 PCWrite Sequencing Beq 1 cond Jump 1 address Subt Fetch --Fetch SRC 2 Register control Memory A B --- ALUout- --- --- Jump Actions: • Branch subtracts A-B in ALU to set Zero output high if A=B, then jumps to BTA computed during instruction decode step • Jump transfers control by writing the JTA into the PC • Both microinstructions return to the point from which their dispatch table entry was called (e. g. , Beq 1 or Jump 1 call)

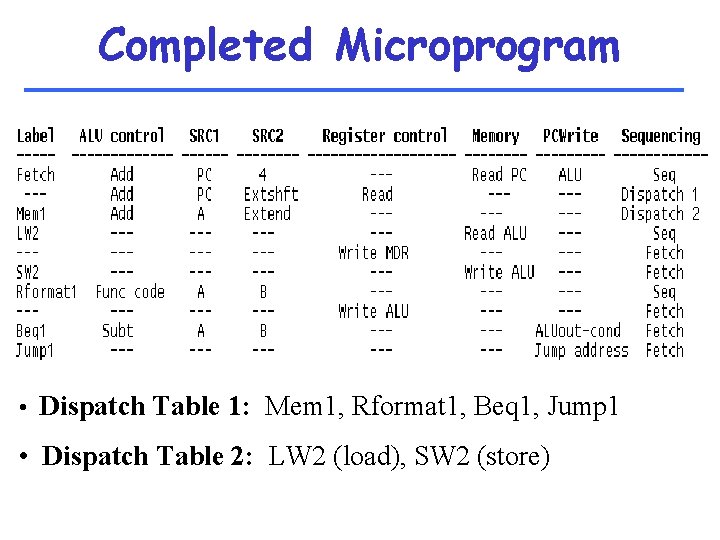

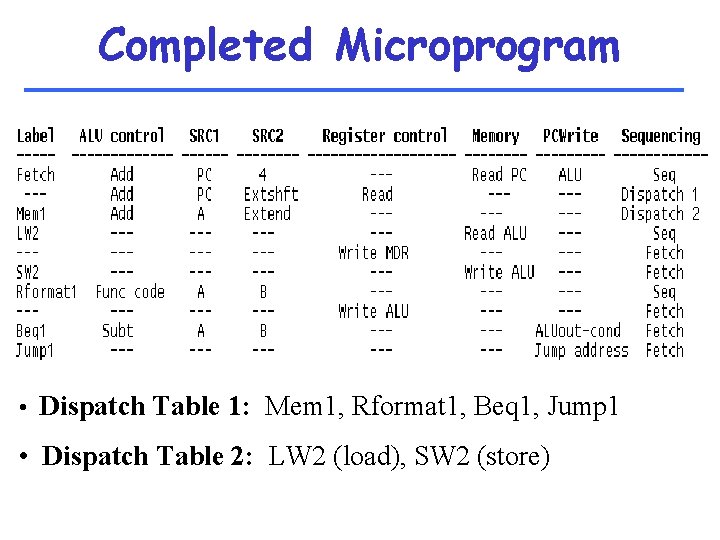

Completed Microprogram • Dispatch Table 1: Mem 1, Rformat 1, Beq 1, Jump 1 • Dispatch Table 2: LW 2 (load), SW 2 (store)

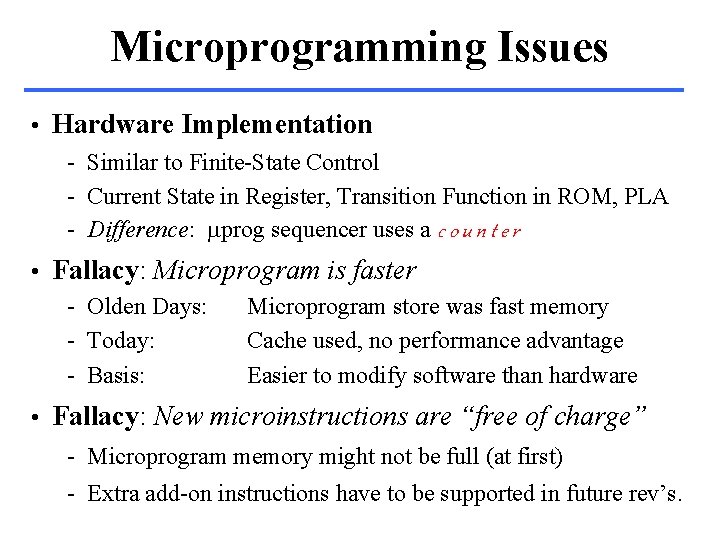

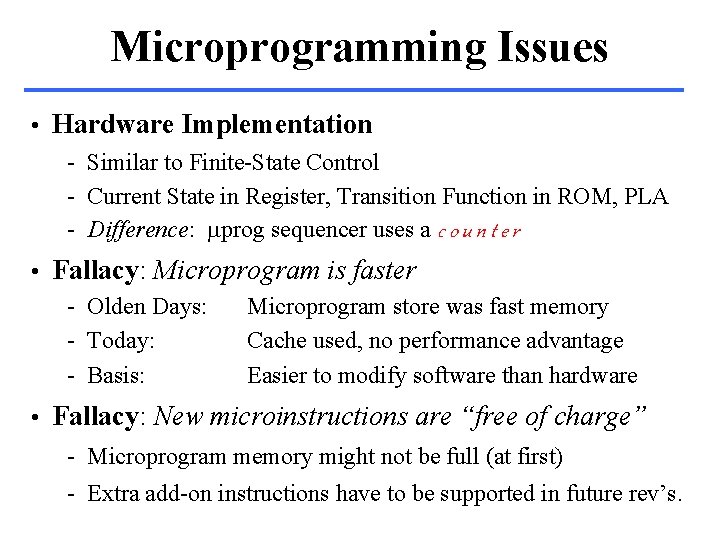

Microprogramming Issues • Hardware Implementation - Similar to Finite-State Control - Current State in Register, Transition Function in ROM, PLA - Difference: mprog sequencer uses a c o u n t e r • Fallacy: Microprogram is faster - Olden Days: Microprogram store was fast memory - Today: Cache used, no performance advantage - Basis: Easier to modify software than hardware • Fallacy: New microinstructions are “free of charge” - Microprogram memory might not be full (at first) - Extra add-on instructions have to be supported in future rev’s.

![New Topic Exceptions Definition Event causes unexpected transfer of control Types 1 Exception overflow New Topic: Exceptions Definition: Event causes unexpected transfer of control Types: (1) Exception [overflow]](https://slidetodoc.com/presentation_image_h2/93583398047f0ca8f728eadf3a6a440c/image-12.jpg)

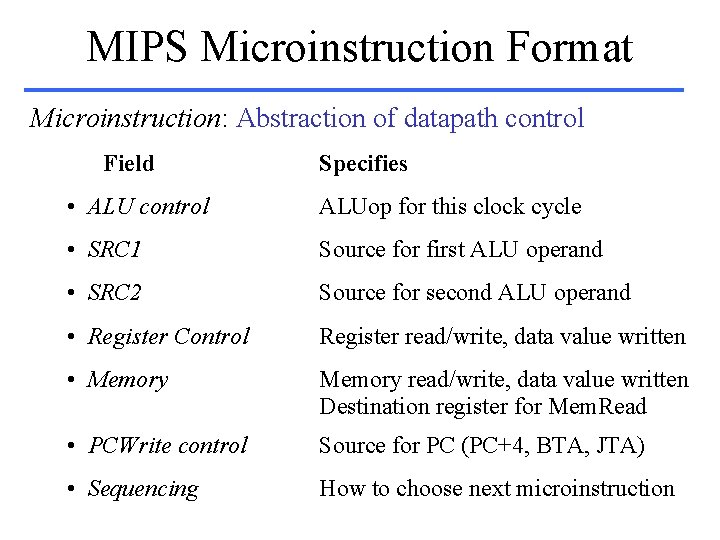

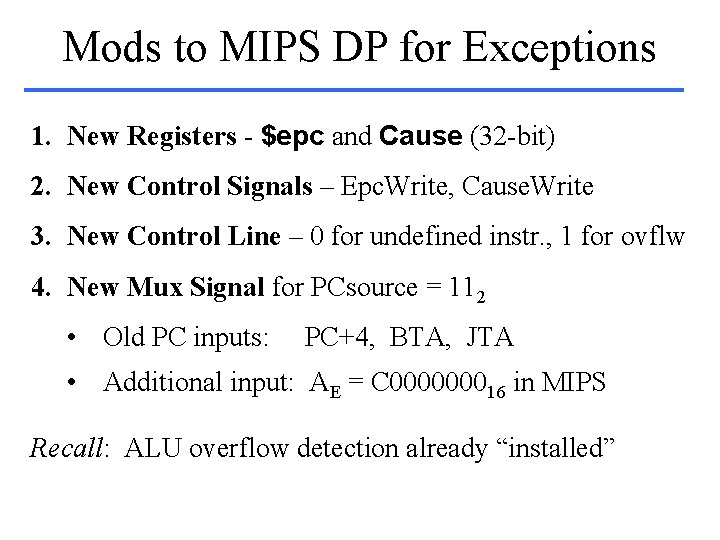

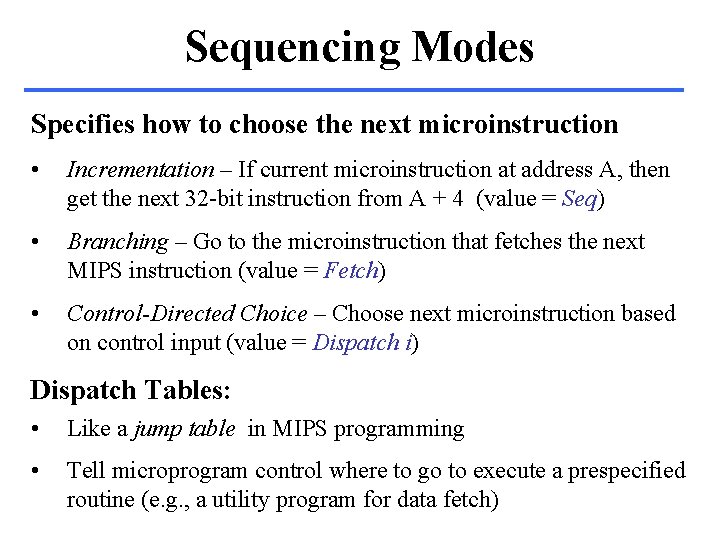

New Topic: Exceptions Definition: Event causes unexpected transfer of control Types: (1) Exception [overflow] (2) Interrupt [I/O] Difference: Exception generated inside the processor Interrupt associated with external event Challenges: • Exception Detection – How to discover exception • Exception Handling – What to do MIPS: 2 types – Undefined instruction, Arith. overflow

![Exception Detection Undefined Instruction 1 Add State 10 Exception to FiniteState Control 2 Exception Detection • Undefined Instruction: 1. Add State 10 [Exception] to Finite-State Control 2.](https://slidetodoc.com/presentation_image_h2/93583398047f0ca8f728eadf3a6a440c/image-13.jpg)

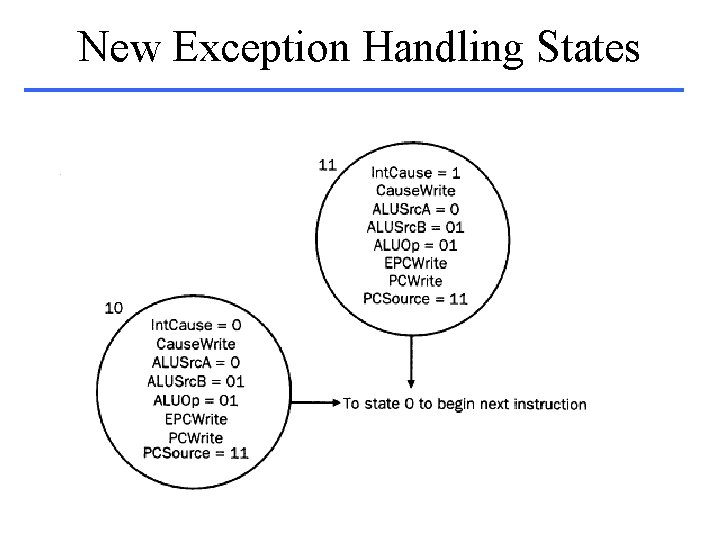

Exception Detection • Undefined Instruction: 1. Add State 10 [Exception] to Finite-State Control 2. Every instruction not lw, sw, beq, R-format, or jump transitions to State 10 • Arithmetic Overflow: 1. Recall: ALU has overflow detection logic. So, create a new State 11 in FSC to handle overflow 2. When ALU output Overflow is asserted, then control is transferred to State 11

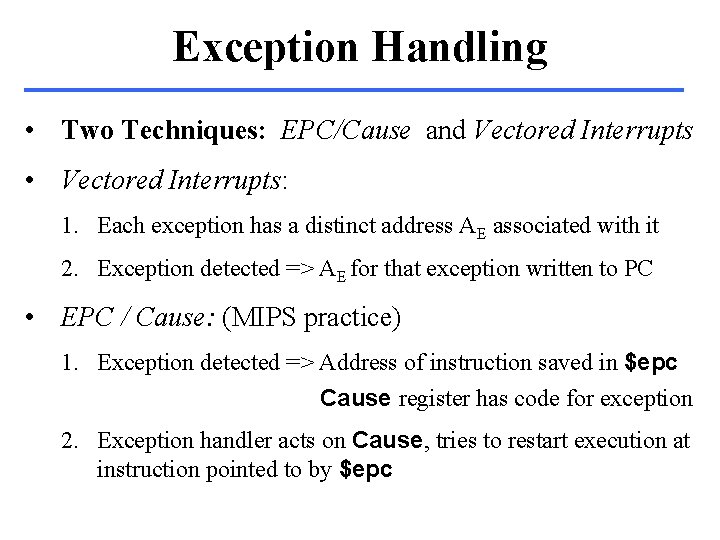

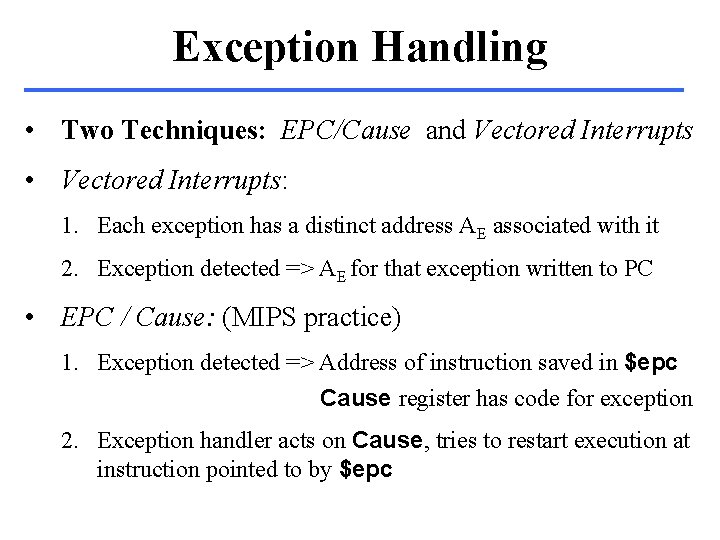

Exception Handling • Two Techniques: EPC/Cause and Vectored Interrupts • Vectored Interrupts: 1. Each exception has a distinct address AE associated with it 2. Exception detected => AE for that exception written to PC • EPC / Cause: (MIPS practice) 1. Exception detected => Address of instruction saved in $epc Cause register has code for exception 2. Exception handler acts on Cause, tries to restart execution at instruction pointed to by $epc

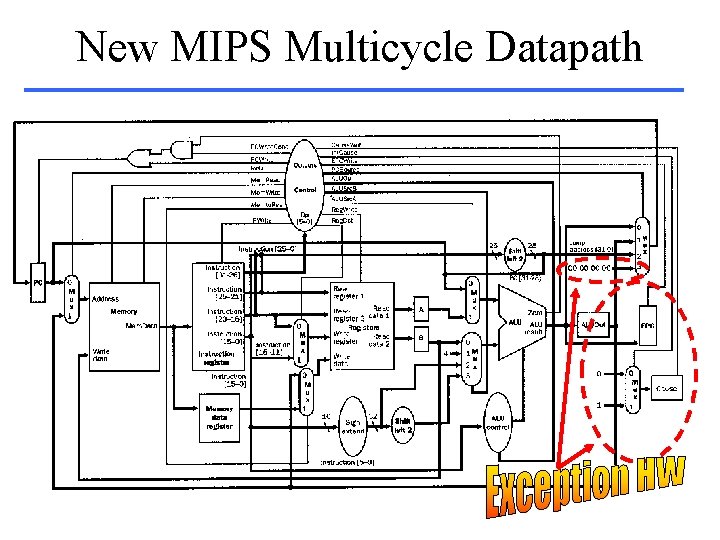

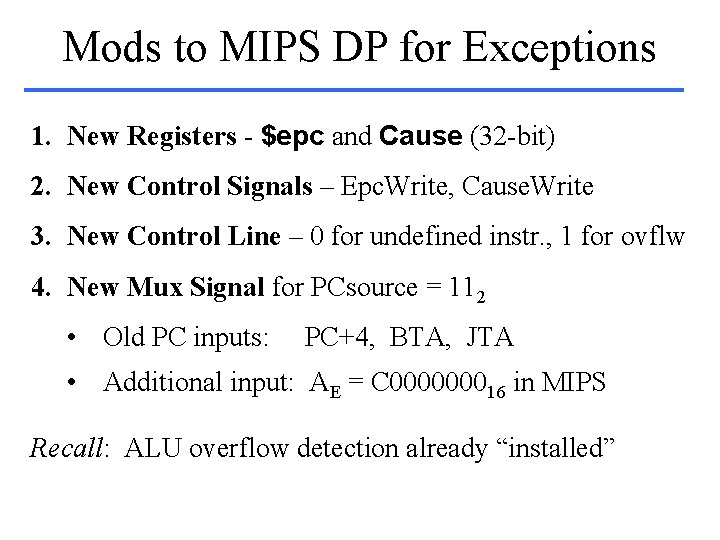

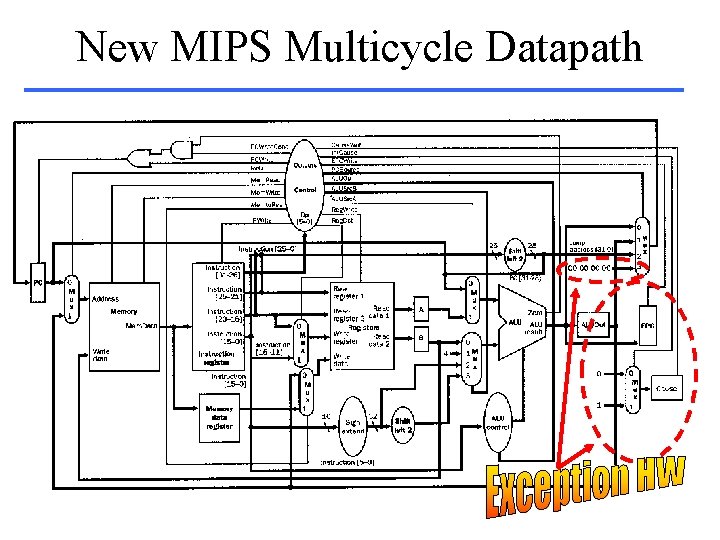

Mods to MIPS DP for Exceptions 1. New Registers - $epc and Cause (32 -bit) 2. New Control Signals – Epc. Write, Cause. Write 3. New Control Line – 0 for undefined instr. , 1 for ovflw 4. New Mux Signal for PCsource = 112 • Old PC inputs: PC+4, BTA, JTA • Additional input: AE = C 000000016 in MIPS Recall: ALU overflow detection already “installed”

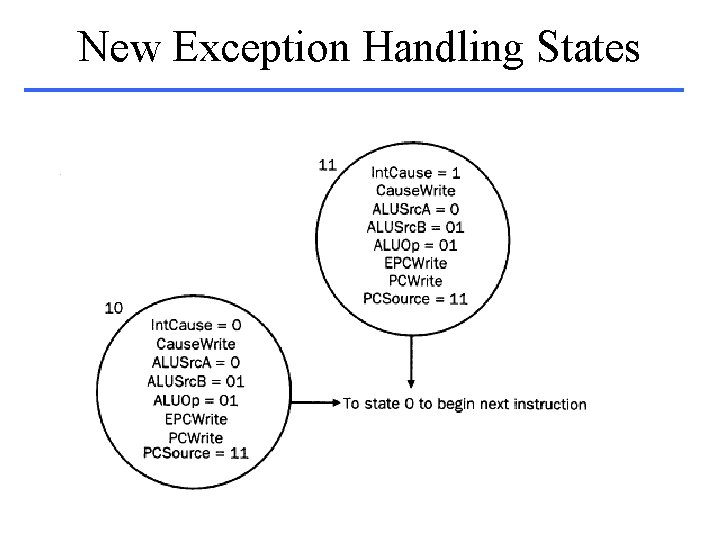

New Exception Handling States

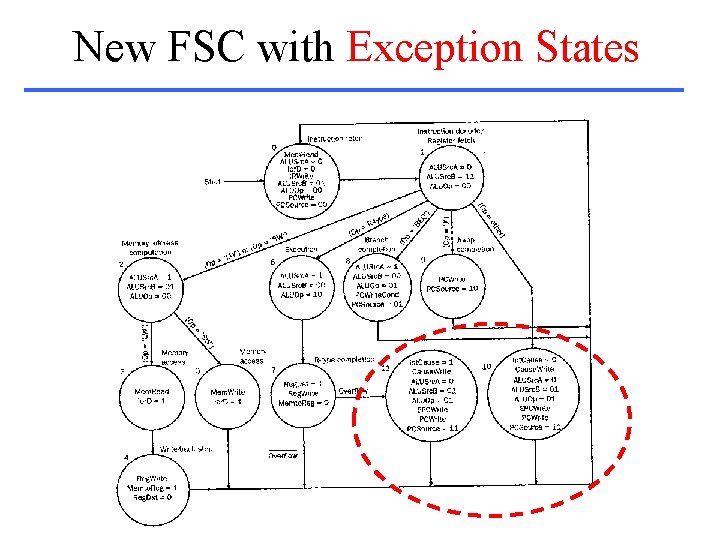

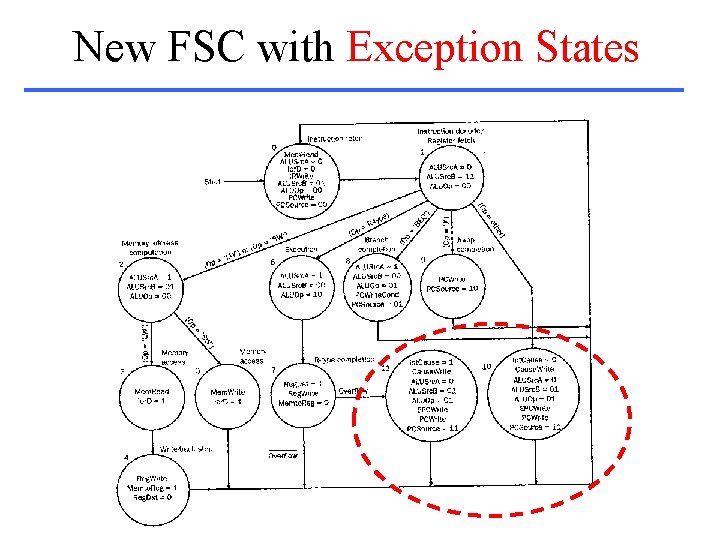

New FSC with Exception States

New MIPS Multicycle Datapath

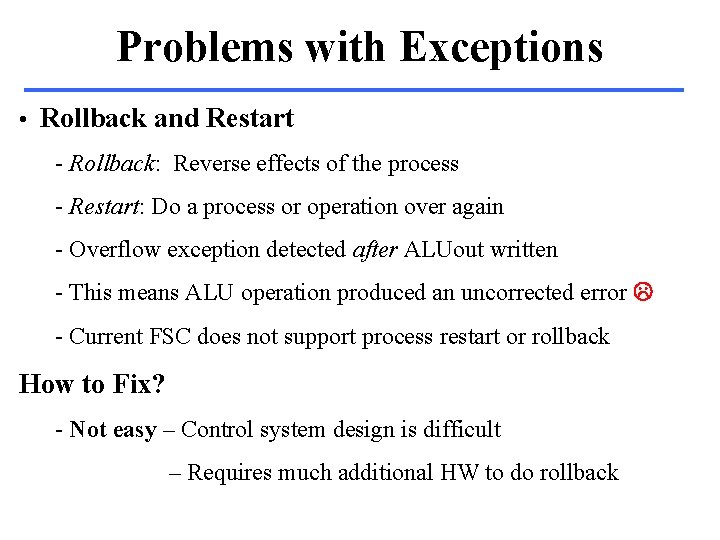

Problems with Exceptions • Rollback and Restart - Rollback: Reverse effects of the process - Restart: Do a process or operation over again - Overflow exception detected after ALUout written - This means ALU operation produced an uncorrected error - Current FSC does not support process restart or rollback How to Fix? - Not easy – Control system design is difficult – Requires much additional HW to do rollback

Conclusions • Microprogramming – More tractable for large ISAs • Challenge: Getting the fields and signals consistent • Pitfall: Microprograms not necessarily faster • Pitfall: Add-on microprogram instructions not “for free” • Exceptions (internal event) vs. Interrupts (external) – Exception Detection needs Special Hardware – Exception Handling needs more hardware ($$$$)

Lookahead: Next Exam Covers… • • MIPS programs, Pointers and Arrays Arithmetic/Logic operations, ALUs, MIPS ALU Boolean Arithmetic (signed and unsigned +, -, x, /) Floating Point Operations and Datapath/Pipelining Next Topic: Pipelining !! a e v a H Happy Spring