CASPER Workshop 2009 Cape Town South Africa Matt

- Slides: 23

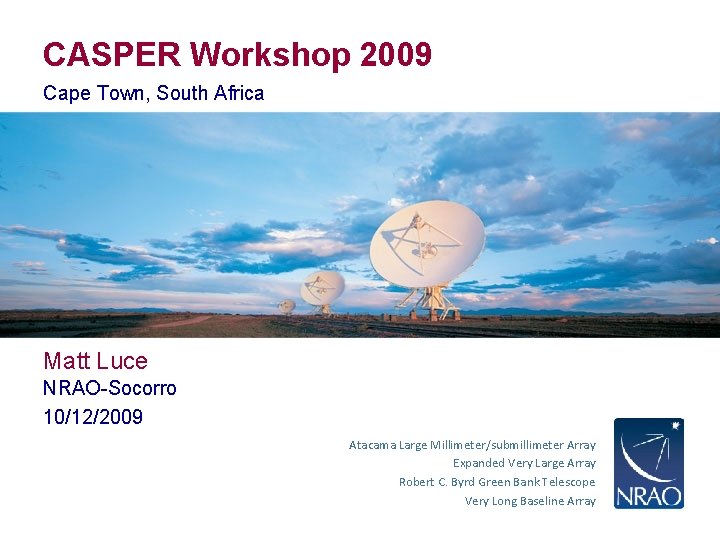

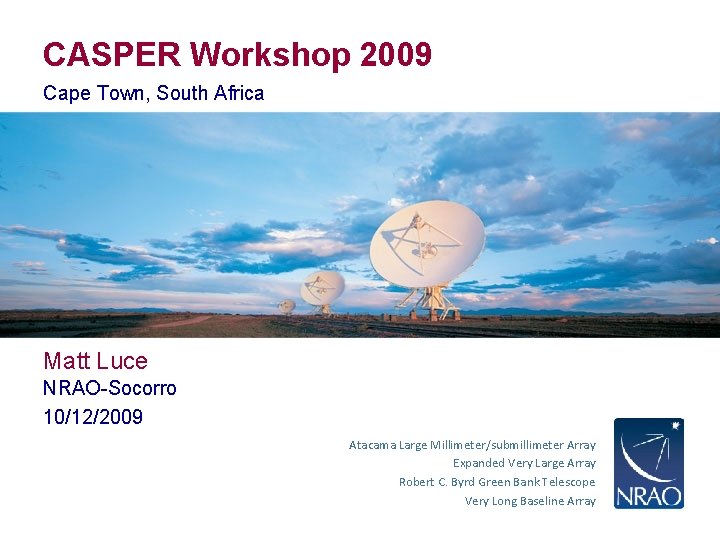

CASPER Workshop 2009 Cape Town, South Africa Matt Luce NRAO-Socorro 10/12/2009 Atacama Large Millimeter/submillimeter Array Expanded Very Large Array Robert C. Byrd Green Bank Telescope Very Long Baseline Array

Introduction • CASPER? • CASPER Workshop 2009 – Applications – Hardware – Tool flow – Tutorials

What is CASPER? • Collaboration for Astronomy Signal Processing and Electronics Research • Original group at UC Berkeley (Dan W. ) – http: //casper. berkeley. edu/ • Distributed community of developers and users. – UC Berkeley, Meer. KAT, NRAO, GMRT, SETI …

CASPER Goals • Streamline and simplify the design flow of radio astronomy instrumentation. • Design reuse through the development of platform-independent, open-source hardware and software.

CASPER Religion & Philosophy • Big projects are “dinosaurs” by release. Faster development time is an absolute necessity. • Custom backplanes are the wrong way to interface with electronics. • The signal processing libraries are a very important part of any project. • “Hardware is free. ” Use commercial, off-the-shelf network hardware to connect together samplers and computing resources so that it can be easily replaced as technology improves (Moore’s Law). • The future will be clusters of general purpose computing hardware connected by fast Ethernet, instead of “hard” correlators. • There is a sweet spot of cost versus capability for deploying a new technology. Too soon and it’s very expensive. Too late and it’s outdated at deployment.

CASPER Hardware: i. Bo. B 6

CASPER Hardware: i. Bo. B • • • Virtex-II Z-DOK CX 4 ADC-to-i. Bo. B-to-10 Gb. E-to-BEE 2 http: //casper. berkeley. edu/wiki/IBOB 7

CASPER Hardware: BEE 2 8

CASPER Hardware: BEE 2 • • General-purpose processing module Five Virtex-II FPGAs 20 GB DDR 2 DRAM http: //bee 2. eecs. berkeley. edu/ 9

CASPER Hardware: ROACH 10

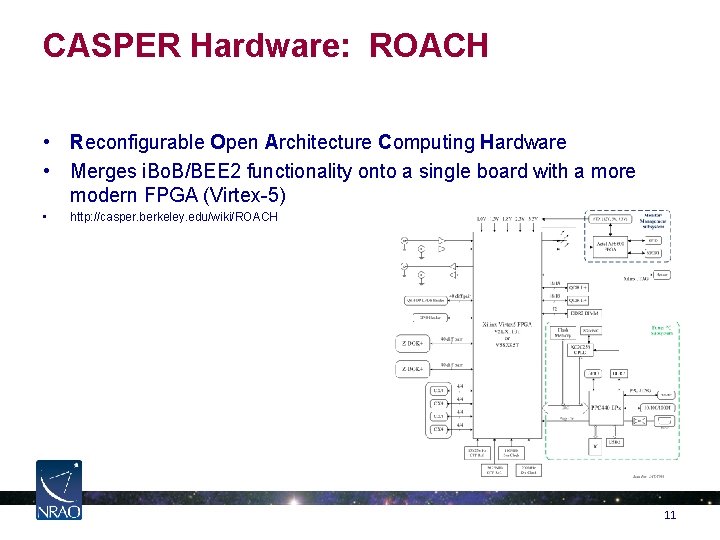

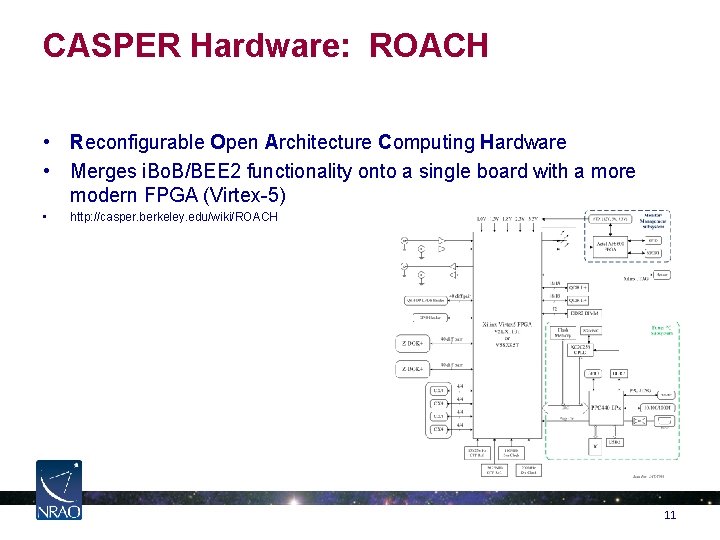

CASPER Hardware: ROACH • Reconfigurable Open Architecture Computing Hardware • Merges i. Bo. B/BEE 2 functionality onto a single board with a more modern FPGA (Virtex-5) • http: //casper. berkeley. edu/wiki/ROACH 11

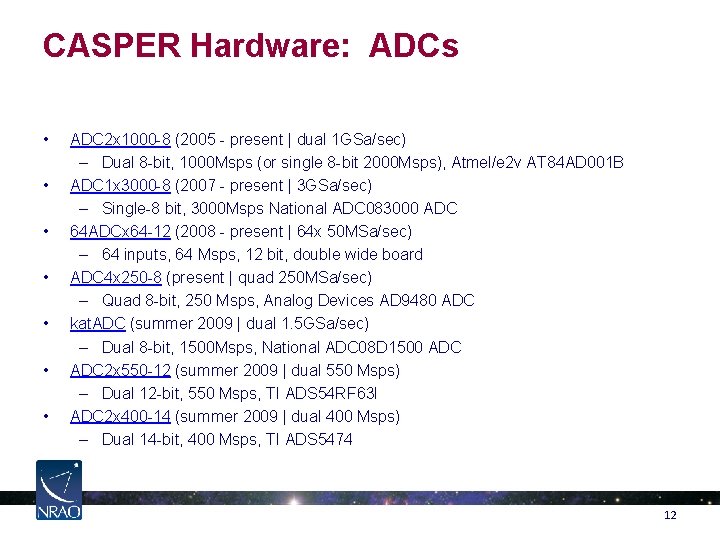

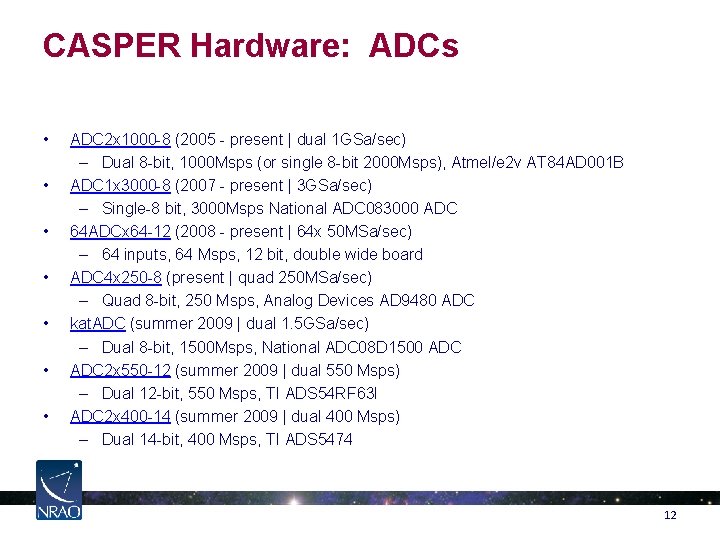

CASPER Hardware: ADCs • • ADC 2 x 1000 -8 (2005 - present | dual 1 GSa/sec) – Dual 8 -bit, 1000 Msps (or single 8 -bit 2000 Msps), Atmel/e 2 v AT 84 AD 001 B ADC 1 x 3000 -8 (2007 - present | 3 GSa/sec) – Single-8 bit, 3000 Msps National ADC 083000 ADC 64 ADCx 64 -12 (2008 - present | 64 x 50 MSa/sec) – 64 inputs, 64 Msps, 12 bit, double wide board ADC 4 x 250 -8 (present | quad 250 MSa/sec) – Quad 8 -bit, 250 Msps, Analog Devices AD 9480 ADC kat. ADC (summer 2009 | dual 1. 5 GSa/sec) – Dual 8 -bit, 1500 Msps, National ADC 08 D 1500 ADC 2 x 550 -12 (summer 2009 | dual 550 Msps) – Dual 12 -bit, 550 Msps, TI ADS 54 RF 63 I ADC 2 x 400 -14 (summer 2009 | dual 400 Msps) – Dual 14 -bit, 400 Msps, TI ADS 5474 12

CASPER Software/Libraries • MATLAB/Simulink • Xilinx System Generator – Custom DSP Libraries • BORPH – Debian Linux – FPGA=CPU – Gateware (BOF) – File System Registers – http: //casper. berkeley. edu/wiki/BORPH

2009 Workshop Overview • Applications: 3 days • Working Groups: 2 days – Hardware – Tool flow – Applications • Tutorials

Application: CASPER Correlators • “The” CASPER Correlator – http: //casper. berkeley. edu/wiki/CASPER_Correlator – FX using i. Bo. B/BEE 2 • PAPER (A. Parsons) – Based on CASPER • KAT-7 (J. Manley) – ROACH • Medicina – i. Bo. B/BEE 2 – 10 day development

Application: CASPER Spectrometers • Fly’s Eye @ ATA (A. Siemion) – 11 i. Bo. Bs, ea. 4 independent spectrometers, 209. 5 MHz w/128 channles, 0. 6 ms integration time. • SERENDIP V @ Arecibo (L. Spitler) – i. Bo. B/BEE 2: 200 MHz/128 M channel • Nancay Co. De. Di Pulsar Machine (I. Cognard) – i. Bo. B: 400 MHz/128 channel – GPU de-dispersion • GUPPI @ GBT (J. Ford) – https: //safe. nrao. edu/wiki/bin/view/CICADA/NGNPPPSpecificatio ns

Application: Other • OVRO Polarimeter (M. Stevenson) – ROACH • Phased Array Processor @ SMA (R. Primiani) – i. Bo. B/BEE 2 – Modified Haystack DBE to Mark 5 B • Kinetic Inductance of Superconducting Resonators (L. Swenson) – ROACH driving DAC boards

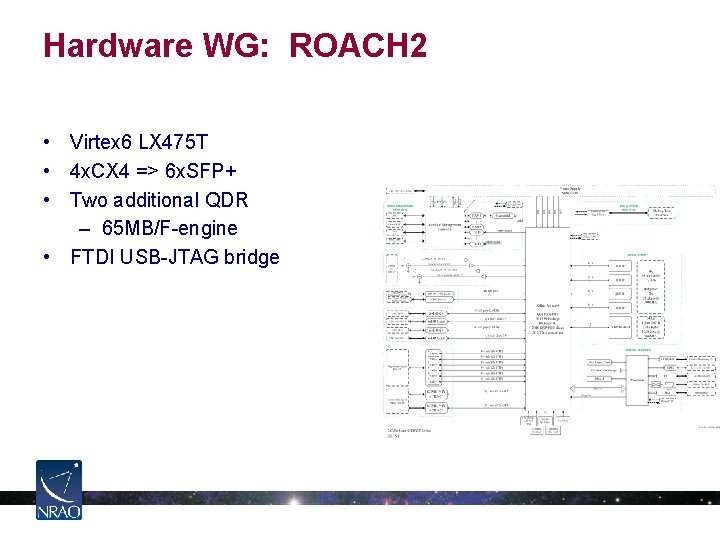

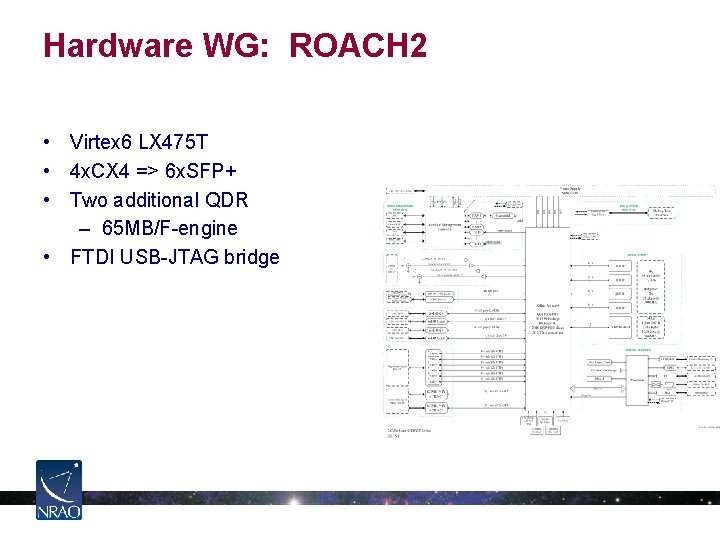

Hardware WG: ROACH 2 • Virtex 6 LX 475 T • 4 x. CX 4 => 6 x. SFP+ • Two additional QDR – 65 MB/F-engine • FTDI USB-JTAG bridge

Hardware WG: future ADCs • E 2 v 20 Gsps – ~8 GHz analog bandwidth • Agilent 20 Gsps – ~13 Ghz analog bandwidth 19

Toolflow WG: Current • Pros – Ease-of-use (Graphical) – Parameterized designs – Full tool flow from DSP through bit files to drivers – Coregen • Highly efficient resource utilization • Cons – Portability – Language stability – Backwards compatibility – Simulation speed – Platform lock-in – Unit testing – Cost 20

Toolflow WG: Future • HDL Cores – Parameterization – Simulink wrappers – Simulation – Documentation • Open source Simulink replacement 21

Tutorials • • • 1: LED blinking on ROACH (Complete) II: 10 Gb. E (Complete) III: Wideband Spectrometer (WIP) IV: Pocket Correlator (WIP) V: High Resolution Spectrometer (WIP) • Available in the CASPER SVN: – http: //casper. berkeley. edu/svn/trunk/ref_designs_tutorials/workshop_20 09/ 22

Questions?