Calice ECAL Readout Hardware Status report Adam Baird

Calice ECAL Readout Hardware Status report Adam Baird ECAL Meeting 26 Sept 2003 LLR-Ecole Polytechnique

Calice - ECAL • Hardware - Readout Module • Firmware – front FPGA (from Osman Zorba) – Trigger (from Matthew Warren) Adam Baird Rutherford Appleton Laboratory

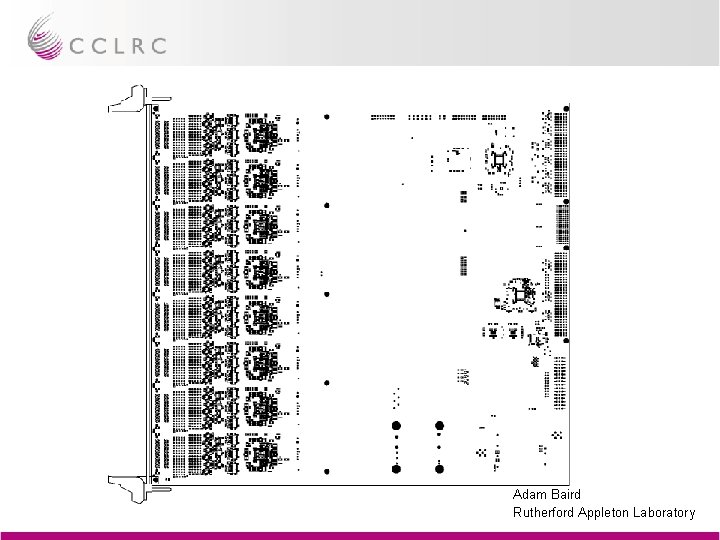

Adam Baird Rutherford Appleton Laboratory

Adam Baird Rutherford Appleton Laboratory

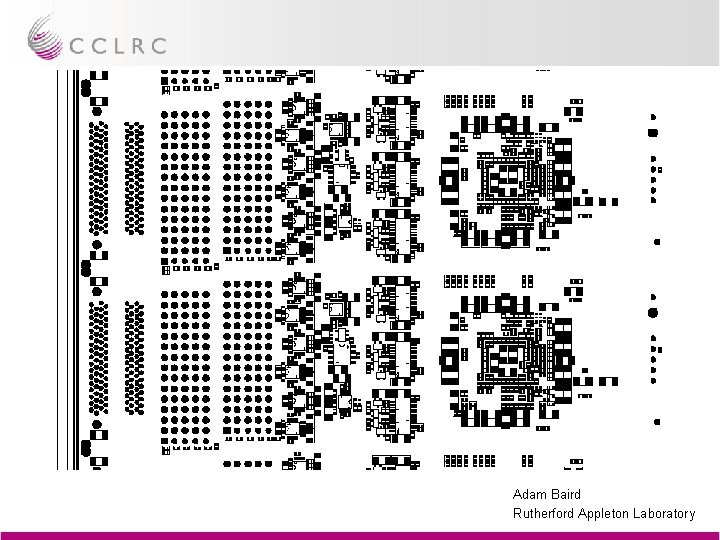

Adam Baird Rutherford Appleton Laboratory

Adam Baird Rutherford Appleton Laboratory

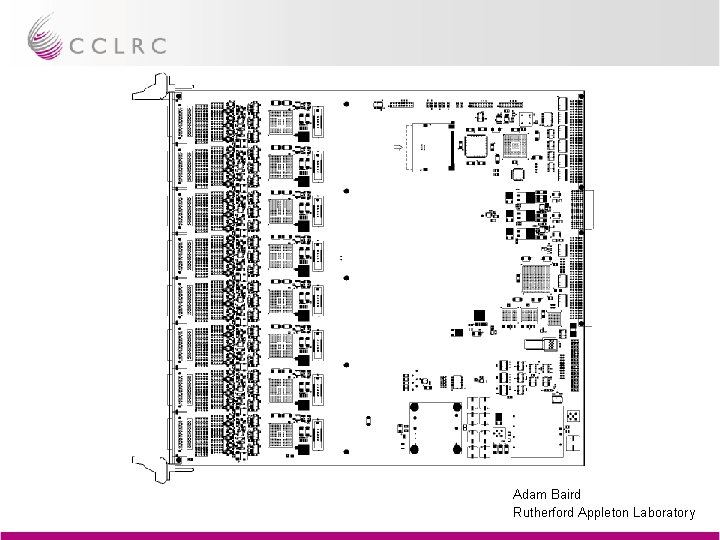

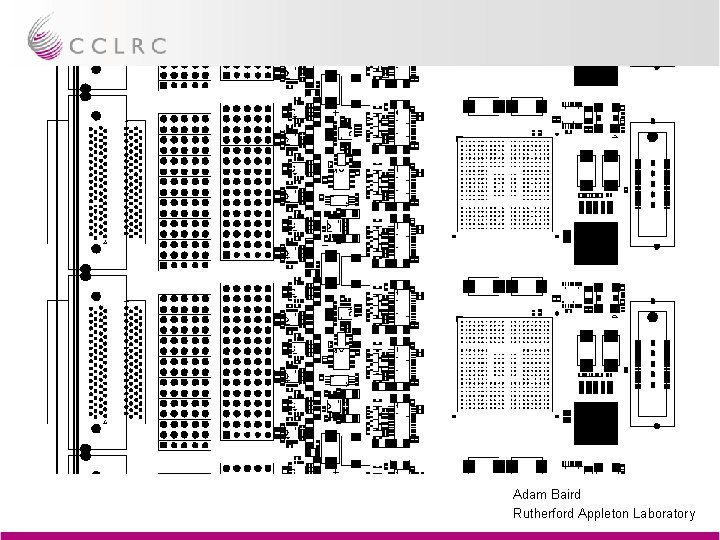

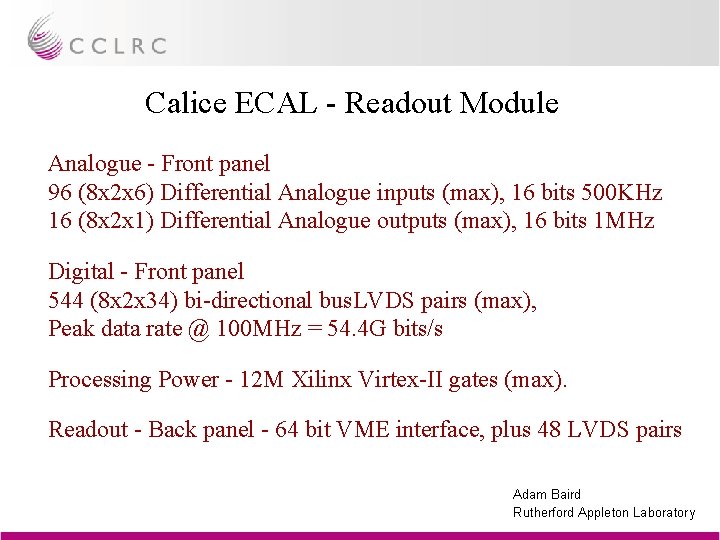

Calice ECAL - Readout Module Analogue - Front panel 96 (8 x 2 x 6) Differential Analogue inputs (max), 16 bits 500 KHz 16 (8 x 2 x 1) Differential Analogue outputs (max), 16 bits 1 MHz Digital - Front panel 544 (8 x 2 x 34) bi-directional bus. LVDS pairs (max), Peak data rate @ 100 MHz = 54. 4 G bits/s Processing Power - 12 M Xilinx Virtex-II gates (max). Readout - Back panel - 64 bit VME interface, plus 48 LVDS pairs Adam Baird Rutherford Appleton Laboratory

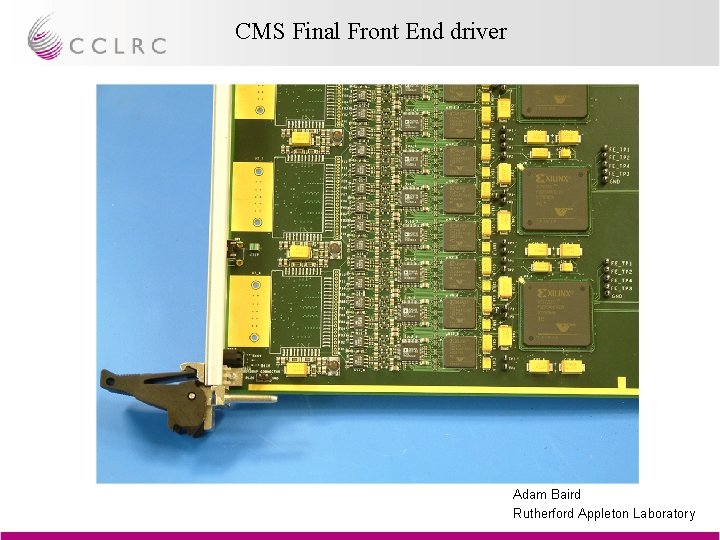

CMS Final Front End driver Adam Baird Rutherford Appleton Laboratory

CMS Final Front End driver Adam Baird Rutherford Appleton Laboratory

Timescales Completion 2 wks (from today) PCB Fabrication, 3 wks PCB assembly, 1 wk JTAG test, 1 wk (mid Nov) VFE test (Jan 2003 ? ? ? ) 3 Months test 3 Months production (30 June 2003) Adam Baird Rutherford Appleton Laboratory

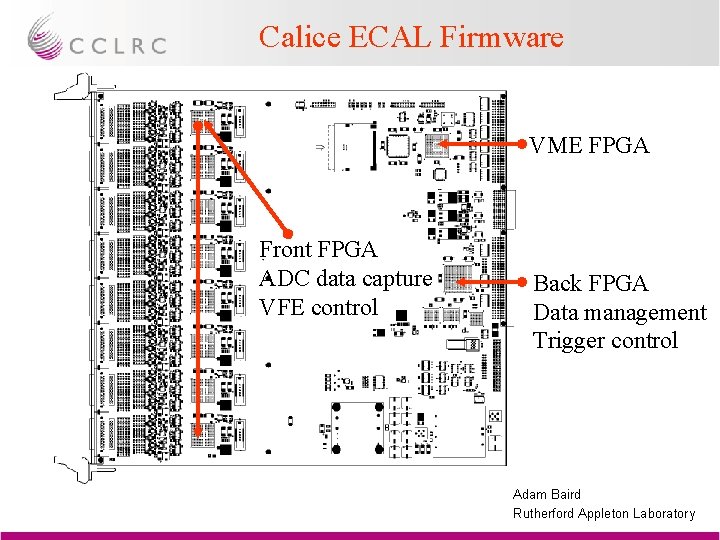

Calice ECAL Firmware VME FPGA Front FPGA ADC data capture VFE control Back FPGA Data management Trigger control Adam Baird Rutherford Appleton Laboratory

- Slides: 11