Calcolatori Elettronici Il Processore 2 Francesco Lo Presti

![Prelievo dell’Istruzione (IF) IR = M[PC]; PC = PC + 4; PC + 4 Prelievo dell’Istruzione (IF) IR = M[PC]; PC = PC + 4; PC + 4](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-21.jpg)

![Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-22.jpg)

![Formato R: (EX) – Esecuzione ALUOut = A op B Reg[rs] R-Type Result PC Formato R: (EX) – Esecuzione ALUOut = A op B Reg[rs] R-Type Result PC](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-23.jpg)

![Formato R: (MEM) – Scrittura Registro Dest. Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result Formato R: (MEM) – Scrittura Registro Dest. Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-24.jpg)

![Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-25.jpg)

![Branch: (EX) – Aggiornamento PC if (A == B) PC = ALUOut; Reg[rs] Branch Branch: (EX) – Aggiornamento PC if (A == B) PC = ALUOut; Reg[rs] Branch](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-26.jpg)

![Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-27.jpg)

![Jump: (EX) – Aggiornamento PC PC = PC[31 -28] concat (IR[25 -0] << 2) Jump: (EX) – Aggiornamento PC PC = PC[31 -28] concat (IR[25 -0] << 2)](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-28.jpg)

![Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-29.jpg)

![Store: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC Store: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-30.jpg)

![Store: (MEM) Scrittura in Memoria M[ALUOut] = B; Reg[rs] PC + 4 Reg[rt] CPU Store: (MEM) Scrittura in Memoria M[ALUOut] = B; Reg[rs] PC + 4 Reg[rt] CPU](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-31.jpg)

![Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-32.jpg)

![Load: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC Load: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-33.jpg)

![Load: (MEM) Lettura in Memoria MDR = M[ALUOut]; Reg[rs] Mem. Address PC + 4 Load: (MEM) Lettura in Memoria MDR = M[ALUOut]; Reg[rs] Mem. Address PC + 4](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-34.jpg)

![Load: (WB) – Scrittura nel Registro Dest. Reg[IR[20 -16]] = MDR; Reg[rs] Mem. Address Load: (WB) – Scrittura nel Registro Dest. Reg[IR[20 -16]] = MDR; Reg[rs] Mem. Address](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-35.jpg)

![Segnali di Controllo: (IF) IR = M[PC]; - Mem. Read=1 - IRWrite=1 - Ior. Segnali di Controllo: (IF) IR = M[PC]; - Mem. Read=1 - IRWrite=1 - Ior.](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-41.jpg)

![Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-42.jpg)

![Segnali di Controllo: (MEM) Formato R – Scrittura Registro Destinazione Reg[IR[15: 11]] = ALUOut; Segnali di Controllo: (MEM) Formato R – Scrittura Registro Destinazione Reg[IR[15: 11]] = ALUOut;](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-44.jpg)

![Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-45.jpg)

![Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-47.jpg)

![Segnali di Controllo: (EX) Jump – Agg. PC PC = PC[21 -28] concat (IR[25 Segnali di Controllo: (EX) Jump – Agg. PC PC = PC[21 -28] concat (IR[25](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-48.jpg)

![Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-49.jpg)

![Segnali di Controllo: (EX) Store – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Segnali di Controllo: (EX) Store – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]);](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-50.jpg)

![Segnali di Controllo: (MEM) Store – Scr. in Memoria Memory[ALUOut] = B; - Ior. Segnali di Controllo: (MEM) Store – Scr. in Memoria Memory[ALUOut] = B; - Ior.](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-51.jpg)

![Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-52.jpg)

![Segnali di Controllo: (EX) Load – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Segnali di Controllo: (EX) Load – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]);](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-53.jpg)

![Segnali di Controllo: (MEM) Load – Lett. in Memoria MDR = Memory[ALUOut]; - Ior. Segnali di Controllo: (MEM) Load – Lett. in Memoria MDR = Memory[ALUOut]; - Ior.](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-54.jpg)

![Segnali di Controllo: (WB) Load – Scr. Registro di Destinazione Reg[IR[20 -16]] = MDR; Segnali di Controllo: (WB) Load – Scr. Registro di Destinazione Reg[IR[20 -16]] = MDR;](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-55.jpg)

![Unita’ di Controllo: Funzione di Uscita Outputs Input Values (Current State[3 -0]) 0000 0001 Unita’ di Controllo: Funzione di Uscita Outputs Input Values (Current State[3 -0]) 0000 0001](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-58.jpg)

![Unita’ di Controllo: Funzione Prossimo Stato Current Inst[31 -26] State 00000010 000100 [3 -0] Unita’ di Controllo: Funzione Prossimo Stato Current Inst[31 -26] State 00000010 000100 [3 -0]](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-59.jpg)

- Slides: 93

Calcolatori Elettronici Il Processore (2) Francesco Lo Presti Rielaborate da Salvatore Tucci

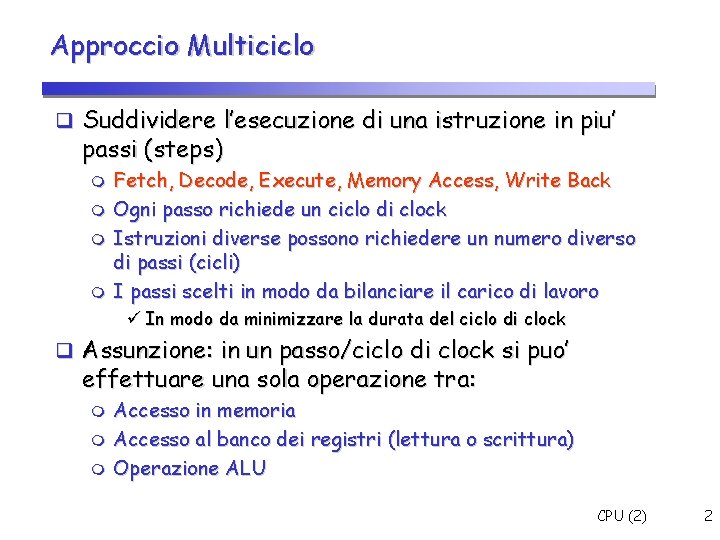

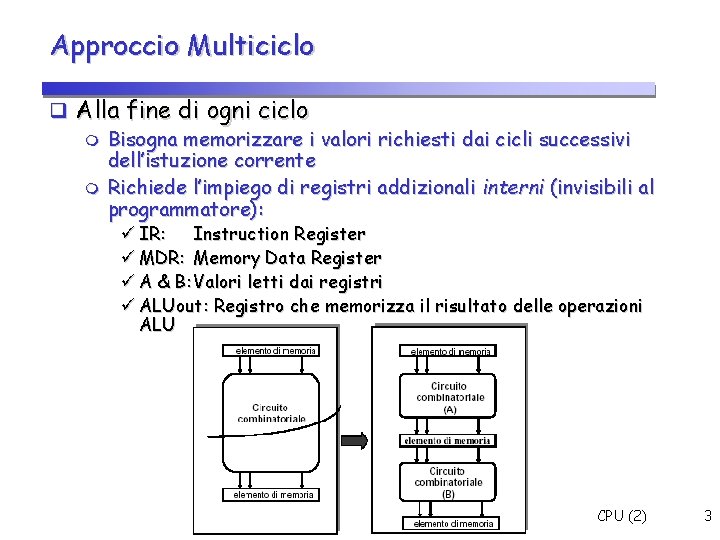

Approccio Multiciclo Suddividere l’esecuzione di una istruzione in piu’ passi (steps) Fetch, Decode, Execute, Memory Access, Write Back Ogni passo richiede un ciclo di clock Istruzioni diverse possono richiedere un numero diverso di passi (cicli) I passi scelti in modo da bilanciare il carico di lavoro In modo da minimizzare la durata del ciclo di clock Assunzione: in un passo/ciclo di clock si puo’ effettuare una sola operazione tra: Accesso in memoria Accesso al banco dei registri (lettura o scrittura) Operazione ALU CPU (2) 2

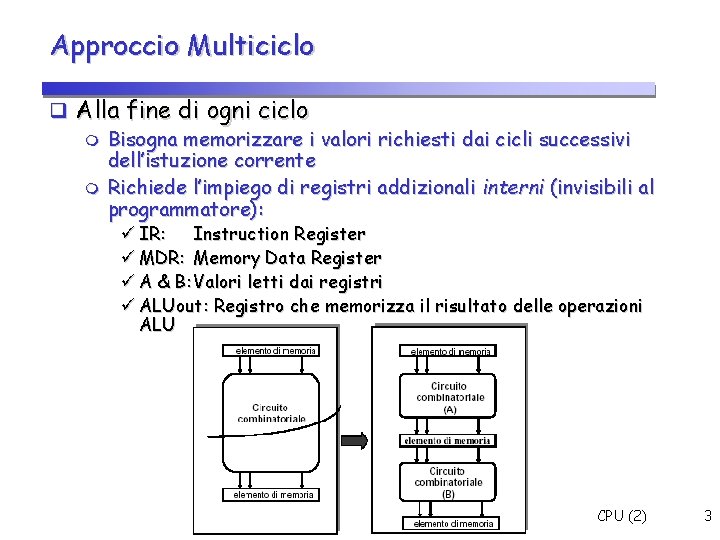

Approccio Multiciclo Alla fine di ogni ciclo Bisogna memorizzare i valori richiesti dai cicli successivi dell’istuzione corrente Richiede l’impiego di registri addizionali interni (invisibili al programmatore): IR: Instruction Register MDR: Memory Data Register A & B: Valori letti dai registri ALUout: Registro che memorizza il risultato delle operazioni ALU CPU (2) 3

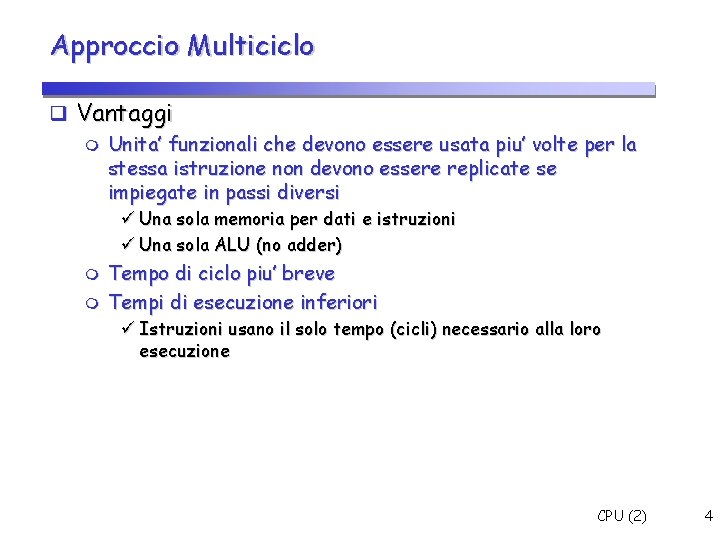

Approccio Multiciclo Vantaggi Unita’ funzionali che devono essere usata piu’ volte per la stessa istruzione non devono essere replicate se impiegate in passi diversi Una sola memoria per dati e istruzioni Una sola ALU (no adder) Tempo di ciclo piu’ breve Tempi di esecuzione inferiori Istruzioni usano il solo tempo (cicli) necessario alla loro esecuzione CPU (2) 4

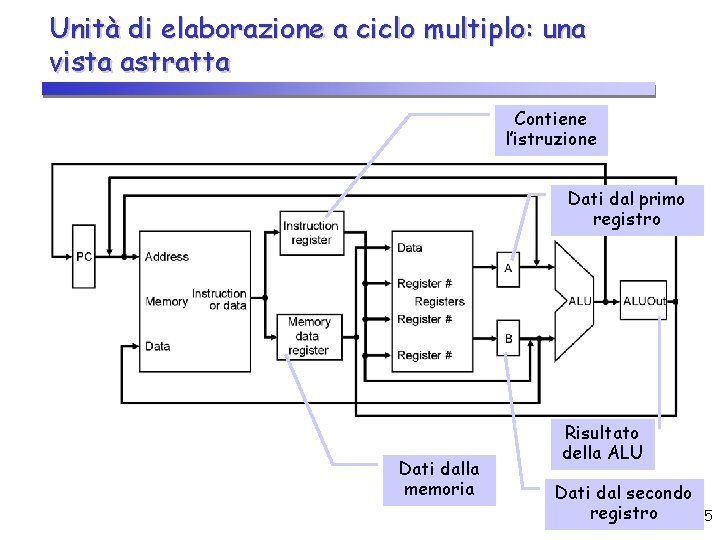

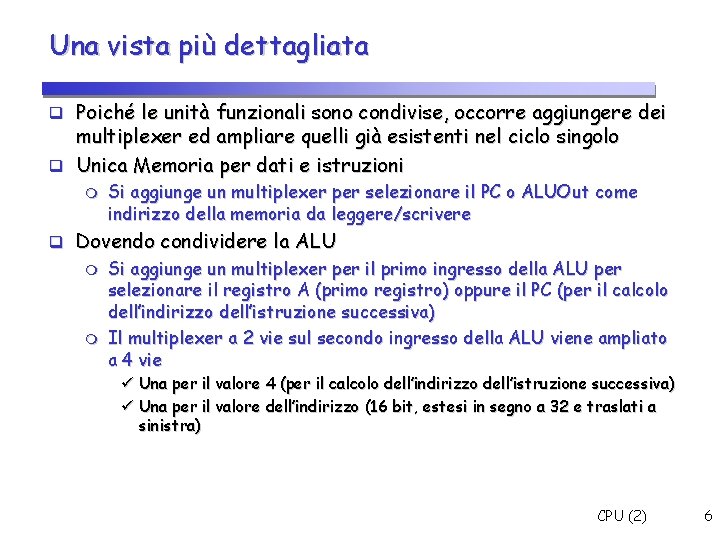

Unità di elaborazione a ciclo multiplo: una vista astratta Contiene l’istruzione Dati dal primo registro Dati dalla memoria Risultato della ALU Dati dal secondo registro CPU (2) 5

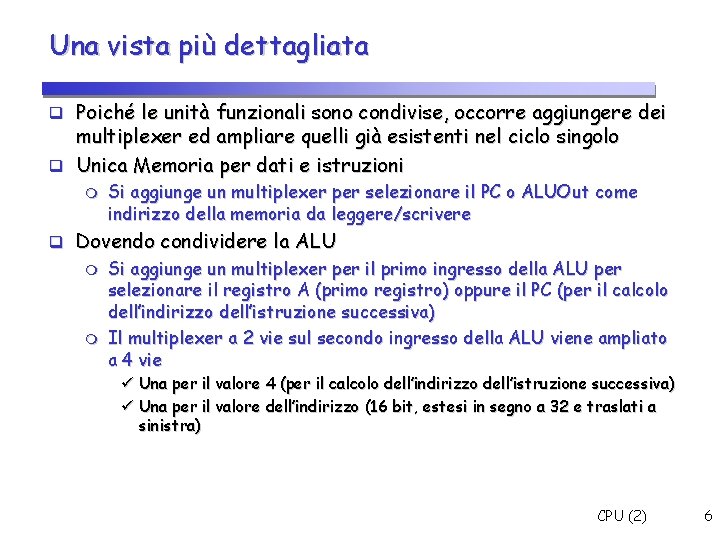

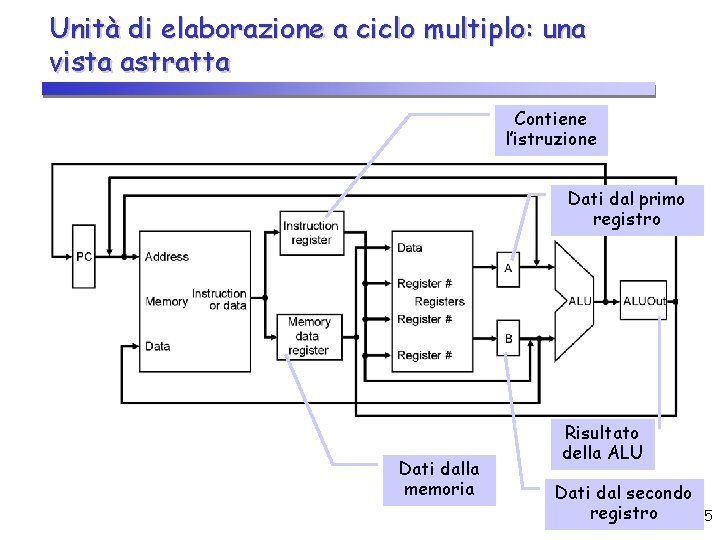

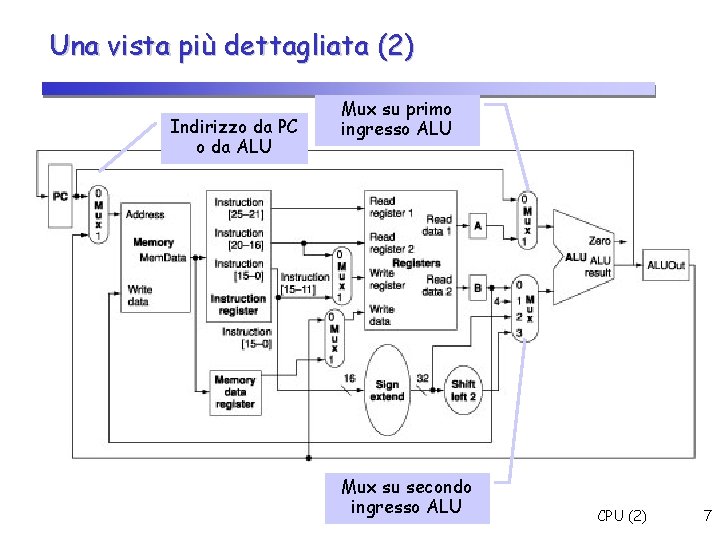

Una vista più dettagliata Poiché le unità funzionali sono condivise, occorre aggiungere dei multiplexer ed ampliare quelli già esistenti nel ciclo singolo Unica Memoria per dati e istruzioni Si aggiunge un multiplexer per selezionare il PC o ALUOut come indirizzo della memoria da leggere/scrivere Dovendo condividere la ALU Si aggiunge un multiplexer per il primo ingresso della ALU per selezionare il registro A (primo registro) oppure il PC (per il calcolo dell’indirizzo dell’istruzione successiva) Il multiplexer a 2 vie sul secondo ingresso della ALU viene ampliato a 4 vie Una per il valore 4 (per il calcolo dell’indirizzo dell’istruzione successiva) Una per il valore dell’indirizzo (16 bit, estesi in segno a 32 e traslati a sinistra) CPU (2) 6

Una vista più dettagliata (2) Indirizzo da PC o da ALU Mux su primo ingresso ALU Mux su secondo ingresso ALU CPU (2) 7

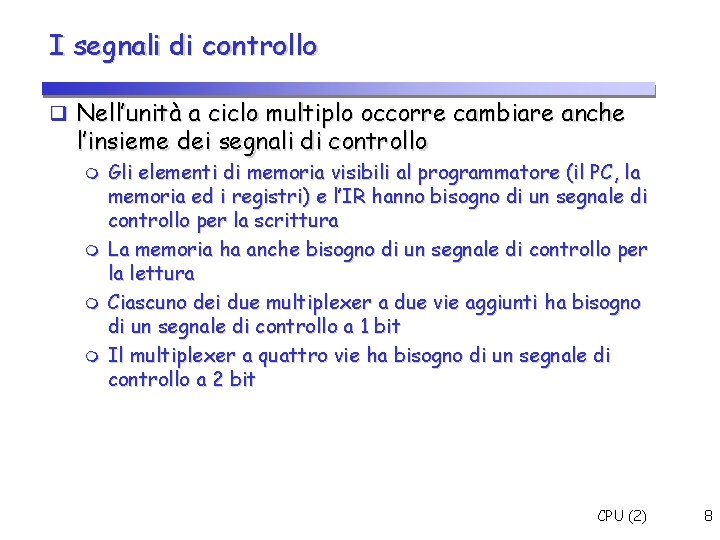

I segnali di controllo Nell’unità a ciclo multiplo occorre cambiare anche l’insieme dei segnali di controllo Gli elementi di memoria visibili al programmatore (il PC, la memoria ed i registri) e l’IR hanno bisogno di un segnale di controllo per la scrittura La memoria ha anche bisogno di un segnale di controllo per la lettura Ciascuno dei due multiplexer a due vie aggiunti ha bisogno di un segnale di controllo a 1 bit Il multiplexer a quattro vie ha bisogno di un segnale di controllo a 2 bit CPU (2) 8

L’unità con i segnali di controllo CPU (2) 9

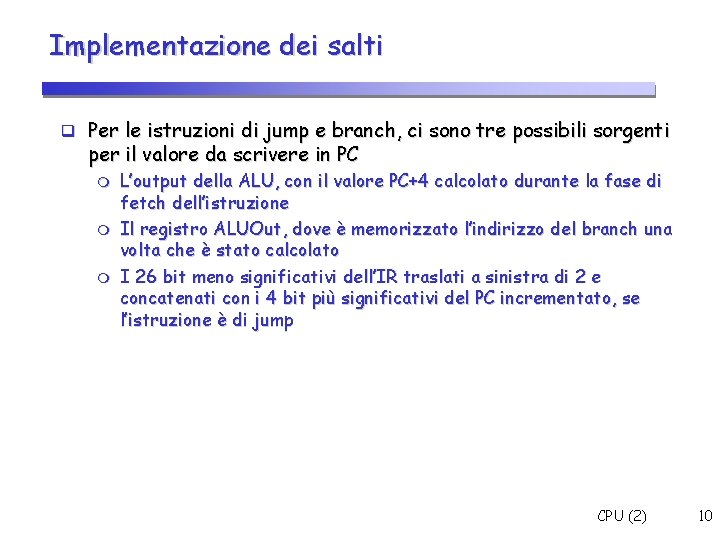

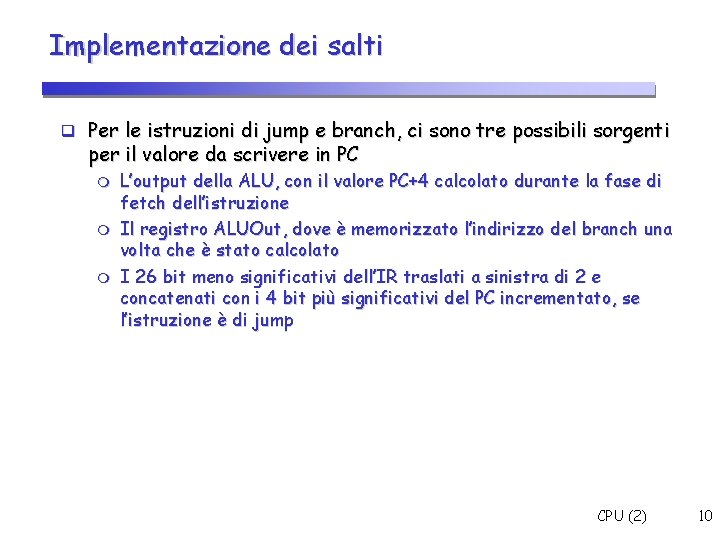

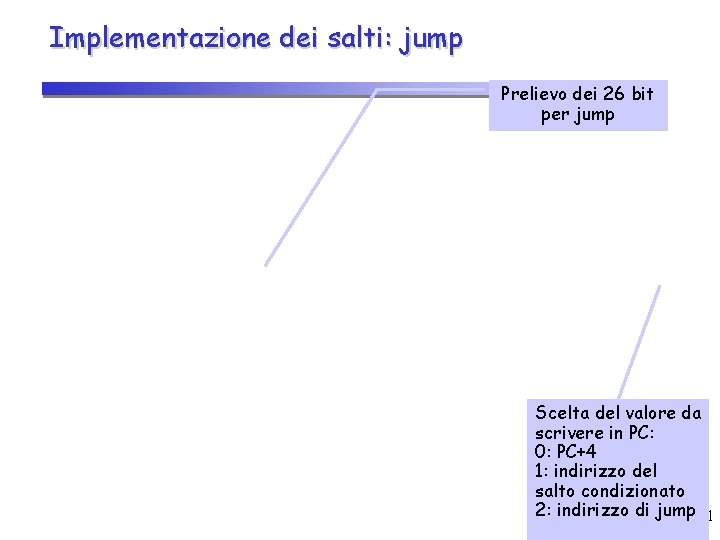

Implementazione dei salti Per le istruzioni di jump e branch, ci sono tre possibili sorgenti per il valore da scrivere in PC L’output della ALU, con il valore PC+4 calcolato durante la fase di fetch dell’istruzione Il registro ALUOut, dove è memorizzato l’indirizzo del branch una volta che è stato calcolato I 26 bit meno significativi dell’IR traslati a sinistra di 2 e concatenati con i 4 bit più significativi del PC incrementato, se l’istruzione è di jump CPU (2) 10

Implementazione dei salti: jump Prelievo dei 26 bit per jump Scelta del valore da scrivere in PC: 0: PC+4 1: indirizzo del salto condizionato 2: indirizzo di jump 11 CPU (2)

Implementazione dei salti: beq In OR con PCWrite per indicare la scrittura di PC Zero (dalla ALU) AND PCWrite. Cond Scelta del valore in PC CPU (2) 12

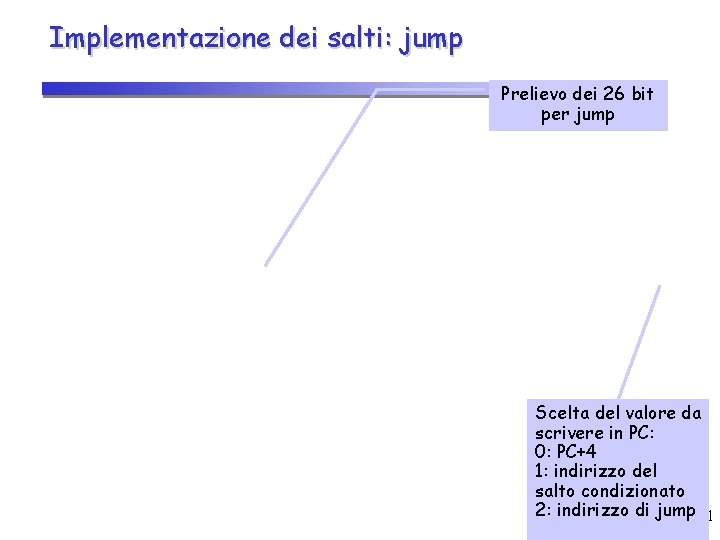

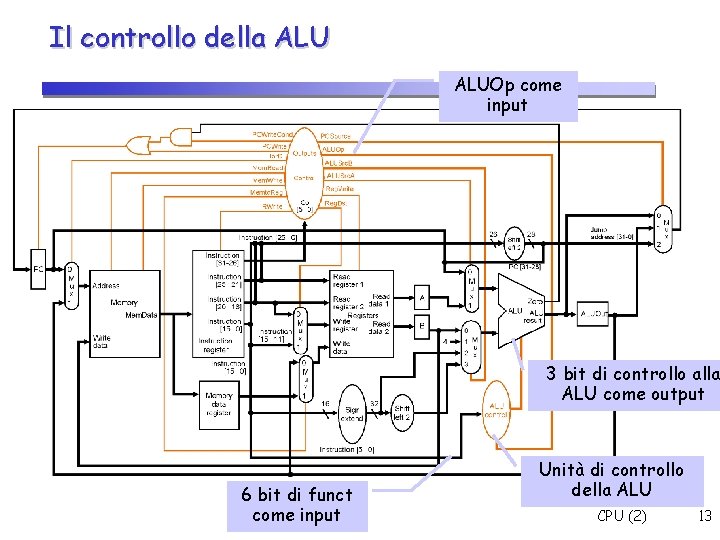

Il controllo della ALUOp come input 3 bit di controllo alla ALU come output 6 bit di funct come input Unità di controllo della ALU CPU (2) 13

L’unità di elaborazione multi-ciclo CPU (2) 14

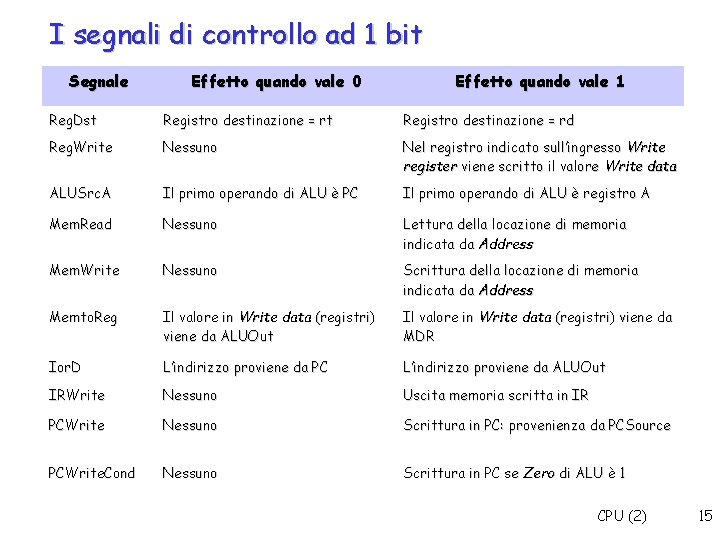

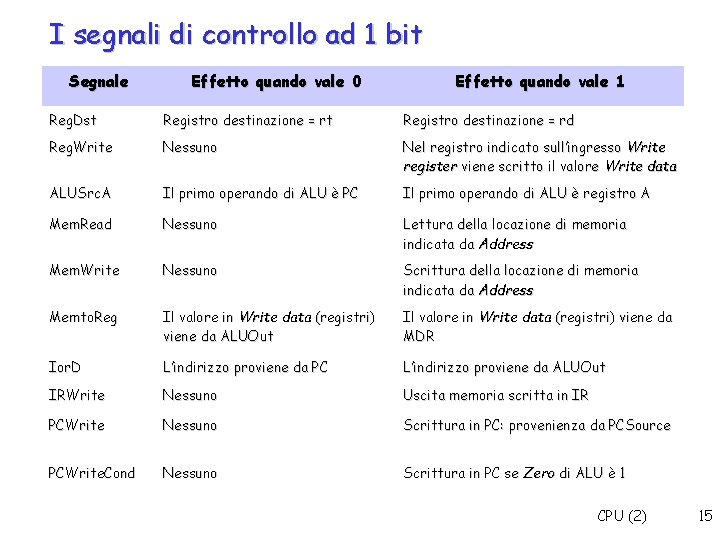

I segnali di controllo ad 1 bit Segnale Effetto quando vale 0 Effetto quando vale 1 Reg. Dst Registro destinazione = rd Reg. Write Nessuno Nel registro indicato sull’ingresso Write register viene scritto il valore Write data ALUSrc. A Il primo operando di ALU è PC Il primo operando di ALU è registro A Mem. Read Nessuno Lettura della locazione di memoria indicata da Address Mem. Write Nessuno Scrittura della locazione di memoria indicata da Address Memto. Reg Il valore in Write data (registri) viene da ALUOut Il valore in Write data (registri) viene da MDR Ior. D L’indirizzo proviene da PC L’indirizzo proviene da ALUOut IRWrite Nessuno Uscita memoria scritta in IR PCWrite Nessuno Scrittura in PC: provenienza da PCSource PCWrite. Cond Nessuno Scrittura in PC se Zero di ALU è 1 CPU (2) 15

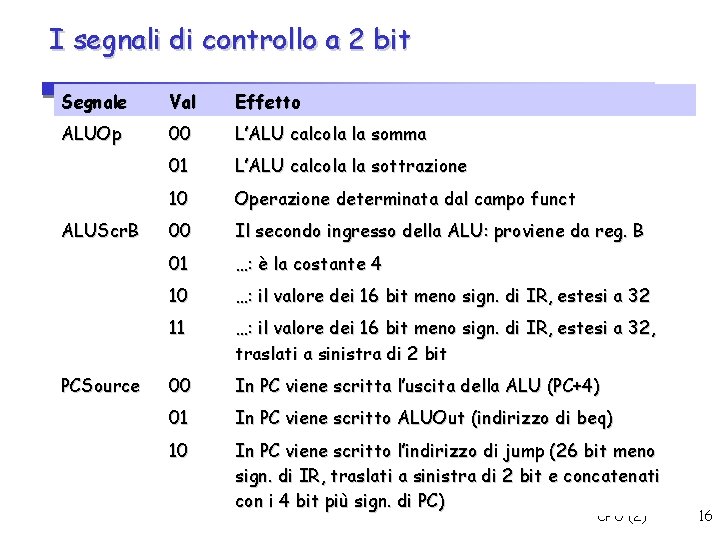

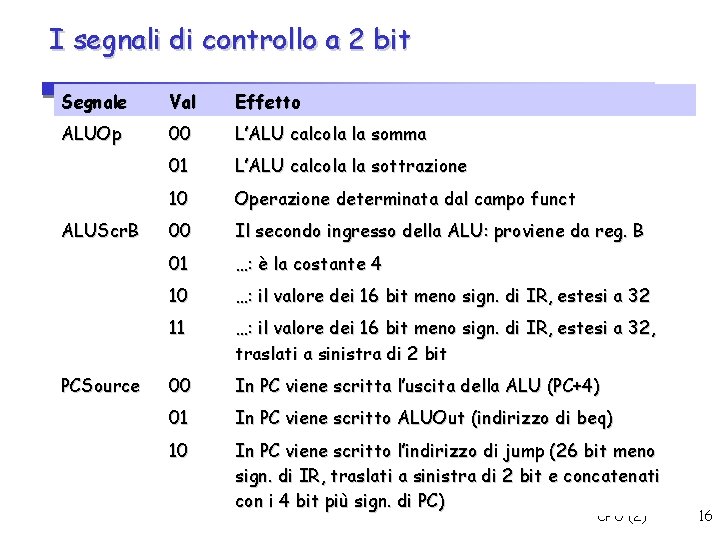

I segnali di controllo a 2 bit Segnale Val Effetto ALUOp 00 L’ALU calcola la somma 01 L’ALU calcola la sottrazione 10 Operazione determinata dal campo funct 00 Il secondo ingresso della ALU: proviene da reg. B 01 …: è la costante 4 10 …: il valore dei 16 bit meno sign. di IR, estesi a 32 11 …: il valore dei 16 bit meno sign. di IR, estesi a 32, traslati a sinistra di 2 bit 00 In PC viene scritta l’uscita della ALU (PC+4) 01 In PC viene scritto ALUOut (indirizzo di beq) 10 In PC viene scritto l’indirizzo di jump (26 bit meno sign. di IR, traslati a sinistra di 2 bit e concatenati con i 4 bit più sign. di PC) ALUScr. B PCSource CPU (2) 16

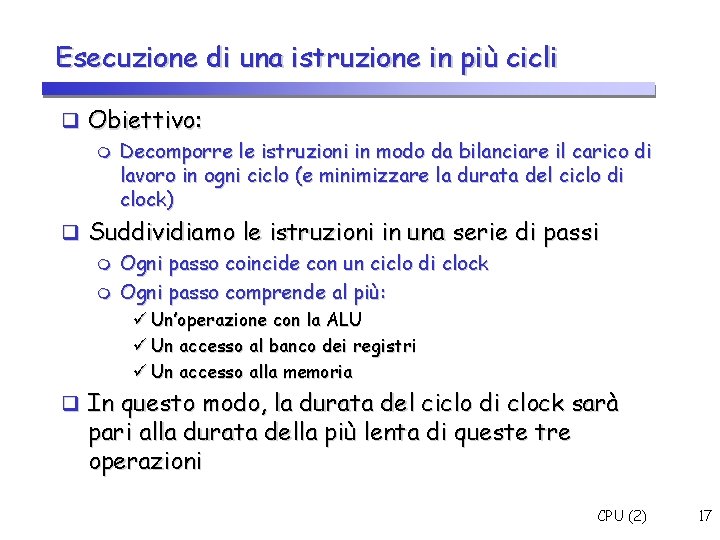

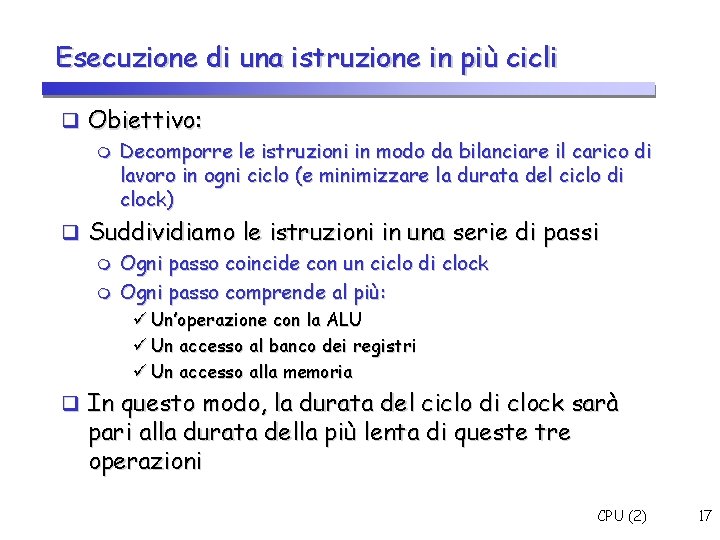

Esecuzione di una istruzione in più cicli Obiettivo: Decomporre le istruzioni in modo da bilanciare il carico di lavoro in ogni ciclo (e minimizzare la durata del ciclo di clock) Suddividiamo le istruzioni in una serie di passi Ogni passo coincide con un ciclo di clock Ogni passo comprende al più: Un’operazione con la ALU Un accesso al banco dei registri Un accesso alla memoria In questo modo, la durata del ciclo di clock sarà pari alla durata della più lenta di queste tre operazioni CPU (2) 17

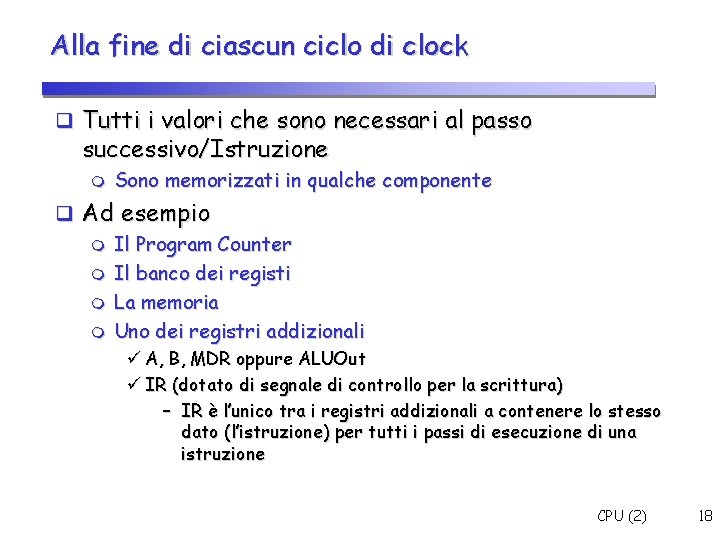

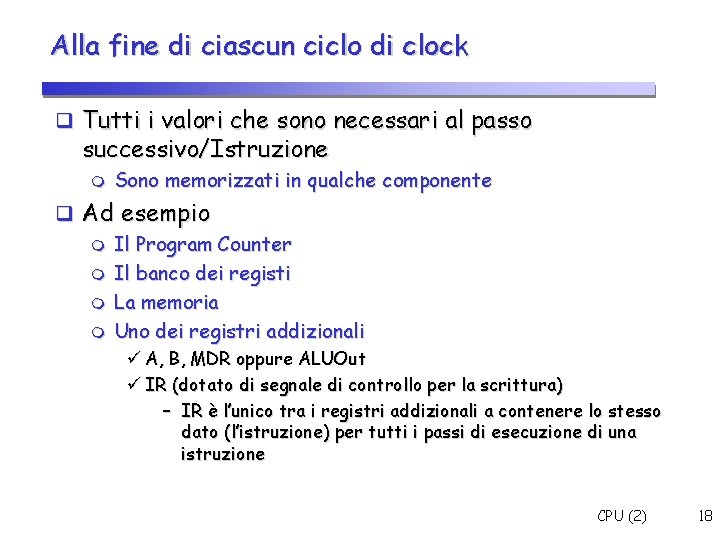

Alla fine di ciascun ciclo di clock Tutti i valori che sono necessari al passo successivo/Istruzione Sono memorizzati in qualche componente Ad esempio Il Program Counter Il banco dei registi La memoria Uno dei registri addizionali A, B, MDR oppure ALUOut IR (dotato di segnale di controllo per la scrittura) – IR è l’unico tra i registri addizionali a contenere lo stesso dato (l’istruzione) per tutti i passi di esecuzione di una istruzione CPU (2) 18

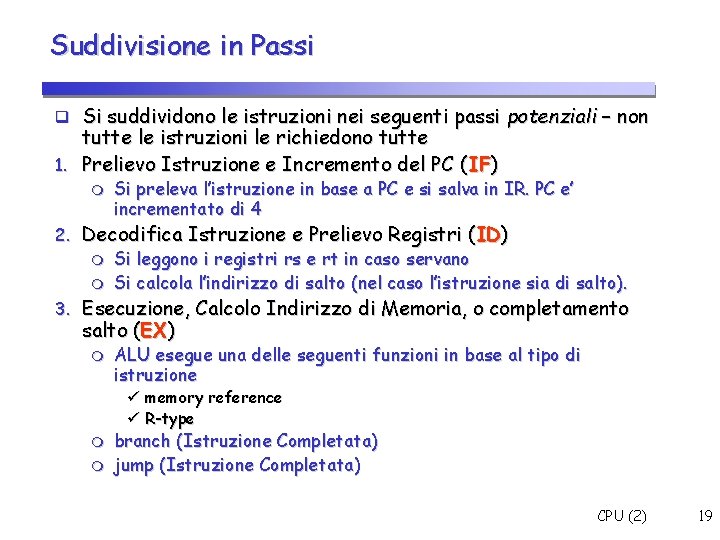

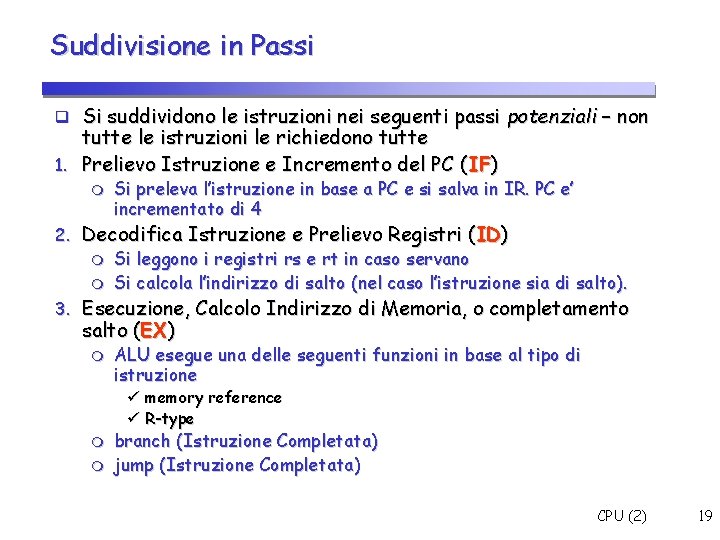

Suddivisione in Passi Si suddividono le istruzioni nei seguenti passi potenziali – non tutte le istruzioni le richiedono tutte 1. Prelievo Istruzione e Incremento del PC (IF) Si preleva l’istruzione in base a PC e si salva in IR. PC e’ incrementato di 4 2. Decodifica Istruzione e Prelievo Registri (ID) Si leggono i registri rs e rt in caso servano Si calcola l’indirizzo di salto (nel caso l’istruzione sia di salto). 3. Esecuzione, Calcolo Indirizzo di Memoria, o completamento salto (EX) ALU esegue una delle seguenti funzioni in base al tipo di istruzione memory reference R-type branch (Istruzione Completata) jump (Istruzione Completata) CPU (2) 19

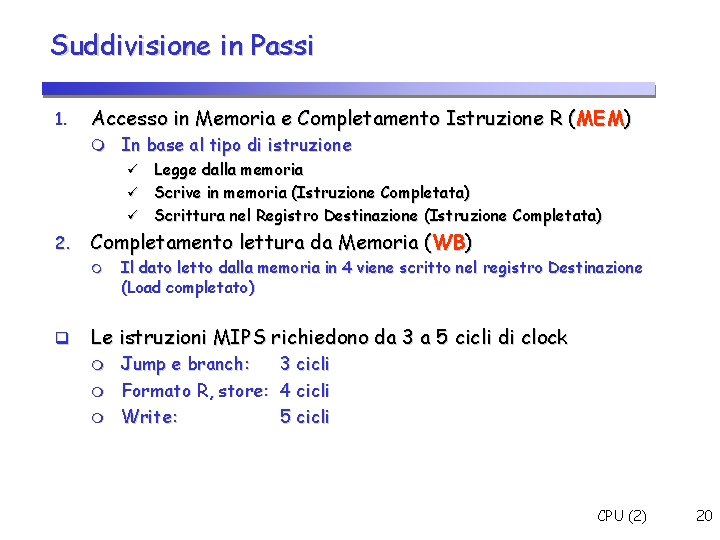

Suddivisione in Passi 1. Accesso in Memoria e Completamento Istruzione R ( MEM) In base al tipo di istruzione Legge dalla memoria Scrive in memoria (Istruzione Completata) Scrittura nel Registro Destinazione (Istruzione Completata) 2. Completamento lettura da Memoria (WB) Il dato letto dalla memoria in 4 viene scritto nel registro Destinazione (Load completato) Le istruzioni MIPS richiedono da 3 a 5 cicli di clock Jump e branch: 3 cicli Formato R, store: 4 cicli Write: 5 cicli CPU (2) 20

![Prelievo dellIstruzione IF IR MPC PC PC 4 PC 4 Prelievo dell’Istruzione (IF) IR = M[PC]; PC = PC + 4; PC + 4](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-21.jpg)

Prelievo dell’Istruzione (IF) IR = M[PC]; PC = PC + 4; PC + 4 4 CPU (2) 21

![Decodifica Istruzione e Lettura Registri ID A RegIR25 21 A Regrs B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-22.jpg)

Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) ALUOut = (PC + sign-extend(IR[15 -0]) << 2) Reg[rs] Branch Target Address PC + 4 Reg[rt] CPU (2) 22

![Formato R EX Esecuzione ALUOut A op B Regrs RType Result PC Formato R: (EX) – Esecuzione ALUOut = A op B Reg[rs] R-Type Result PC](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-23.jpg)

Formato R: (EX) – Esecuzione ALUOut = A op B Reg[rs] R-Type Result PC + 4 Reg[rt] CPU (2) 23

![Formato R MEM Scrittura Registro Dest RegIR15 11 ALUOUT Regrs RType Result Formato R: (MEM) – Scrittura Registro Dest. Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-24.jpg)

Formato R: (MEM) – Scrittura Registro Dest. Reg[IR[15: 11]] = ALUOUT Reg[rs] R-Type Result PC + 4 Reg[rt] CPU (2) 24

![Decodifica Istruzione e Lettura Registri ID A RegIR25 21 A Regrs B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-25.jpg)

Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) ALUOut = (PC + sign-extend(IR[15 -0]) << 2) Reg[rs] Branch Target Address PC + 4 Reg[rt] CPU (2) 25

![Branch EX Aggiornamento PC if A B PC ALUOut Regrs Branch Branch: (EX) – Aggiornamento PC if (A == B) PC = ALUOut; Reg[rs] Branch](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-26.jpg)

Branch: (EX) – Aggiornamento PC if (A == B) PC = ALUOut; Reg[rs] Branch Target Address Reg[rt] CPU (2) 26

![Decodifica Istruzione e Lettura Registri ID A RegIR25 21 A Regrs B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-27.jpg)

Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) ALUOut = (PC + sign-extend(IR[15 -0]) << 2) Reg[rs] Branch Target Address PC + 4 Reg[rt] CPU (2) 27

![Jump EX Aggiornamento PC PC PC31 28 concat IR25 0 2 Jump: (EX) – Aggiornamento PC PC = PC[31 -28] concat (IR[25 -0] << 2)](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-28.jpg)

Jump: (EX) – Aggiornamento PC PC = PC[31 -28] concat (IR[25 -0] << 2) Reg[rs] Branch Target Address Jump Address Reg[rt] CPU (2) 28

![Decodifica Istruzione e Lettura Registri ID A RegIR25 21 A Regrs B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-29.jpg)

Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) ALUOut = (PC + sign-extend(IR[15 -0]) << 2) Reg[rs] Branch Target Address PC + 4 Reg[rt] CPU (2) 29

![Store EX Calcolo Indirizzo ALUOut A signextendIR15 0 Regrs Mem Address PC Store: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-30.jpg)

Store: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC + 4 Reg[rt] CPU (2) 30

![Store MEM Scrittura in Memoria MALUOut B Regrs PC 4 Regrt CPU Store: (MEM) Scrittura in Memoria M[ALUOut] = B; Reg[rs] PC + 4 Reg[rt] CPU](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-31.jpg)

Store: (MEM) Scrittura in Memoria M[ALUOut] = B; Reg[rs] PC + 4 Reg[rt] CPU (2) 31

![Decodifica Istruzione e Lettura Registri ID A RegIR25 21 A Regrs B Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-32.jpg)

Decodifica Istruzione e Lettura Registri (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) ALUOut = (PC + sign-extend(IR[15 -0]) << 2) Reg[rs] Branch Target Address PC + 4 Reg[rt] CPU (2) 32

![Load EX Calcolo Indirizzo ALUOut A signextendIR15 0 Regrs Mem Address PC Load: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-33.jpg)

Load: (EX) Calcolo Indirizzo ALUOut = A + sign-extend(IR[15 -0]); Reg[rs] Mem. Address PC + 4 Reg[rt] CPU (2) 33

![Load MEM Lettura in Memoria MDR MALUOut Regrs Mem Address PC 4 Load: (MEM) Lettura in Memoria MDR = M[ALUOut]; Reg[rs] Mem. Address PC + 4](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-34.jpg)

Load: (MEM) Lettura in Memoria MDR = M[ALUOut]; Reg[rs] Mem. Address PC + 4 Mem. Data Reg[rt] CPU (2) 34

![Load WB Scrittura nel Registro Dest RegIR20 16 MDR Regrs Mem Address Load: (WB) – Scrittura nel Registro Dest. Reg[IR[20 -16]] = MDR; Reg[rs] Mem. Address](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-35.jpg)

Load: (WB) – Scrittura nel Registro Dest. Reg[IR[20 -16]] = MDR; Reg[rs] Mem. Address PC + 4 Mem. Data Reg[rt] CPU (2) 35

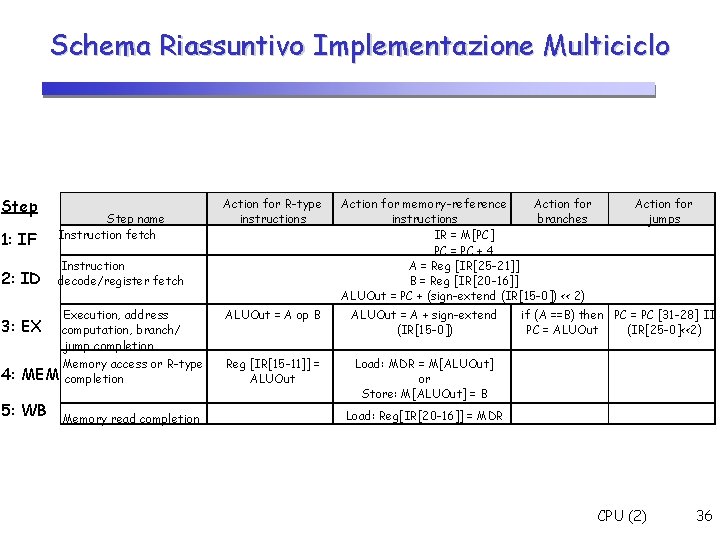

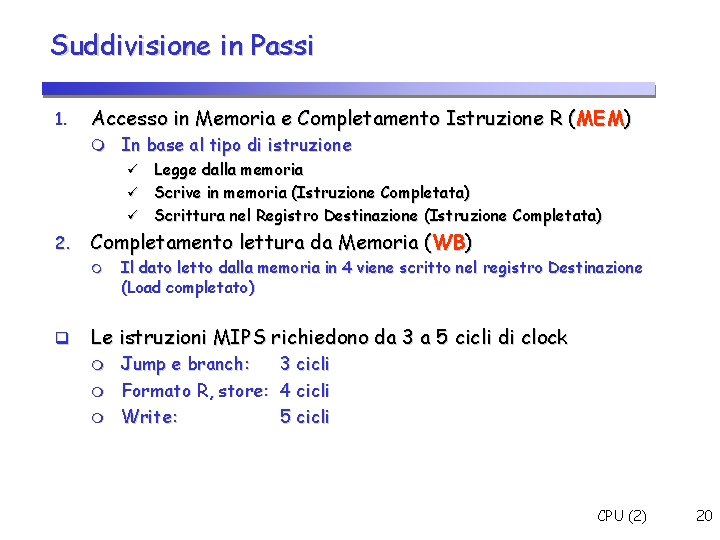

Schema Riassuntivo Implementazione Multiciclo Step 1: IF Step name Instruction fetch Action for R-type instructions Action for memory-reference Action for instructions branches IR = M[PC] PC = PC + 4 A = Reg [IR[25 -21]] B = Reg [IR[20 -16]] ALUOut = PC + (sign-extend (IR[15 -0]) << 2) 2: ID Instruction decode/register fetch 3: EX Execution, address computation, branch/ jump completion ALUOut = A op B ALUOut = A + sign-extend (IR[15 -0]) 4: MEM Memory access or R-type completion Reg [IR[15 -11]] = ALUOut Load: MDR = M[ALUOut] or Store: M[ALUOut] = B 5: WB Memory read completion Action for jumps if (A ==B) then PC = PC [31 -28] II PC = ALUOut (IR[25 -0]<<2) Load: Reg[IR[20 -16]] = MDR CPU (2) 36

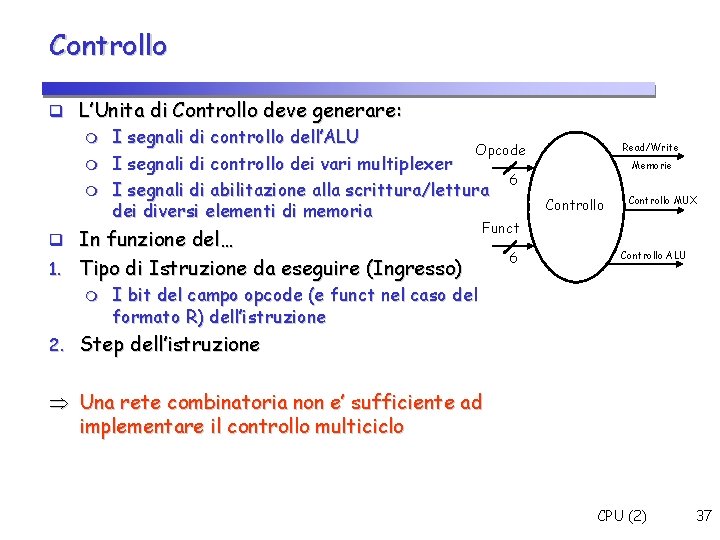

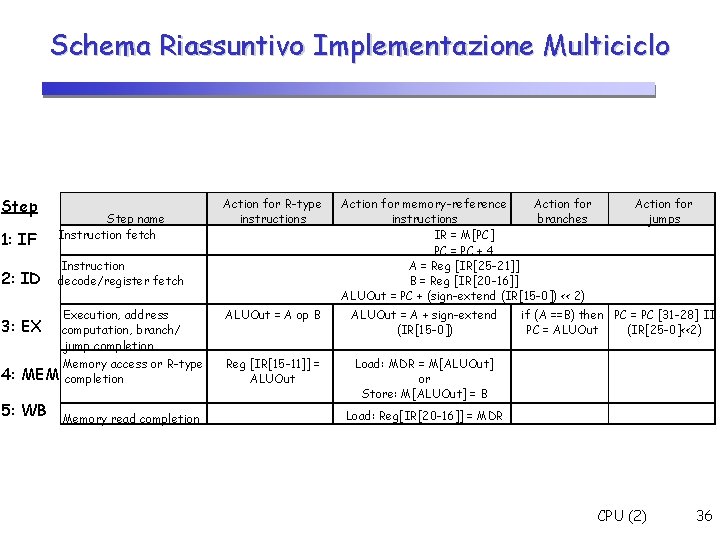

Controllo L’Unita di Controllo deve generare: I segnali di controllo dell’ALU Opcode I segnali di controllo dei vari multiplexer 6 I segnali di abilitazione alla scrittura/lettura dei diversi elementi di memoria In funzione del… Read/Write Memorie Controllo MUX Funct 1. Tipo di Istruzione da eseguire (Ingresso) I bit del campo opcode (e funct nel caso del formato R) dell’istruzione 6 Controllo ALU 2. Step dell’istruzione Una rete combinatoria non e’ sufficiente ad implementare il controllo multiciclo CPU (2) 37

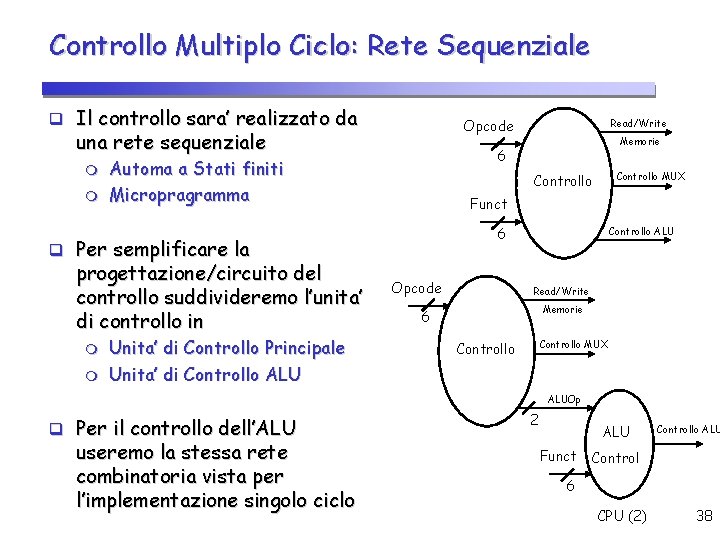

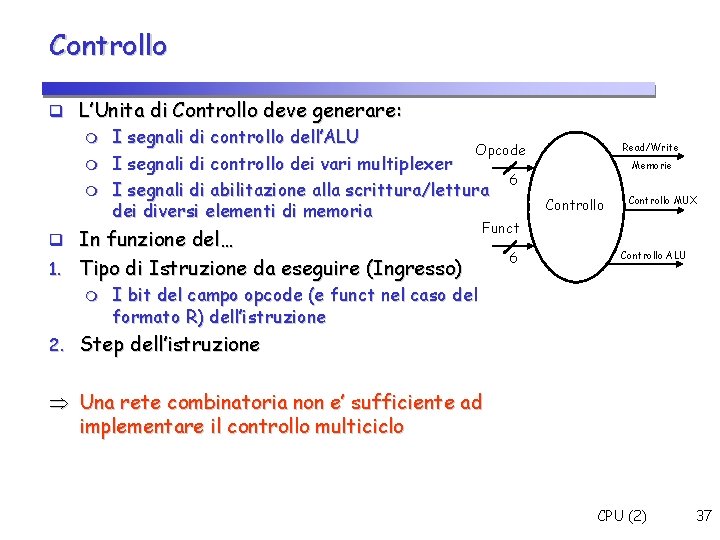

Controllo Multiplo Ciclo: Rete Sequenziale Il controllo sara’ realizzato da Opcode una rete sequenziale Unita’ di Controllo Principale Unita’ di Controllo ALU Controllo MUX Controllo Funct 6 Per semplificare la Memorie 6 Automa a Stati finiti Micropragramma progettazione/circuito del controllo suddivideremo l’unita’ di controllo in Read/Write Opcode Controllo ALU Read/Write Memorie 6 Controllo MUX Controllo ALUOp Per il controllo dell’ALU useremo la stessa rete combinatoria vista per l’implementazione singolo ciclo 2 ALU Funct Controllo ALU Control 6 CPU (2) 38

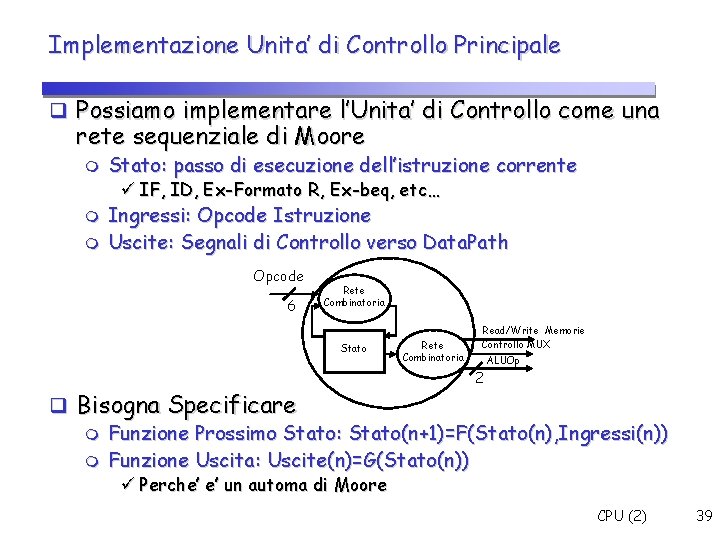

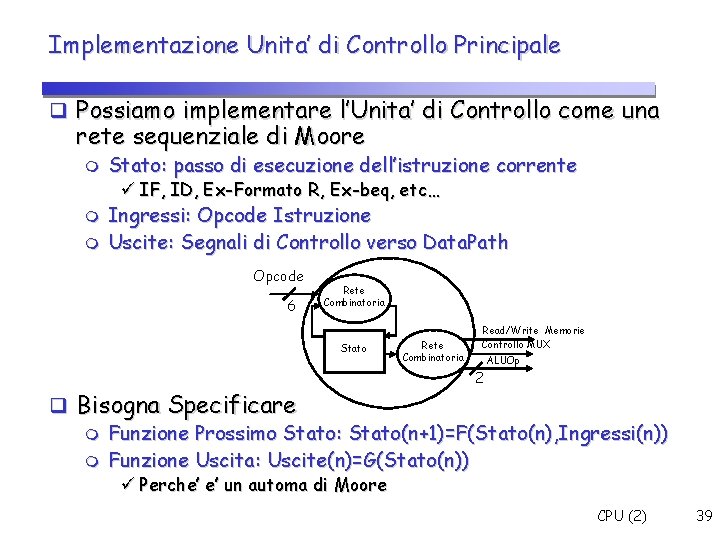

Implementazione Unita’ di Controllo Principale Possiamo implementare l’Unita’ di Controllo come una rete sequenziale di Moore Stato: passo di esecuzione dell’istruzione corrente IF, ID, Ex-Formato R, Ex-beq, etc… Ingressi: Opcode Istruzione Uscite: Segnali di Controllo verso Data. Path Opcode 6 Rete Combinatoria Stato Rete Combinatoria Read/Write Memorie Controllo MUX ALUOp 2 Bisogna Specificare Funzione Prossimo Stato: Stato(n+1)=F(Stato(n), Ingressi(n)) Funzione Uscita: Uscite(n)=G(Stato(n)) Perche’ e’ un automa di Moore CPU (2) 39

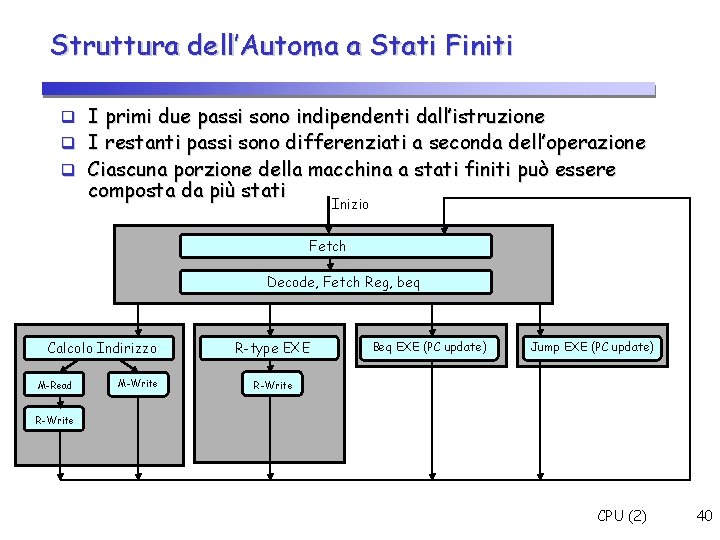

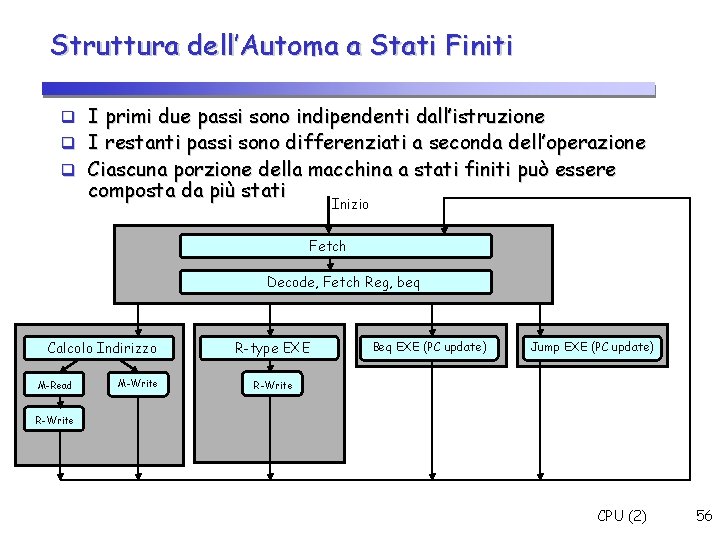

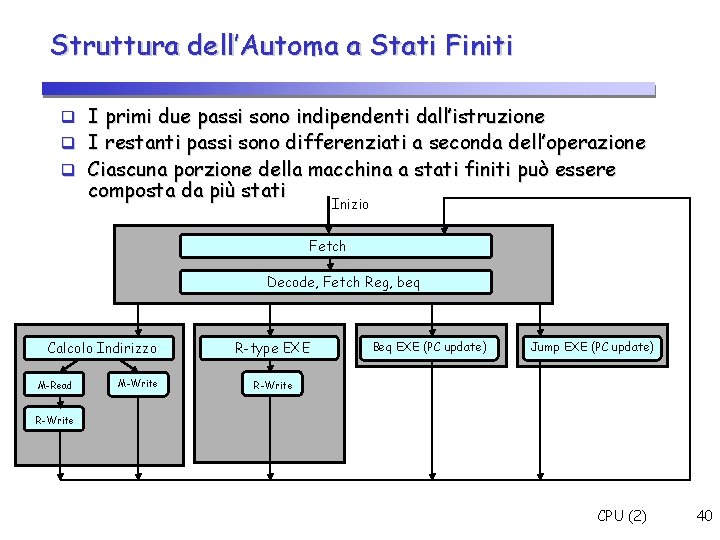

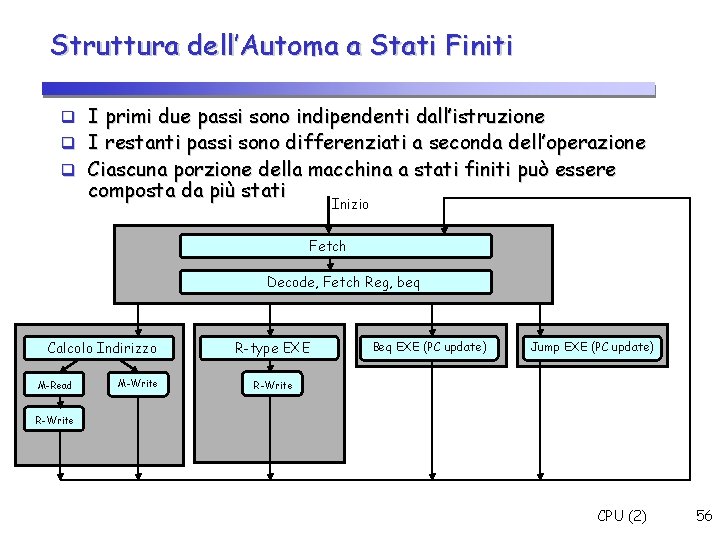

Struttura dell’Automa a Stati Finiti I primi due passi sono indipendenti dall’istruzione I restanti passi sono differenziati a seconda dell’operazione Ciascuna porzione della macchina a stati finiti può essere composta da più stati Inizio Fetch Decode, Fetch Reg, beq Calcolo Indirizzo M-Read M-Write R-type EXE Beq EXE (PC update) Jump EXE (PC update) R-Write CPU (2) 40

![Segnali di Controllo IF IR MPC Mem Read1 IRWrite1 Ior Segnali di Controllo: (IF) IR = M[PC]; - Mem. Read=1 - IRWrite=1 - Ior.](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-41.jpg)

Segnali di Controllo: (IF) IR = M[PC]; - Mem. Read=1 - IRWrite=1 - Ior. D=0 PC = PC + 4; ALUSrc. A=0, ALUSrc. B=01 ALUOp=00 PCWrite=1, PCSource=00 1 1 0 0 X 0 010 0 1 X 0 1 CPU (2) 41

![Segnali di Controllo ID A RegIR25 21 A Regrs B RegIR20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-42.jpg)

Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) - A e B sempre sovrascritti (nessun segnale di controllo) ALUOut = (PC + sign-extend(IR[15 -0]) << 2); ALUSrc. A=0, ALUSrc. B=11 ALUOp=00 0 0 X 0 010 X 0 3 CPU (2) 42

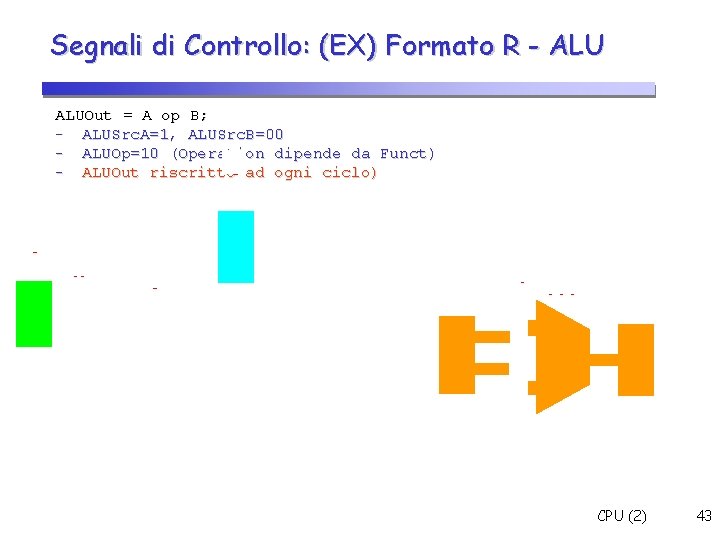

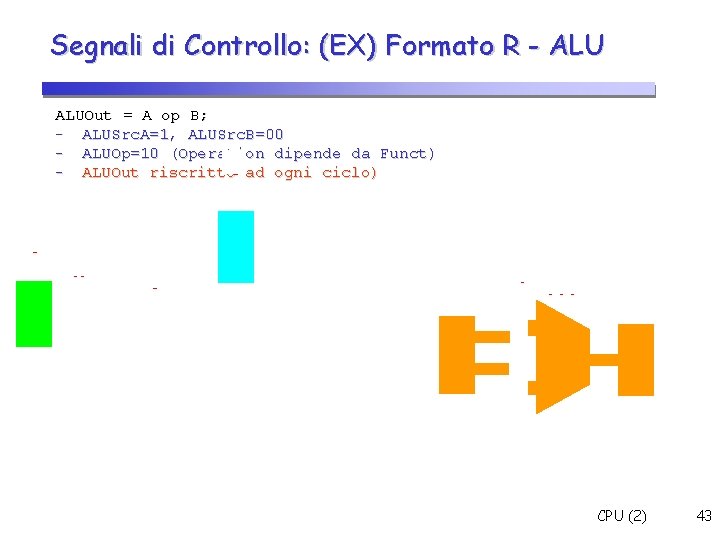

Segnali di Controllo: (EX) Formato R - ALUOut = A op B; - ALUSrc. A=1, ALUSrc. B=00 - ALUOp=10 (Operation dipende da Funct) - ALUOut riscritto 0 ad ogni ciclo) 0 X 1 ? ? ? X 0 0 CPU (2) 43

![Segnali di Controllo MEM Formato R Scrittura Registro Destinazione RegIR15 11 ALUOut Segnali di Controllo: (MEM) Formato R – Scrittura Registro Destinazione Reg[IR[15: 11]] = ALUOut;](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-44.jpg)

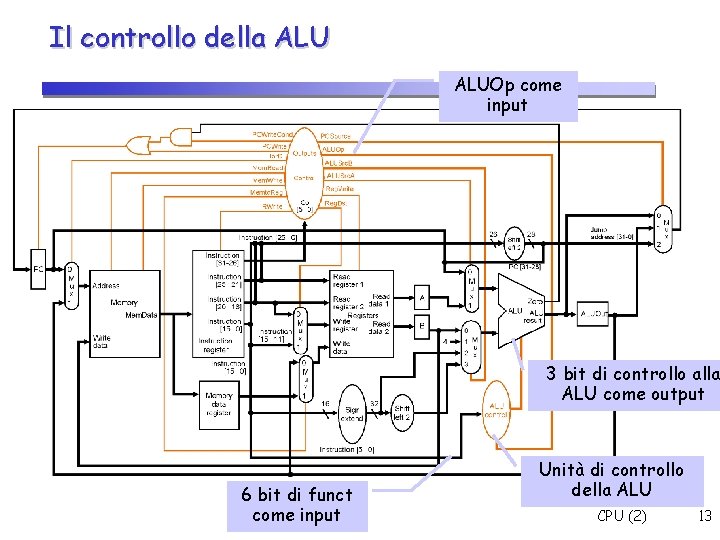

Segnali di Controllo: (MEM) Formato R – Scrittura Registro Destinazione Reg[IR[15: 11]] = ALUOut; - Reg. Dest=1 - Re. Write=1 - Memto. Reg=0 0 (Reg[Rd] = ALUOut) IRWrite I R 0 PCWr* X PC U 1 X 32 0 Memory 5 rt 5 5 0 MUX rd 1 RN 1 RD M D R 1 0 M U X RN 2 WD WD RD 1 RD 2 Mem. Read 0 Reg. Dst 1 immediate Reg. Write 1 16 E X T N D 32 2 4 0 1 M U 2 X 3 M 1 U XXX 0 X 3 U 1 X A B CONCAT Operation 0 M Memto. Reg 0 X ALUSrc. A WN Registers 32 <<2 I[25: 0] 5 Mem. Write ADDR 28 jmpaddr rs Ior. D 0 M Instruction I PCSource Zero ALU OUT X ALUSrc. B <<2 X CPU (2) 44

![Segnali di Controllo ID A RegIR25 21 A Regrs B RegIR20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-45.jpg)

Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) - A e B sempre sovrascritti (nessun segnale di controllo) ALUOut = (PC + sign-extend(IR[15 -0]) << 2); ALUSrc. A=0, ALUSrc. B=11 ALUOp=00 0 0 X 0 010 X 0 3 CPU (2) 45

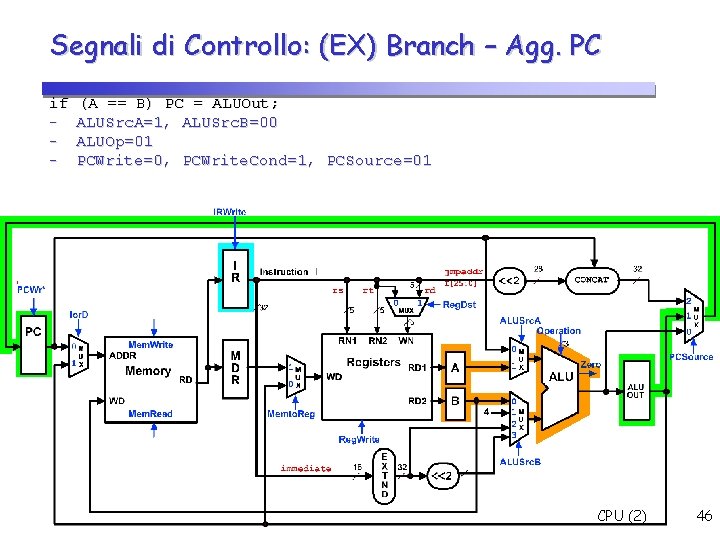

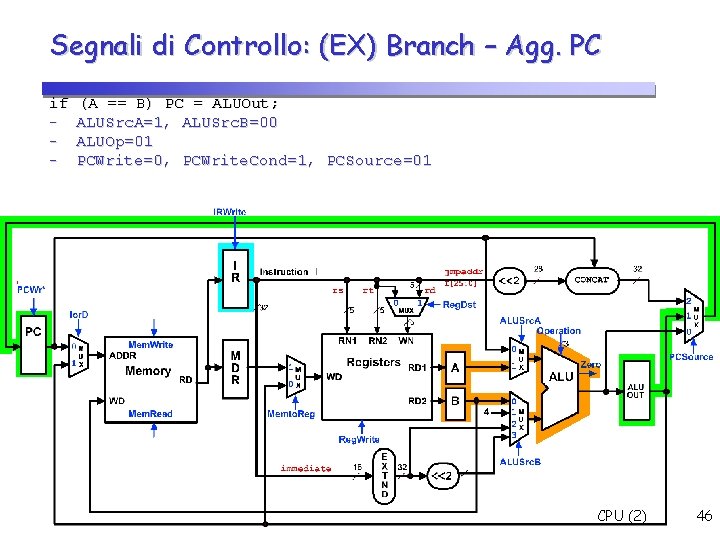

Segnali di Controllo: (EX) Branch – Agg. PC if (A == B) PC = ALUOut; - ALUSrc. A=1, ALUSrc. B=00 - ALUOp=01 - PCWrite=0, PCWrite. Cond=1, PCSource=01 0 1 if Zero=1 X 0 X 1 110 1 0 X 0 0 CPU (2) 46

![Segnali di Controllo ID A RegIR25 21 A Regrs B RegIR20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-47.jpg)

Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) - A e B sempre sovrascritti (nessun segnale di controllo) ALUOut = (PC + sign-extend(IR[15 -0]) << 2); ALUSrc. A=0, ALUSrc. B=11 ALUOp=00 0 0 X 0 010 X 0 3 CPU (2) 47

![Segnali di Controllo EX Jump Agg PC PC PC21 28 concat IR25 Segnali di Controllo: (EX) Jump – Agg. PC PC = PC[21 -28] concat (IR[25](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-48.jpg)

Segnali di Controllo: (EX) Jump – Agg. PC PC = PC[21 -28] concat (IR[25 -0] << 2); - PCWrite=1, PCSource=10 0 1 X 0 X X XXX 2 0 X CPU (2) 48

![Segnali di Controllo ID A RegIR25 21 A Regrs B RegIR20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-49.jpg)

Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) - A e B sempre sovrascritti (nessun segnale di controllo) ALUOut = (PC + sign-extend(IR[15 -0]) << 2); ALUSrc. A=0, ALUSrc. B=11 ALUOp=00 0 0 X 0 010 X 0 3 CPU (2) 49

![Segnali di Controllo EX Store Calc Indirizzo ALUOut A signextendIR15 0 Segnali di Controllo: (EX) Store – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]);](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-50.jpg)

Segnali di Controllo: (EX) Store – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]); - ALUSrc. A=1, ALUSrc. B=10 - ALUOp=00 0 0 X 1 010 X 0 2 CPU (2) 50

![Segnali di Controllo MEM Store Scr in Memoria MemoryALUOut B Ior Segnali di Controllo: (MEM) Store – Scr. in Memoria Memory[ALUOut] = B; - Ior.](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-51.jpg)

Segnali di Controllo: (MEM) Store – Scr. in Memoria Memory[ALUOut] = B; - Ior. D=1 - Mem. Write=1 0 0 1 1 X X XXX X 0 X CPU (2) 51

![Segnali di Controllo ID A RegIR25 21 A Regrs B RegIR20 Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-52.jpg)

Segnali di Controllo: (ID) A = Reg[IR[25 -21]]; (A = Reg[rs]) B = Reg[IR[20 -15]]; (B = Reg[rt]) - A e B sempre sovrascritti (nessun segnale di controllo) ALUOut = (PC + sign-extend(IR[15 -0]) << 2); ALUSrc. A=0, ALUSrc. B=11 ALUOp=00 0 0 X 0 010 X 0 3 CPU (2) 52

![Segnali di Controllo EX Load Calc Indirizzo ALUOut A signextendIR15 0 Segnali di Controllo: (EX) Load – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]);](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-53.jpg)

Segnali di Controllo: (EX) Load – Calc. Indirizzo ALUOut = A + sign-extend(IR[15 -0]); - ALUSrc. A=1, ALUSrc. B=10 - ALUOp=00 0 0 X 1 010 X 0 2 CPU (2) 53

![Segnali di Controllo MEM Load Lett in Memoria MDR MemoryALUOut Ior Segnali di Controllo: (MEM) Load – Lett. in Memoria MDR = Memory[ALUOut]; - Ior.](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-54.jpg)

Segnali di Controllo: (MEM) Load – Lett. in Memoria MDR = Memory[ALUOut]; - Ior. D=1 - Mem. Read=1 0 0 1 0 X X XXX X 1 X 0 X CPU (2) 54

![Segnali di Controllo WB Load Scr Registro di Destinazione RegIR20 16 MDR Segnali di Controllo: (WB) Load – Scr. Registro di Destinazione Reg[IR[20 -16]] = MDR;](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-55.jpg)

Segnali di Controllo: (WB) Load – Scr. Registro di Destinazione Reg[IR[20 -16]] = MDR; - Reg. Dest=0 - Reg. Write=1 - Memto. Reg=0 IRWrite I R 0 PCWr* 0 Instruction I rs X 0 Ior. D 32 U 1 X 5 0 MUX rd 1 RN 1 RD M D R 0 1 M U X RN 2 WD WD RD 1 RD 2 Mem. Read 0 0 immediate B 1 E X T N D 32 CONCAT 2 XXX 4 0 1 M U 2 X 3 0 X 3 U 1 X M 1 U Operation A Reg. Write 16 ALUSrc. A 0 M Memto. Reg 0 X Reg. Dst WN Registers 32 <<2 I[25: 0] 5 Mem. Write ADDR Memory 5 rt 5 PC 0 M 28 jmpaddr PCSource Zero ALU OUT X ALUSrc. B <<2 X CPU (2) 55

Struttura dell’Automa a Stati Finiti I primi due passi sono indipendenti dall’istruzione I restanti passi sono differenziati a seconda dell’operazione Ciascuna porzione della macchina a stati finiti può essere composta da più stati Inizio Fetch Decode, Fetch Reg, beq Calcolo Indirizzo M-Read M-Write R-type EXE Beq EXE (PC update) Jump EXE (PC update) R-Write CPU (2) 56

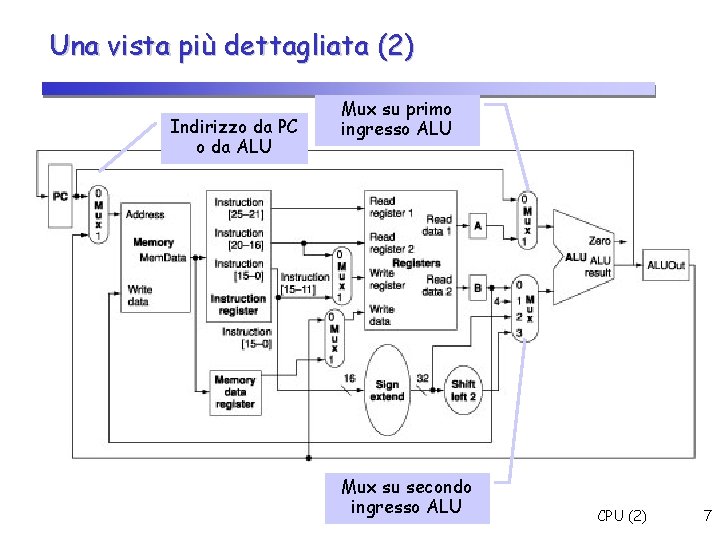

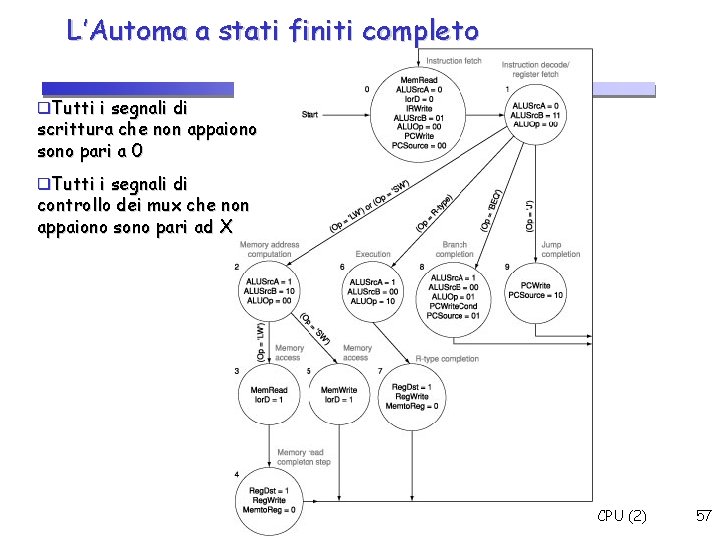

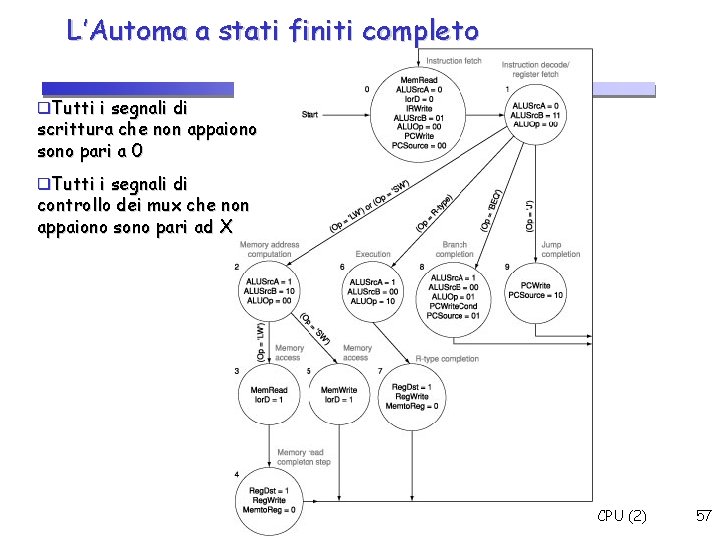

L’Automa a stati finiti completo Tutti i segnali di scrittura che non appaiono sono pari a 0 Tutti i segnali di controllo dei mux che non appaiono sono pari ad X CPU (2) 57

![Unita di Controllo Funzione di Uscita Outputs Input Values Current State3 0 0000 0001 Unita’ di Controllo: Funzione di Uscita Outputs Input Values (Current State[3 -0]) 0000 0001](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-58.jpg)

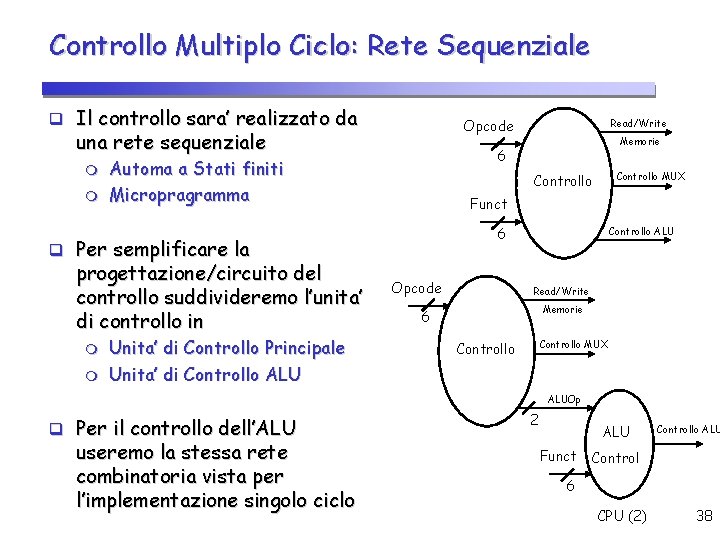

Unita’ di Controllo: Funzione di Uscita Outputs Input Values (Current State[3 -0]) 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 PCWrite 1 0 0 0 0 1 PCWrite. Cond X 0 0 0 0 1 X Ior. D 0 X X 1 X X Mem. Read 1 0 0 0 0 Mem. Write 0 0 0 1 0 0 IRWrite 1 0 0 0 0 0 Memto. Reg X X 1 X X 0 X X PCSource 00 XX XX 01 10 ALUOp 00 00 00 XX XX XX 10 XX 01 XX ALUSrc. B 01 11 10 XX XX XX 00 XX ALUSrc. A 0 0 1 X X X 1 X Reg. Write 0 0 1 0 0 CPU (2) 58

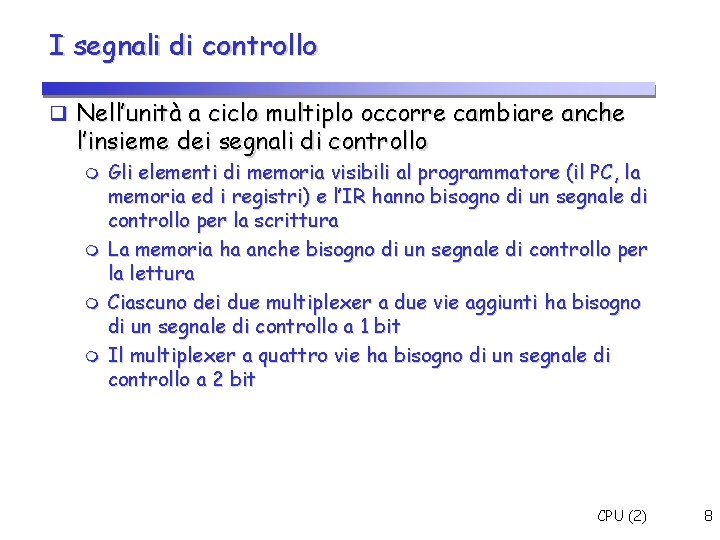

![Unita di Controllo Funzione Prossimo Stato Current Inst31 26 State 00000010 000100 3 0 Unita’ di Controllo: Funzione Prossimo Stato Current Inst[31 -26] State 00000010 000100 [3 -0]](https://slidetodoc.com/presentation_image_h2/4cc12e42b91986ff109da3e8803d7332/image-59.jpg)

Unita’ di Controllo: Funzione Prossimo Stato Current Inst[31 -26] State 00000010 000100 [3 -0] (R(jmp) (beq) type) (Op[5 -0]) 100011 (lw) 101011 (sw) Any other 0000 0001 0001 0110 1001 1000 0010 illegal 0010 XXXX 0011 0101 illegal 0011 XXXX 0100 XXXX illegal 0100 XXXX 0000 XXXX illegal 0101 XXXX 0000 illegal 0110 0111 XXXX illegal 0111 0000 XXXX illegal 1000 XXXX 0000 XXXX CPU (2) illegal 59

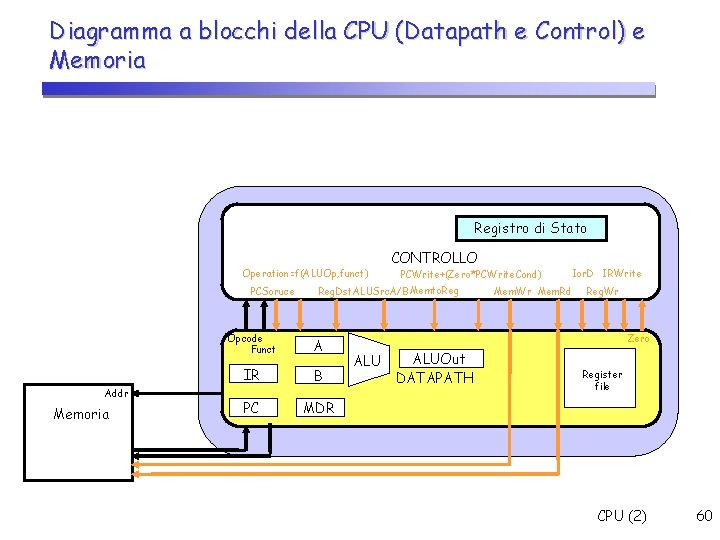

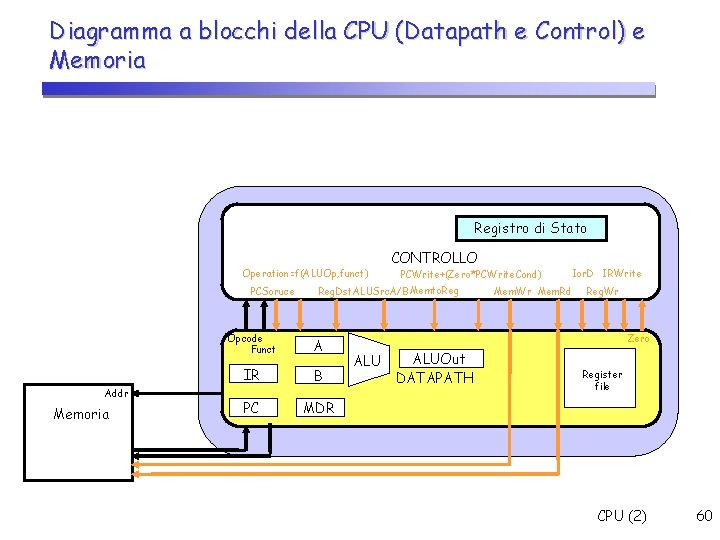

Diagramma a blocchi della CPU (Datapath e Control) e Memoria Registro di Stato Operation=f(ALUOp, funct) PCSoruce Addr Memoria CONTROLLO PCWrite+(Zero*PCWrite. Cond) Reg. Dst. ALUSrc. A/B Memto. Reg Opcode Funct A IR B PC MDR Ior. D IRWrite Mem. Wr Mem. Rd Reg. Wr Zero ALUOut DATAPATH Register file CPU (2) 60

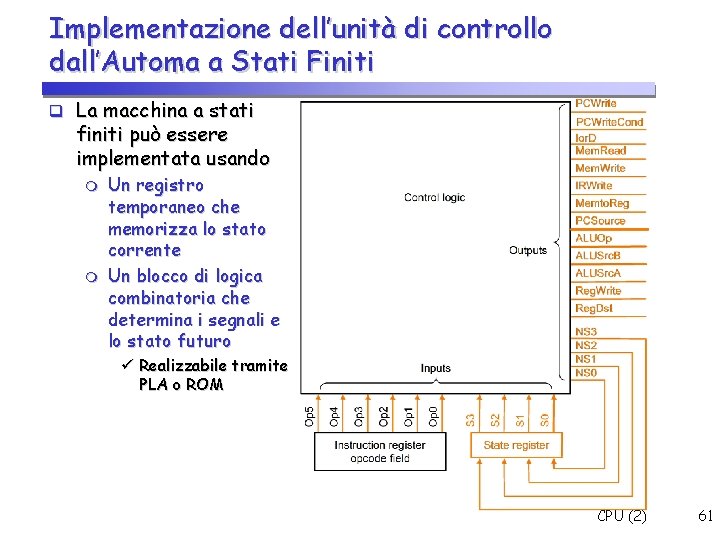

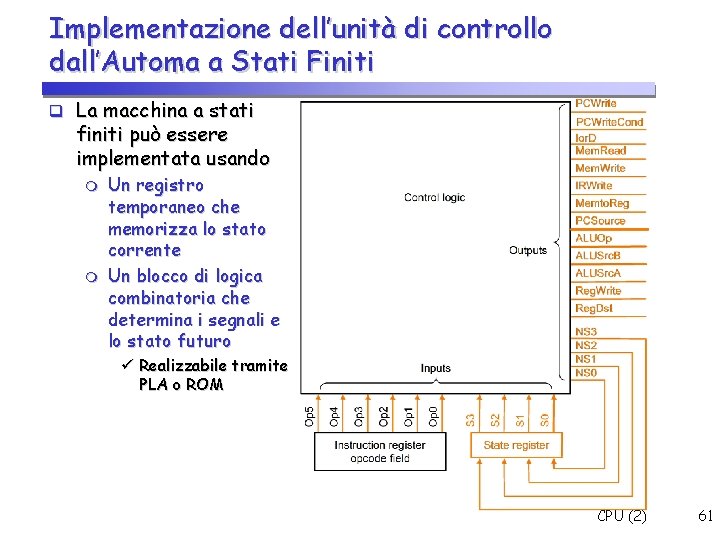

Implementazione dell’unità di controllo dall’Automa a Stati Finiti La macchina a stati finiti può essere implementata usando Un registro temporaneo che memorizza lo stato corrente Un blocco di logica combinatoria che determina i segnali e lo stato futuro Realizzabile tramite PLA o ROM CPU (2) 61

Implementazione Controllo Tramite PLA Blocco combinatorio della rete sequenziale puo’ essere implementato con logica digitale a 2 livelli PLA Numero minimo di porte logiche # celle= #ingresso*#termini prodotto+#uscite*termini prodotto 10*17+20*17=510 celle PLA Non modificabile Poco flessibile Soluzione efficiente per piccoli circuiti CPU (2) 62

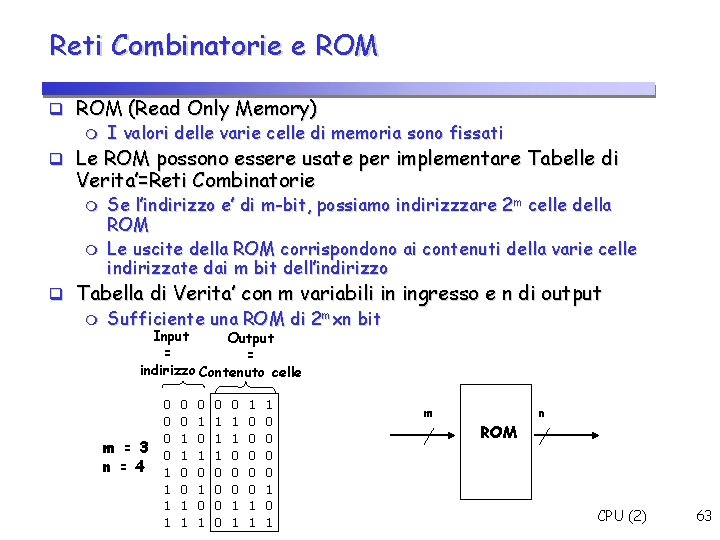

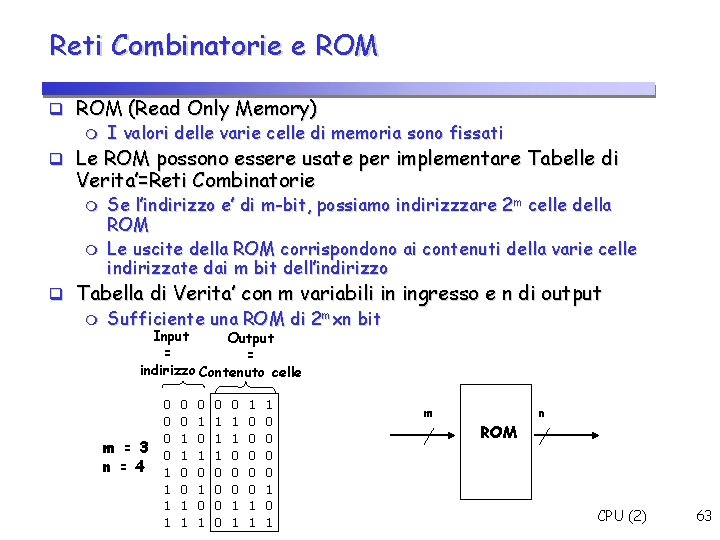

Reti Combinatorie e ROM (Read Only Memory) I valori delle varie celle di memoria sono fissati Le ROM possono essere usate per implementare Tabelle di Verita’=Reti Combinatorie Se l’indirizzo e’ di m-bit, possiamo indirizzzare 2 m celle della ROM Le uscite della ROM corrispondono ai contenuti della varie celle indirizzate dai m bit dell’indirizzo Tabella di Verita’ con m variabili in ingresso e n di output Sufficiente una ROM di 2 mxn bit Input Output = = indirizzo Contenuto celle m = 3 n = 4 0 0 1 1 0 1 0 1 0 1 1 1 0 0 0 1 1 1 0 0 0 0 1 m ROM n CPU (2) 63

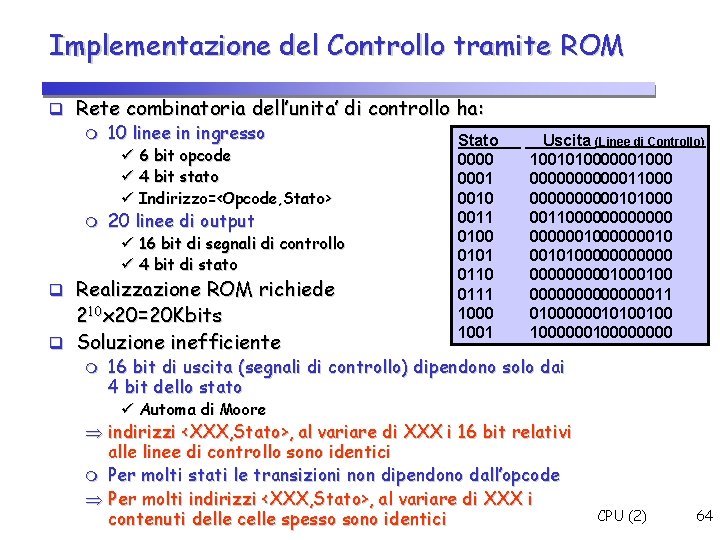

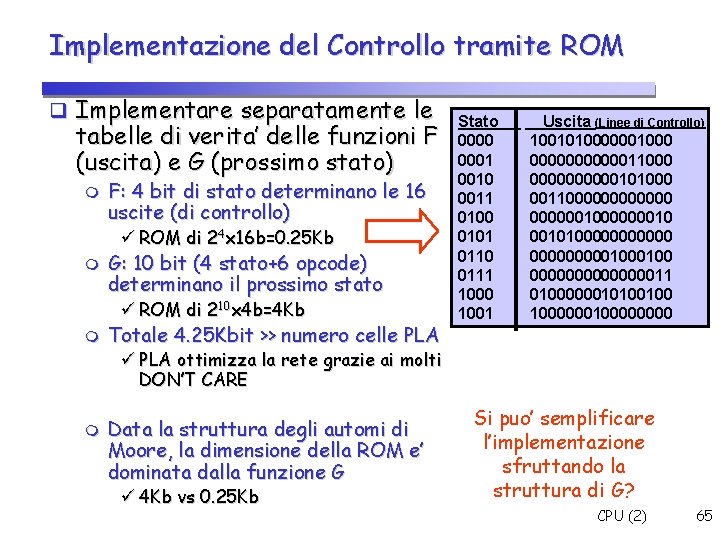

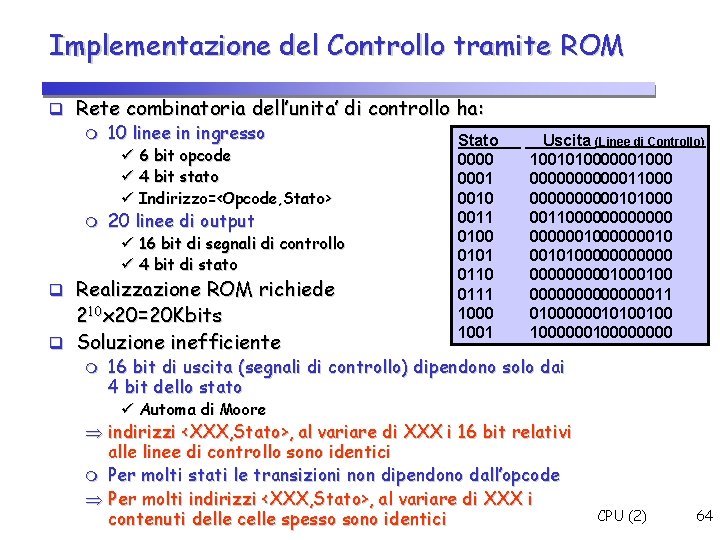

Implementazione del Controllo tramite ROM Rete combinatoria dell’unita’ di controllo ha: 10 linee in ingresso Stato 6 bit opcode 4 bit stato Indirizzo=<Opcode, Stato> 20 linee di output 16 bit di segnali di controllo 4 bit di stato Realizzazione ROM richiede 210 x 20=20 Kbits Soluzione inefficiente 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 __Uscita (Linee di Controllo) 1001010000001000 00000011000 00000101000 001100000010 00101000000100 000000011 0100000010100100 100000000 16 bit di uscita (segnali di controllo) dipendono solo dai 4 bit dello stato Automa di Moore indirizzi <XXX, Stato>, al variare di XXX i 16 bit relativi alle linee di controllo sono identici Per molti stati le transizioni non dipendono dall’opcode Per molti indirizzi <XXX, Stato>, al variare di XXX i contenuti delle celle spesso sono identici CPU (2) 64

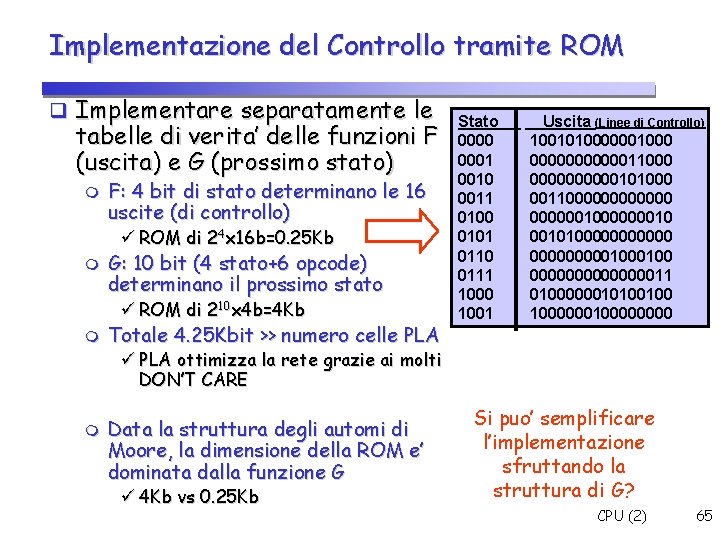

Implementazione del Controllo tramite ROM Implementare separatamente le tabelle di verita’ delle funzioni F (uscita) e G (prossimo stato) F: 4 bit di stato determinano le 16 uscite (di controllo) ROM di 24 x 16 b=0. 25 Kb G: 10 bit (4 stato+6 opcode) determinano il prossimo stato ROM di 210 x 4 b=4 Kb Totale 4. 25 Kbit >> numero celle PLA Stato 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 __Uscita (Linee di Controllo) 1001010000001000 00000011000 00000101000 001100000010 00101000000100 000000011 0100000010100100 100000000 PLA ottimizza la rete grazie ai molti DON’T CARE Data la struttura degli automi di Moore, la dimensione della ROM e’ dominata dalla funzione G 4 Kb vs 0. 25 Kb Si puo’ semplificare l’implementazione sfruttando la struttura di G? CPU (2) 65

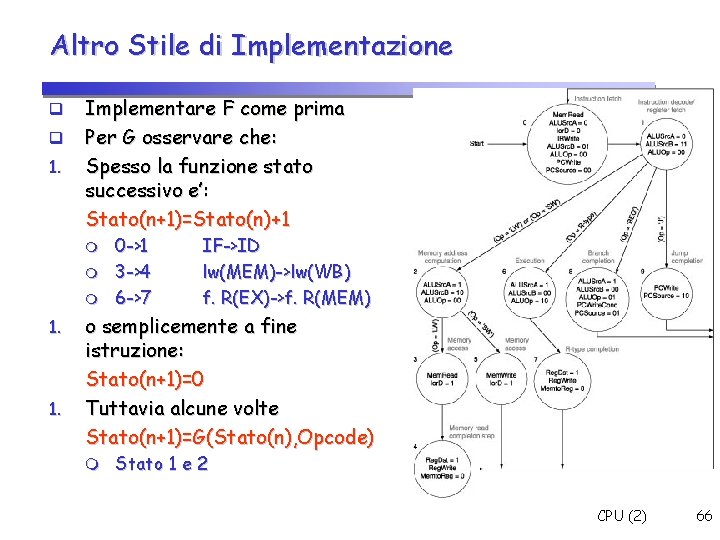

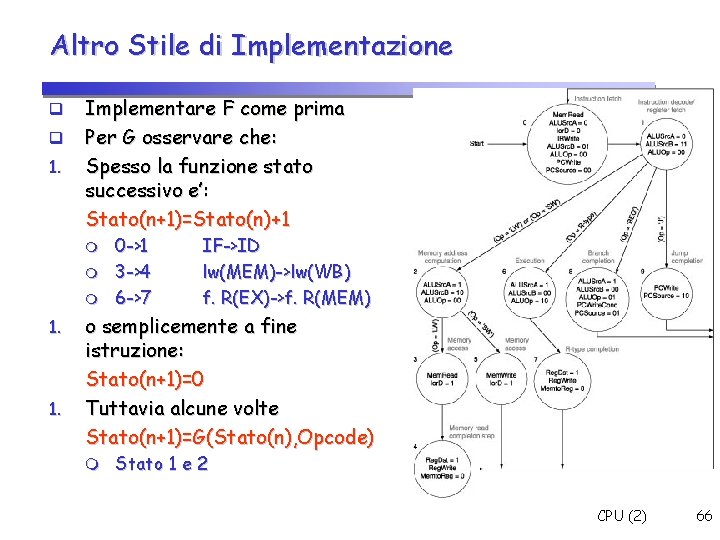

Altro Stile di Implementazione Implementare F come prima Per G osservare che: 1. Spesso la funzione stato successivo e’: Stato(n+1)=Stato(n)+1 1. 0 ->1 3 ->4 6 ->7 IF->ID lw(MEM)->lw(WB) f. R(EX)->f. R(MEM) o semplicemente a fine istruzione: Stato(n+1)=0 Tuttavia alcune volte Stato(n+1)=G(Stato(n), Opcode) Stato 1 e 2 CPU (2) 66

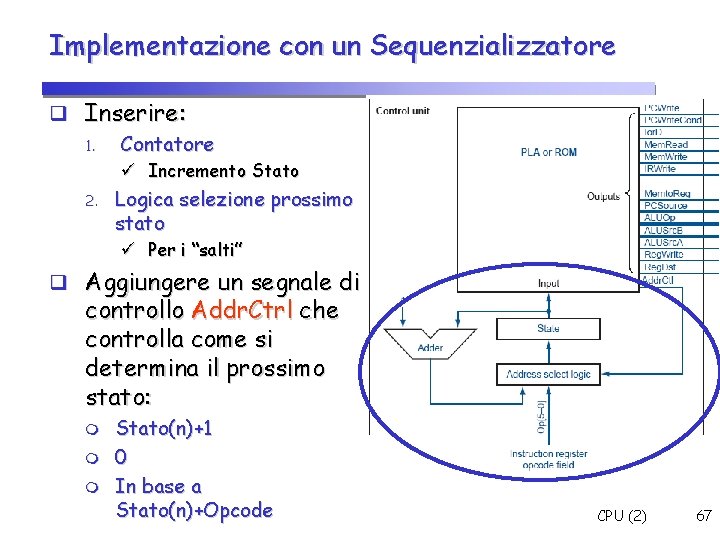

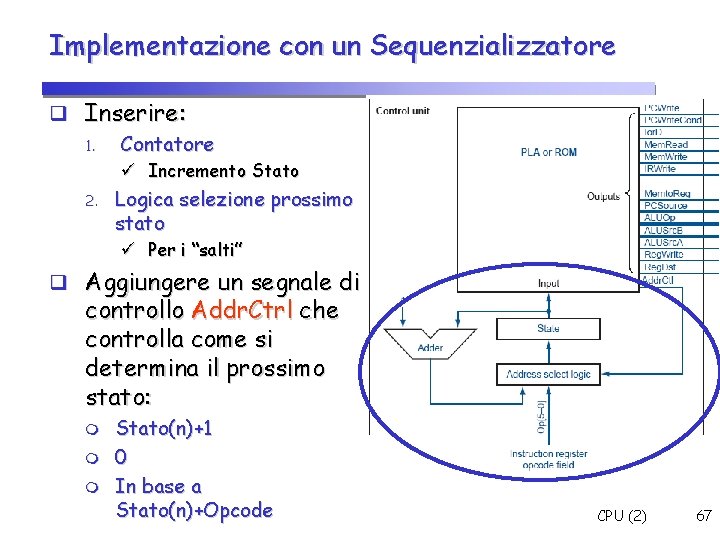

Implementazione con un Sequenzializzatore Inserire: 1. Contatore Incremento Stato 2. Logica selezione prossimo stato Per i “salti” Aggiungere un segnale di controllo Addr. Ctrl che controlla come si determina il prossimo stato: Stato(n)+1 0 In base a Stato(n)+Opcode CPU (2) 67

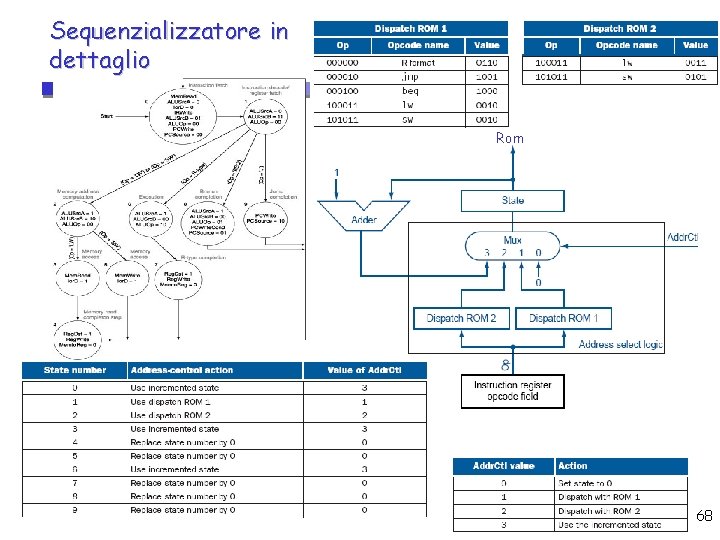

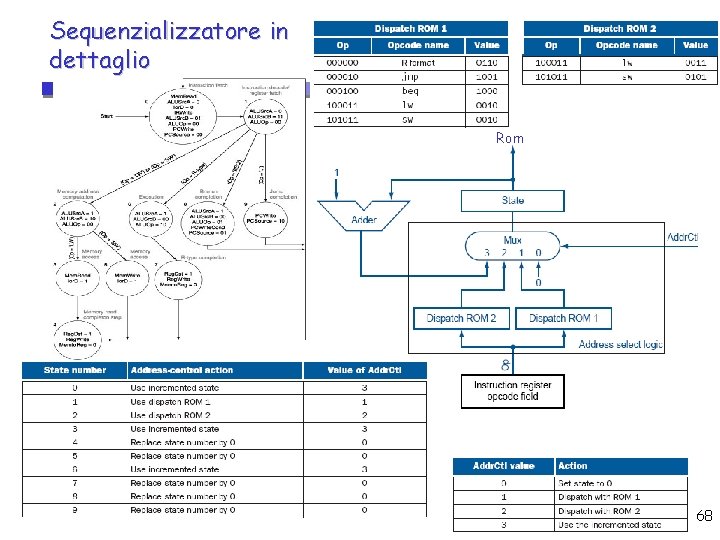

Sequenzializzatore in dettaglio Rom CPU (2) 68

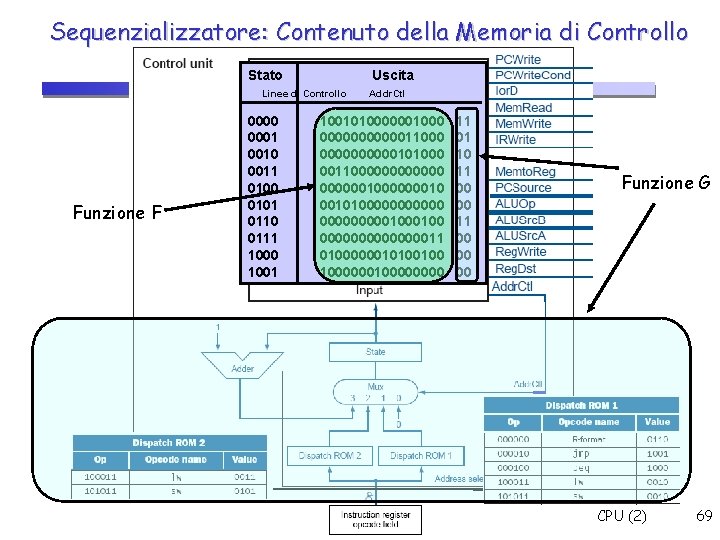

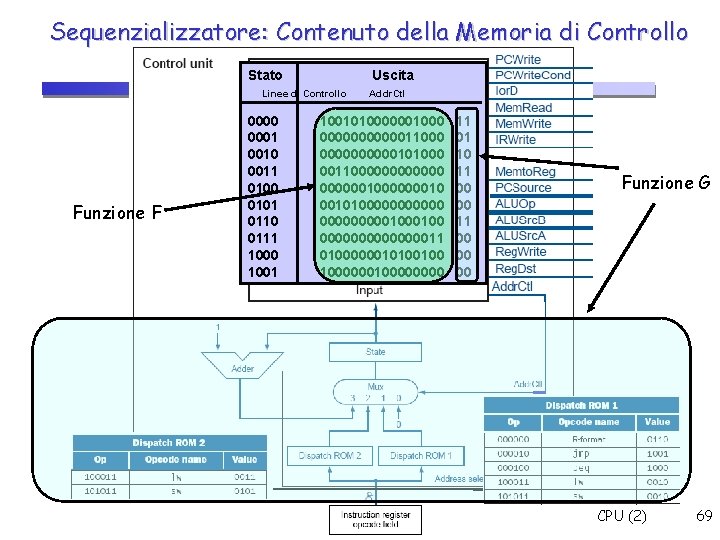

Sequenzializzatore: Contenuto della Memoria di Controllo Stato Uscita Linee di Controllo Funzione F 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 Addr. Ctl 1001010000001000 00000011000 00000101000 001100000010 00101000000100 000000011 0100000010100100 100000000 11 01 10 11 00 00 00 Funzione G CPU (2) 69

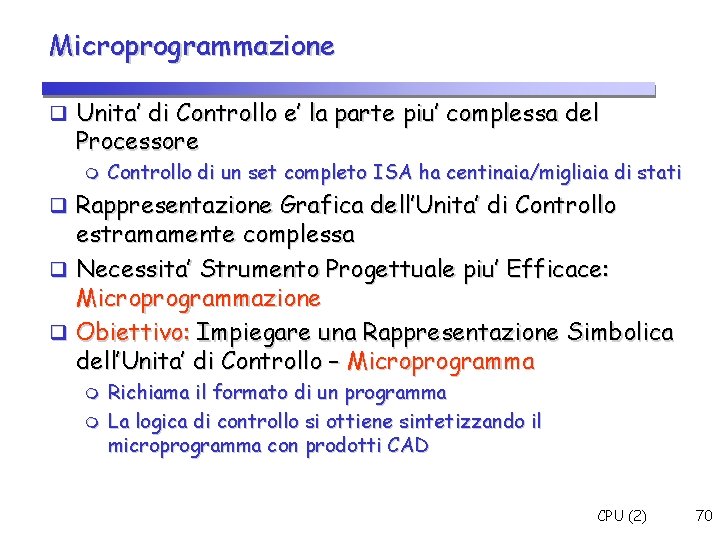

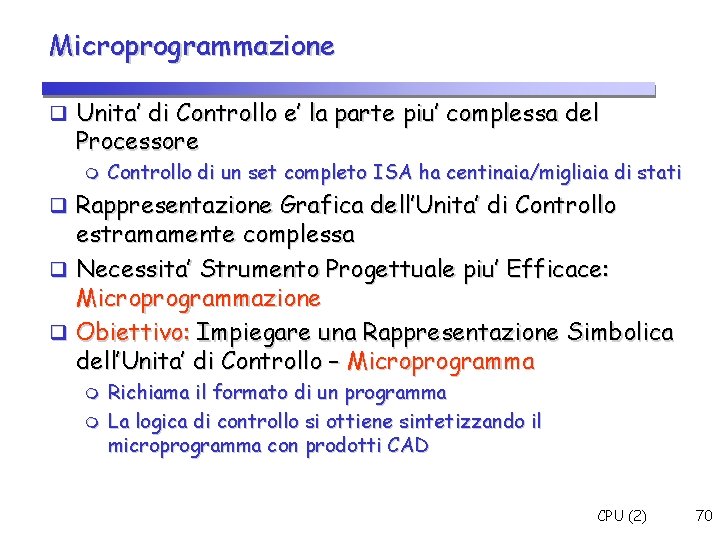

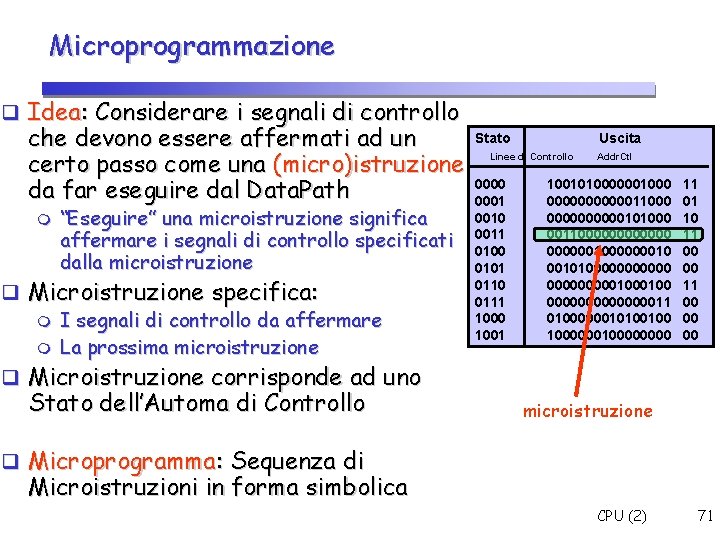

Microprogrammazione Unita’ di Controllo e’ la parte piu’ complessa del Processore Controllo di un set completo ISA ha centinaia/migliaia di stati Rappresentazione Grafica dell’Unita’ di Controllo estramamente complessa Necessita’ Strumento Progettuale piu’ Efficace: Microprogrammazione Obiettivo: Impiegare una Rappresentazione Simbolica dell’Unita’ di Controllo – Microprogramma Richiama il formato di un programma La logica di controllo si ottiene sintetizzando il microprogramma con prodotti CAD CPU (2) 70

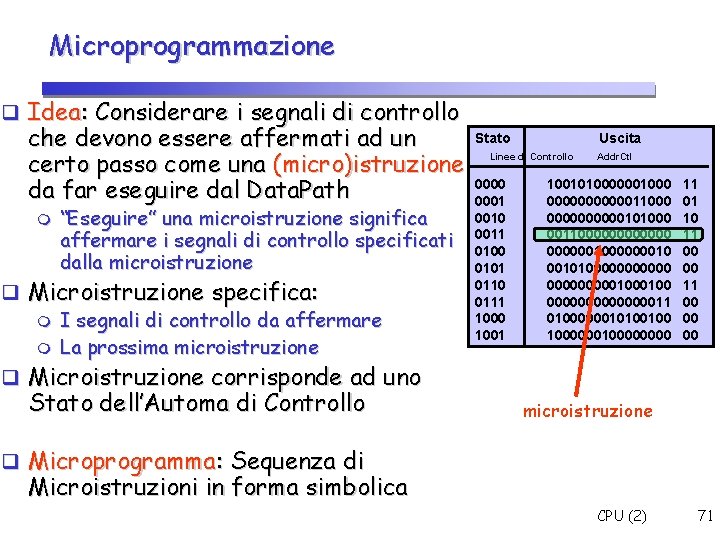

Microprogrammazione Idea: Considerare i segnali di controllo che devono essere affermati ad un certo passo come una (micro)istruzione da far eseguire dal Data. Path “Eseguire” una microistruzione significa affermare i segnali di controllo specificati dalla microistruzione Microistruzione specifica: I segnali di controllo da affermare La prossima microistruzione Microistruzione corrisponde ad uno Stato dell’Automa di Controllo Stato Uscita Linee di Controllo 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 Addr. Ctl 1001010000001000 00000011000 00000101000 001100000010 00101000000100 000000011 0100000010100100 100000000 11 01 10 11 00 00 00 microistruzione Microprogramma: Sequenza di Microistruzioni in forma simbolica CPU (2) 71

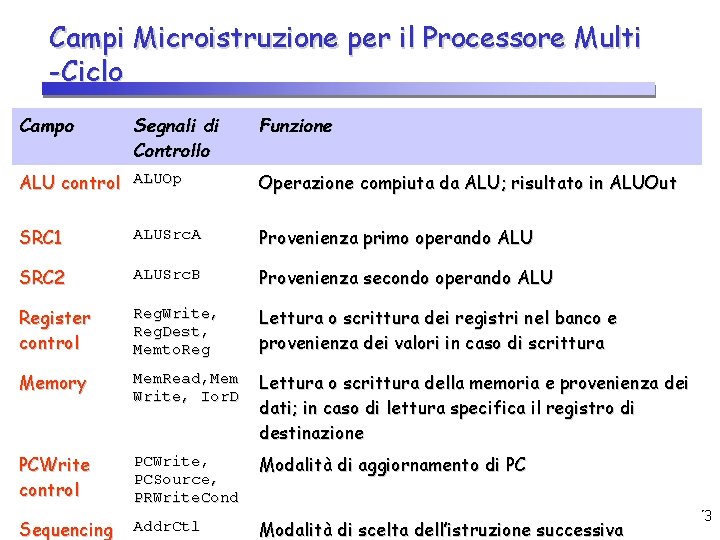

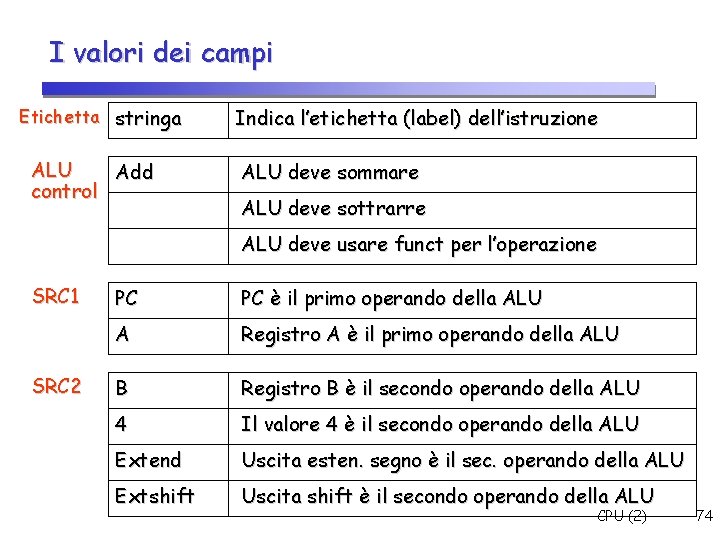

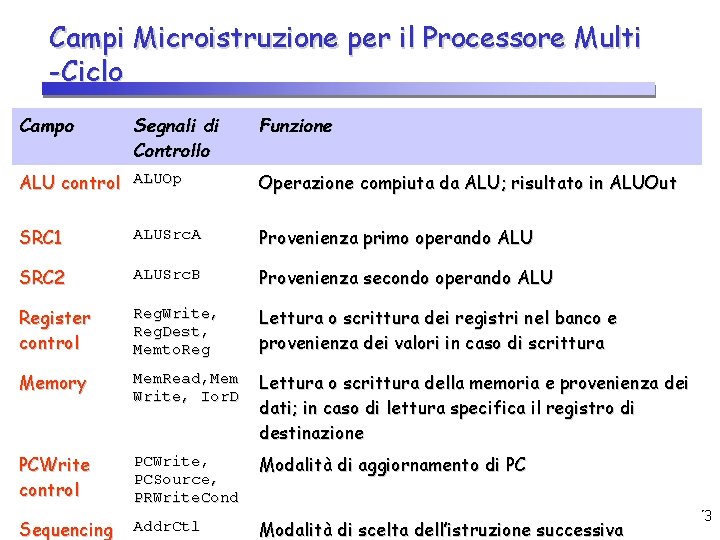

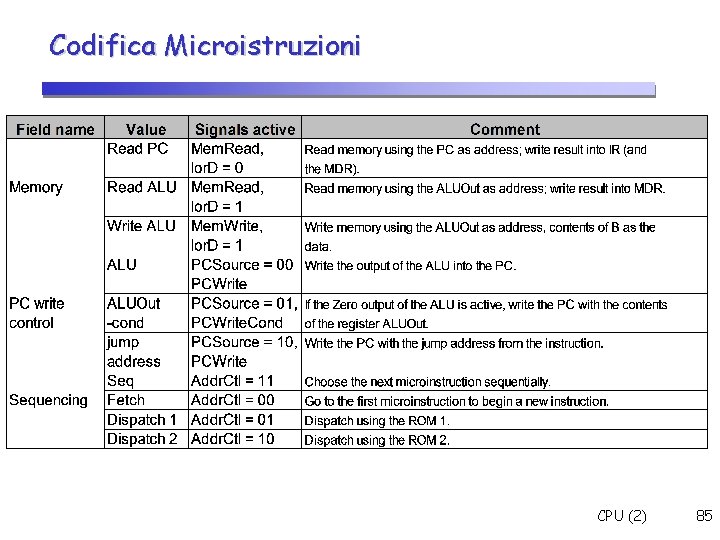

Campi Microistruzione per il Processore Multi -Ciclo Campo Segnali di Controllo Funzione ALU control ALUOp Operazione compiuta da ALU; risultato in ALUOut SRC 1 ALUSrc. A Provenienza primo operando ALU SRC 2 ALUSrc. B Provenienza secondo operando ALU Register control Reg. Write, Reg. Dest, Memto. Reg Lettura o scrittura dei registri nel banco e provenienza dei valori in caso di scrittura Memory Mem. Read, Mem Write, Ior. D Lettura o scrittura della memoria e provenienza dei dati; in caso di lettura specifica il registro di destinazione PCWrite control PCWrite, PCSource, PRWrite. Cond Modalità di aggiornamento di PC Sequencing Addr. Ctl Modalità di scelta dell’istruzione successiva CPU (2) 73

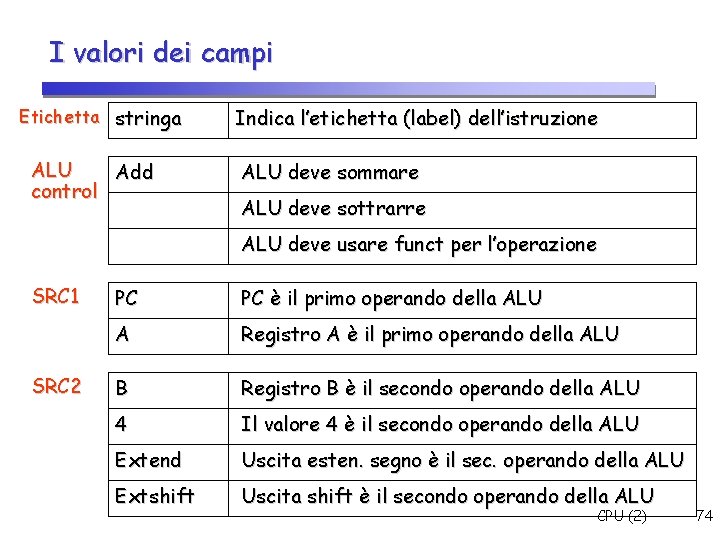

I valori dei campi Etichetta stringa ALU Add control Indica l’etichetta (label) dell’istruzione ALU deve sommare ALU deve sottrarre ALU deve usare funct per l’operazione SRC 1 SRC 2 PC PC è il primo operando della ALU A Registro A è il primo operando della ALU B Registro B è il secondo operando della ALU 4 Il valore 4 è il secondo operando della ALU Extend Uscita esten. segno è il sec. operando della ALU Extshift Uscita shift è il secondo operando della ALU CPU (2) 74

I valori dei campi (2) Register control Memory PCWrite control Read Legge i due registri usando IR, output in A e B Write ALU Scrive usando rd come registro e ALUOut come dato Write MDR Scrive usando rt come registro e MDR come dato Read PC Legge la memoria usando PC, risultato in IR e MDR Read ALU Legge la memoria usando ALUOut, risultato in MDR Write ALU Scrive la memoria usando ALUOut e B ALU Scrive uscita della ALU in PC ALUout-cond Se Zero vale 1, scrive in PC il valore di ALUOut Jump address Scrive in PC l’indirizzo di salto preso dall’istruzione Sequencing Seq Vai alla microistruzione successiva Fetch Vai alla prima microistruzione Dispatch i Usa la tabella di Dispatch per indicare la prossima CPU (2) istr. 75

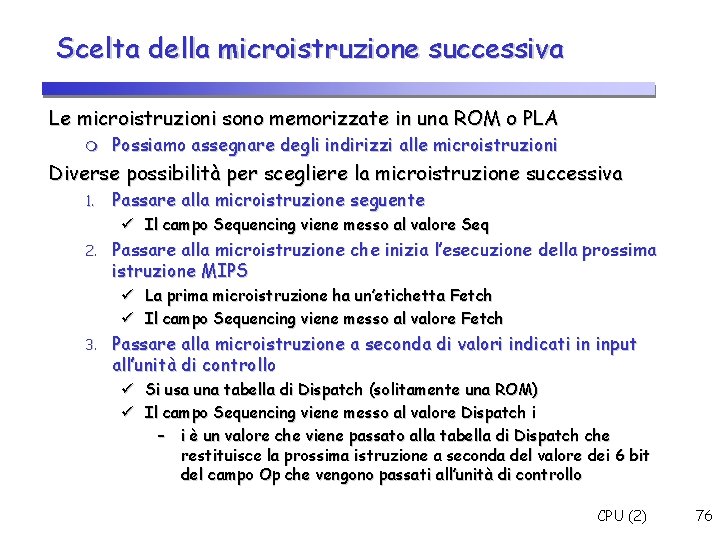

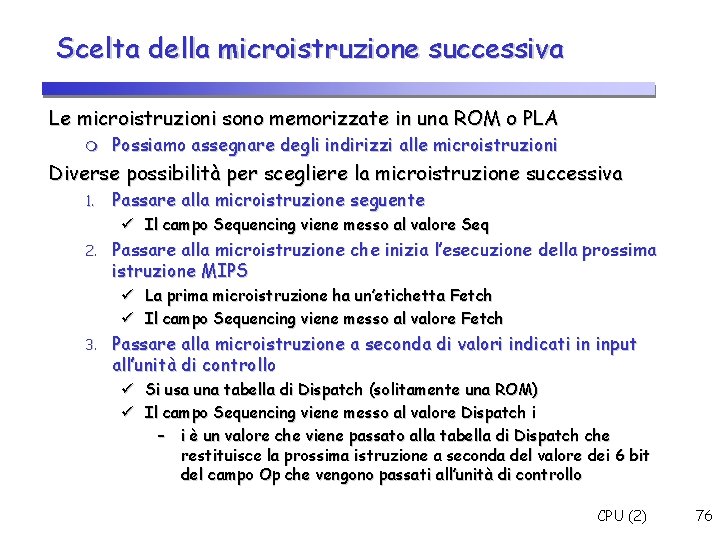

Scelta della microistruzione successiva Le microistruzioni sono memorizzate in una ROM o PLA Possiamo assegnare degli indirizzi alle microistruzioni Diverse possibilità per scegliere la microistruzione successiva 1. Passare alla microistruzione seguente Il campo Sequencing viene messo al valore Seq 2. Passare alla microistruzione che inizia l’esecuzione della prossima istruzione MIPS La prima microistruzione ha un’etichetta Fetch Il campo Sequencing viene messo al valore Fetch 3. Passare alla microistruzione a seconda di valori indicati in input all’unità di controllo Si usa una tabella di Dispatch (solitamente una ROM) Il campo Sequencing viene messo al valore Dispatch i – i è un valore che viene passato alla tabella di Dispatch che restituisce la prossima istruzione a seconda del valore dei 6 bit del campo Op che vengono passati all’unità di controllo CPU (2) 76

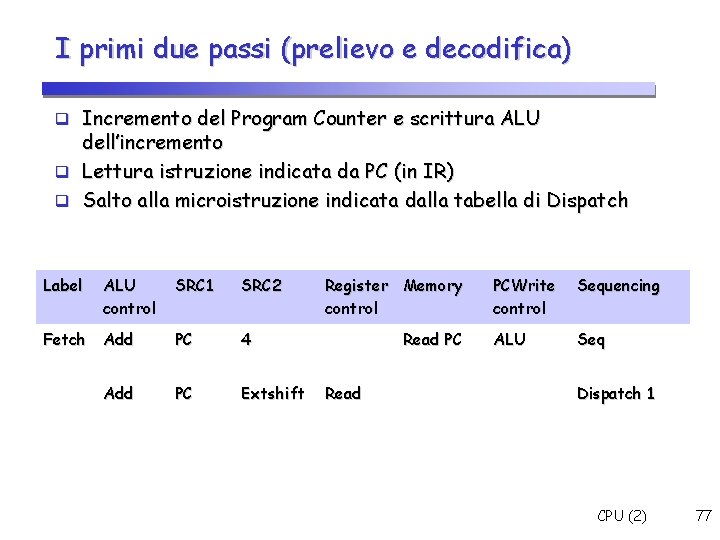

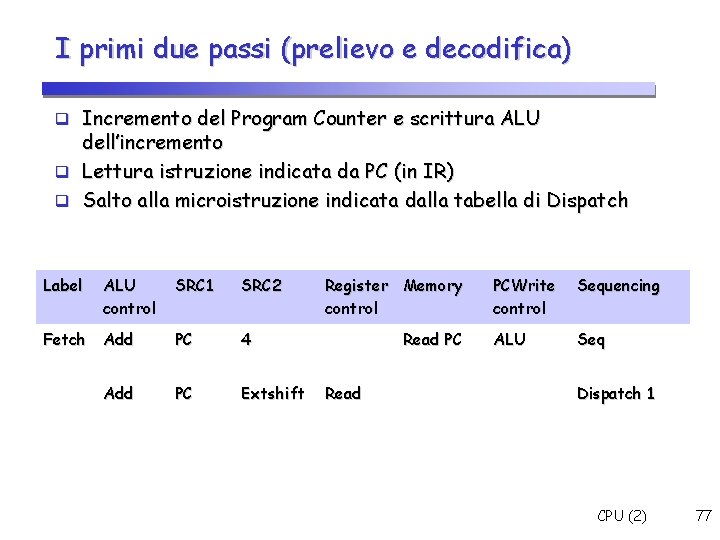

I primi due passi (prelievo e decodifica) Incremento del Program Counter e scrittura ALU dell’incremento Lettura istruzione indicata da PC (in IR) Salto alla microistruzione indicata dalla tabella di Dispatch Label ALU control SRC 1 SRC 2 Fetch Add PC 4 Add PC Extshift Register Memory control Read PCWrite control Sequencing ALU Seq Dispatch 1 CPU (2) 77

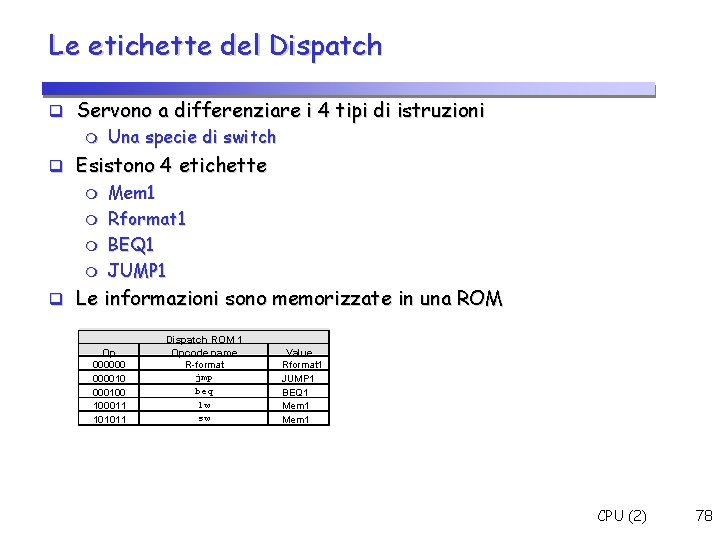

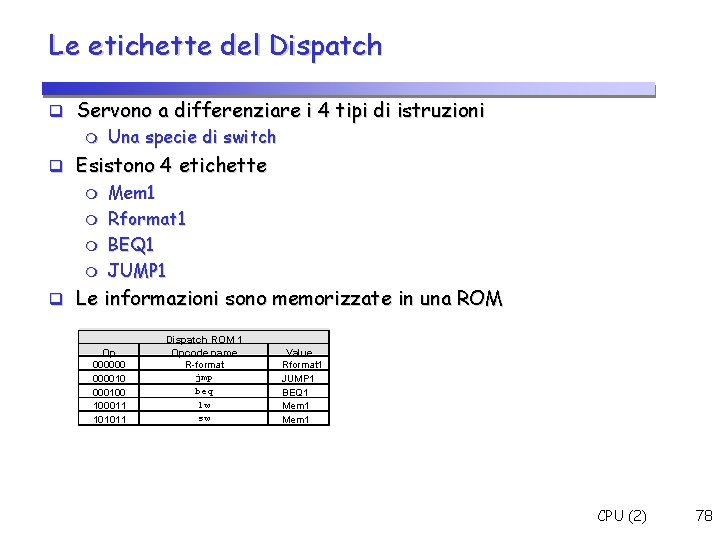

Le etichette del Dispatch Servono a differenziare i 4 tipi di istruzioni Una specie di switch Esistono 4 etichette Mem 1 Rformat 1 BEQ 1 JUMP 1 Le informazioni sono memorizzate in una ROM Op 00000010 000100 100011 101011 Dispatch ROM 1 Opcode name R-format jmp beq lw sw Value Rformat 1 JUMP 1 BEQ 1 Mem 1 CPU (2) 78

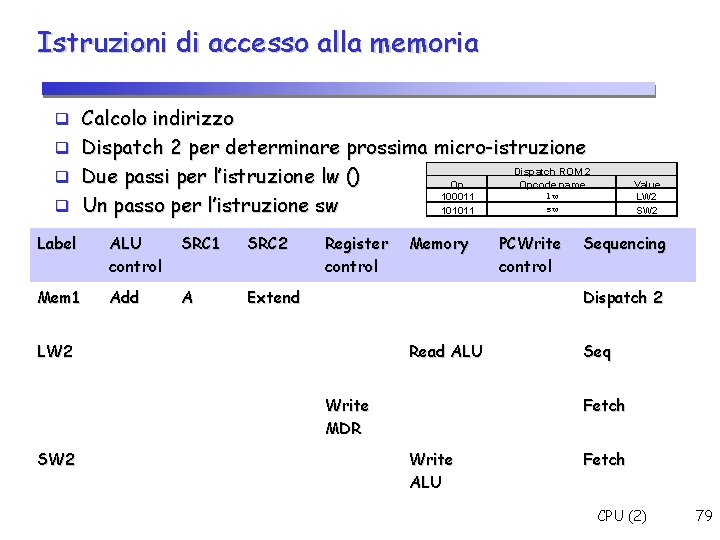

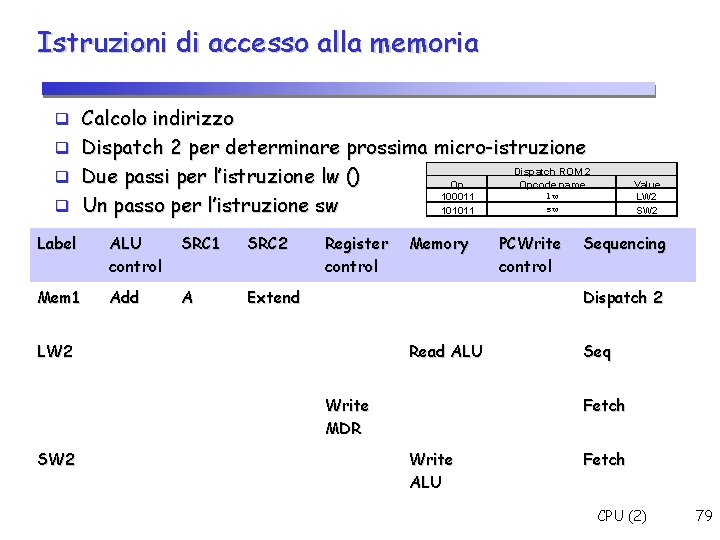

Istruzioni di accesso alla memoria Calcolo indirizzo Dispatch 2 per determinare prossima micro-istruzione Due passi per l’istruzione lw () Un passo per l’istruzione sw Label ALU control SRC 1 SRC 2 Mem 1 Add A Extend Register control Op 100011 101011 Memory PCWrite control Value LW 2 Sequencing Dispatch 2 LW 2 Read ALU Write MDR SW 2 Dispatch ROM 2 Opcode name lw sw Seq Fetch Write ALU Fetch CPU (2) 79

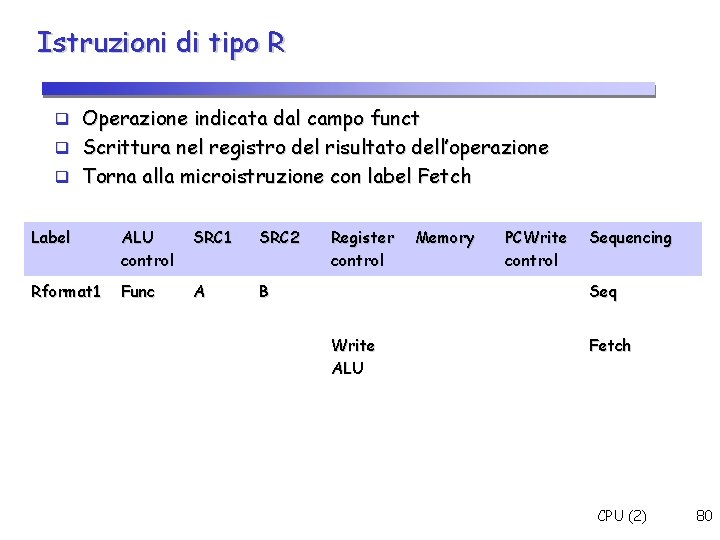

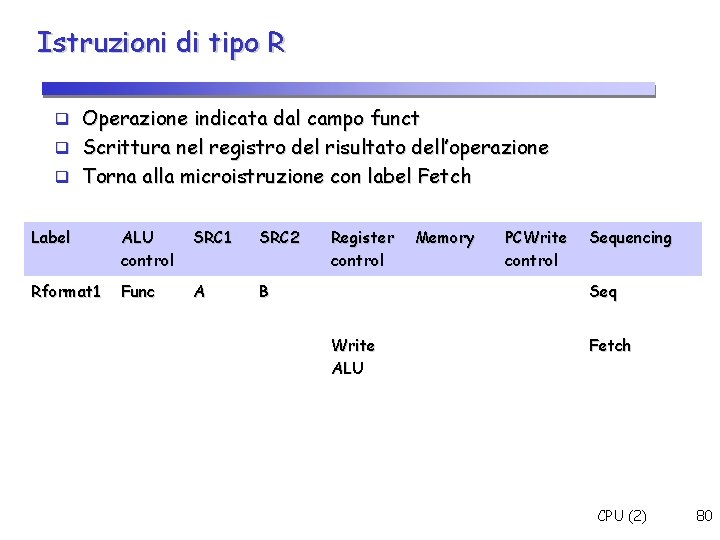

Istruzioni di tipo R Operazione indicata dal campo funct Scrittura nel registro del risultato dell’operazione Torna alla microistruzione con label Fetch Label ALU control SRC 1 SRC 2 Rformat 1 Func A B Register control Memory PCWrite control Sequencing Seq Write ALU Fetch CPU (2) 80

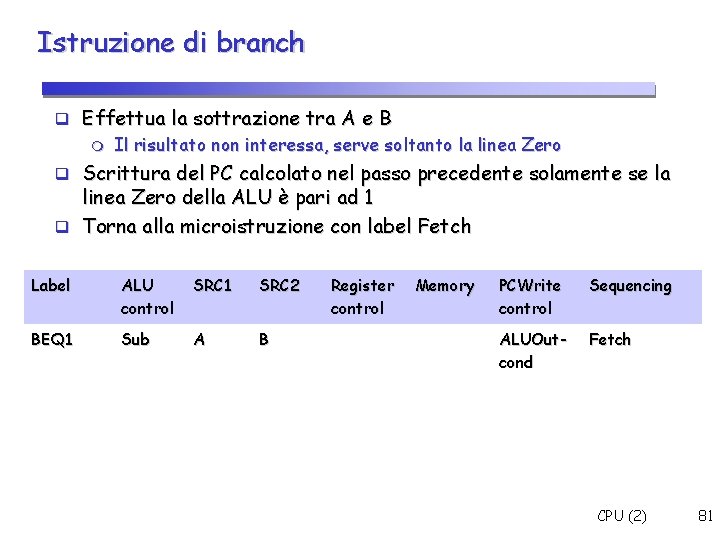

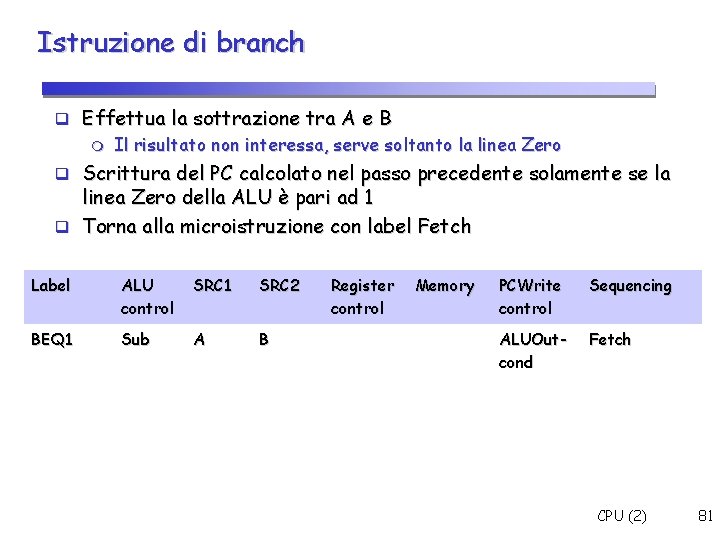

Istruzione di branch Effettua la sottrazione tra A e B Il risultato non interessa, serve soltanto la linea Zero Scrittura del PC calcolato nel passo precedente solamente se la linea Zero della ALU è pari ad 1 Torna alla microistruzione con label Fetch Label ALU control SRC 1 SRC 2 BEQ 1 Sub A B Register control Memory PCWrite control Sequencing ALUOutcond Fetch CPU (2) 81

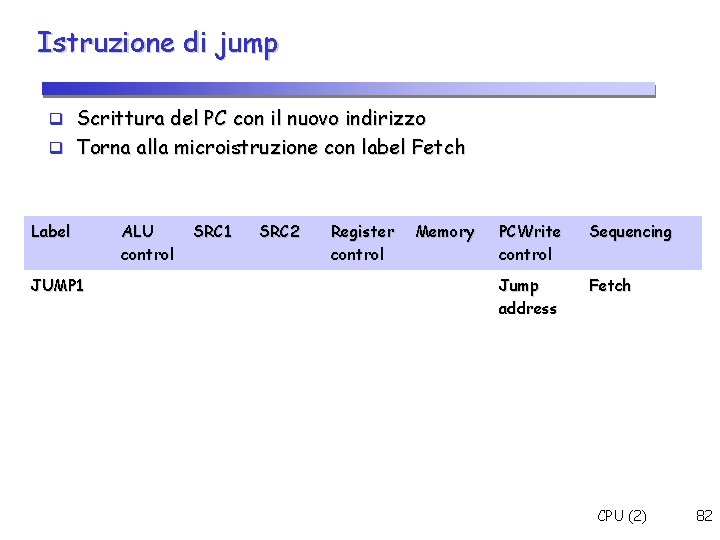

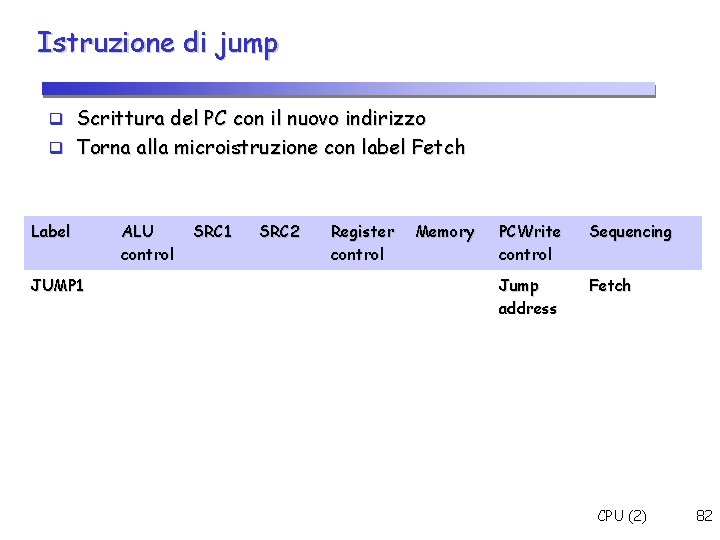

Istruzione di jump Scrittura del PC con il nuovo indirizzo Torna alla microistruzione con label Fetch Label JUMP 1 ALU control SRC 1 SRC 2 Register control Memory PCWrite control Sequencing Jump address Fetch CPU (2) 82

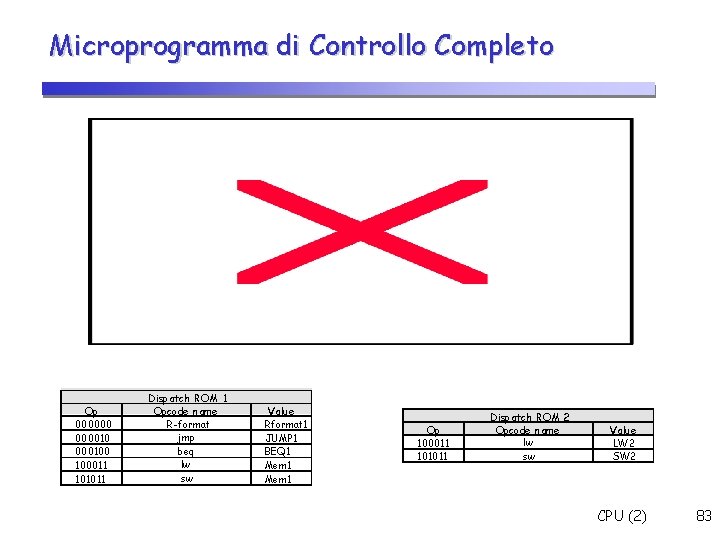

Microprogramma di Controllo Completo Op 00000010 000100 100011 101011 Dispatch ROM 1 Opcode name R-format jmp beq lw sw Value Rformat 1 JUMP 1 BEQ 1 Mem 1 Op 100011 101011 Dispatch ROM 2 Opcode name lw sw Value LW 2 SW 2 CPU (2) 83

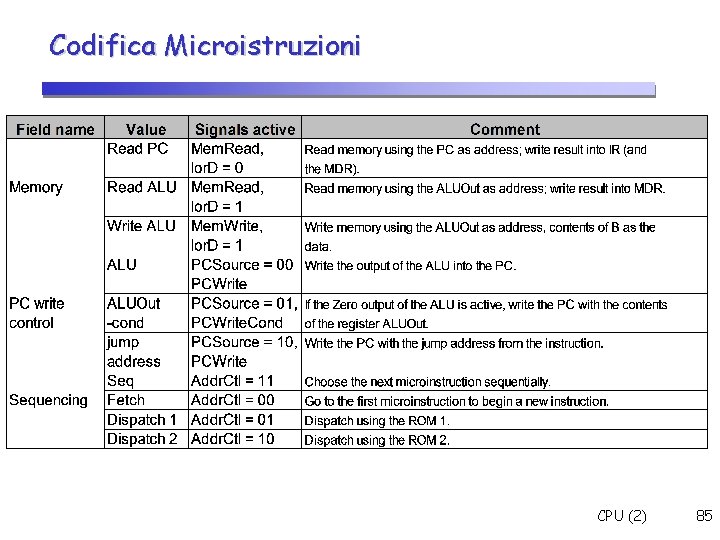

Codifica Microistruzioni CPU (2) 84

Codifica Microistruzioni CPU (2) 85

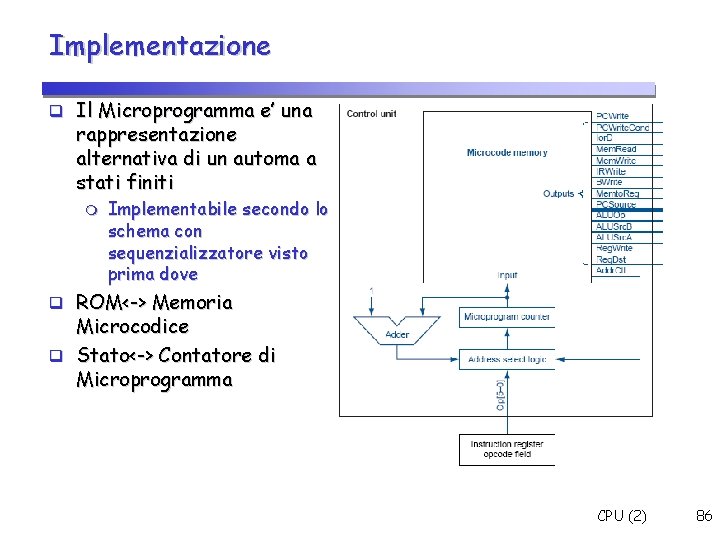

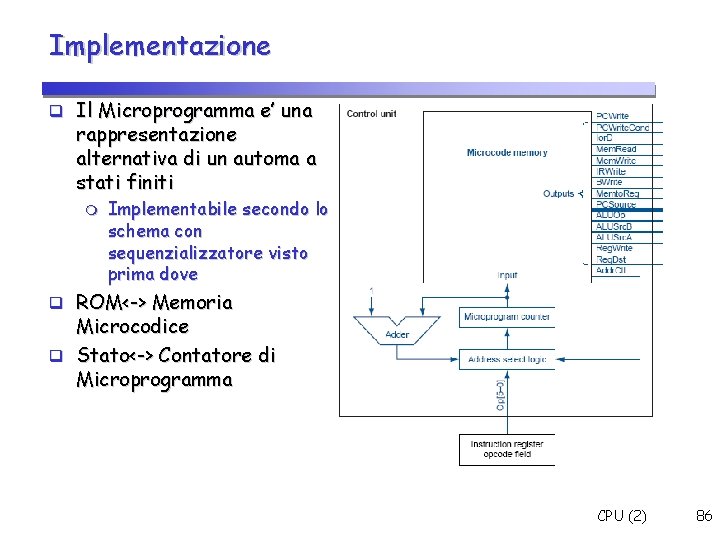

Implementazione Il Microprogramma e’ una rappresentazione alternativa di un automa a stati finiti Implementabile secondo lo schema con sequenzializzatore visto prima dove ROM<-> Memoria Microcodice Stato<-> Contatore di Microprogramma CPU (2) 86

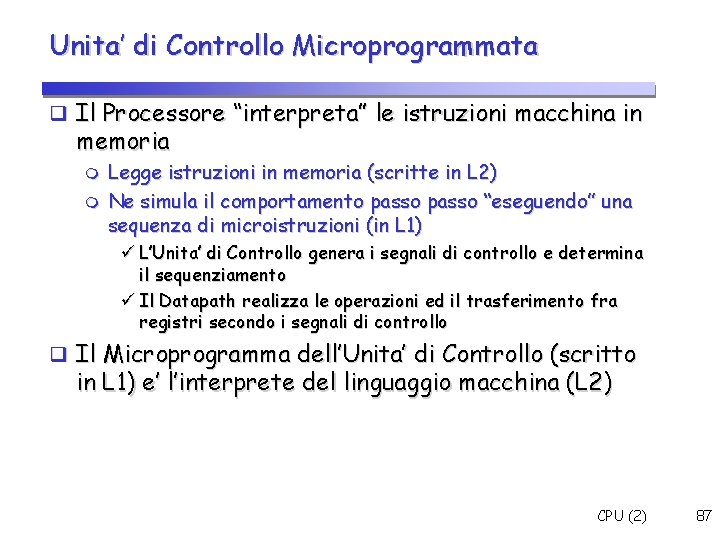

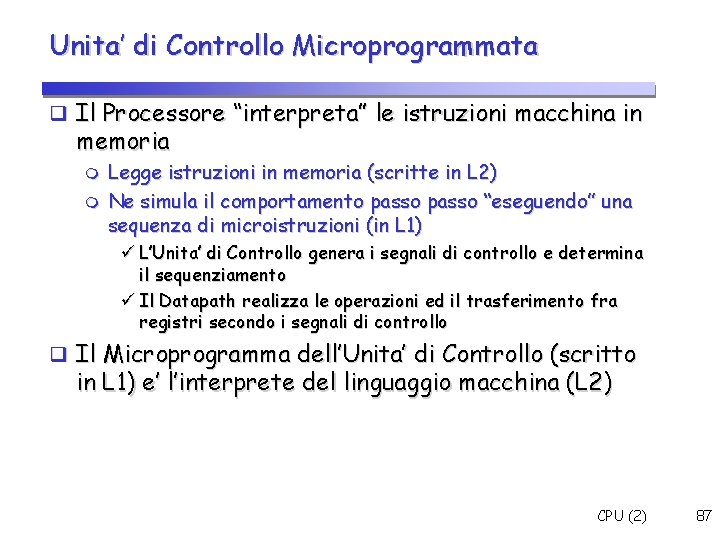

Unita’ di Controllo Microprogrammata Il Processore “interpreta” le istruzioni macchina in memoria Legge istruzioni in memoria (scritte in L 2) Ne simula il comportamento passo “eseguendo” una sequenza di microistruzioni (in L 1) L’Unita’ di Controllo genera i segnali di controllo e determina il sequenziamento Il Datapath realizza le operazioni ed il trasferimento fra registri secondo i segnali di controllo Il Microprogramma dell’Unita’ di Controllo (scritto in L 1) e’ l’interprete del linguaggio macchina (L 2) CPU (2) 87

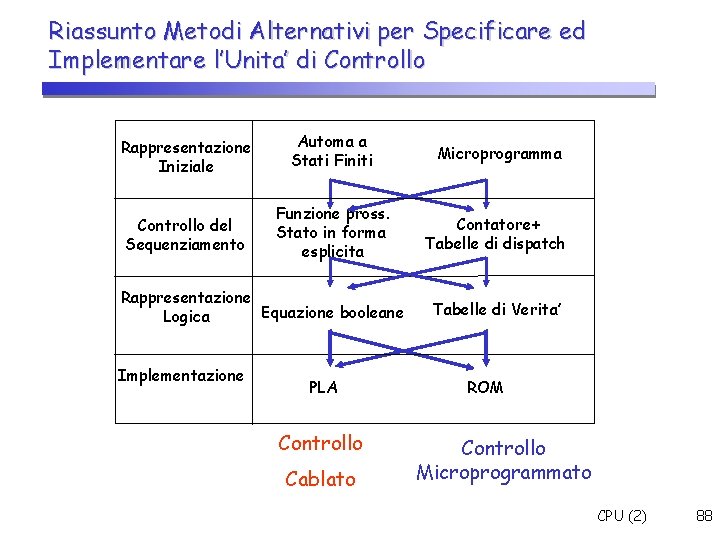

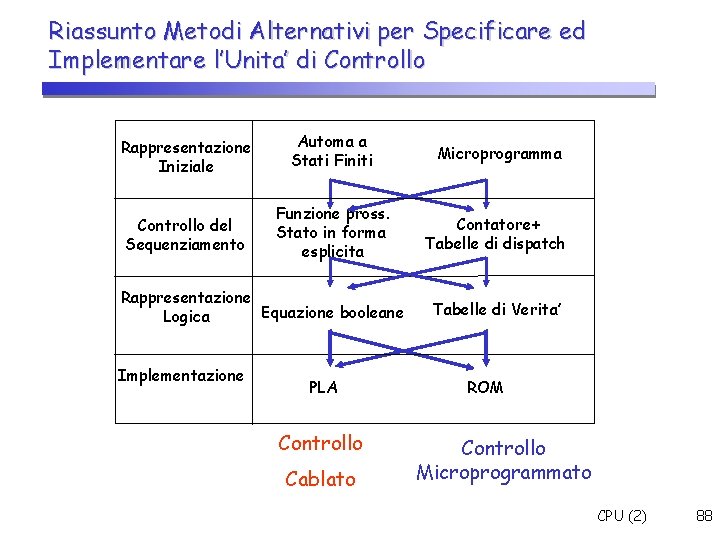

Riassunto Metodi Alternativi per Specificare ed Implementare l’Unita’ di Controllo Rappresentazione Iniziale Automa a Stati Finiti Microprogramma Controllo del Sequenziamento Funzione pross. Stato in forma esplicita Contatore+ Tabelle di dispatch Rappresentazione Equazione booleane Logica Implementazione PLA Controllo Cablato Tabelle di Verita’ ROM Controllo Microprogrammato CPU (2) 88

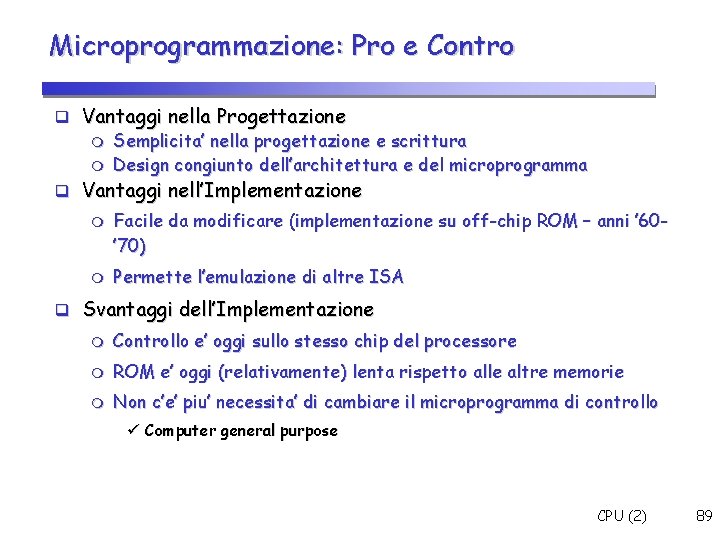

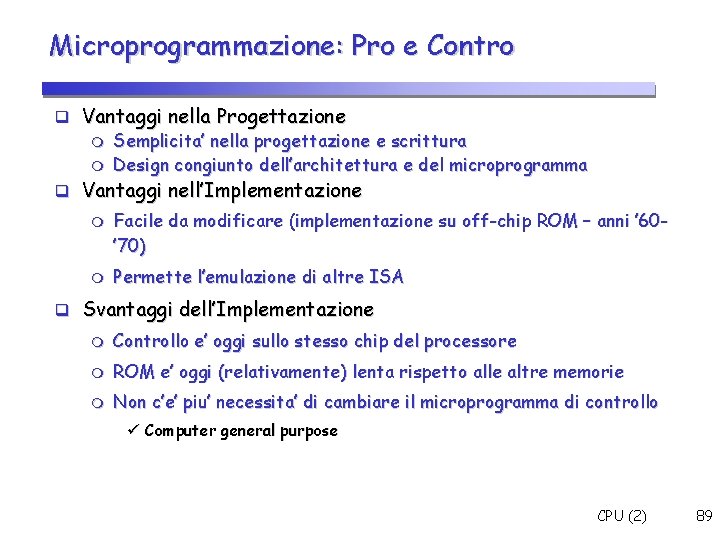

Microprogrammazione: Pro e Contro Vantaggi nella Progettazione Semplicita’ nella progettazione e scrittura Design congiunto dell’architettura e del microprogramma Vantaggi nell’Implementazione Facile da modificare (implementazione su off-chip ROM – anni ’ 60’ 70) Permette l’emulazione di altre ISA Svantaggi dell’Implementazione Controllo e’ oggi sullo stesso chip del processore ROM e’ oggi (relativamente) lenta rispetto alle altre memorie Non c’e’ piu’ necessita’ di cambiare il microprogramma di controllo Computer general purpose CPU (2) 89

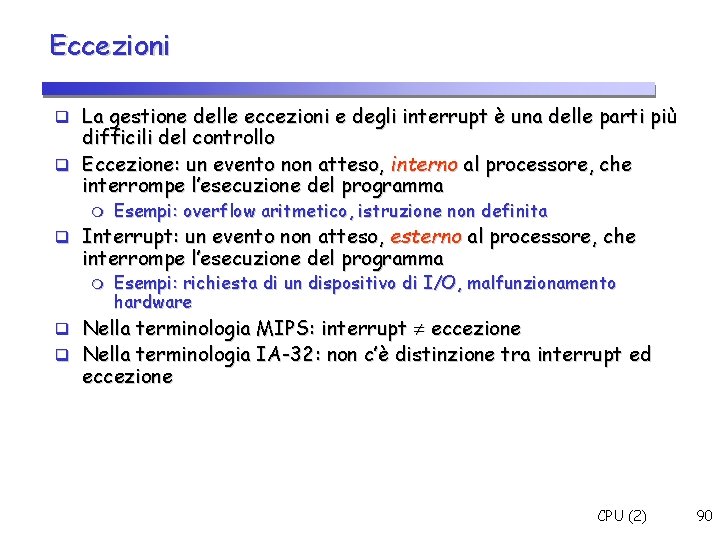

Eccezioni La gestione delle eccezioni e degli interrupt è una delle parti più difficili del controllo Eccezione: un evento non atteso, interno al processore, che interrompe l’esecuzione del programma Esempi: overflow aritmetico, istruzione non definita Interrupt: un evento non atteso, esterno al processore, che interrompe l’esecuzione del programma Esempi: richiesta di un dispositivo di I/O, malfunzionamento hardware Nella terminologia MIPS: interrupt eccezione Nella terminologia IA-32: non c’è distinzione tra interrupt ed eccezione CPU (2) 90

Gestione delle eccezioni Quando avviene un’eccezione occorre Salvare nel registro EPC (Exception Program Counter) l’indirizzo dell’istruzione che ha causato l’eccezione Trasferire il controllo al sistema operativo a qualche indirizzo specifico per la gestione dell’eccezione Il sistema operativo, dopo aver eseguito le azioni necessarie, può terminare il programma o continuarne l’esecuzione usando EPC per determinare da dove riprendere l’esecuzione Oltre a EPC, il sistema operativo deve conoscere la ragione dell’eccezione; esistono due meccanismi Registro di stato (Cause register nel MIPS): contiene un campo che indica la causa dell’eccezione Interrupt vettorializzato: l’indirizzo a cui trasferire il controllo è determinato dalla causa dell’eccezione Consideriamo due tipi di eccezioni nell’implementazione a ciclo multiplo Esecuzione di un’istruzione non definita Overflow aritmetico CPU (2) 91

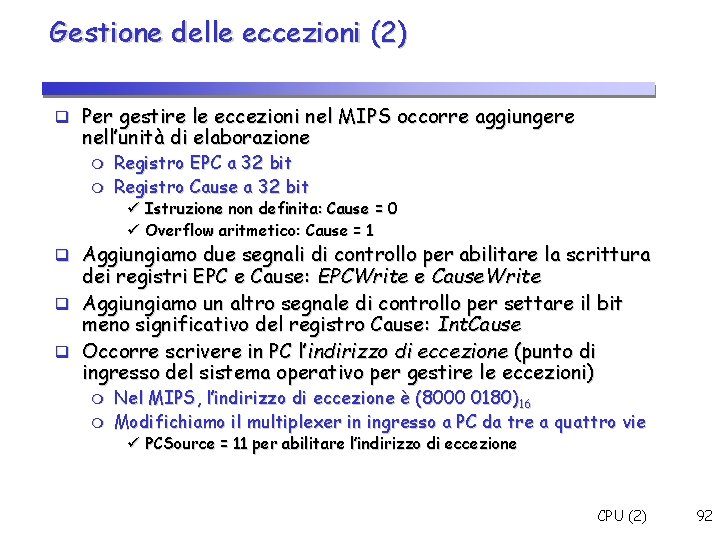

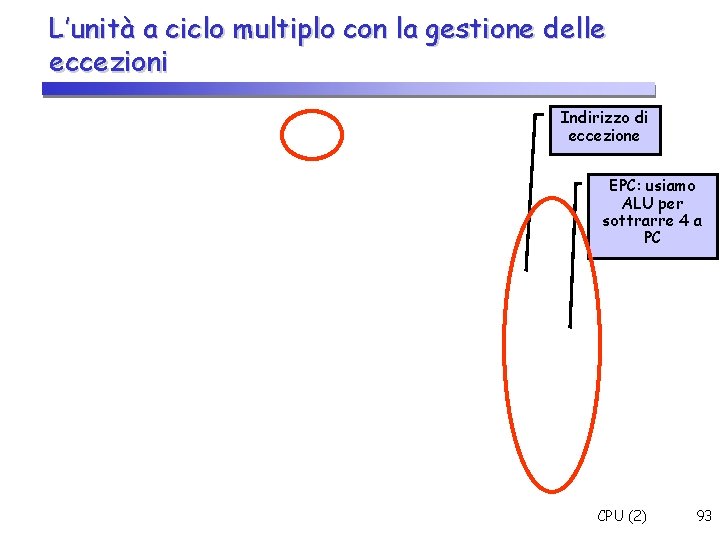

Gestione delle eccezioni (2) Per gestire le eccezioni nel MIPS occorre aggiungere nell’unità di elaborazione Registro EPC a 32 bit Registro Cause a 32 bit Istruzione non definita: Cause = 0 Overflow aritmetico: Cause = 1 Aggiungiamo due segnali di controllo per abilitare la scrittura dei registri EPC e Cause: EPCWrite e Cause. Write Aggiungiamo un altro segnale di controllo per settare il bit meno significativo del registro Cause: Int. Cause Occorre scrivere in PC l’indirizzo di eccezione (punto di ingresso del sistema operativo per gestire le eccezioni) Nel MIPS, l’indirizzo di eccezione è (8000 0180)16 Modifichiamo il multiplexer in ingresso a PC da tre a quattro vie PCSource = 11 per abilitare l’indirizzo di eccezione CPU (2) 92

L’unità a ciclo multiplo con la gestione delle eccezioni Indirizzo di eccezione EPC: usiamo ALU per sottrarre 4 a PC CPU (2) 93

La macchina a stati finiti con la gestione delle eccezioni CPU (2) 94