Calcolatori Elettronici Cenni sulle memorie Francesco Lo Presti

- Slides: 21

Calcolatori Elettronici Cenni sulle memorie Francesco Lo Presti Rielaborate da Salvatore Tucci

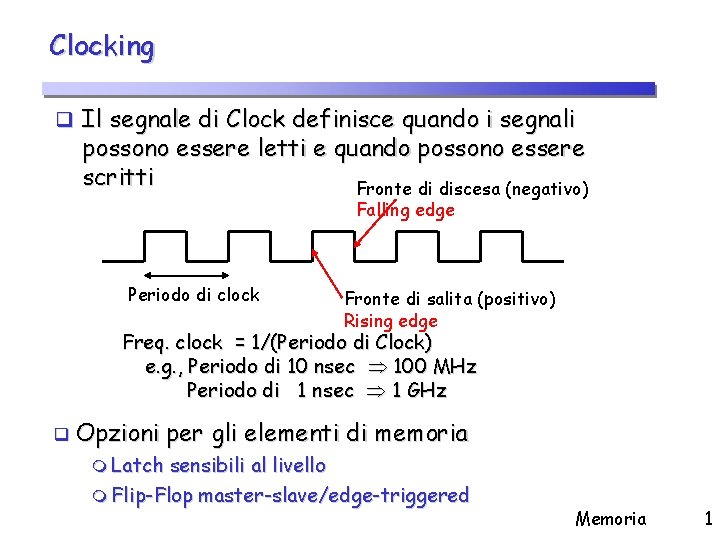

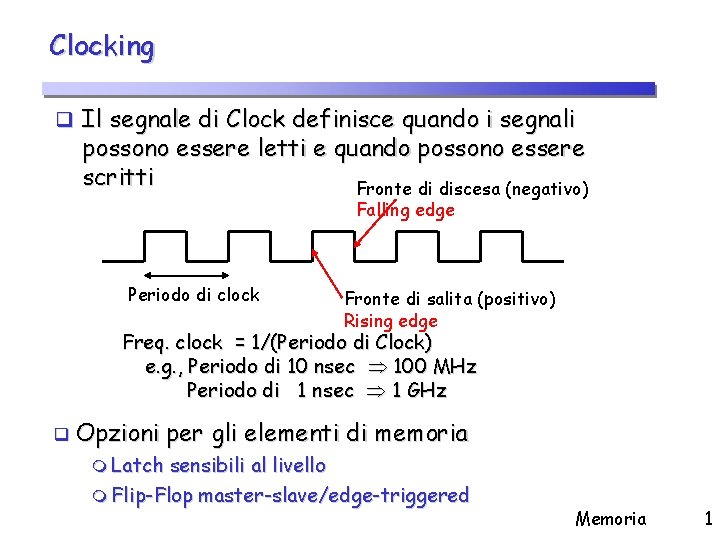

Clocking q Il segnale di Clock definisce quando i segnali possono essere letti e quando possono essere scritti Fronte di discesa (negativo) Falling edge Periodo di clock Fronte di salita (positivo) Rising edge Freq. clock = 1/(Periodo di Clock) e. g. , Periodo di 10 nsec 100 MHz Periodo di 1 nsec 1 GHz q Opzioni per gli elementi di memoria m Latch sensibili al livello m Flip-Flop master-slave/edge-triggered Memoria 1

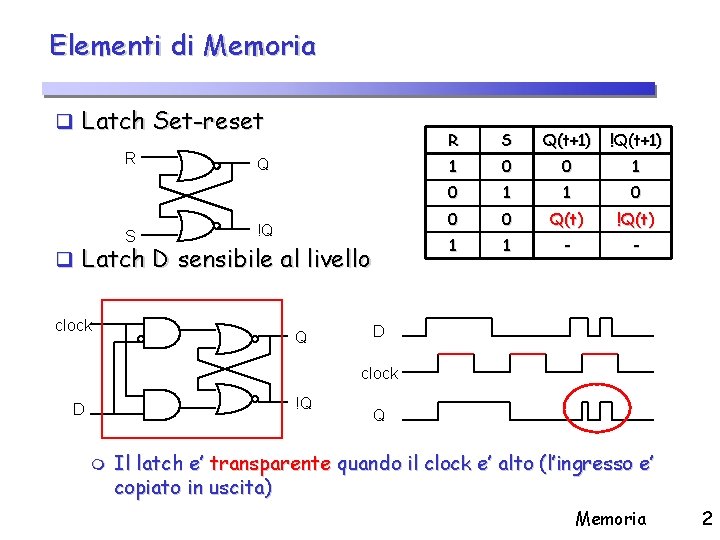

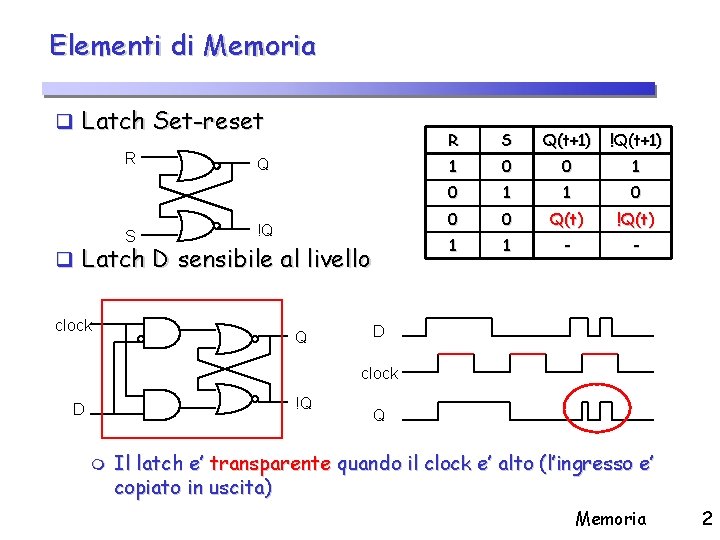

Elementi di Memoria q Latch Set-reset R S Q !Q q Latch D sensibile al livello clock Q R S Q(t+1) !Q(t+1) 1 0 0 1 1 0 0 0 Q(t) !Q(t) 1 1 - - D clock !Q D m Q Il latch e’ transparente quando il clock e’ alto (l’ingresso e’ copiato in uscita) Memoria 2

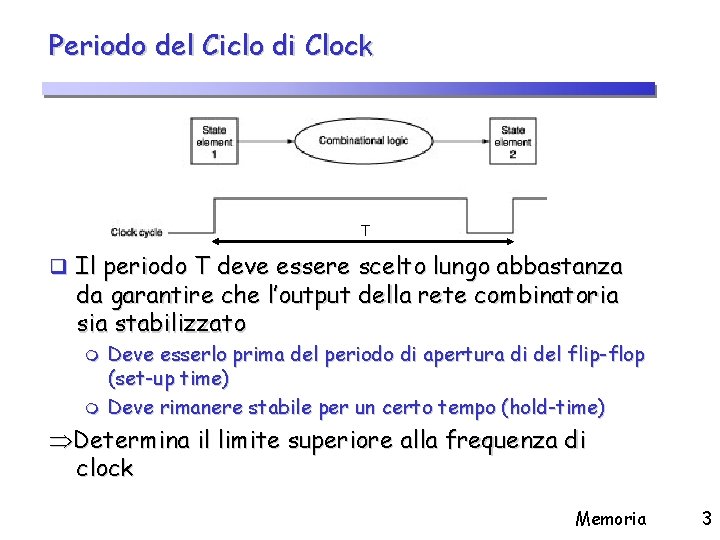

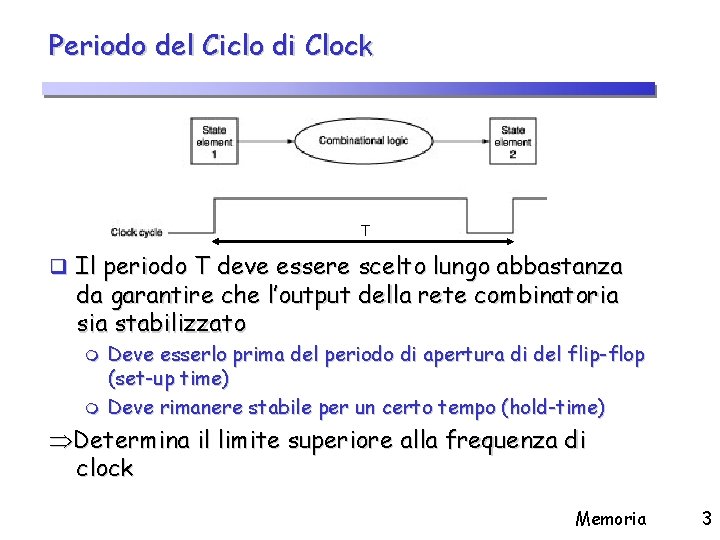

Periodo del Ciclo di Clock T q Il periodo T deve essere scelto lungo abbastanza da garantire che l’output della rete combinatoria stabilizzato m m Deve esserlo prima del periodo di apertura di del flip-flop (set-up time) Deve rimanere stabile per un certo tempo (hold-time) Determina il limite superiore alla frequenza di clock Memoria 3

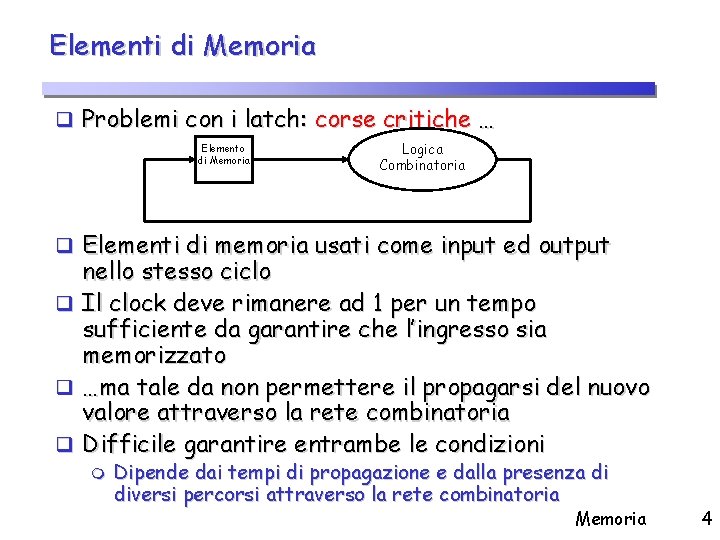

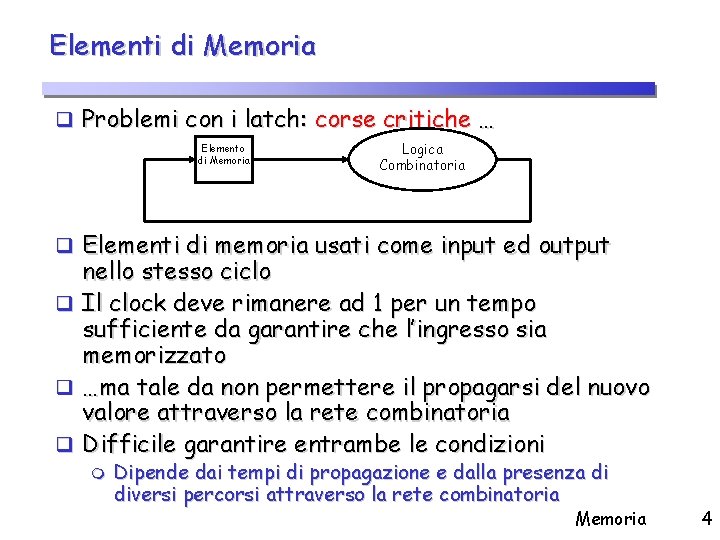

Elementi di Memoria q Problemi con i latch: corse critiche … Elemento di Memoria Logica Combinatoria q Elementi di memoria usati come input ed output nello stesso ciclo q Il clock deve rimanere ad 1 per un tempo sufficiente da garantire che l’ingresso sia memorizzato q …ma tale da non permettere il propagarsi del nuovo valore attraverso la rete combinatoria q Difficile garantire entrambe le condizioni m Dipende dai tempi di propagazione e dalla presenza di diversi percorsi attraverso la rete combinatoria Memoria 4

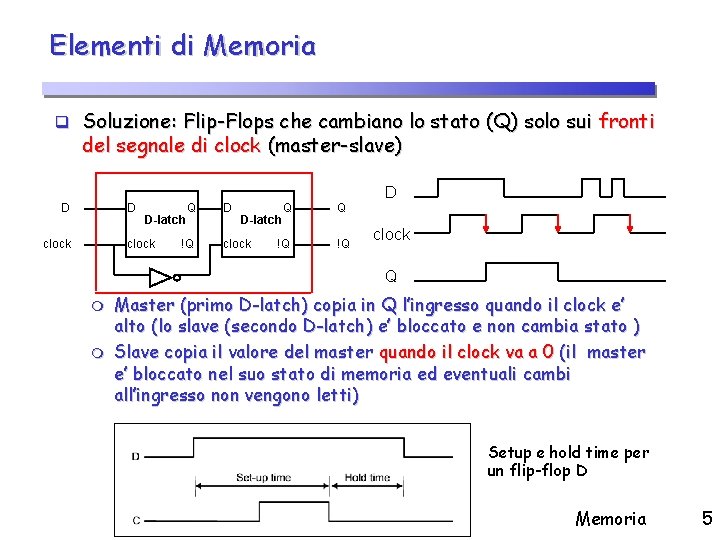

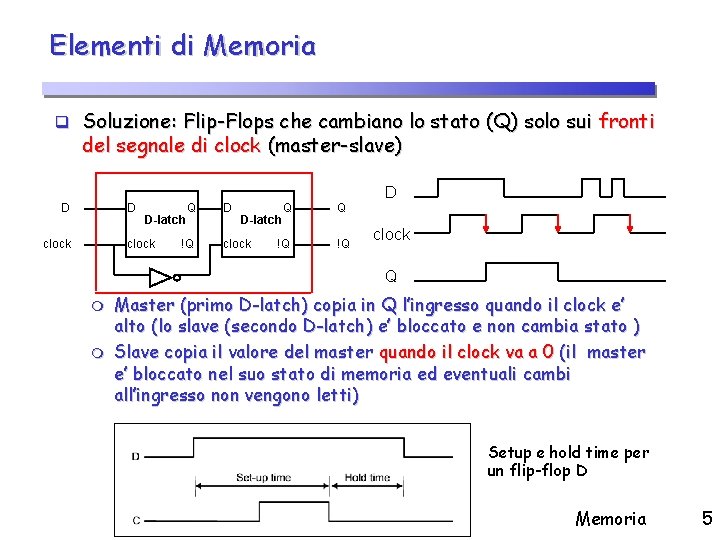

Elementi di Memoria q Soluzione: Flip-Flops che cambiano lo stato (Q) solo sui fronti del segnale di clock (master-slave) D D clock D-latch clock Q !Q D Q Q !Q !Q D-latch clock D clock Q m m Master (primo D-latch) copia in Q l’ingresso quando il clock e’ alto (lo slave (secondo D-latch) e’ bloccato e non cambia stato ) Slave copia il valore del master quando il clock va a 0 (il master e’ bloccato nel suo stato di memoria ed eventuali cambi all’ingresso non vengono letti) Setup e hold time per un flip-flop D Memoria 5

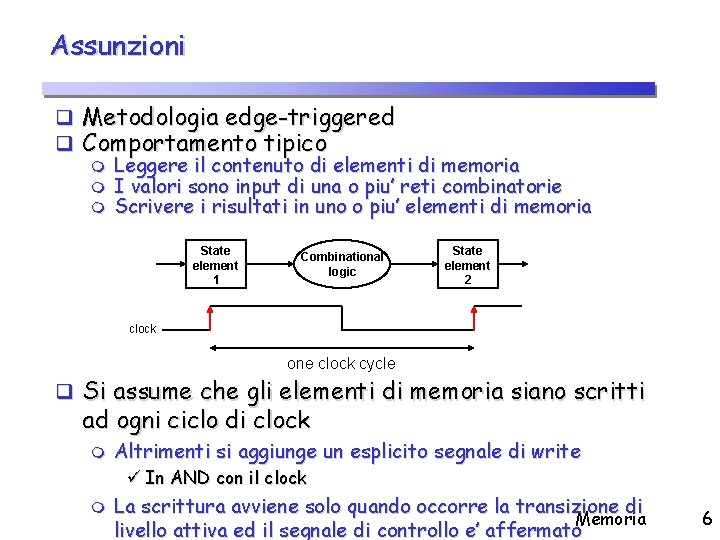

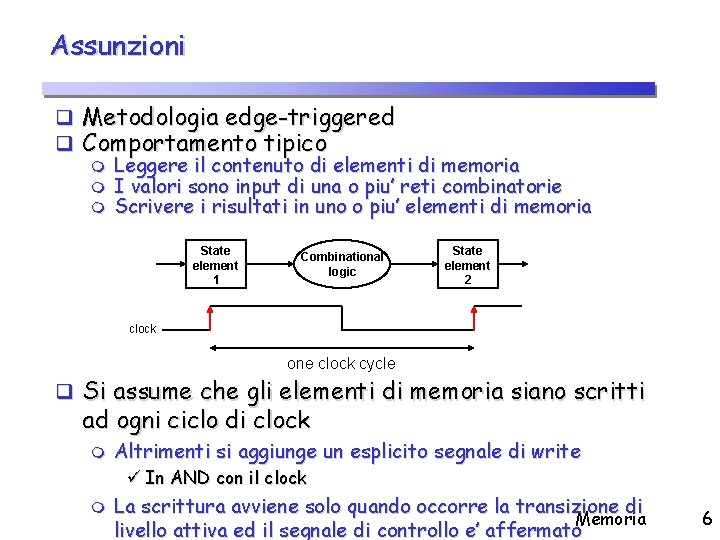

Assunzioni q Metodologia edge-triggered q Comportamento tipico m Leggere il contenuto di elementi di memoria m I valori sono input di una o piu’ reti combinatorie m Scrivere i risultati in uno o piu’ elementi di memoria State element 1 Combinational logic State element 2 clock one clock cycle q Si assume che gli elementi di memoria siano scritti ad ogni ciclo di clock m Altrimenti si aggiunge un esplicito segnale di write ü In AND con il clock m La scrittura avviene solo quando occorre la transizione di Memoria livello attiva ed il segnale di controllo e’ affermato 6

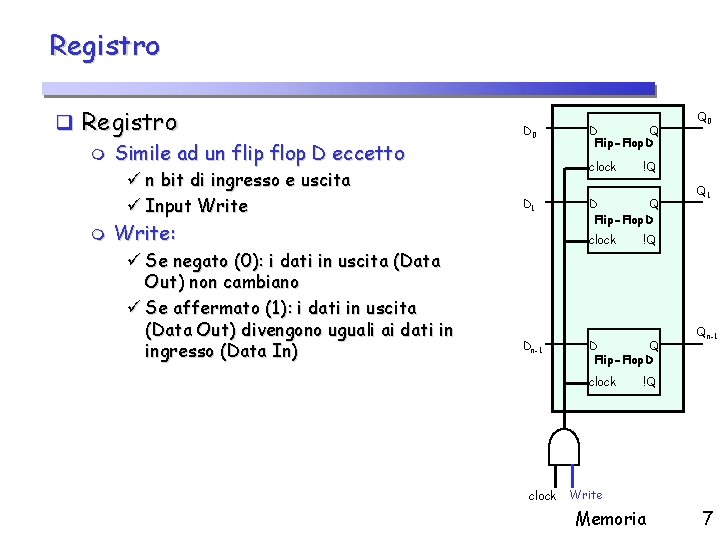

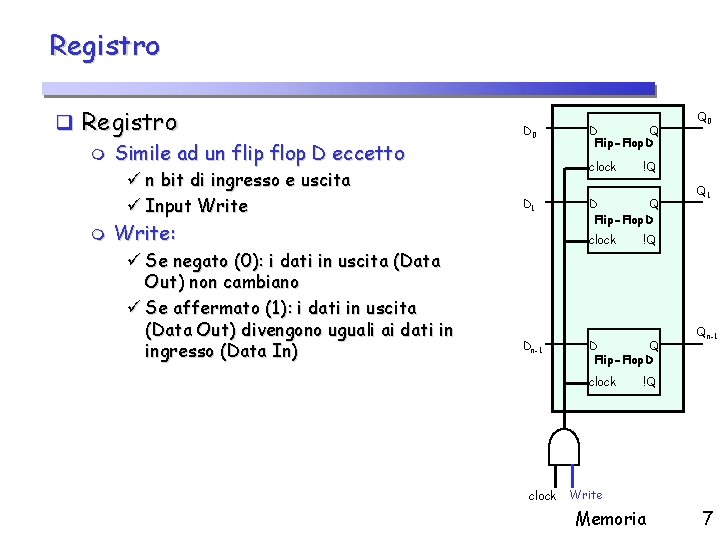

Registro q Registro m Simile ad un flip flop D eccetto ü n bit di ingresso e uscita ü Input Write m D 0 clock D 1 Write: ü Se negato (0): i dati in uscita (Data Out) non cambiano ü Se affermato (1): i dati in uscita (Data Out) divengono uguali ai dati in ingresso (Data In) D Q Flip-Flop. D Dn-1 Q 1 !Q D Q Flip-Flop. D clock Q 0 Qn-1 !Q Write Memoria 7

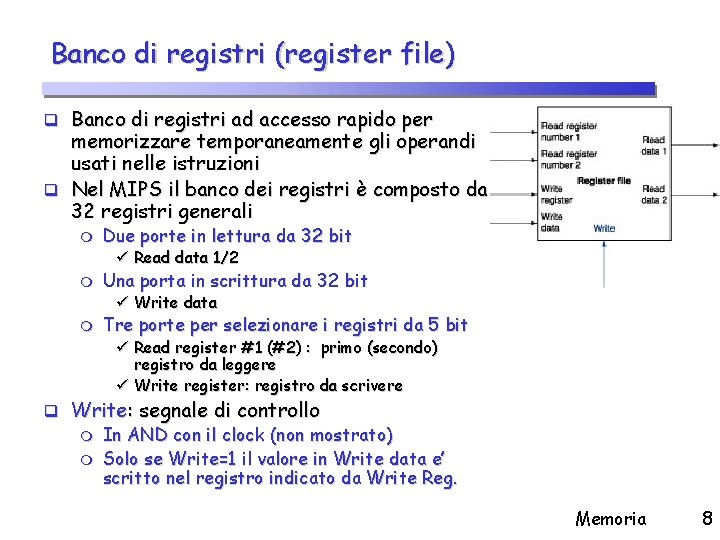

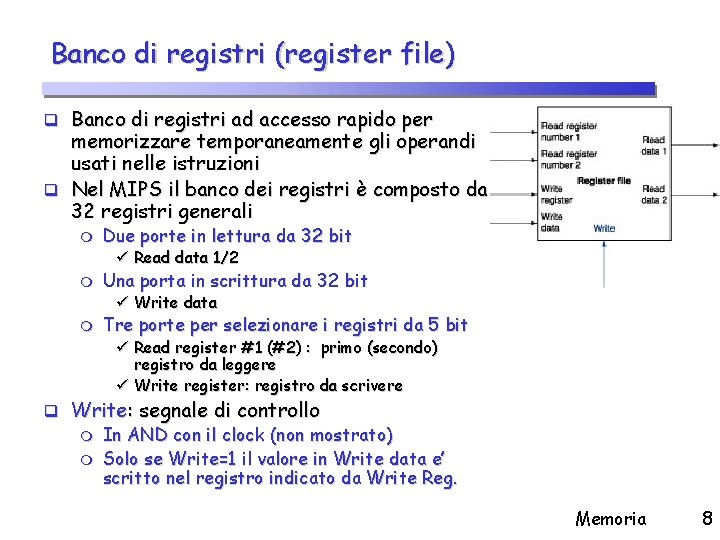

Banco di registri (register file) q Banco di registri ad accesso rapido per memorizzare temporaneamente gli operandi usati nelle istruzioni q Nel MIPS il banco dei registri è composto da 32 registri generali m Due porte in lettura da 32 bit ü Read data 1/2 m Una porta in scrittura da 32 bit ü Write data m Tre porte per selezionare i registri da 5 bit ü Read register #1 (#2) : primo (secondo) registro da leggere ü Write register: registro da scrivere q Write: segnale di controllo m In AND con il clock (non mostrato) m Solo se Write=1 il valore in Write data e’ scritto nel registro indicato da Write Reg. Memoria 8

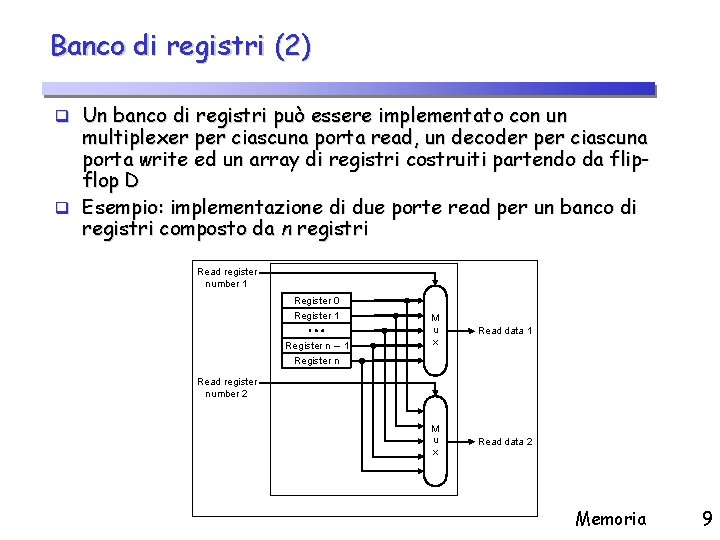

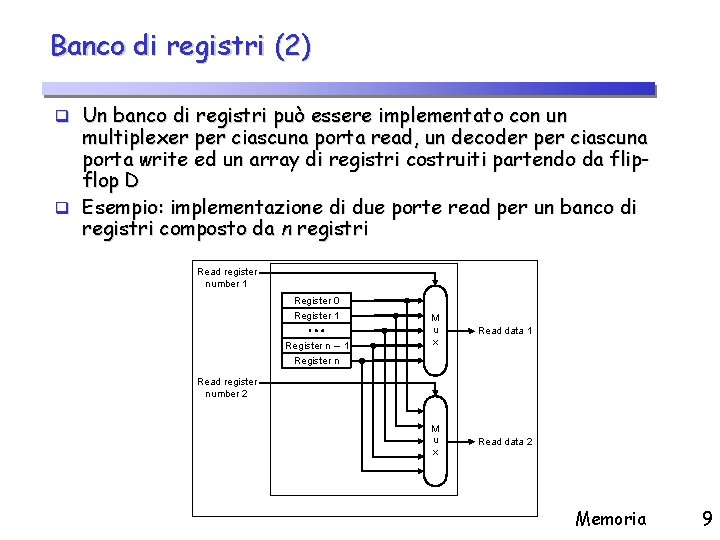

Banco di registri (2) q Un banco di registri può essere implementato con un multiplexer per ciascuna porta read, un decoder per ciascuna porta write ed un array di registri costruiti partendo da flipflop D q Esempio: implementazione di due porte read per un banco di registri composto da n registri Read register number 1 Register 0 Register 1 Register n – 1 Register n M u x Read data 1 M u x Read data 2 Read register number 2 Memoria 9

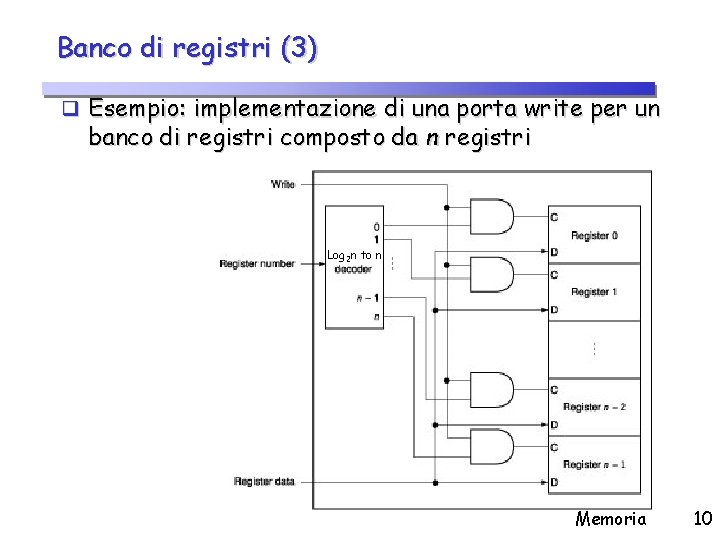

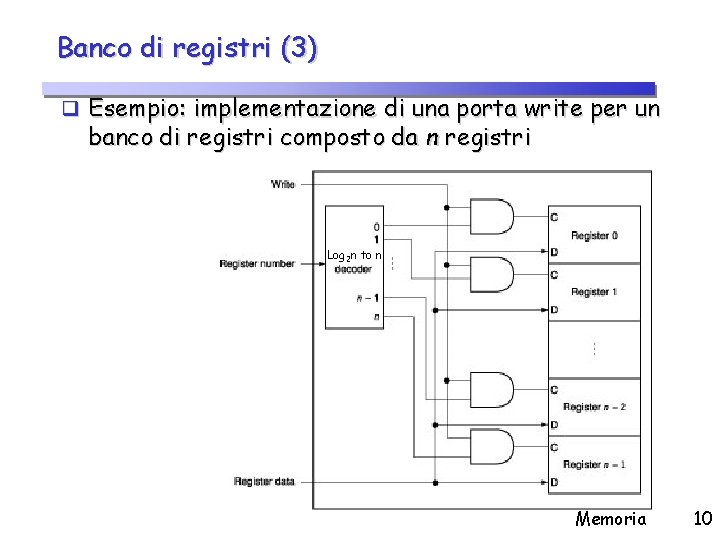

Banco di registri (3) q Esempio: implementazione di una porta write per un banco di registri composto da n registri Log 2 n to n Memoria 10

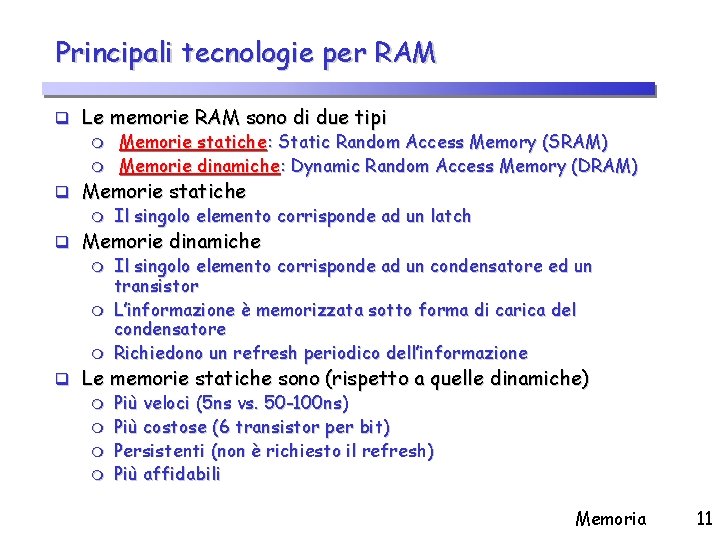

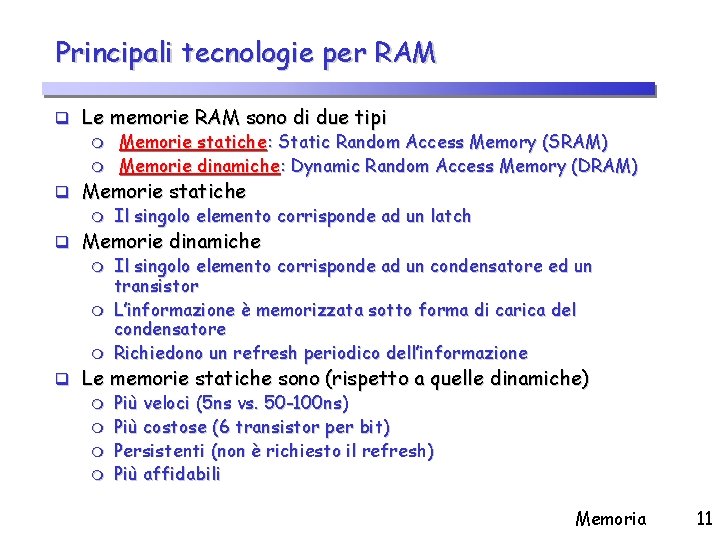

Principali tecnologie per RAM q Le memorie RAM sono di due tipi m Memorie statiche: Static Random Access Memory (SRAM) m Memorie dinamiche: Dynamic Random Access Memory (DRAM) q Memorie statiche m Il singolo elemento corrisponde ad un latch q Memorie dinamiche m Il singolo elemento corrisponde ad un condensatore ed un transistor m L’informazione è memorizzata sotto forma di carica del condensatore m Richiedono un refresh periodico dell’informazione q Le memorie statiche sono (rispetto a quelle dinamiche) m Più veloci (5 ns vs. 50 -100 ns) m Più costose (6 transistor per bit) m Persistenti (non è richiesto il refresh) m Più affidabili Memoria 11

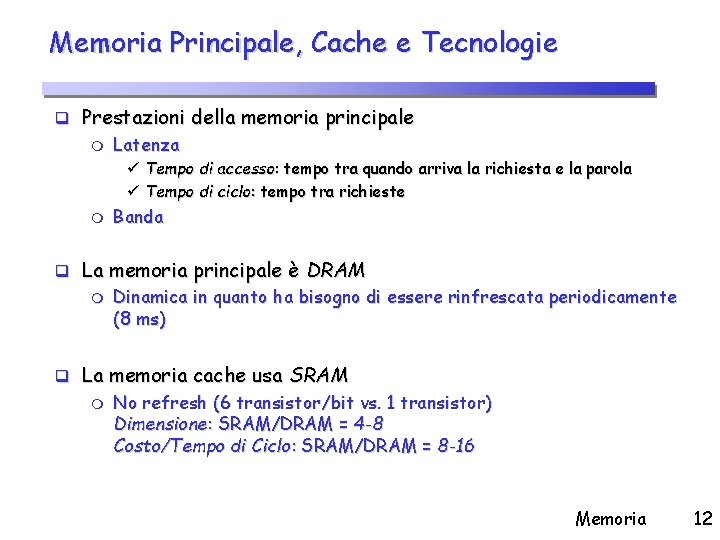

Memoria Principale, Cache e Tecnologie q Prestazioni della memoria principale m Latenza ü Tempo di accesso: tempo tra quando arriva la richiesta e la parola ü Tempo di ciclo: tempo tra richieste m Banda q La memoria principale è DRAM m Dinamica in quanto ha bisogno di essere rinfrescata periodicamente (8 ms) q La memoria cache usa SRAM m No refresh (6 transistor/bit vs. 1 transistor) Dimensione: SRAM/DRAM = 4 -8 Costo/Tempo di Ciclo: SRAM/DRAM = 8 -16 Memoria 12

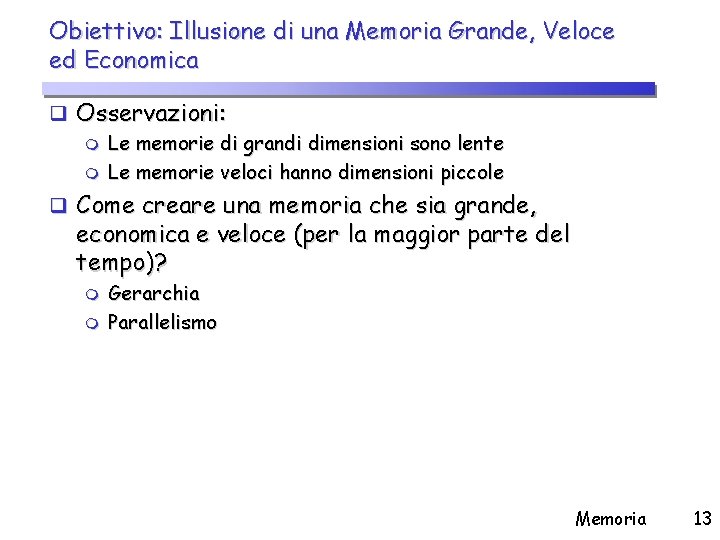

Obiettivo: Illusione di una Memoria Grande, Veloce ed Economica q Osservazioni: m Le memorie di grandi dimensioni sono lente m Le memorie veloci hanno dimensioni piccole q Come creare una memoria che sia grande, economica e veloce (per la maggior parte del tempo)? m m Gerarchia Parallelismo Memoria 13

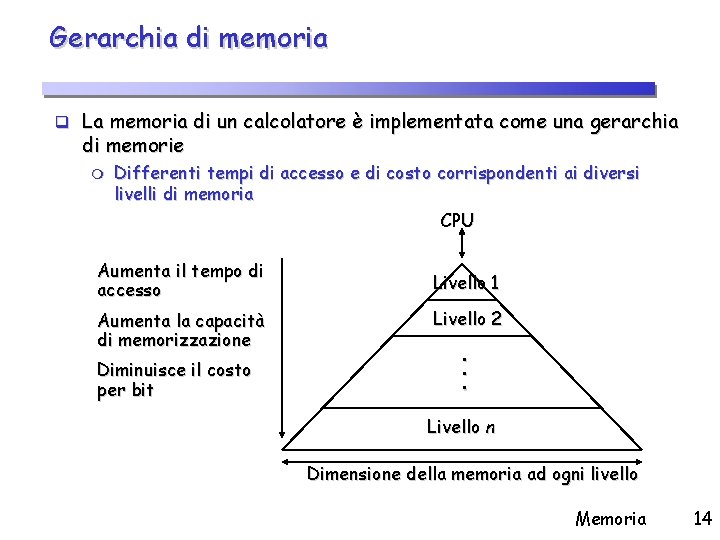

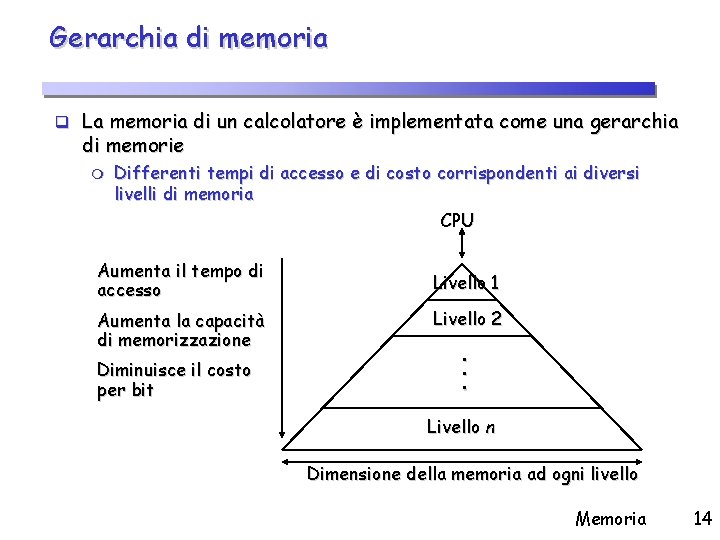

Gerarchia di memoria q La memoria di un calcolatore è implementata come una gerarchia di memorie m Differenti tempi di accesso e di costo corrispondenti ai diversi livelli di memoria CPU Aumenta il tempo di accesso Aumenta la capacità di memorizzazione Diminuisce il costo per bit Livello 1 Livello 2 . . . Livello n Dimensione della memoria ad ogni livello Memoria 14

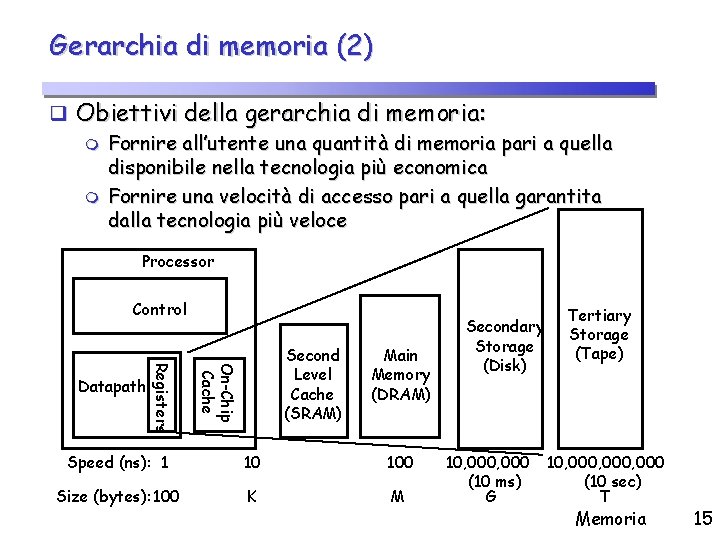

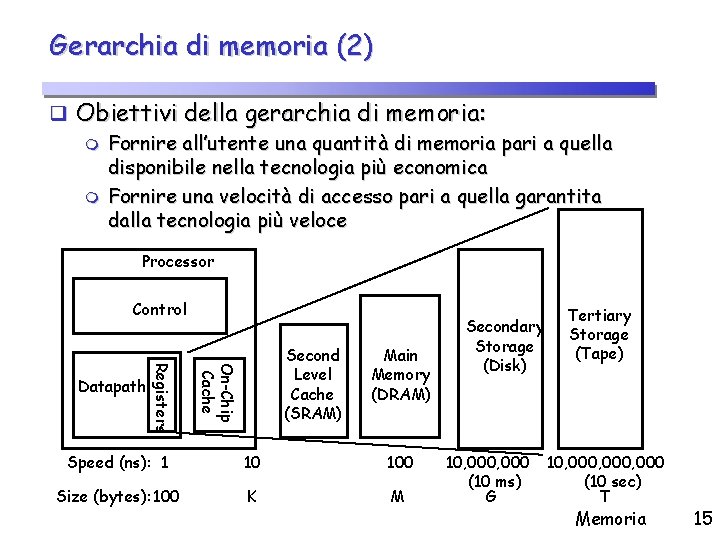

Gerarchia di memoria (2) q Obiettivi della gerarchia di memoria: m Fornire all’utente una quantità di memoria pari a quella disponibile nella tecnologia più economica m Fornire una velocità di accesso pari a quella garantita dalla tecnologia più veloce Processor Control On-Chip Cache Registers Datapath Second Level Cache (SRAM) Main Memory (DRAM) Speed (ns): 1 10 100 Size (bytes): 100 K M Secondary Storage (Disk) 10, 000 (10 ms) G Tertiary Storage (Tape) 10, 000, 000 (10 sec) T Memoria 15

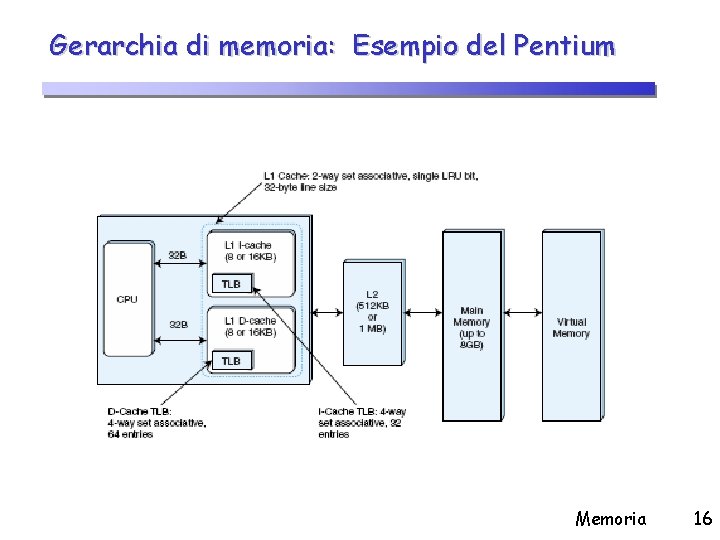

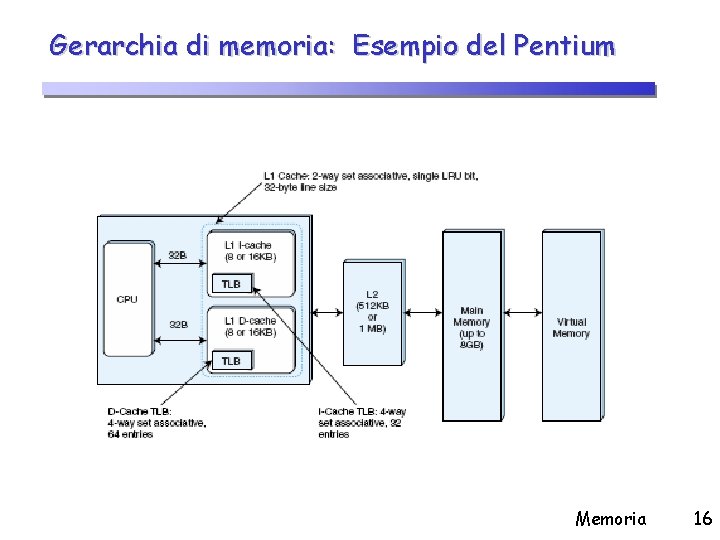

Gerarchia di memoria: Esempio del Pentium Memoria 16

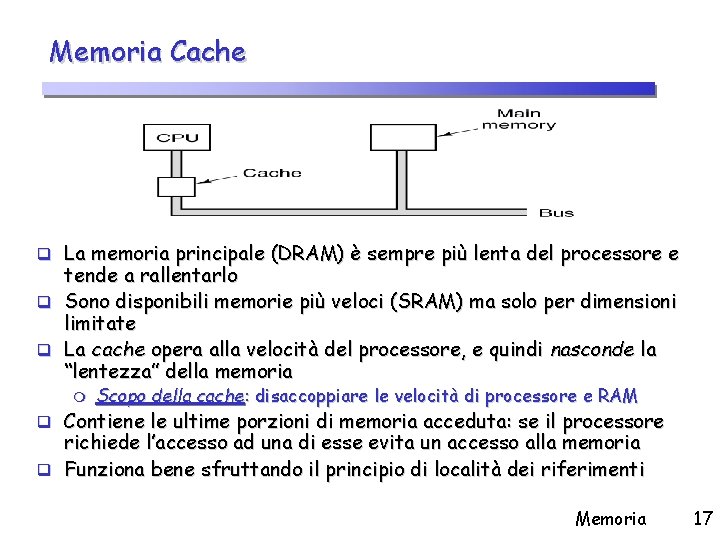

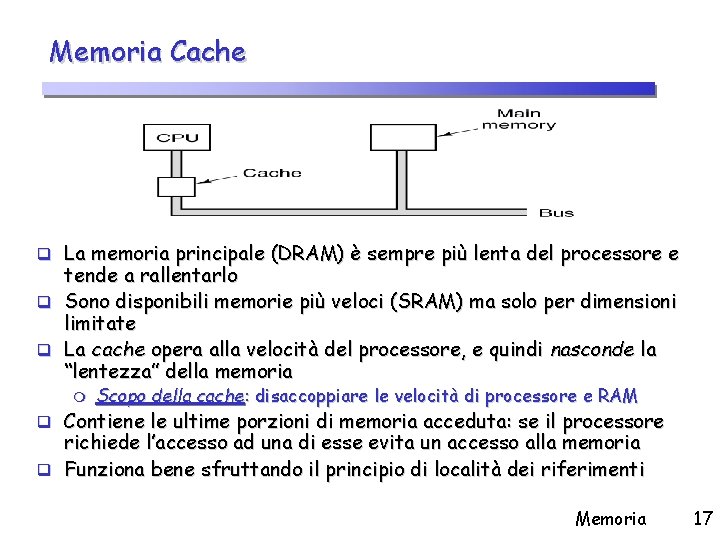

Memoria Cache q La memoria principale (DRAM) è sempre più lenta del processore e q q tende a rallentarlo Sono disponibili memorie più veloci (SRAM) ma solo per dimensioni limitate La cache opera alla velocità del processore, e quindi nasconde la “lentezza” della memoria m Scopo della cache: disaccoppiare le velocità di processore e RAM q Contiene le ultime porzioni di memoria acceduta: se il processore richiede l’accesso ad una di esse evita un accesso alla memoria q Funziona bene sfruttando il principio di località dei riferimenti Memoria 17

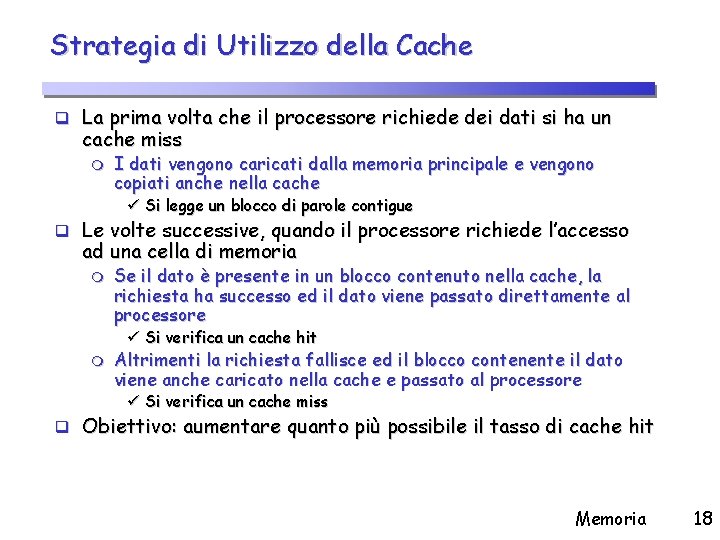

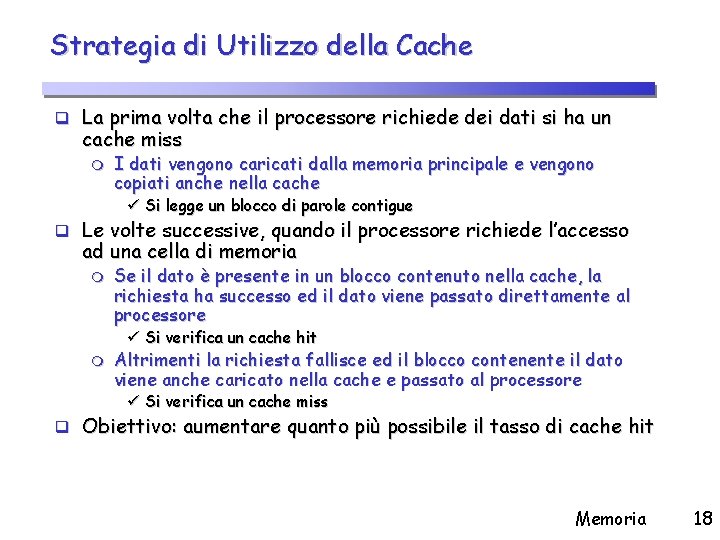

Strategia di Utilizzo della Cache q La prima volta che il processore richiede dei dati si ha un cache miss m I dati vengono caricati dalla memoria principale e vengono copiati anche nella cache ü Si legge un blocco di parole contigue q Le volte successive, quando il processore richiede l’accesso ad una cella di memoria m Se il dato è presente in un blocco contenuto nella cache, la richiesta ha successo ed il dato viene passato direttamente al processore ü Si verifica un cache hit m Altrimenti la richiesta fallisce ed il blocco contenente il dato viene anche caricato nella cache e passato al processore ü Si verifica un cache miss q Obiettivo: aumentare quanto più possibile il tasso di cache hit Memoria 18

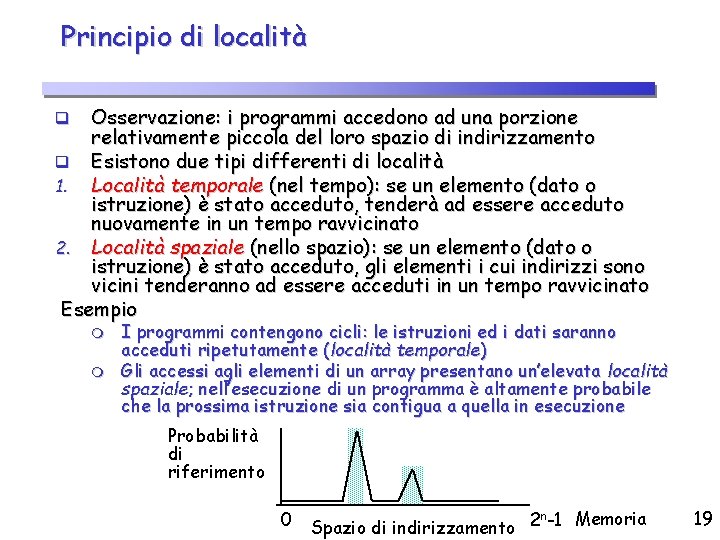

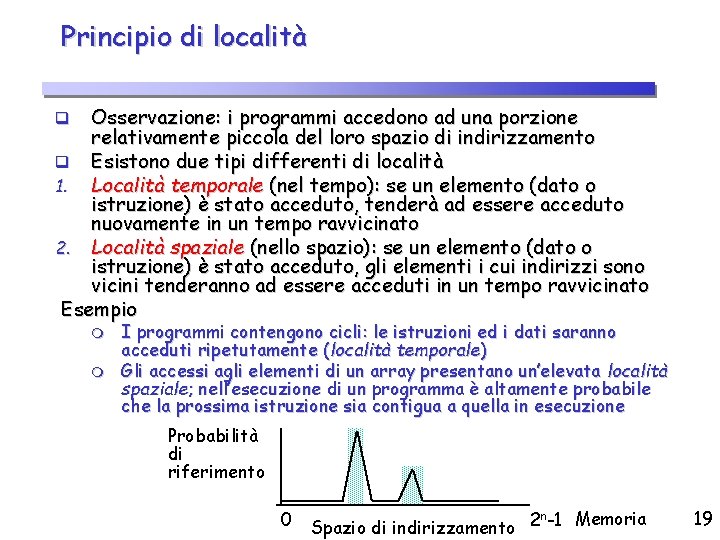

Principio di località Osservazione: i programmi accedono ad una porzione relativamente piccola del loro spazio di indirizzamento q Esistono due tipi differenti di località 1. Località temporale (nel tempo): se un elemento (dato o istruzione) è stato acceduto, tenderà ad essere acceduto nuovamente in un tempo ravvicinato 2. Località spaziale (nello spazio): se un elemento (dato o istruzione) è stato acceduto, gli elementi i cui indirizzi sono vicini tenderanno ad essere acceduti in un tempo ravvicinato Esempio q m m I programmi contengono cicli: le istruzioni ed i dati saranno acceduti ripetutamente (località temporale) Gli accessi agli elementi di un array presentano un’elevata località spaziale; nell’esecuzione di un programma è altamente probabile che la prossima istruzione sia contigua a quella in esecuzione Probabilità di riferimento 0 n Spazio di indirizzamento 2 -1 Memoria 19

Principio di località (2) q Come sfruttare la: 1. Località temporale m Tenendo gli elementi acceduti più frequentemente vicino al processore 2. Località spaziale m Spostando blocchi contigui di parole al livello superiore Memoria 20