Cadences Solution for HighSpeed Design Cadence Design Systems

- Slides: 53

Cadence’s Solution for High-Speed Design Cadence Design Systems, Inc.

confidential Agenda 2 §What is High-Speed Design? §Ideal High-Speed Design Process §Introduction to SPECCTRAQuest Power Integrity §SPECCTRAQuest Demonstration

confidential The Day of “High-Speed” Has Come 3 “Pc-board designers, meanwhile, were retooling in 1999 for high-speed design. Signal integrity, once confined to high-end boards, has become everybody’s problem…” Richard Goering, commenting on why the PCB layout market grew 20% while the IC layout market shrunk 30%, in EETimes 4/10/2000 page 70

confidential Welcome Networking! 4 Hammerhead Networks

Agenda confidential NOW 5 §What is High-Speed Design? §Ideal High-Speed Design Process §SPECCTRAQuest Demonstration §Introduction to SPECCTRAQuest Power Integrity

“H ? What is “High-Speed” to ig wice its edg sig e-speed yt wh na n e hin en l i h w ric g it s “H s r yo is u lect ant c c u’v f igh o die ort ” e ast -S mp ed and i de er pe e p S sig t ed me t o h c c h g e ne an ” e d “Hi eff ts b be n fec i k f Huh? s s ef or e los confidential an 6 fre h-Sp qu ee en d” z H M cy is o 0 5 f ” r ris , it’ n’t Ove h-Speed e t s a rel g i im fu ate is “H nc d e s A net is “Hig tio h-Speed” w n hen its round-trip delay is grea A than t ter

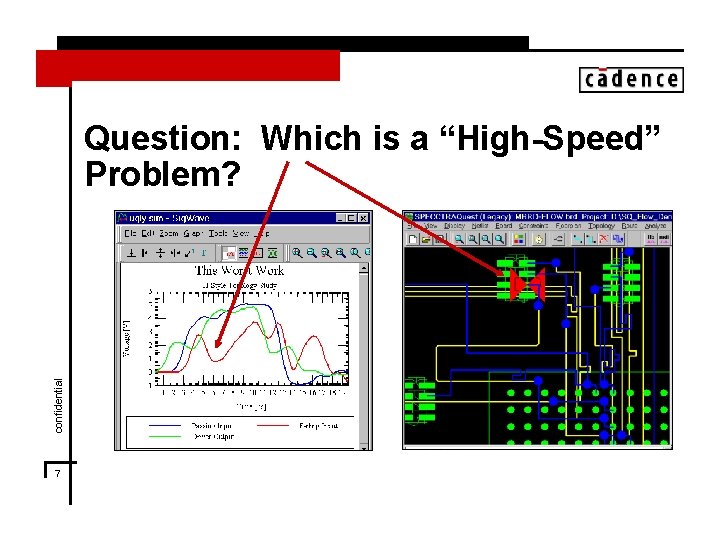

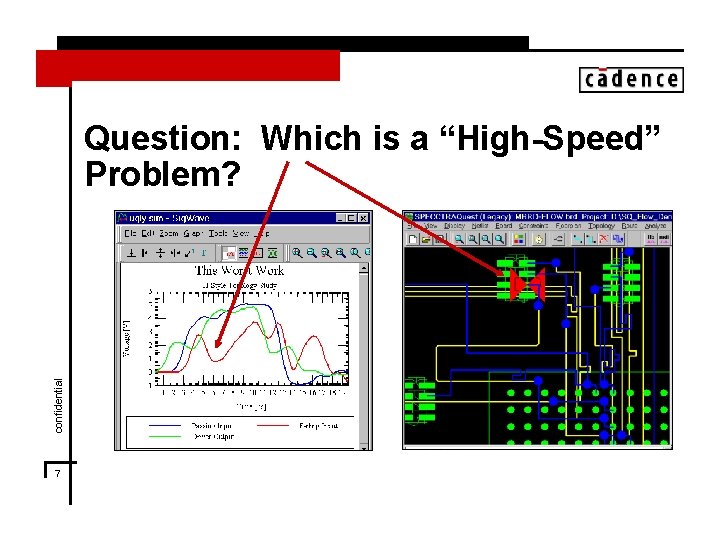

confidential Question: Which is a “High-Speed” Problem? 7

confidential Answer: They BOTH Are !! 8

Definition of High-Speed confidential A net can be considered ‘High-Speed’ when you have to do something other than simply connect it. 9

High-Speed Design Involves 2 Things Nets that are understood, and must be confidential constrained Nets that must be analyzed to be understood, and then 10 constrained

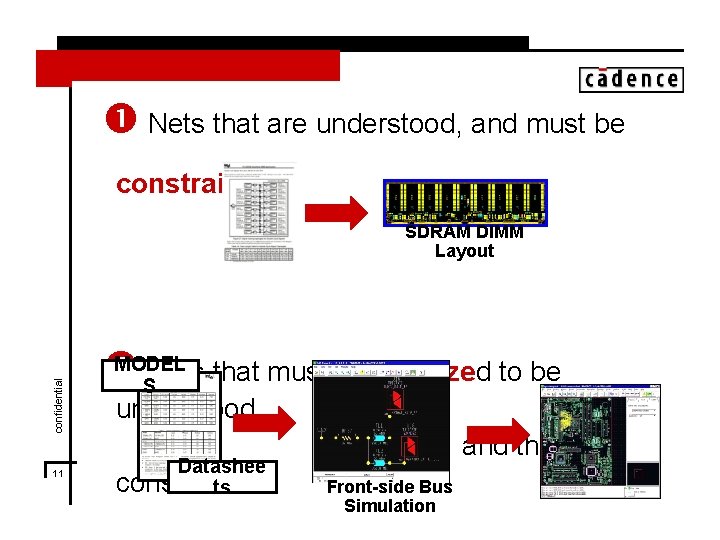

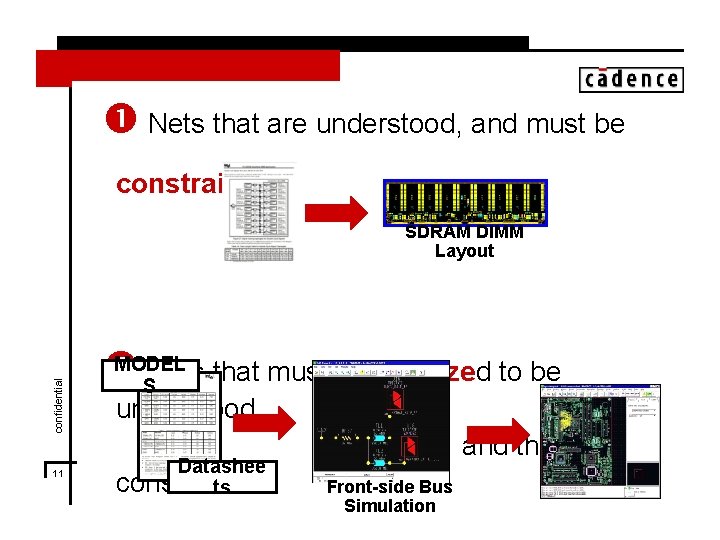

Nets that are understood, and must be constrained confidential SDRAM DIMM Layout 11 MODEL Nets that must be analyzed to be S understood, Datashee constrained ts and then Front-side Bus Simulation

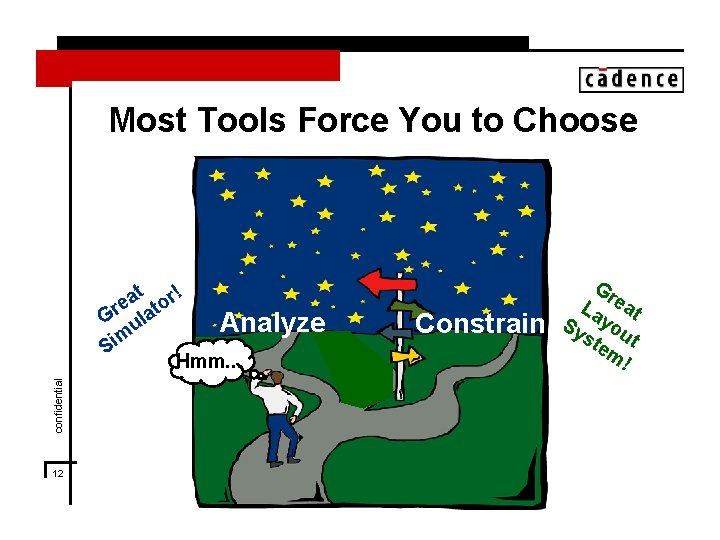

Most Tools Force You to Choose confidential at or! e t Gr ula Analyze m i S Hmm. . . 12 Constrain Gr La eat Sy you ste t m!

But for High-Speed You Need BOTH confidential Let’s Go! 13 Analyze & Constrain All in ONE integrated & interactive environment !

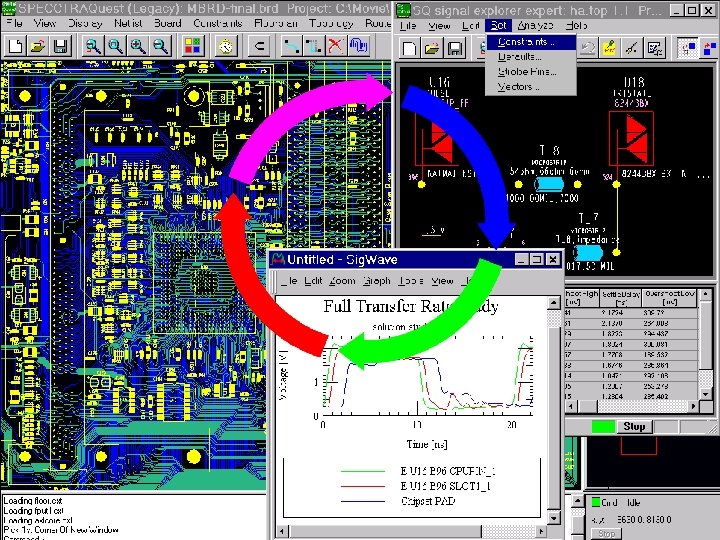

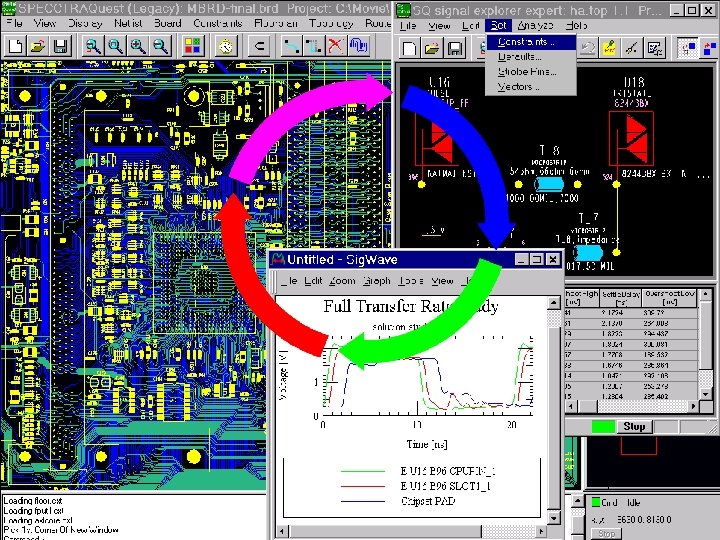

14 confidential

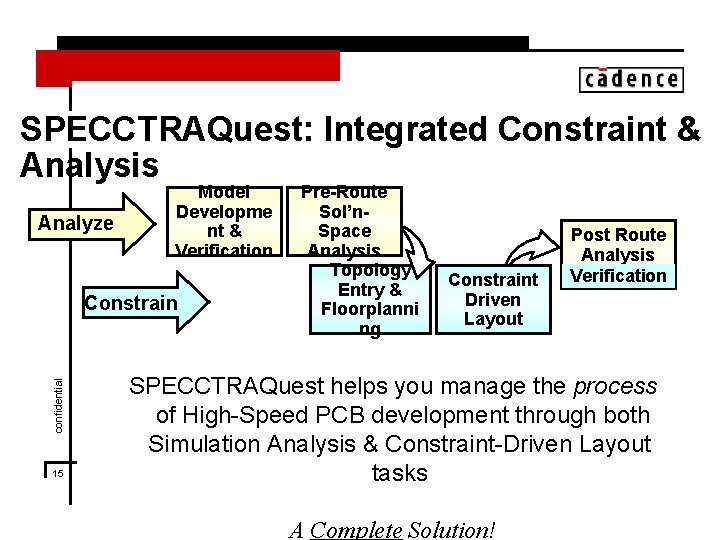

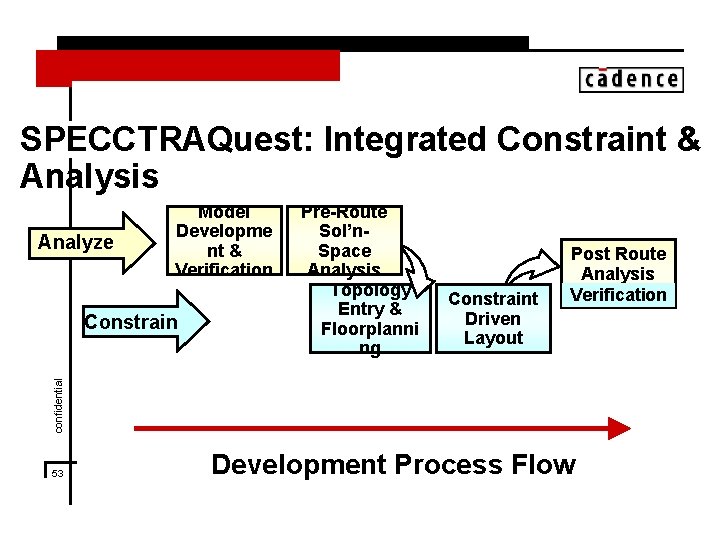

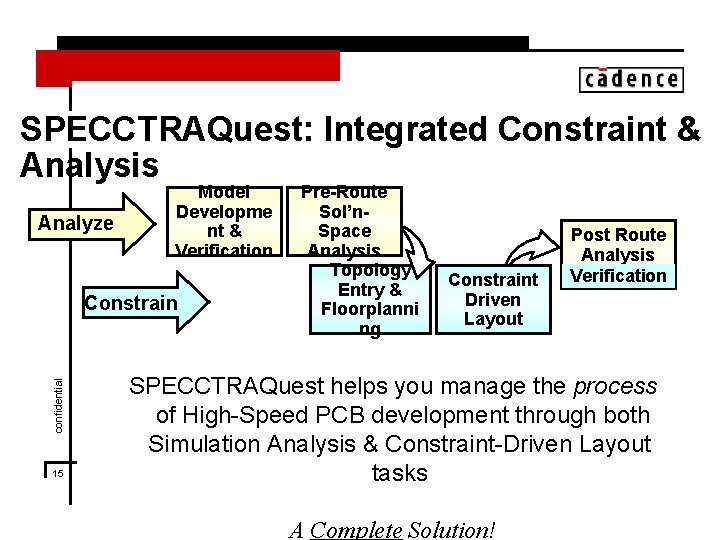

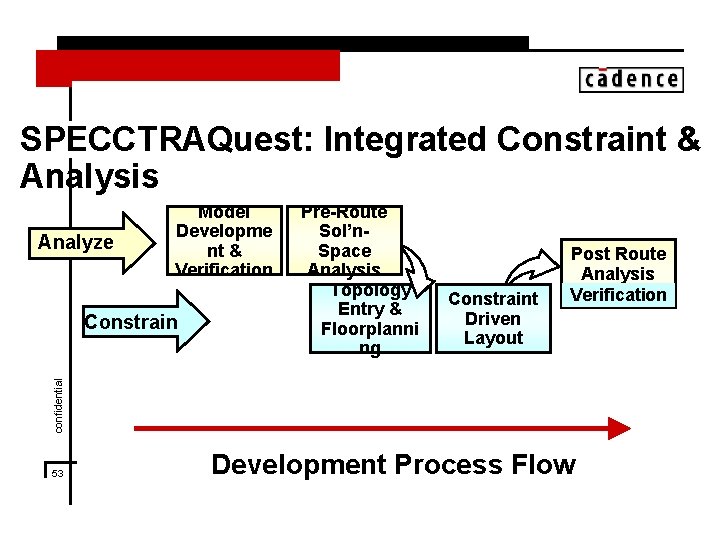

SPECCTRAQuest: Integrated Constraint & Analysis Analyze Model Developme nt & Verification confidential Constrain 15 Pre-Route Sol’n. Space Analysis Topology Entry & Floorplanni ng Constraint Driven Layout Post Route Analysis Verification SPECCTRAQuest helps you manage the process of High-Speed PCB development through both Simulation Analysis & Constraint-Driven Layout tasks A Complete Solution!

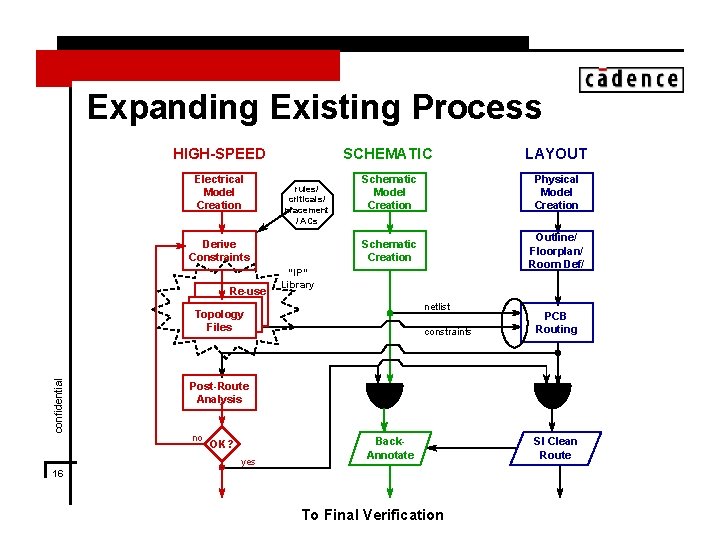

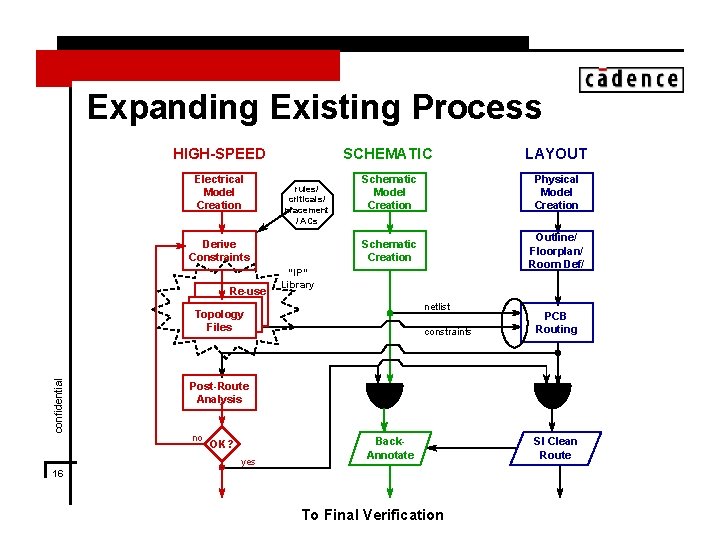

Expanding Existing Process HIGH-SPEED Electrical Model Creation rules/ criticals/ placement / ACs Derive Constraints confidential Re-use Topology Files SCHEMATIC LAYOUT Schematic Model Creation Physical Model Creation Schematic Creation Outline/ Floorplan/ Room Def/ “IP” Library netlist constraints PCB Routing Post-Route Analysis no OK? yes Back. Annotate 16 To Final Verification SI Clean Route

Agenda confidential NOW 17 §What is High-Speed Design? §Ideal High-Speed Design Process §SPECCTRAQuest Demonstration §Introduction to SPECCTRAQuest Power Integrity

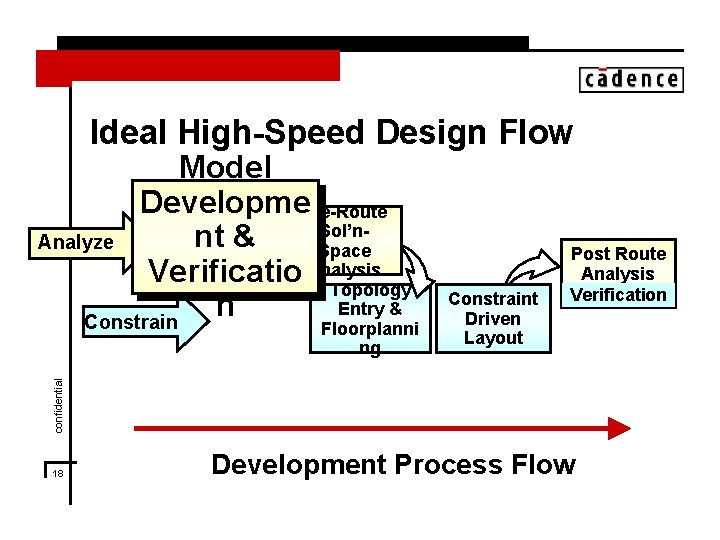

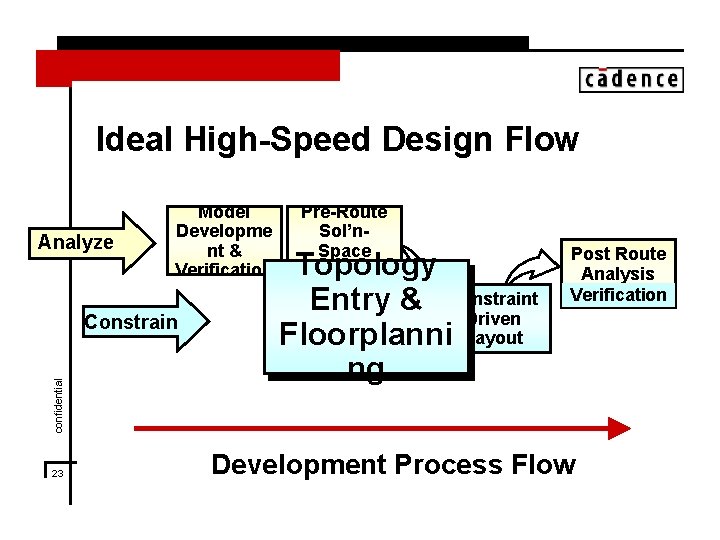

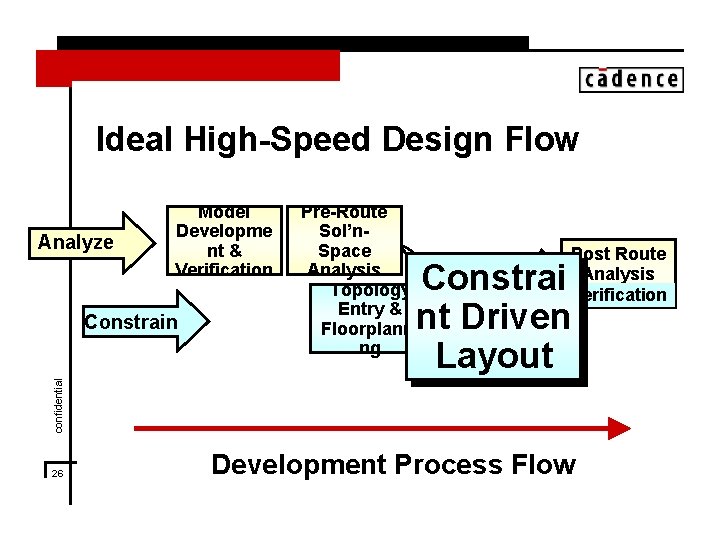

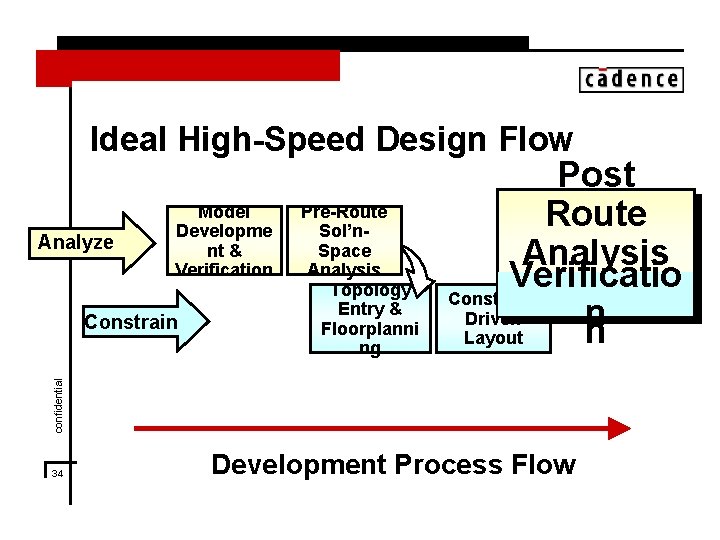

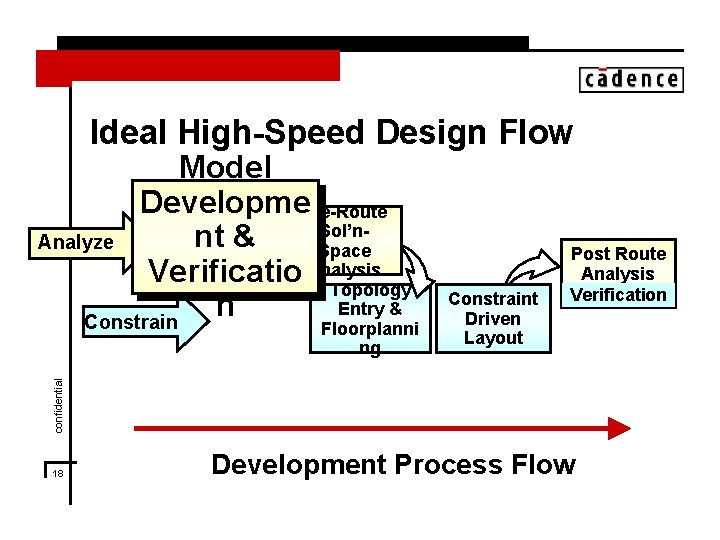

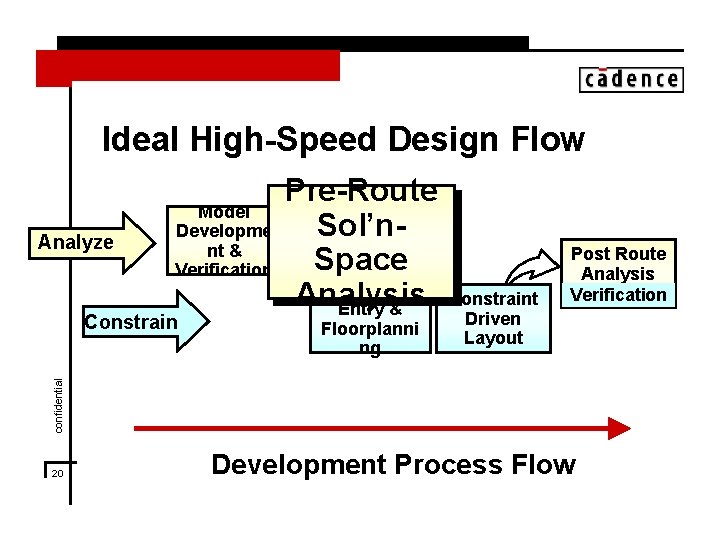

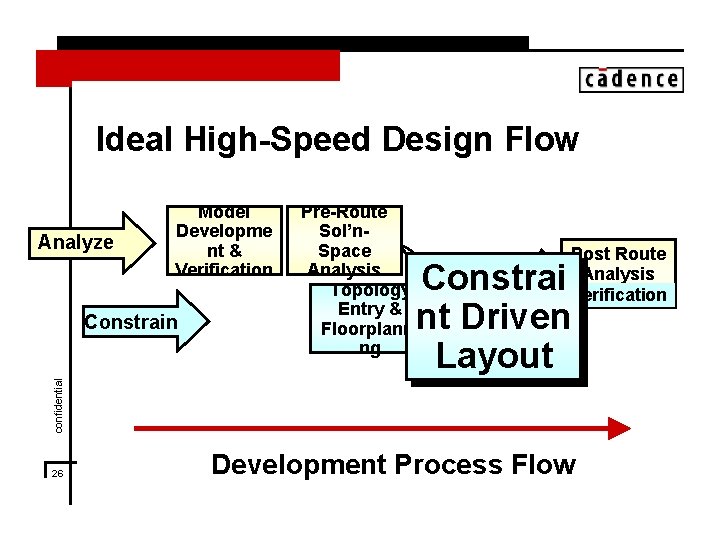

Ideal High-Speed Design Flow Model Developme Model Pre-Route Developme Sol’nnt & Analyze nt & Space Verification Analysis Verificatio Topology Entry & n Constrain confidential Floorplanni ng Constraint Driven Layout Post Route Analysis Verification 18 Development Process Flow

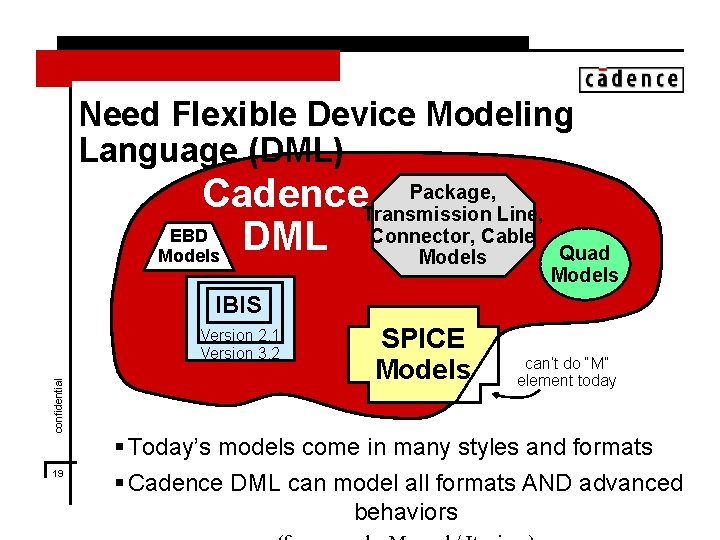

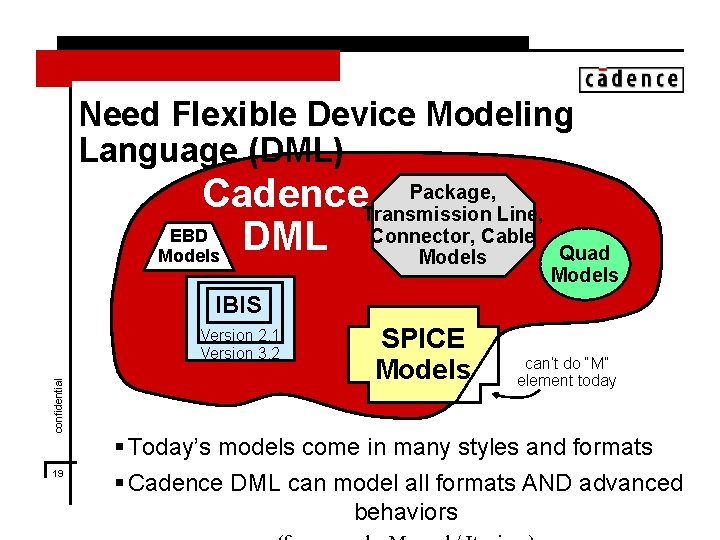

Need Flexible Device Modeling Language (DML) Package, Cadence. Transmission Line, EBD Connector, Cable DML Models Quad Models IBIS confidential Version 2. 1 Version 3. 2 19 SPICE Models can’t do “M” element today § Today’s models come in many styles and formats § Cadence DML can model all formats AND advanced behaviors

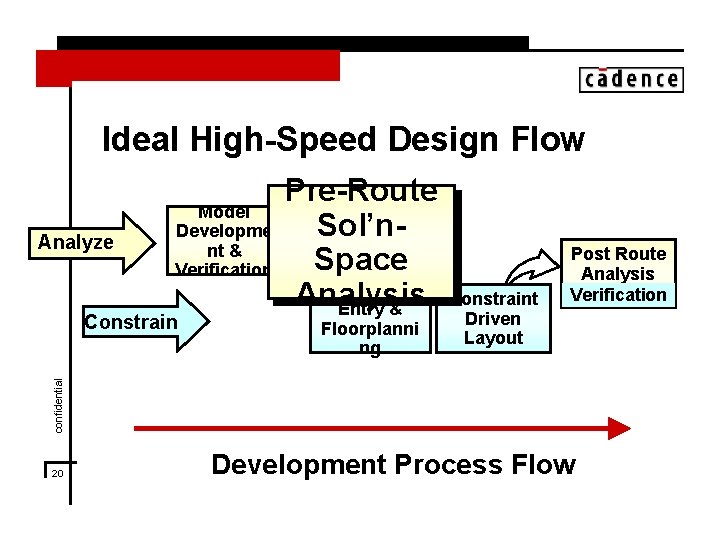

Ideal High-Speed Design Flow Analyze Model Developme nt & Verification Floorplanni ng Constraint Driven Layout Post Route Analysis Verification confidential Constrain Pre-Route Sol’n. Space Analysis Topology Analysis Entry & 20 Development Process Flow

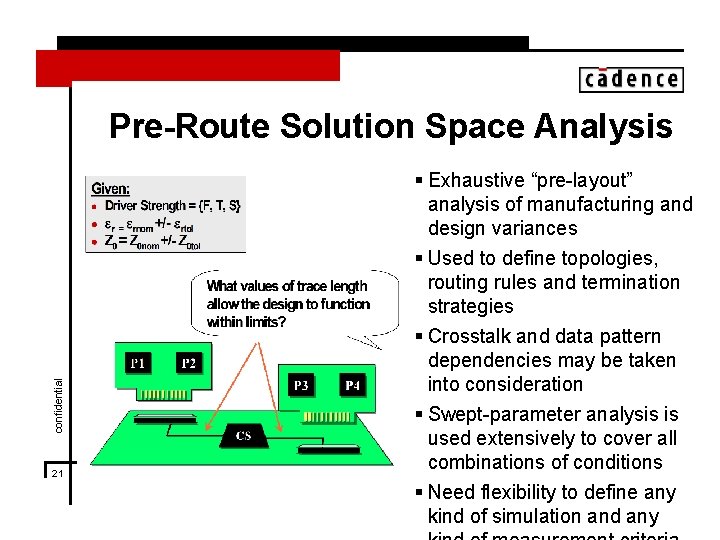

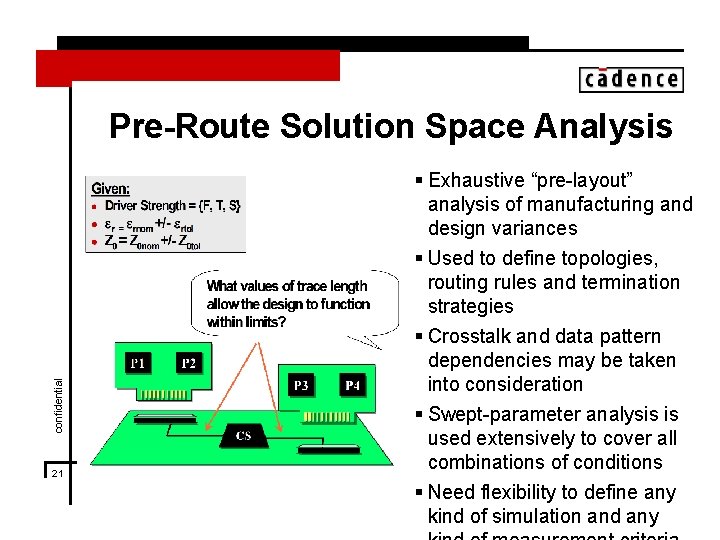

confidential Pre-Route Solution Space Analysis 21 § Exhaustive “pre-layout” analysis of manufacturing and design variances § Used to define topologies, routing rules and termination strategies § Crosstalk and data pattern dependencies may be taken into consideration § Swept-parameter analysis is used extensively to cover all combinations of conditions § Need flexibility to define any kind of simulation and any

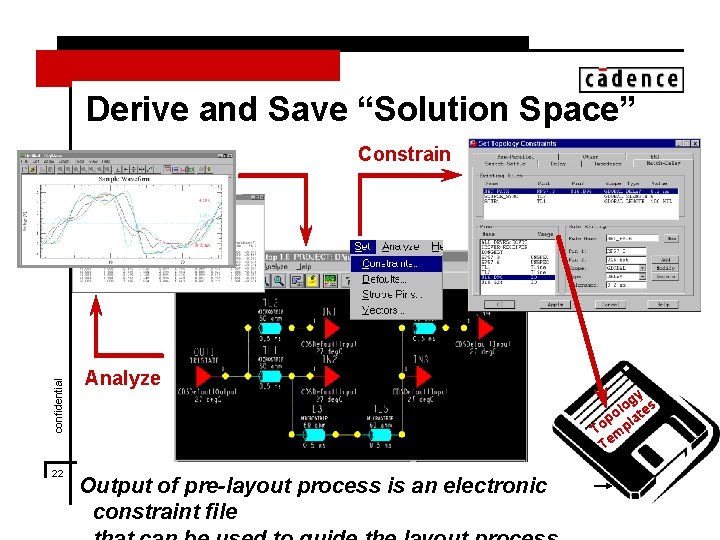

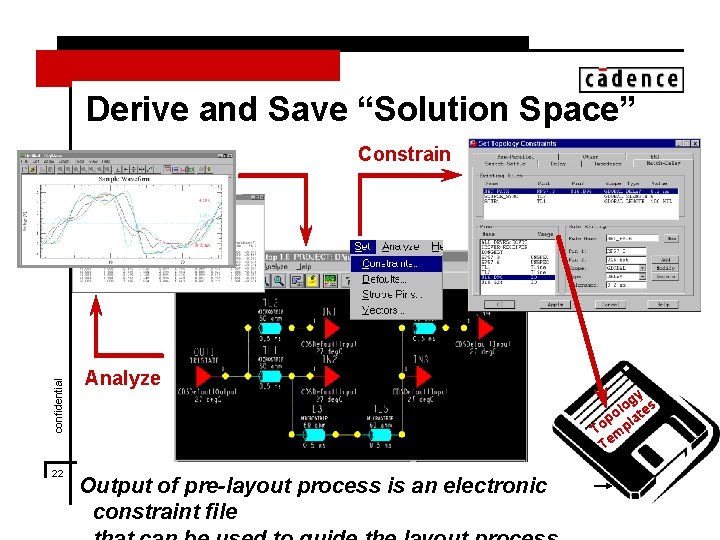

Derive and Save “Solution Space” confidential Constrain 22 Analyze Output of pre-layout process is an electronic constraint file y og es l po lat o T mp Te

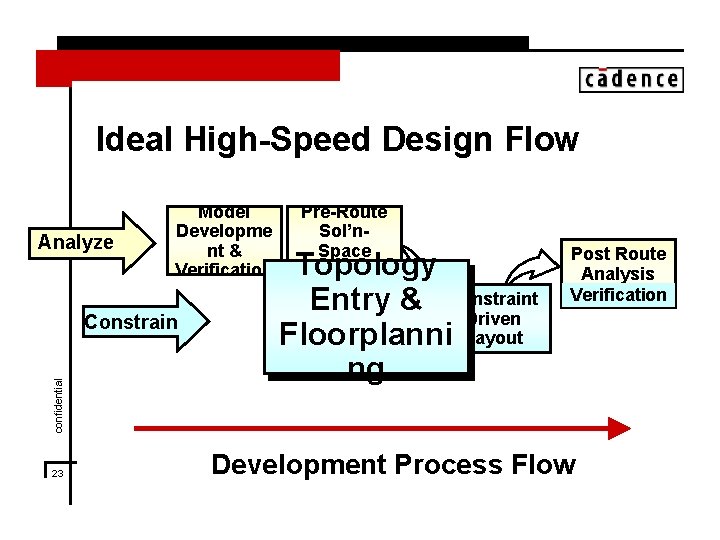

Ideal High-Speed Design Flow Analyze Model Developme nt & Verification confidential Constrain 23 Pre-Route Sol’n. Space Analysis Topology Entry & Floorplanni ng Topology Entry & Constraint Driven Floorplanni Layout ng Post Route Analysis Verification Development Process Flow

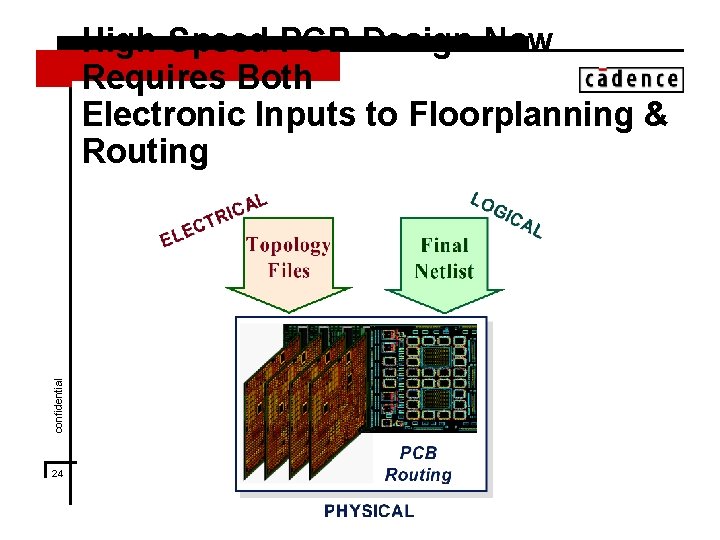

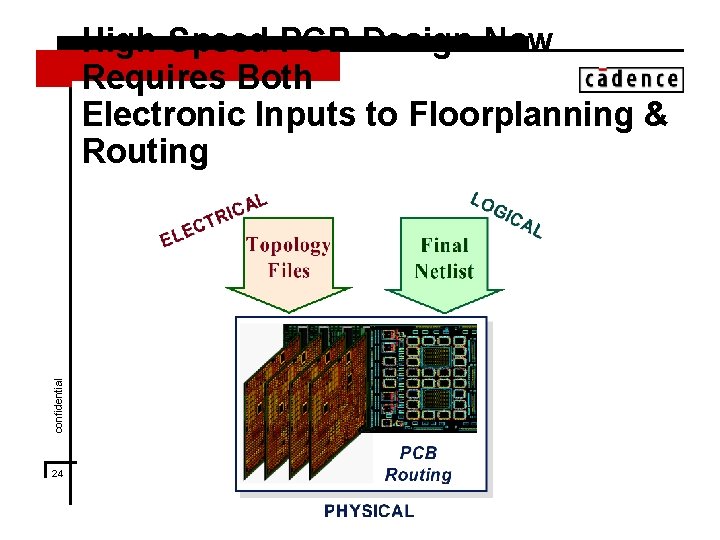

confidential High-Speed PCB Design Now Requires Both Electronic Inputs to Floorplanning & Routing 24

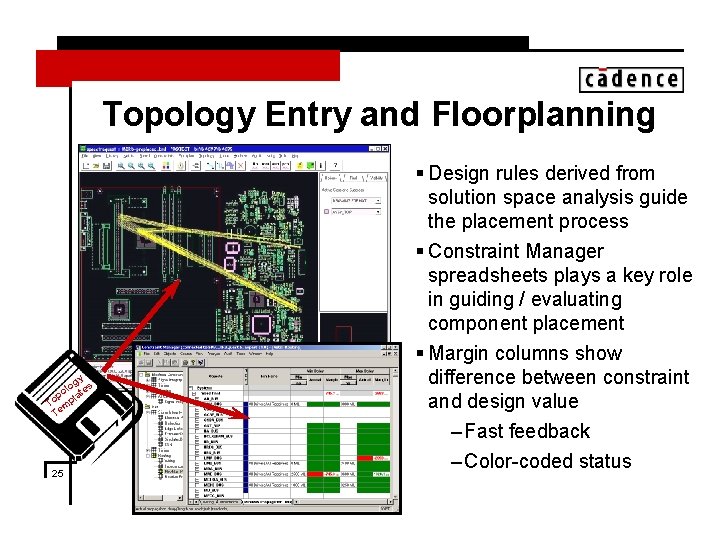

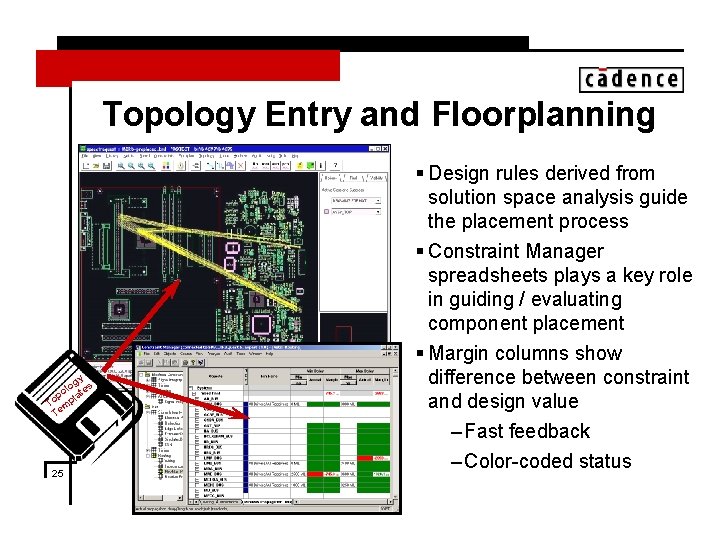

Topology Entry and Floorplanning confidential gy lo tes o p la To mp Te 25 § Design rules derived from solution space analysis guide the placement process § Constraint Manager spreadsheets plays a key role in guiding / evaluating component placement § Margin columns show difference between constraint and design value – Fast feedback – Color-coded status

Ideal High-Speed Design Flow Analyze Model Developme nt & Verification Post Route Analysis Verification Constraint Driven Layout confidential Constrain Pre-Route Sol’n. Space Analysis Topology Entry & Floorplanni ng 26 Development Process Flow

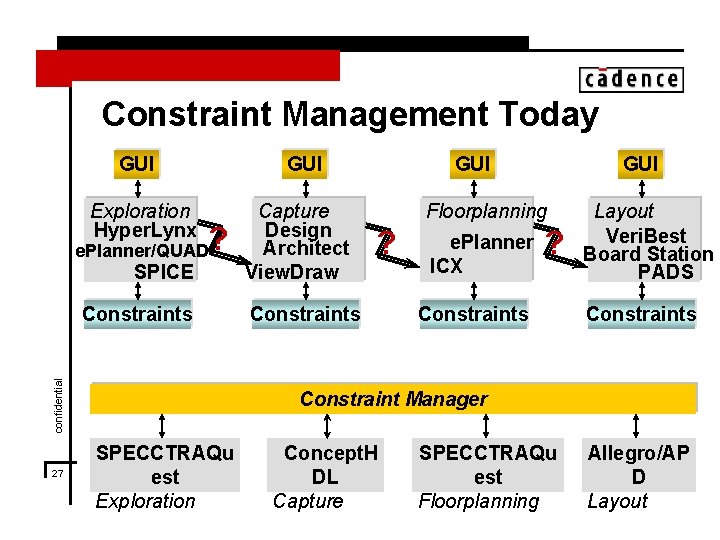

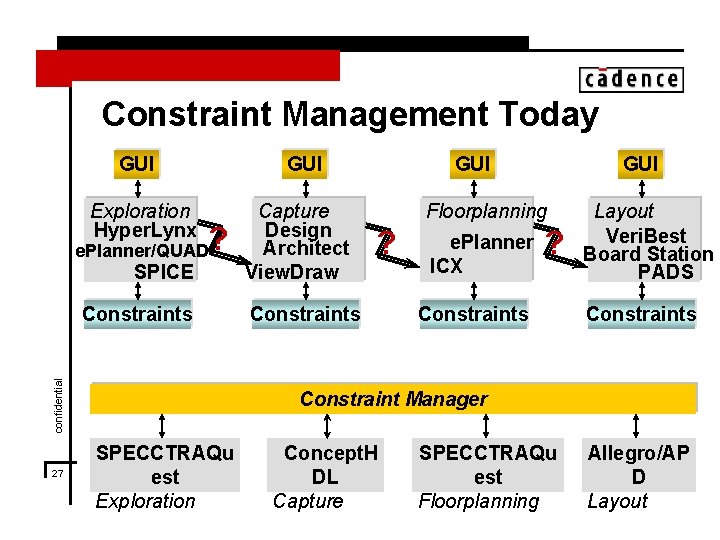

Constraint Management Today GUI Exploration Hyper. Lynx GUI ? e. Planner/QUAD SPICE confidential Constraints 27 Capture Design Architect View. Draw GUI Floorplanning ? Constraints e. Planner ICX ? Constraints Layout Veri. Best Board Station PADS Constraints Constraint Manager SPECCTRAQu est Exploration Concept. H DL Capture SPECCTRAQu est Floorplanning Allegro/AP D Layout

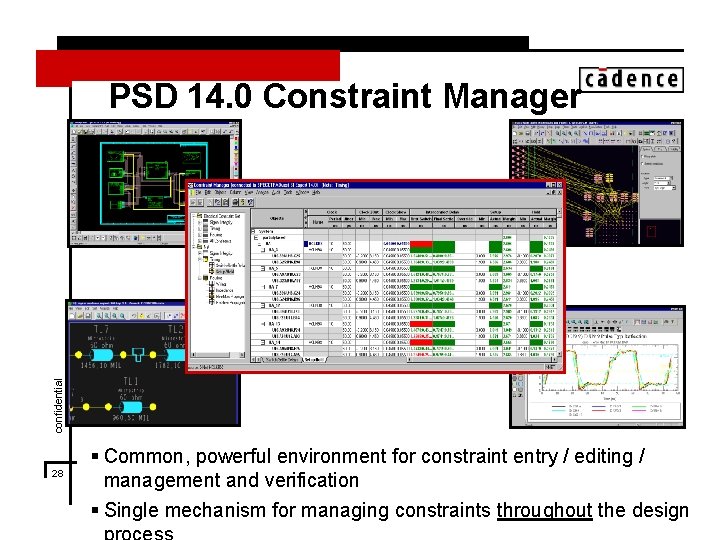

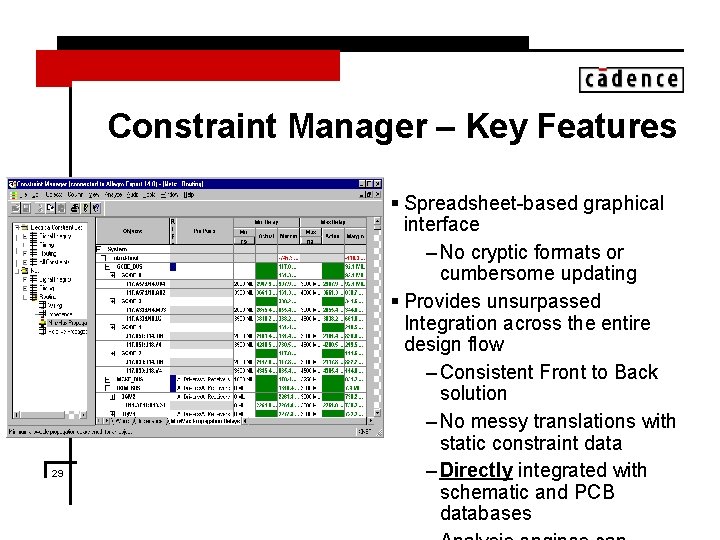

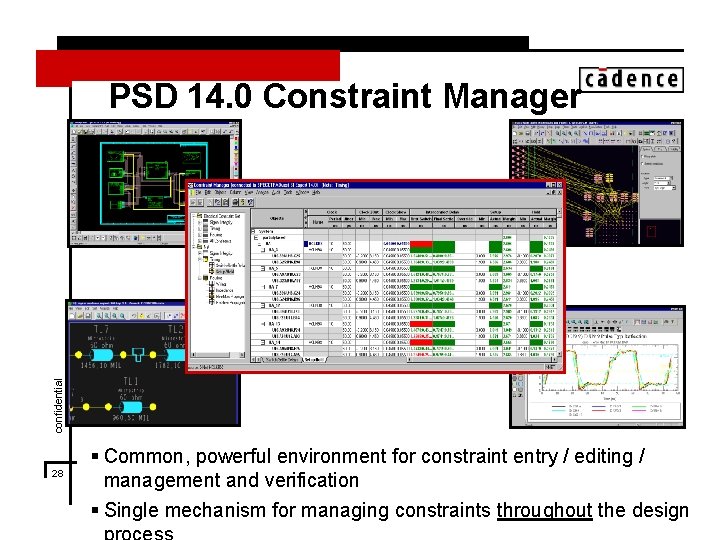

confidential PSD 14. 0 Constraint Manager 28 § Common, powerful environment for constraint entry / editing / management and verification § Single mechanism for managing constraints throughout the design

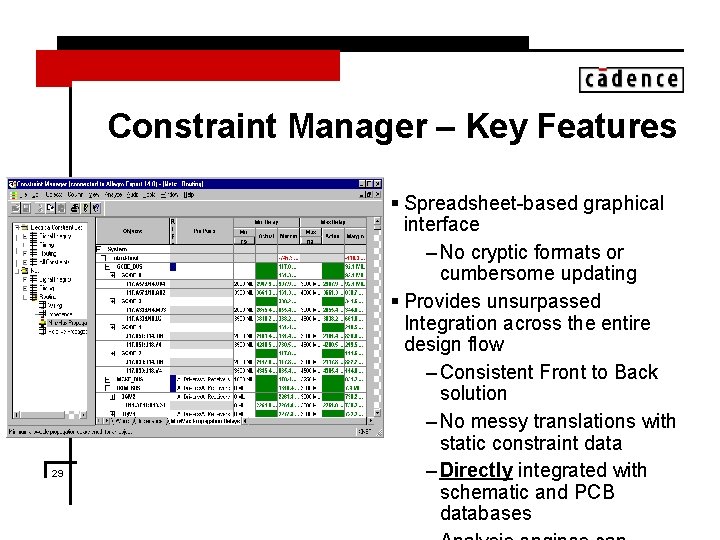

confidential Constraint Manager – Key Features 29 § Spreadsheet-based graphical interface – No cryptic formats or cumbersome updating § Provides unsurpassed Integration across the entire design flow – Consistent Front to Back solution – No messy translations with static constraint data – Directly integrated with schematic and PCB databases

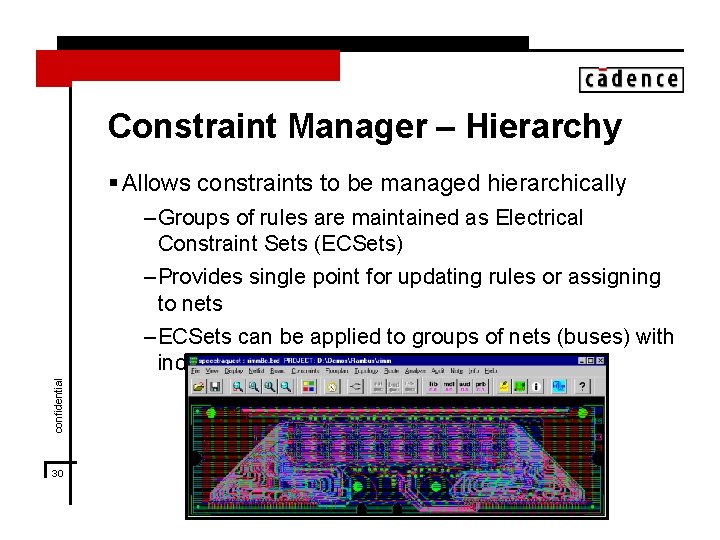

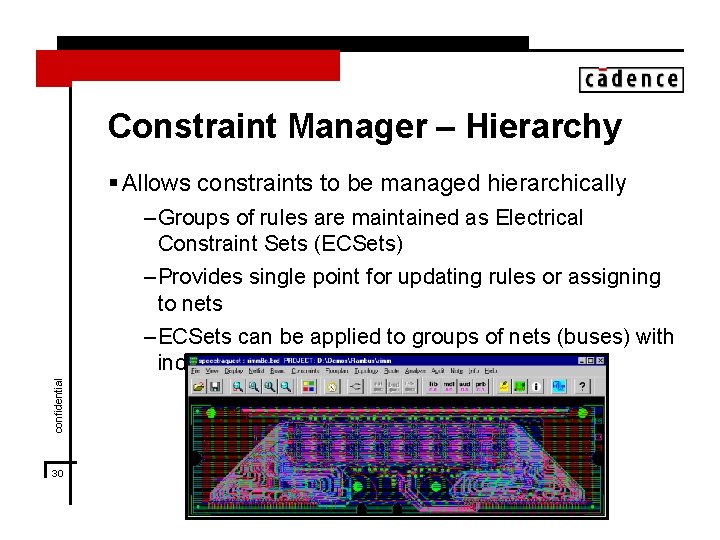

Constraint Manager – Hierarchy § Allows constraints to be managed hierarchically confidential – Groups of rules are maintained as Electrical Constraint Sets (ECSets) – Provides single point for updating rules or assigning to nets – ECSets can be applied to groups of nets (buses) with individual overrides 30

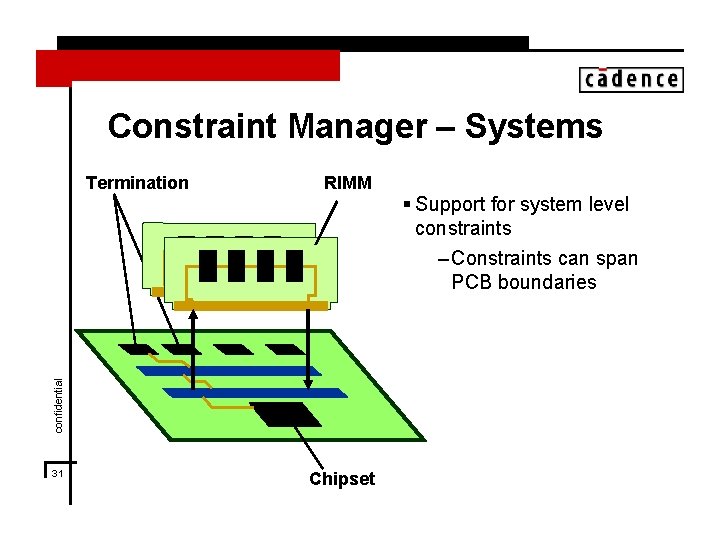

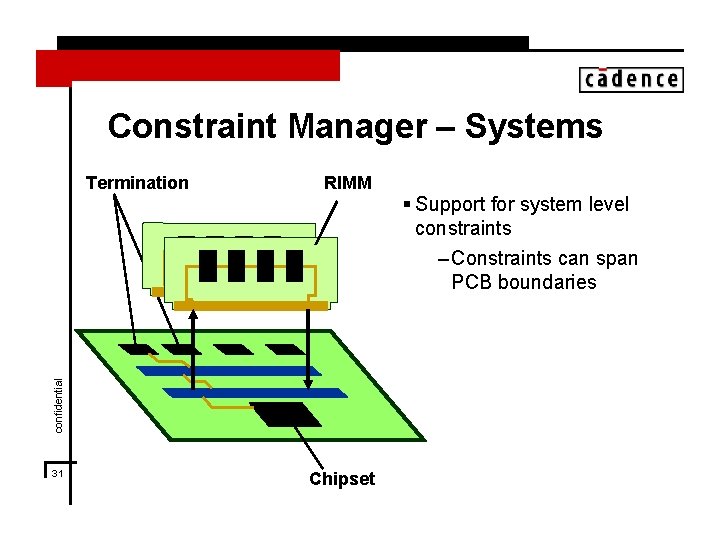

Constraint Manager – Systems Termination RIMM confidential § Support for system level constraints – Constraints can span PCB boundaries 31 Chipset

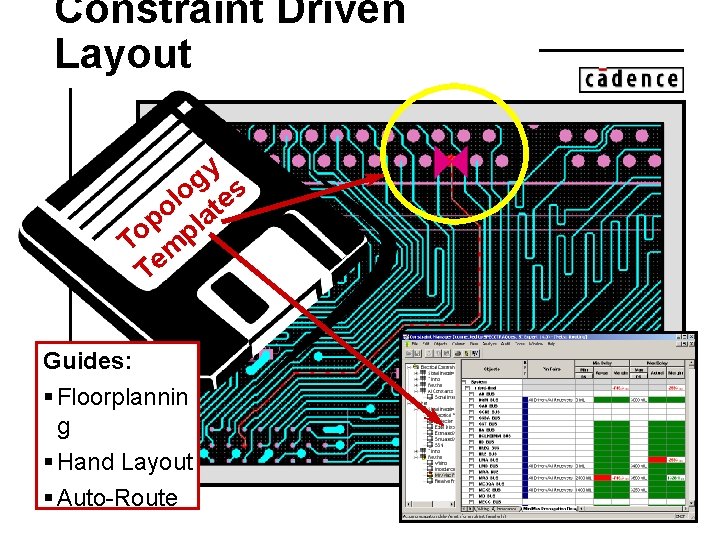

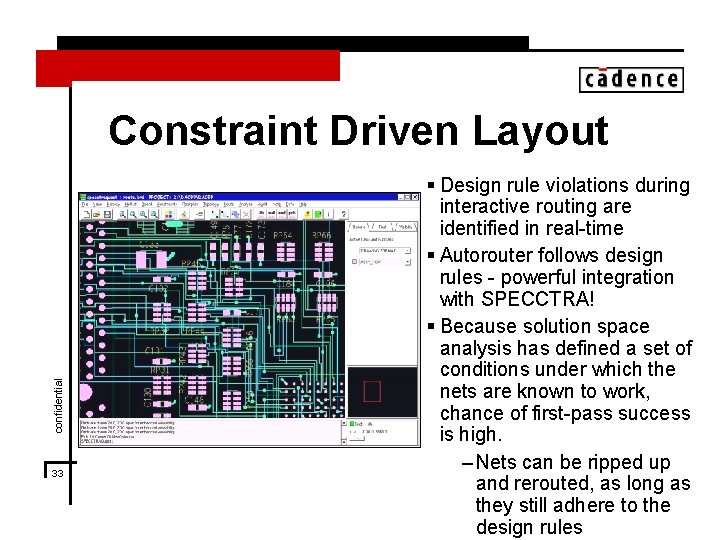

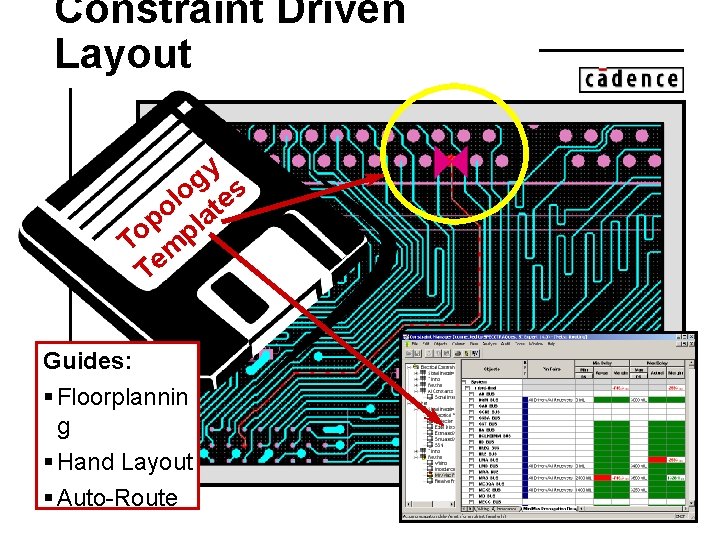

Constraint Driven Layout y g o es l o lat p To mp Te confidential Guides: § Floorplannin g § 32 Hand Layout § Auto-Route

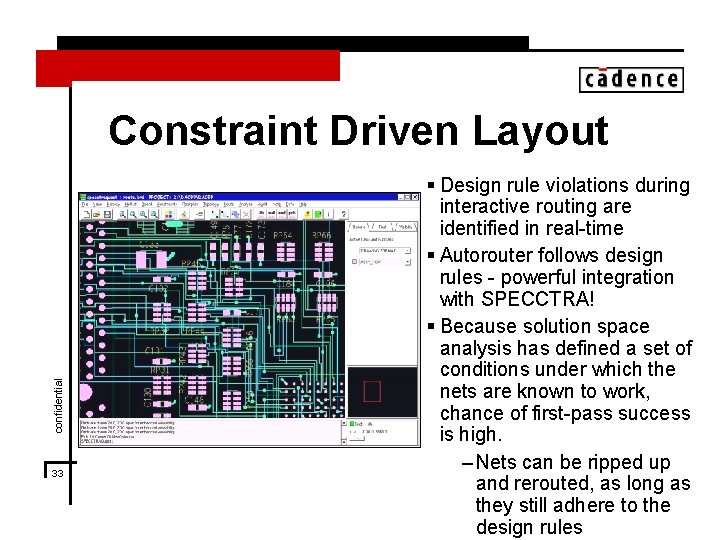

confidential Constraint Driven Layout 33 § Design rule violations during interactive routing are identified in real-time § Autorouter follows design rules - powerful integration with SPECCTRA! § Because solution space analysis has defined a set of conditions under which the nets are known to work, chance of first-pass success is high. – Nets can be ripped up and rerouted, as long as they still adhere to the design rules

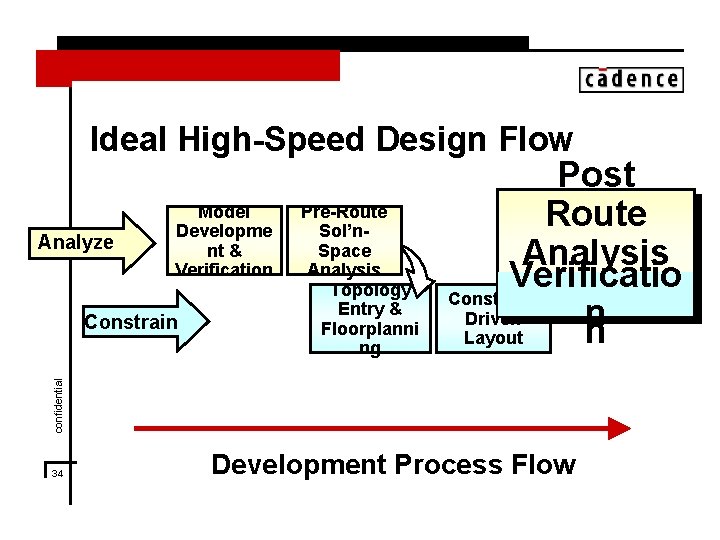

Ideal High-Speed Design Flow Analyze Model Developme nt & Verification confidential Constrain Pre-Route Sol’n. Space Analysis Topology Entry & Floorplanni ng Post Route Analysis Verification Verificatio Constraint Driven n n Layout 34 Development Process Flow

Agenda confidential NOW 35 §What is High-Speed Design? §Ideal High-Speed Design Process §Introduction to SPECCTRAQuest Power Integrity §SPECCTRAQuest Demonstration

SPECCTRAQuest Power Integrity Module The Future of Power Delivery System Design Cadence Design Systems, Inc.

SPECCTRAQuest Power Integrity confidential § Innovative technology developed and proven by Sun Microsystems, now commercialized by Cadence Design Systems, Inc. to address Power Delivery issues in high-speed PCB System Designs. § A design tool / methodology used to design and optimize the frequency-dependent characteristics of Power Delivery Systems in high-speed system designs 37 § An integrated solution to allow many quick iterations of

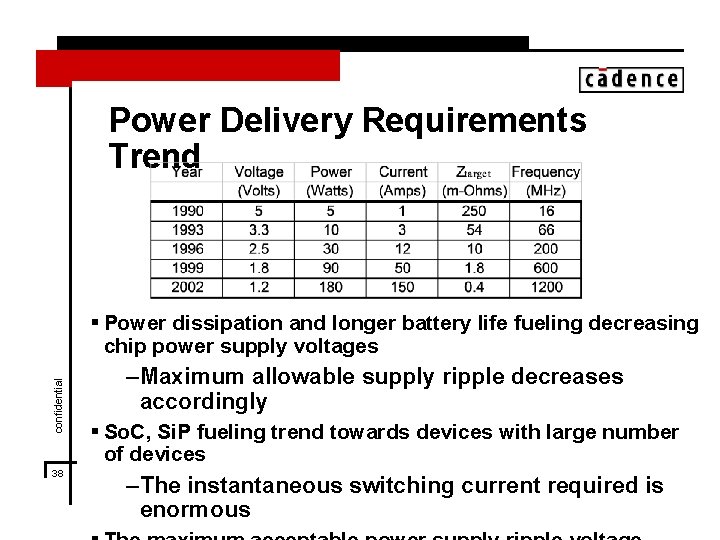

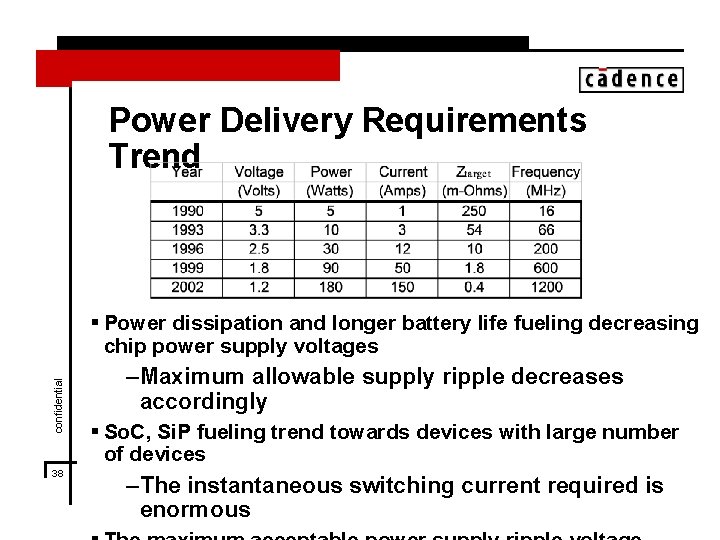

Power Delivery Requirements Trend confidential § Power dissipation and longer battery life fueling decreasing chip power supply voltages 38 –Maximum allowable supply ripple decreases accordingly § So. C, Si. P fueling trend towards devices with large number of devices –The instantaneous switching current required is enormous

Power Delivery System Design Challenges § Power supply droop confidential – Alters system timing and can cause Setup failures – Can cause sampling errors that results in a system crash 39 § Unreliable power delivery system design cause increased common-mode EMI preventing product shipment due to compliance problems § Power delivery system impedance is frequencydependent Development – Must be controlled for. Increases all frequency range of all Costs and Time to Market is LOST! transient currents

Power Delivery System Design How it is done today § Standalone analysis tools – Design data translation is left up to the user – Changes to the design resulting from simulation is manual confidential § Use Time Domain simulation 40 – Power delivery system impedance is frequencydependent! – With only time domain simulation, it is like searching for needle in a haystack § Over design - add more de-coupling capacitors than necessary

The Cadence approach § Allow users to determine the needs of the power delivery system confidential – Target impedance – Decoupling capacitor requirements 41 § Provide frequency domain analysis to find problem areas § Provide an integrated PCB design editor to optimize capacitor placement Develop reliable power delivery sys while shortening design cycle time

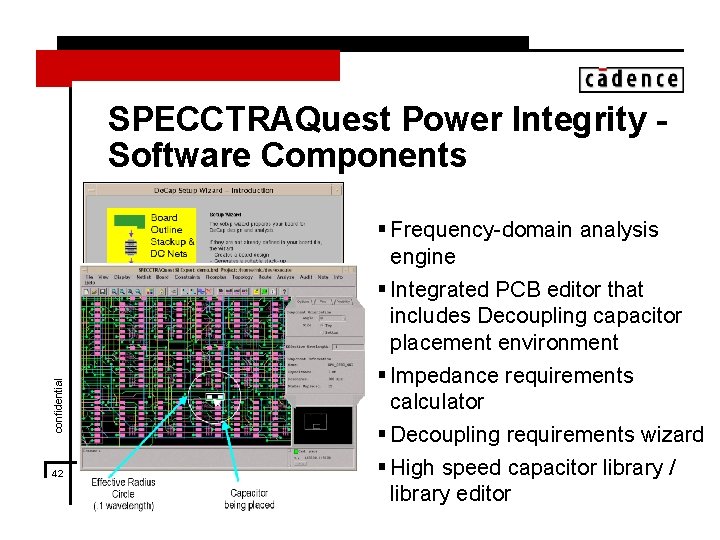

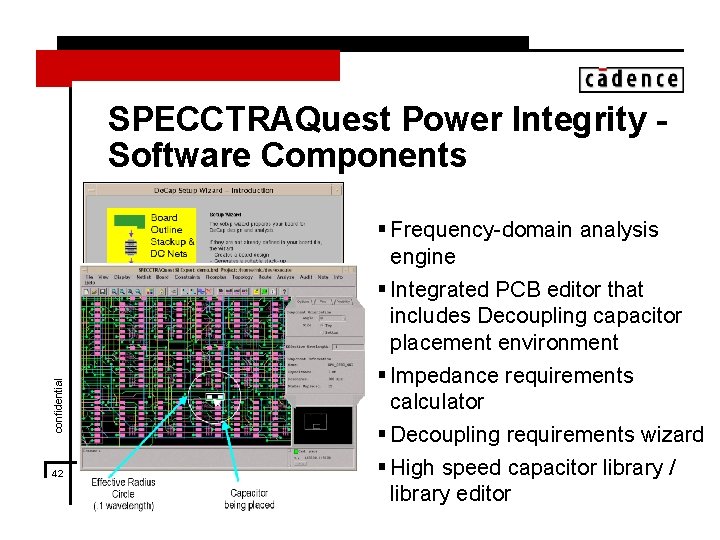

confidential SPECCTRAQuest Power Integrity Software Components 42 § Frequency-domain analysis engine § Integrated PCB editor that includes Decoupling capacitor placement environment § Impedance requirements calculator § Decoupling requirements wizard § High speed capacitor library / library editor

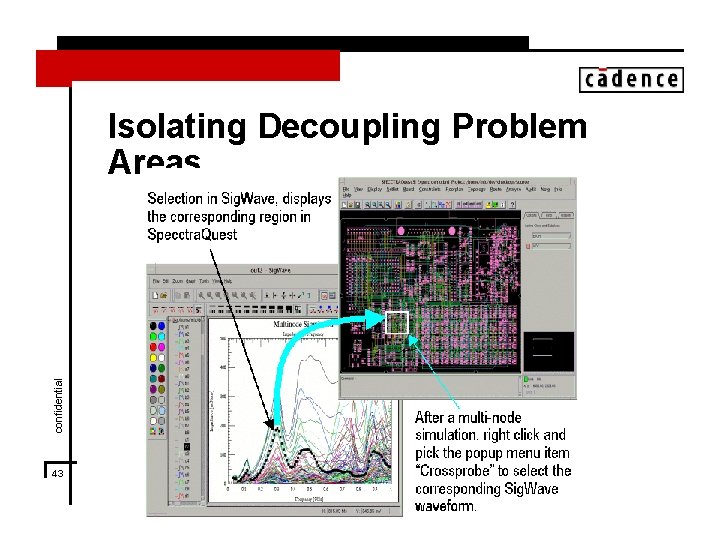

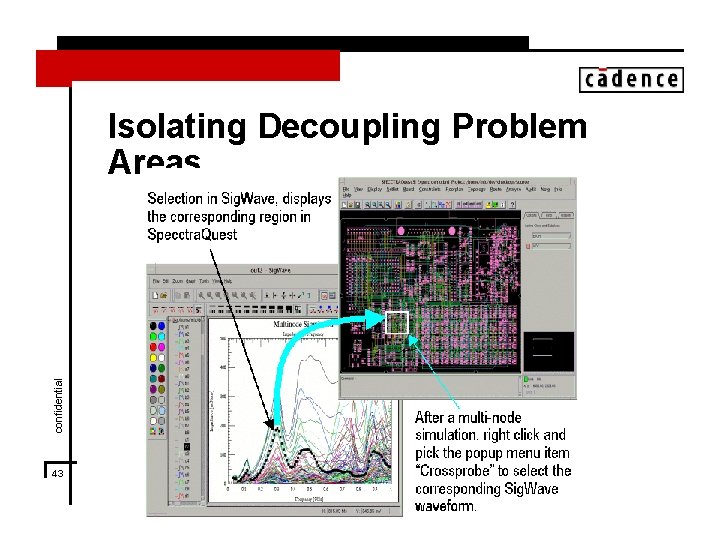

confidential Isolating Decoupling Problem Areas 43

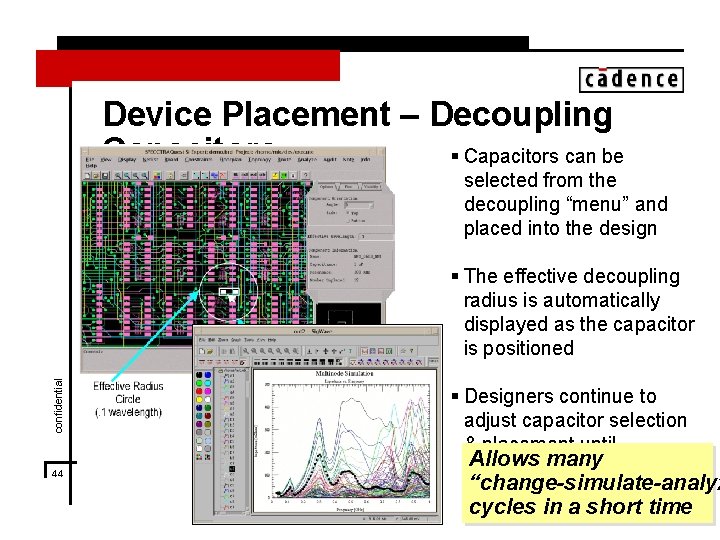

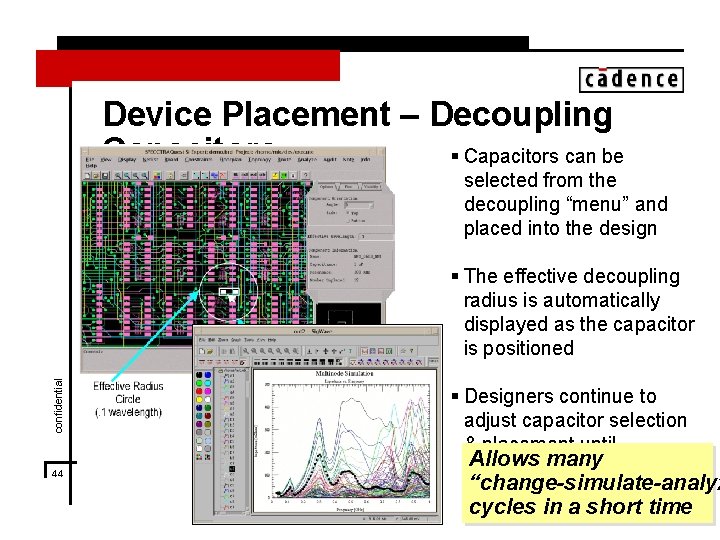

Device Placement – Decoupling Capacitors § Capacitors can be selected from the decoupling “menu” and placed into the design confidential § The effective decoupling radius is automatically displayed as the capacitor is positioned 44 § Designers continue to adjust capacitor selection & placement until Allows many performance of the PDS is “change-simulate-analyz acceptable cycles in a short time

Release § Available with PSD release version 14. 1 – Scheduled for late Q 2, 2001 § First release available on Sun Solaris (7 / 8) only confidential – Other platforms to follow with next major release 45

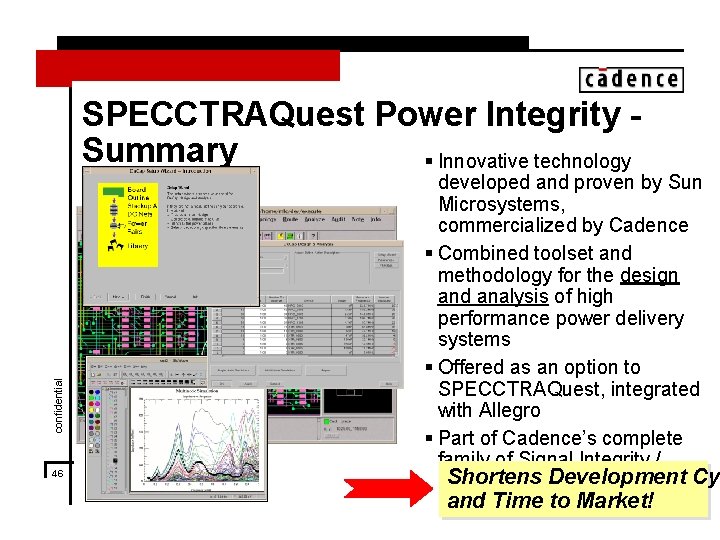

confidential SPECCTRAQuest Power Integrity Summary § Innovative technology 46 developed and proven by Sun Microsystems, commercialized by Cadence § Combined toolset and methodology for the design and analysis of high performance power delivery systems § Offered as an option to SPECCTRAQuest, integrated with Allegro § Part of Cadence’s complete family of Signal Integrity / Shortens Development Cy Power Delivery / EMI and Time to Market! solutions

Agenda confidential NOW 47 §What is High-Speed Design? §Ideal High-Speed Design Process §Introduction to SPECCTRAQuest Power Integrity §SPECCTRAQuest Demonstration

SPECCTRAQuest Demonstration (please ask questions as we proceed!) Cadence Design Systems, Inc.

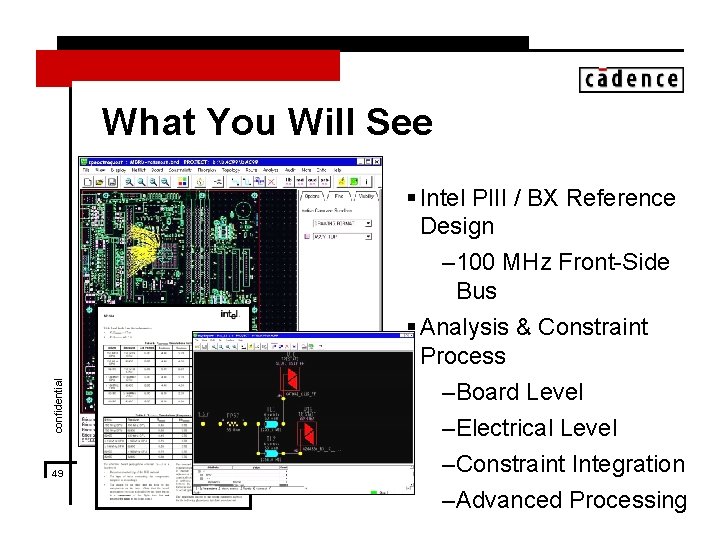

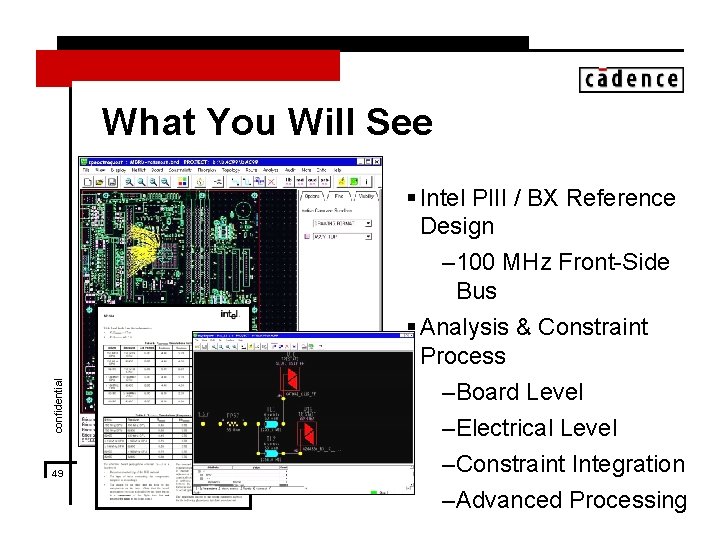

confidential What You Will See 49 § Intel PIII / BX Reference Design – 100 MHz Front-Side Bus § Analysis & Constraint Process –Board Level –Electrical Level –Constraint Integration –Advanced Processing

50 confidential

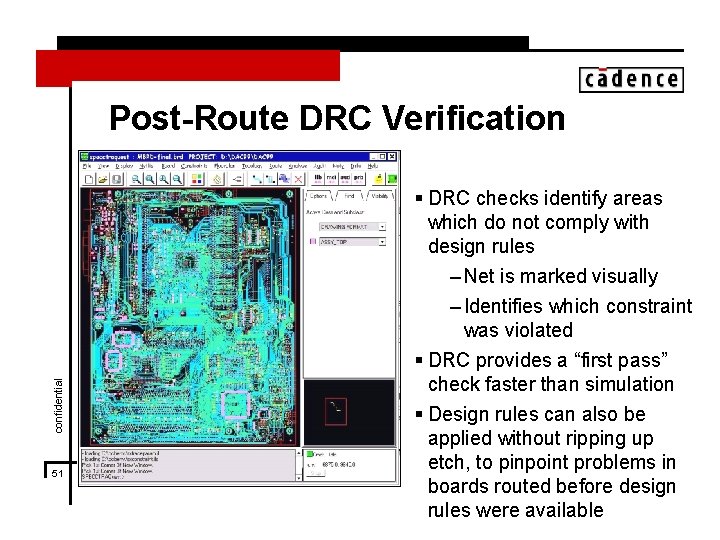

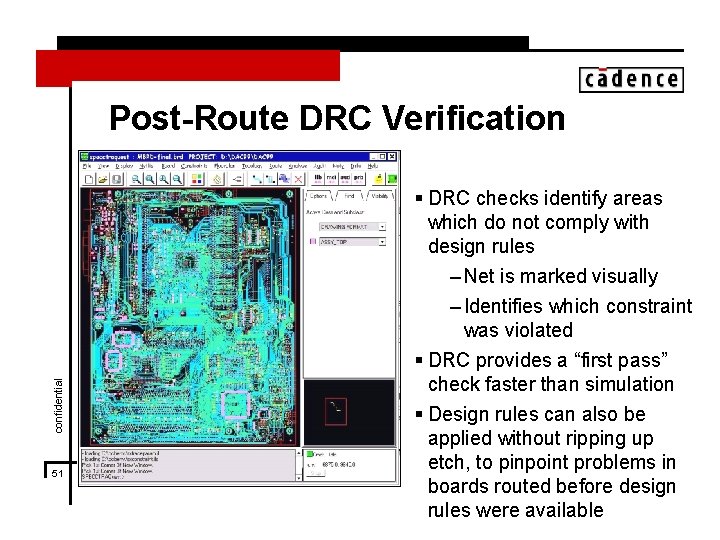

confidential Post-Route DRC Verification 51 § DRC checks identify areas which do not comply with design rules – Net is marked visually – Identifies which constraint was violated § DRC provides a “first pass” check faster than simulation § Design rules can also be applied without ripping up etch, to pinpoint problems in boards routed before design rules were available

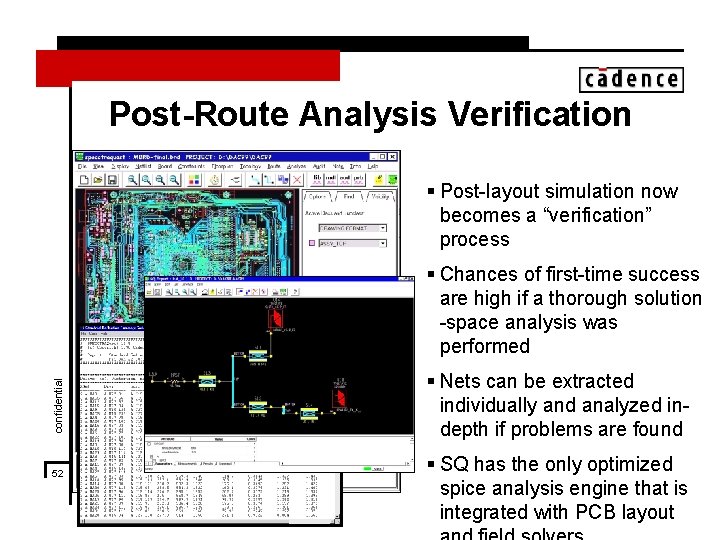

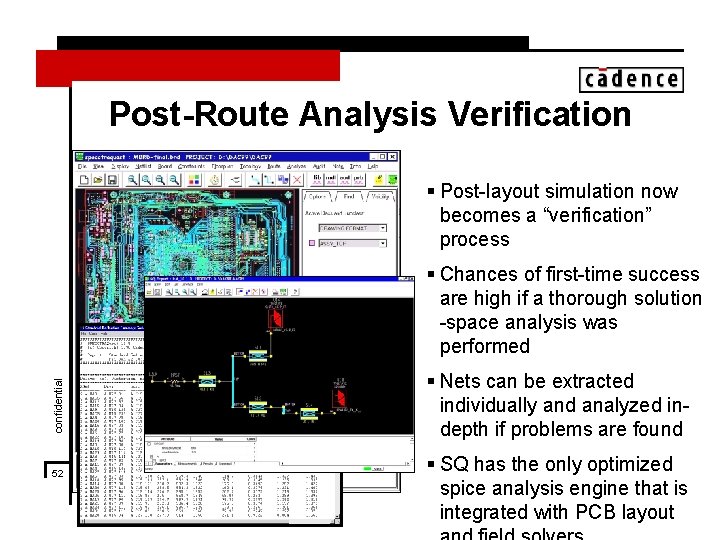

Post-Route Analysis Verification § Post-layout simulation now becomes a “verification” process confidential § Chances of first-time success are high if a thorough solution -space analysis was performed 52 § Nets can be extracted individually and analyzed indepth if problems are found § SQ has the only optimized spice analysis engine that is integrated with PCB layout

SPECCTRAQuest: Integrated Constraint & Analysis Analyze Model Developme nt & Verification Constraint Driven Layout Post Route Analysis Verification confidential Constrain Pre-Route Sol’n. Space Analysis Topology Entry & Floorplanni ng 53 Development Process Flow