CAD Algorithms and Tools Overview Introduction Boolean networks

CAD Algorithms and Tools

Overview • Introduction • Boolean networks • Transformations of Boolean networks • Optimization loop • Implementation • Conclusions • Software demo • Multi-level logic synthesis • SIS as a representative CAD tool • sweep, eliminate, fast_extract, resub, full_simplify • network/node data structure, packages, scripts

Introduction • Multi-level logic synthesis • Description, motivation, results • Logic synthesis methods • In the past, applied by hand; now, by the tools • CAD tools • Experimental, industrial

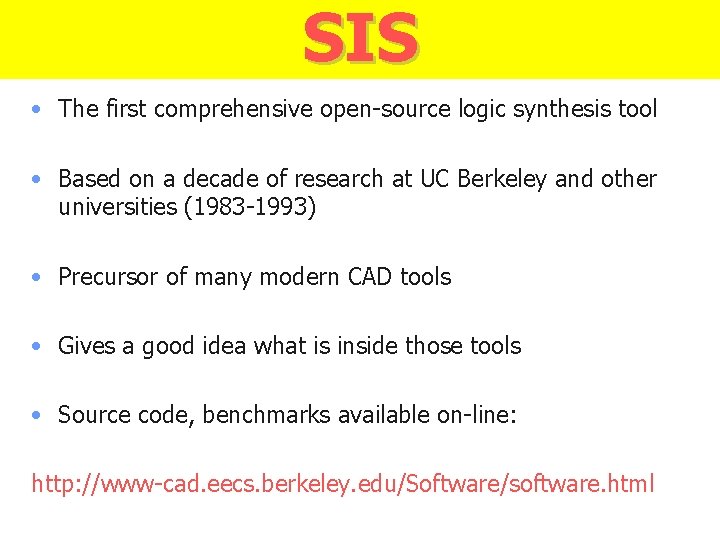

SIS • The first comprehensive open-source logic synthesis tool • Based on a decade of research at UC Berkeley and other universities (1983 -1993) • Precursor of many modern CAD tools • Gives a good idea what is inside those tools • Source code, benchmarks available on-line: http: //www-cad. eecs. berkeley. edu/Software/software. html

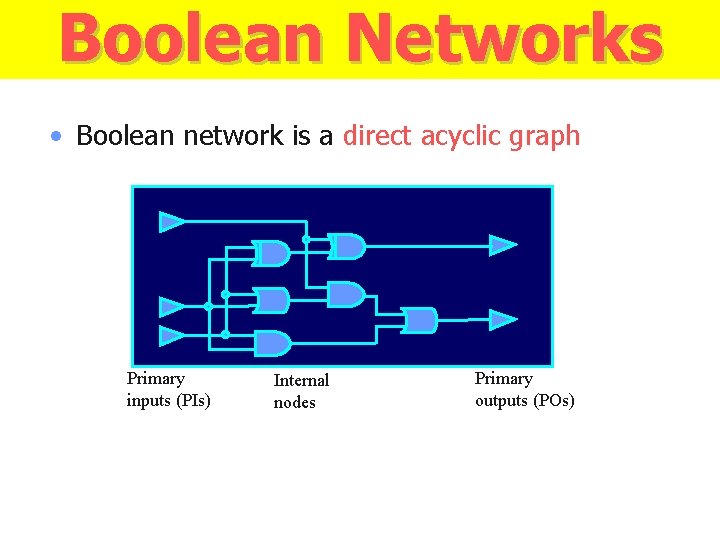

Boolean Networks • Boolean network is a direct acyclic graph Primary inputs (PIs) Internal nodes Primary outputs (POs)

Fanin/Fanout of a Node • Node has only one output. • Node can have any number of inputs (fanins) • and can be an input to any number of nodes (fanouts) Fanouts FO 1 FO 3 N Node Fanins FO 2 FI 1 FI 2 FI 3

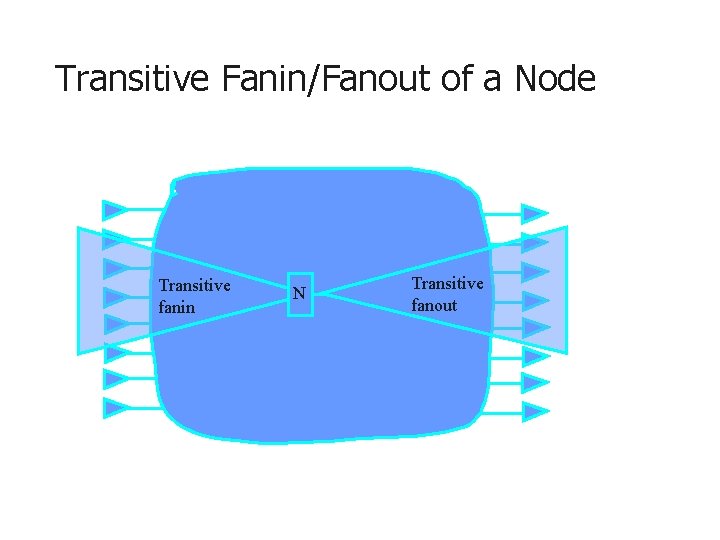

Transitive Fanin/Fanout of a Node Transitive fanin N Transitive fanout

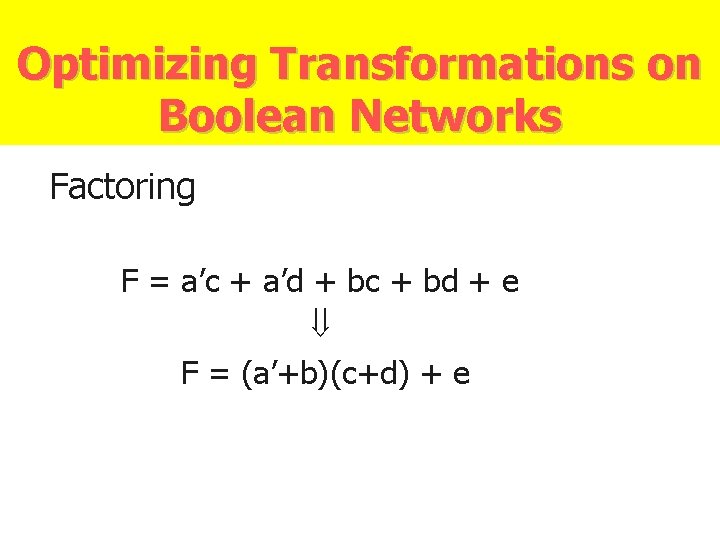

Optimizing Transformations on Boolean Networks Factoring F = a’c + a’d + bc + bd + e F = (a’+b)(c+d) + e

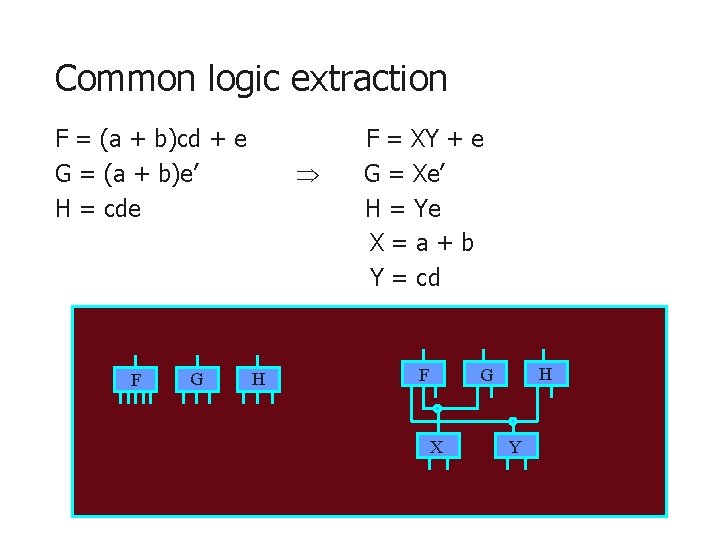

Common logic extraction F = (a + b)cd + e G = (a + b)e’ H = cde F G H F = XY + e G = Xe’ H = Ye X=a+b Y = cd F H G X Y

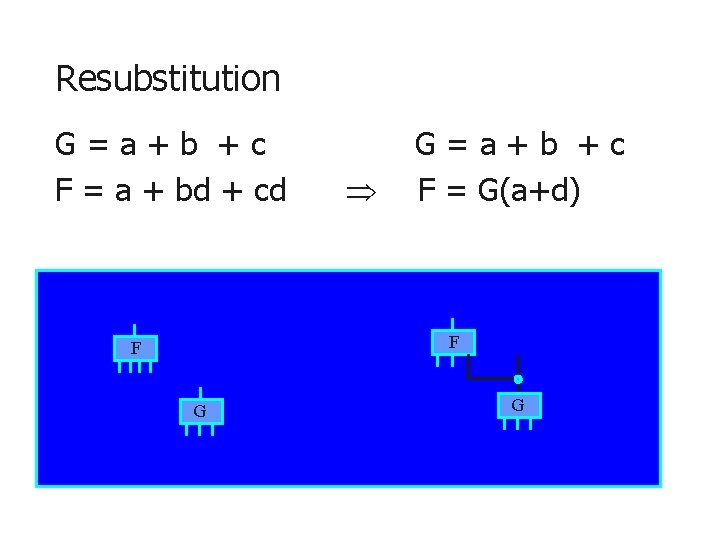

Resubstitution G=a+b +c F = a + bd + cd G=a+b +c F = G(a+d) F F G G

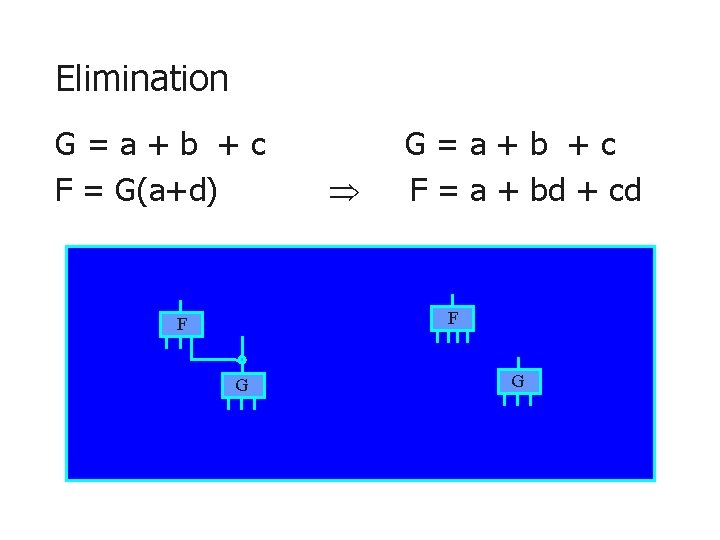

Elimination G=a+b +c F = G(a+d) G=a+b +c F = a + bd + cd F F G G

Sweep (1) Removes nodes that do not fanout (2) Eliminates constant nodes and singleinput nodes (buffers, inverters)

full_simplify • Simplifies each node in the network using don’t-cares

Don’t-cares for Nodes in the Network • External don’t-cares • Some input combinations never occur (unused codes, unreachable states) • Internal don’t-cares • Satisfiability don’t-cares • Some input combinations never occur at a node • Observability don’t-cares • Under some input combinations, the value produced at the output of the node does not matter

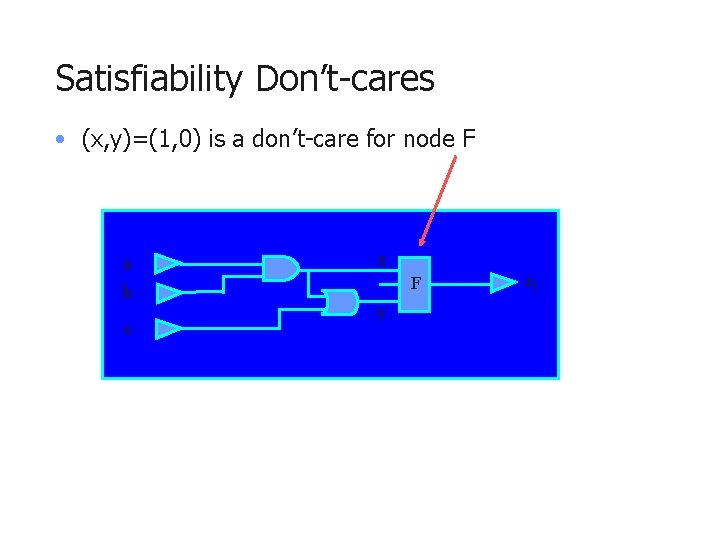

Satisfiability Don’t-cares • (x, y)=(1, 0) is a don’t-care for node F a b c x F y z 1

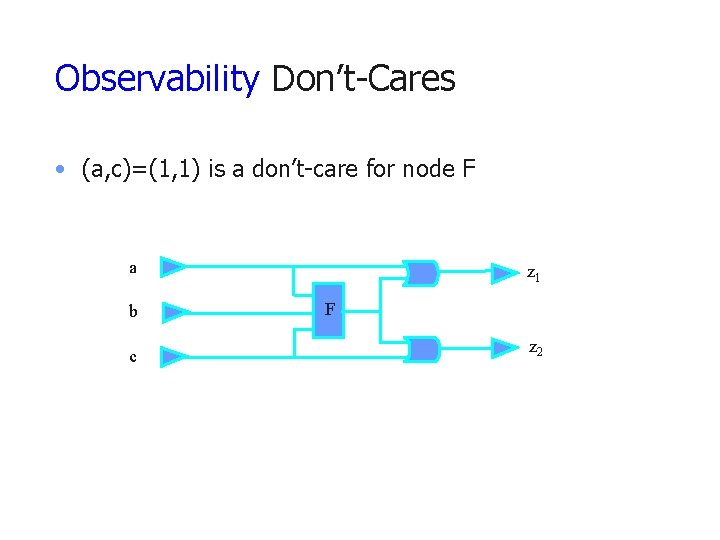

Observability Don’t-Cares • (a, c)=(1, 1) is a don’t-care for node F a b c z 1 F z 2

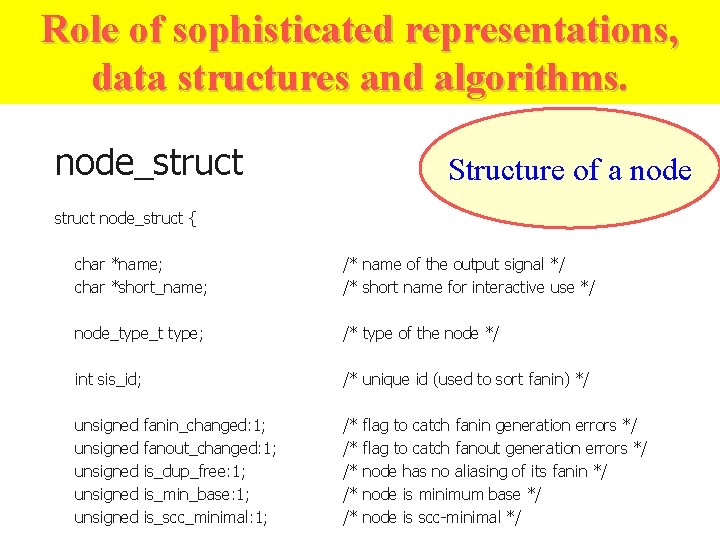

Role of sophisticated representations, data structures and algorithms. node_struct Structure of a node struct node_struct { char *name; char *short_name; /* name of the output signal */ /* short name for interactive use */ node_type_t type; /* type of the node */ int sis_id; /* unique id (used to sort fanin) */ unsigned unsigned fanin_changed: 1; fanout_changed: 1; is_dup_free: 1; is_min_base: 1; is_scc_minimal: 1; /* /* /* flag to catch fanin generation errors */ flag to catch fanout generation errors */ node has no aliasing of its fanin */ node is minimum base */ node is scc-minimal */

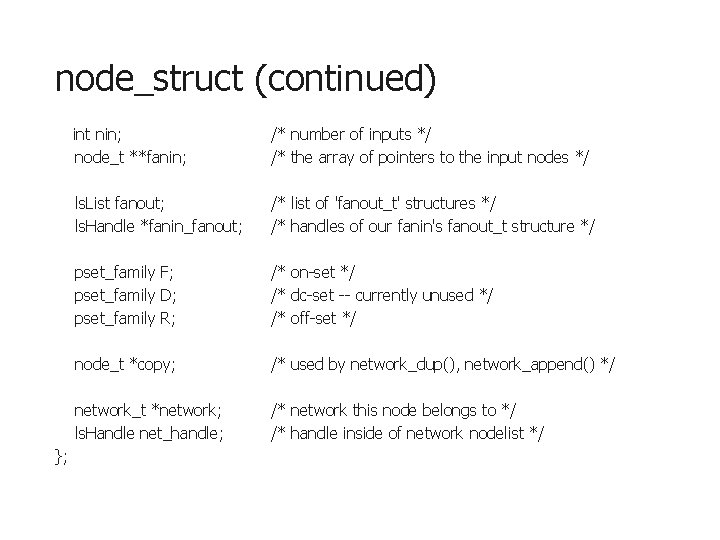

node_struct (continued) }; int nin; node_t **fanin; /* number of inputs */ /* the array of pointers to the input nodes */ ls. List fanout; ls. Handle *fanin_fanout; /* list of 'fanout_t' structures */ /* handles of our fanin's fanout_t structure */ pset_family F; pset_family D; pset_family R; /* on-set */ /* dc-set -- currently unused */ /* off-set */ node_t *copy; /* used by network_dup(), network_append() */ network_t *network; ls. Handle net_handle; /* network this node belongs to */ /* handle inside of network nodelist */

Structure of a network_struct { char *net_name; st_table *name_table; st_table *short_name_table; }; /* the name of the network */ /* table to hash names into node pointers */ ls. List nodes; ls. List pi; ls. List po; network_t *dc_network; /* /* list of all nodes */ list of just primary inputs */ list of just primary outputs */ external don't care network */ st_table *latch_table; ls. List latch; graph_t *stg; char *clock; /* /* table to hash names into latch pointers */ the linked list of latches */ state transition graph */ the clock */ char *default_delay; astg_t *astg; /* stores default delay info */ /* asynchronous signal transition graph */

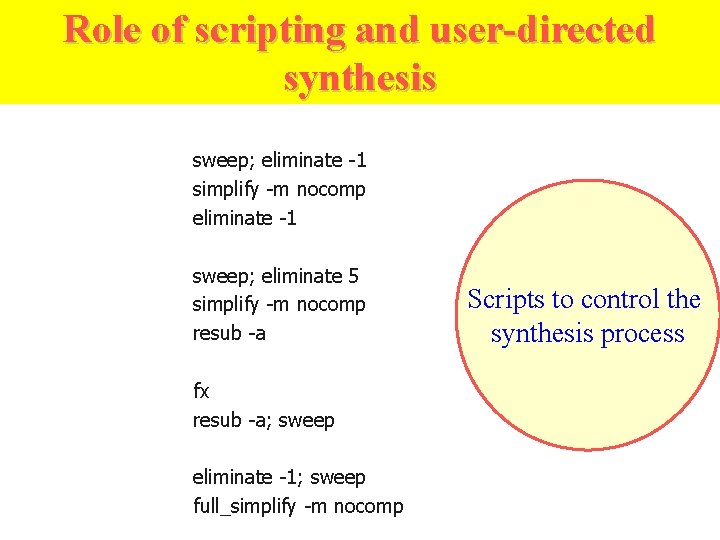

Role of scripting and user-directed script. rugged synthesis sweep; eliminate -1 simplify -m nocomp eliminate -1 sweep; eliminate 5 simplify -m nocomp resub -a fx resub -a; sweep eliminate -1; sweep full_simplify -m nocomp Scripts to control the synthesis process

What’s next? • Multi-valued logic optimization – New CAD tool: MVSIS • Reversible logic synthesis • Quantum, DNA-based, etc

full_simplify SIS vs. MVSIS

Conclusions • Reviewed multi-level logic optimization • Introduced Boolean networks • Considered typical operations • Looked into the implementation of SIS

Problems for students • What are BDDs and how are they used. • Shannon expansion and its role in trees and diagrams • Boolean networks • Operations on Boolean Networks. • Various types of don’t cares and their use • SIS system in practice.

Sources Alan Mishchenko Electrical and Computer Engineering Portland State University

- Slides: 25