Ca RIBOu V 1 Status Update H Chen

Ca. RIBOu V 1 Status Update H. Chen, Kai Chen, H. Liu, W. Wu 04/06/2016

Outline Ca. R Board V 1. 0 Status FEI 4 Board V 1. 0 Design Review Question List 2

Outline Ca. R Board V 1. 0 Status FEI 4 Board V 1. 0 Design Review Question List 3

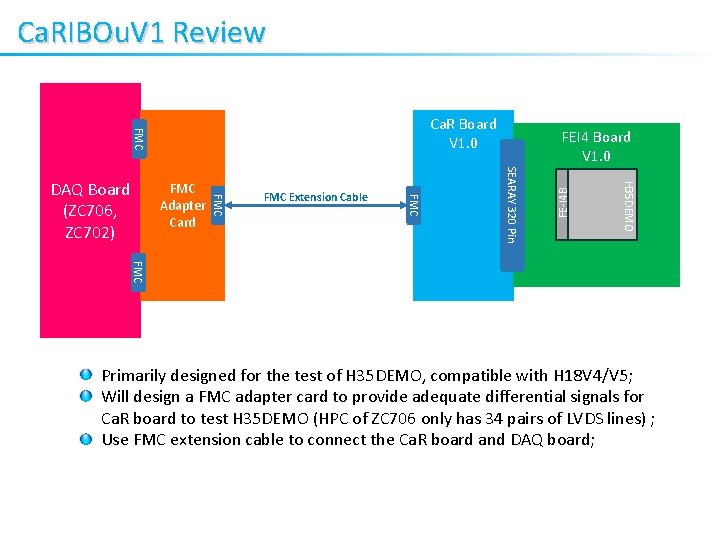

Ca. RIBOu. V 1 Review H 35 DEMO SEARAY 320 Pin FMC Extension Cable FMC Adapter Card FMC DAQ Board (ZC 706, ZC 702) FEI 4 Board V 1. 0 FE-I 4 B FMC Ca. R Board V 1. 0 FMC Primarily designed for the test of H 35 DEMO, compatible with H 18 V 4/V 5; Will design a FMC adapter card to provide adequate differential signals for Ca. R board to test H 35 DEMO (HPC of ZC 706 only has 34 pairs of LVDS lines) ; Use FMC extension cable to connect the Ca. R board and DAQ board;

Ca. R Board V 1. 0 - Specifications FMC mezzanine One FMC HPC Connector Chip Board Connector Samtec SEARAY 320 Pin 8 x Adjustable Power Supplies @ 3 A 32 x Ajustable bias voltages (0 ~ 4 V) 8 x Current sources, -100 u. A to 100 u. A Ajustable (Timepix) 1 x 16 channel/12 bit/80 MHz ADC 1 x 8 channel I 2 C interface ADC, 0 ~ 4 V input (Timepix) 8 x CMOS Inputs (1. 8 V, 2. 5 V, 3. 3 V Configurable) 16 x CMOS Outputs (1. 8 V, 2. 5 V, 3. 3 V Configurable) TLU Input 17 x LVDS Pairs 4 x Injection Pulser 8 x Duplex transceiver interface (Timepix) I 2 C Bus Jitter Cleaner SI 5345 for clock distribution Input: TLU, FMC, EXT; Output: 2 x GBT_CLK(FMC), 2 x Chip Board Ref CLK (SEAF), 1 x ADC CLK; 0 -delay mode;

Ca. R Board V 1. 0 – Power Distribution #1 Larger output current capability: 8 LDO rails share 12 A; Limited radiation/magnetic field tolerance; 6

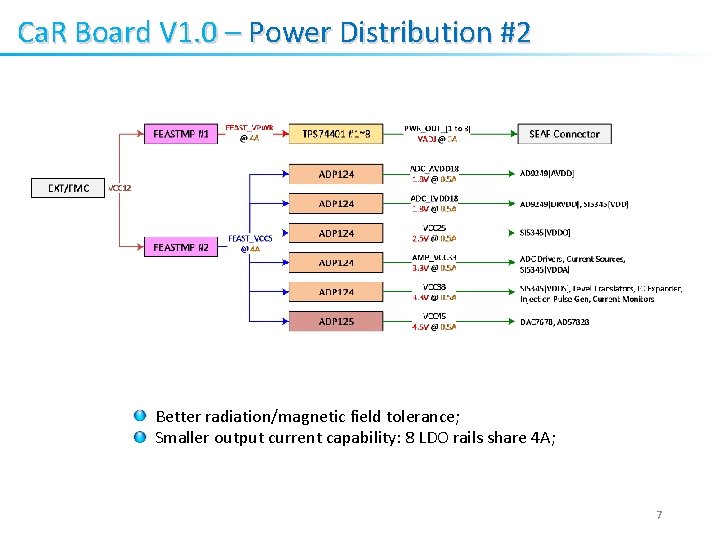

Ca. R Board V 1. 0 – Power Distribution #2 Better radiation/magnetic field tolerance; Smaller output current capability: 8 LDO rails share 4 A; 7

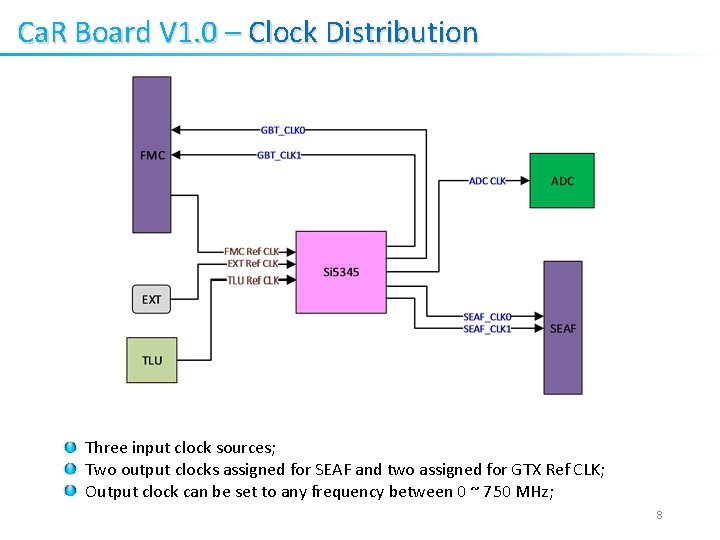

Ca. R Board V 1. 0 – Clock Distribution Three input clock sources; Two output clocks assigned for SEAF and two assigned for GTX Ref CLK; Output clock can be set to any frequency between 0 ~ 750 MHz; 8

Ca. R Board V 1. 0 – FMC Mapping

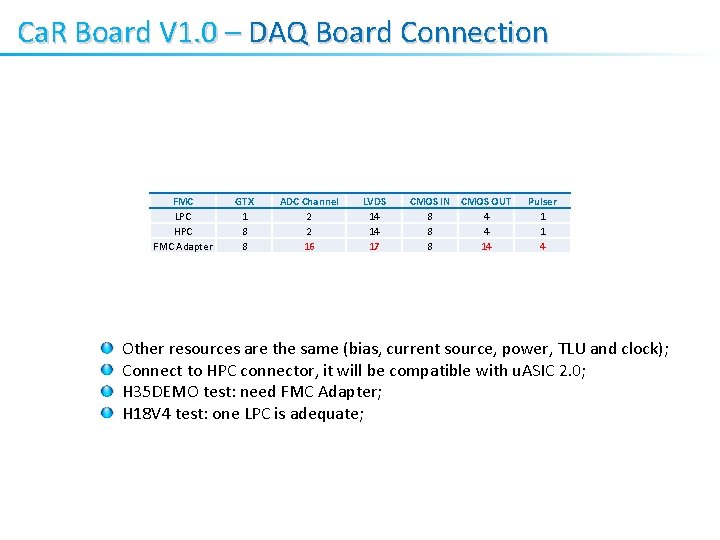

Ca. R Board V 1. 0 – DAQ Board Connection FMC LPC HPC FMC Adapter GTX 1 8 8 ADC Channel 2 2 16 LVDS 14 14 17 CMOS IN CMOS OUT 8 4 8 14 Pulser 1 1 4 Other resources are the same (bias, current source, power, TLU and clock); Connect to HPC connector, it will be compatible with u. ASIC 2. 0; H 35 DEMO test: need FMC Adapter; H 18 V 4 test: one LPC is adequate;

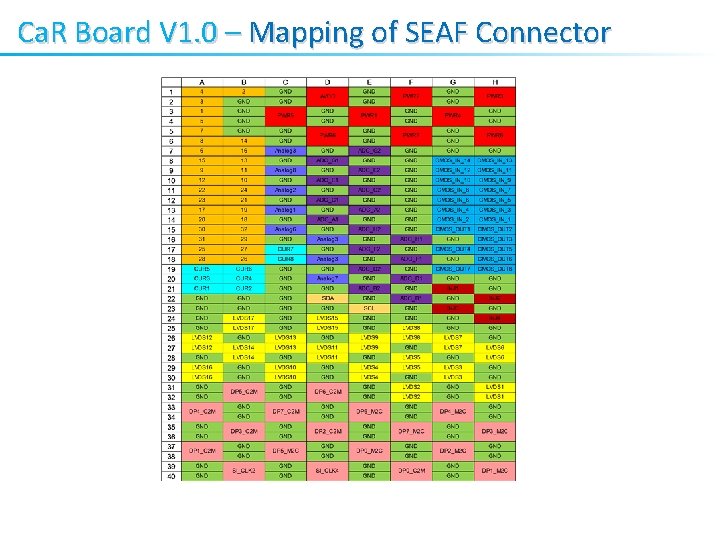

Ca. R Board V 1. 0 – Mapping of SEAF Connector

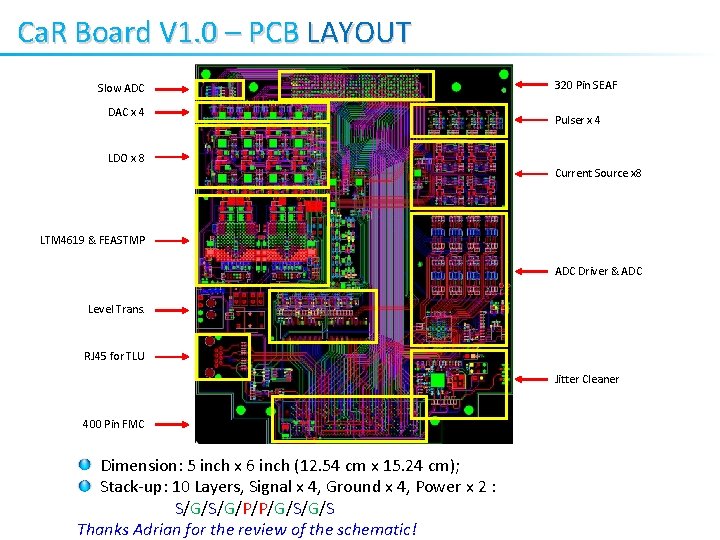

Ca. R Board V 1. 0 – PCB LAYOUT Slow ADC DAC x 4 320 Pin SEAF Pulser x 4 LDO x 8 Current Source x 8 LTM 4619 & FEASTMP ADC Driver & ADC Level Trans. RJ 45 for TLU Jitter Cleaner 400 Pin FMC Dimension: 5 inch x 6 inch (12. 54 cm x 15. 24 cm); Stack-up: 10 Layers, Signal x 4, Ground x 4, Power x 2 : S/G/P/P/G/S Thanks Adrian for the review of the schematic!

Outline Ca. R Board V 1. 0 Status FEI 4 Board V 1. 0 Design Review Question List 13

FEI 4 Board V 1. 0 – Power Distribution H 35 DEMO and H 18 V 4 share four power rails; Each matrix can be powered separately (jumper resistor); 14

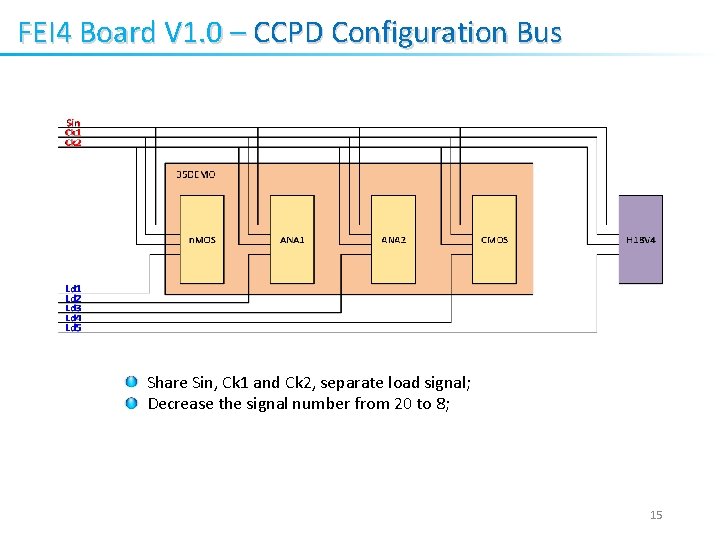

FEI 4 Board V 1. 0 – CCPD Configuration Bus Share Sin, Ck 1 and Ck 2, separate load signal; Decrease the signal number from 20 to 8; 15

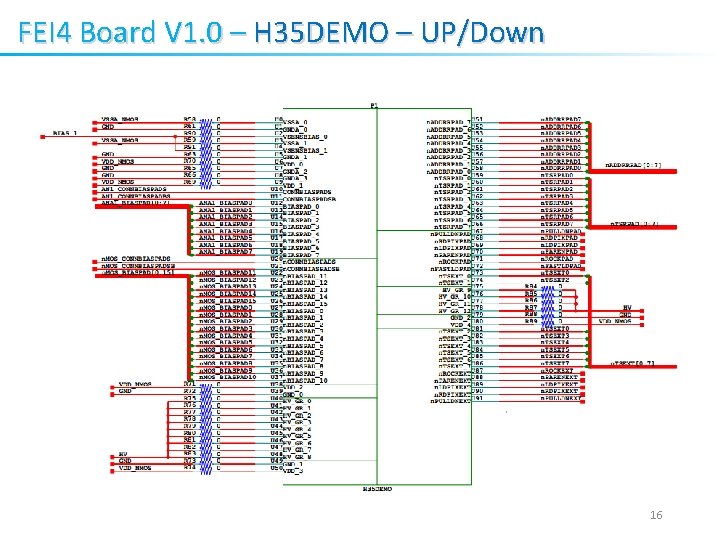

FEI 4 Board V 1. 0 – H 35 DEMO – UP/Down 16

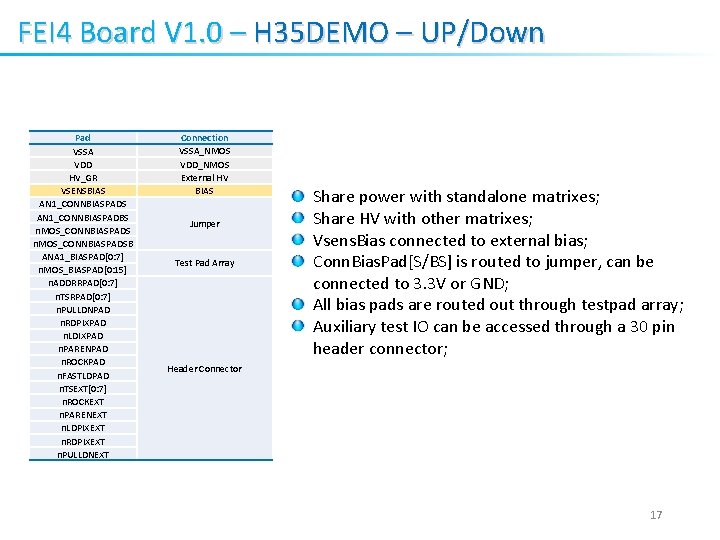

FEI 4 Board V 1. 0 – H 35 DEMO – UP/Down Pad VSSA VDD HV_GR VSENSBIAS AN 1_CONNBIASPADBS n. MOS_CONNBIASPADSB ANA 1_BIASPAD[0: 7] n. MOS_BIASPAD[0: 15] n. ADDRRPAD[0: 7] n. TSRPAD[0: 7] n. PULLDNPAD n. RDPIXPAD n. LDIXPAD n. PARENPAD n. ROCKPAD n. FASTLDPAD n. TSEXT[0: 7] n. ROCKEXT n. PARENEXT n. LDPIXEXT n. RDPIXEXT n. PULLDNEXT Connection VSSA_NMOS VDD_NMOS External HV BIAS Jumper Test Pad Array Share power with standalone matrixes; Share HV with other matrixes; Vsens. Bias connected to external bias; Conn. Bias. Pad[S/BS] is routed to jumper, can be connected to 3. 3 V or GND; All bias pads are routed out through testpad array; Auxiliary test IO can be accessed through a 30 pin header connector; Header Connector 17

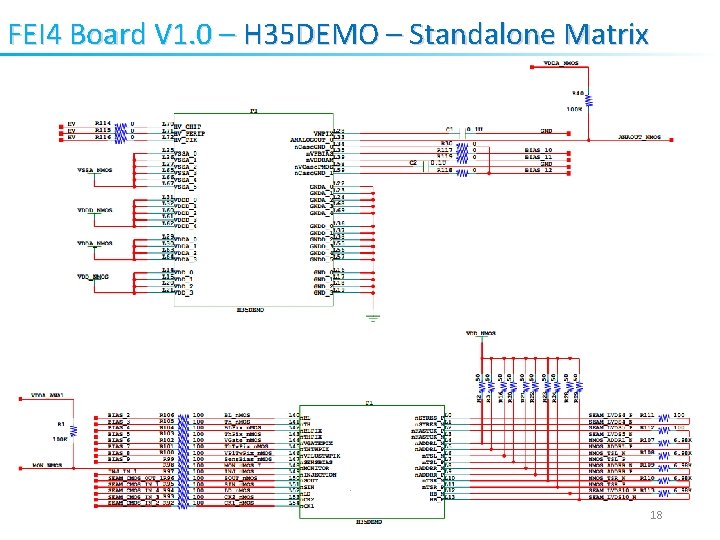

FEI 4 Board V 1. 0 – H 35 DEMO – Standalone Matrix 18

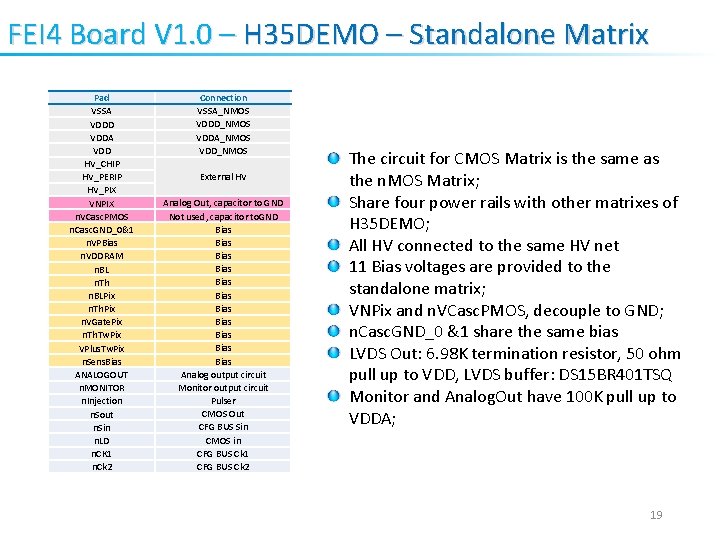

FEI 4 Board V 1. 0 – H 35 DEMO – Standalone Matrix Pad VSSA VDDD VDDA VDD HV_CHIP HV_PERIP HV_PIX VNPIX n. VCasc. PMOS n. Casc. GND_0&1 n. VPBias n. VDDRAM n. BL n. Th n. BLPix n. Th. Pix n. VGate. Pix n. Th. Tw. Pix VPlus. Tw. Pix n. Sens. Bias ANALOGOUT n. MONITOR n. Injection n. Sout n. Sin n. LD n. CK 1 n. Ck 2 Connection VSSA_NMOS VDDD_NMOS VDDA_NMOS VDD_NMOS External HV Analog Out, capacitor to GND Not used, capacitor to. GND Bias Bias Bias Analog output circuit Monitor output circuit Pulser CMOS Out CFG BUS Sin CMOS in CFG BUS Ck 1 CFG BUS Ck 2 The circuit for CMOS Matrix is the same as the n. MOS Matrix; Share four power rails with other matrixes of H 35 DEMO; All HV connected to the same HV net 11 Bias voltages are provided to the standalone matrix; VNPix and n. VCasc. PMOS, decouple to GND; n. Casc. GND_0 &1 share the same bias LVDS Out: 6. 98 K termination resistor, 50 ohm pull up to VDD, LVDS buffer: DS 15 BR 401 TSQ Monitor and Analog. Out have 100 K pull up to VDDA; 19

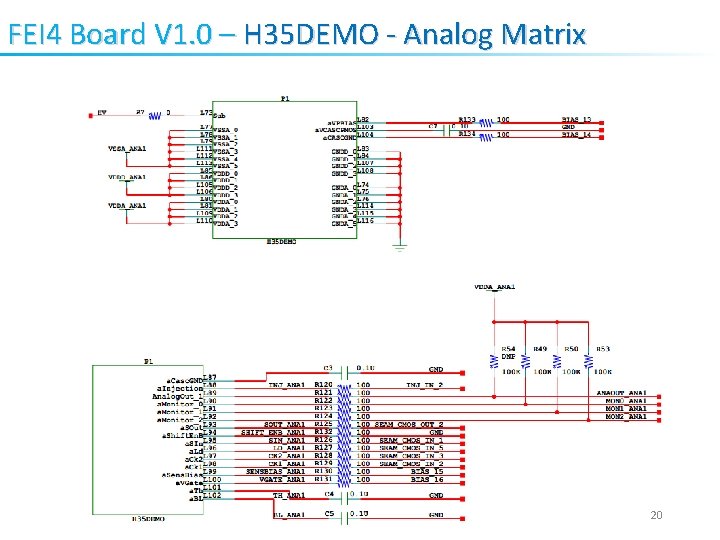

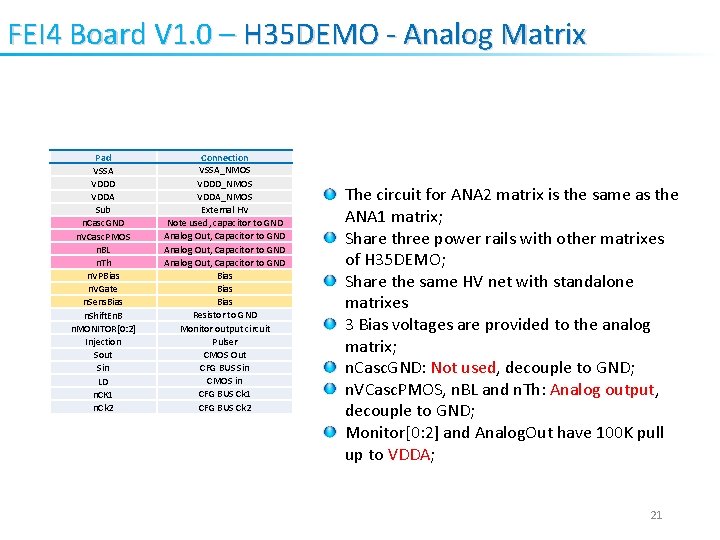

FEI 4 Board V 1. 0 – H 35 DEMO - Analog Matrix 20

FEI 4 Board V 1. 0 – H 35 DEMO - Analog Matrix Pad VSSA VDDD VDDA Sub n. Casc. GND n. VCasc. PMOS n. BL n. Th n. VPBias n. VGate n. Sens. Bias n. Shift. En. B n. MONITOR[0: 2] Injection Sout Sin LD n. CK 1 n. Ck 2 Connection VSSA_NMOS VDDD_NMOS VDDA_NMOS External HV Note used, capacitor to GND Analog Out, Capacitor to GND Bias Resistor to GND Monitor output circuit Pulser CMOS Out CFG BUS Sin CMOS in CFG BUS Ck 1 CFG BUS Ck 2 The circuit for ANA 2 matrix is the same as the ANA 1 matrix; Share three power rails with other matrixes of H 35 DEMO; Share the same HV net with standalone matrixes 3 Bias voltages are provided to the analog matrix; n. Casc. GND: Not used, decouple to GND; n. VCasc. PMOS, n. BL and n. Th: Analog output, decouple to GND; Monitor[0: 2] and Analog. Out have 100 K pull up to VDDA; 21

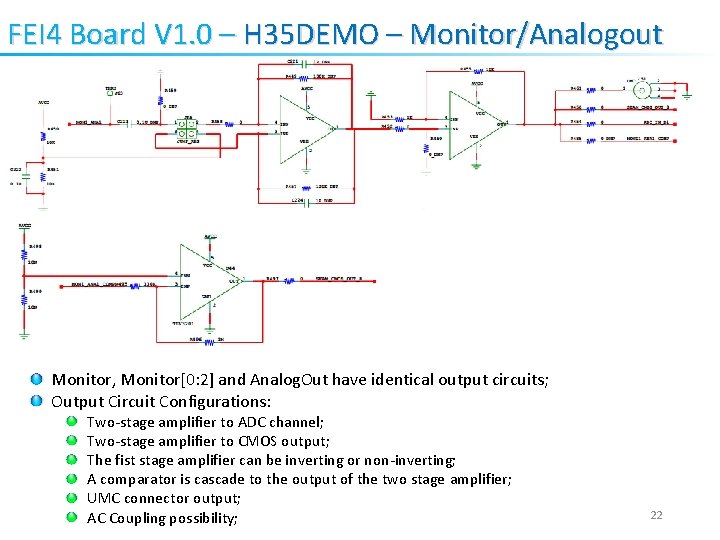

FEI 4 Board V 1. 0 – H 35 DEMO – Monitor/Analogout Monitor, Monitor[0: 2] and Analog. Out have identical output circuits; Output Circuit Configurations: Two-stage amplifier to ADC channel; Two-stage amplifier to CMOS output; The fist stage amplifier can be inverting or non-inverting; A comparator is cascade to the output of the two stage amplifier; UMC connector output; AC Coupling possibility; 22

FEI 4 Board V 1. 0 – H 35 DEMO – Test Structure Left Unconnected; 23

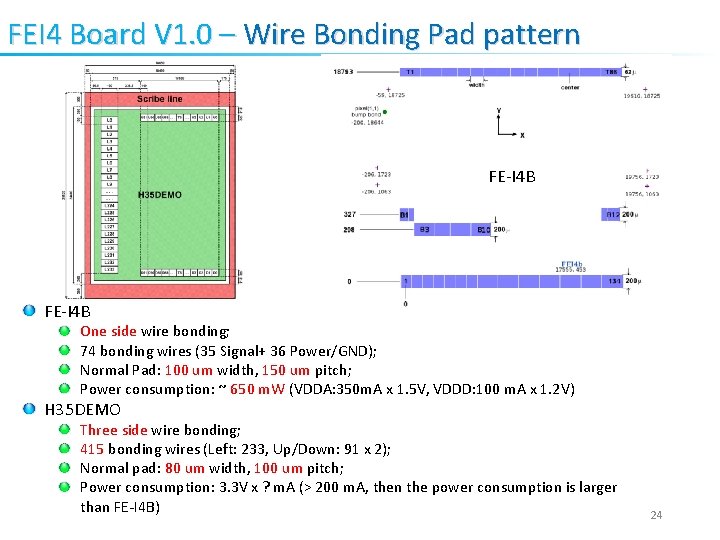

FEI 4 Board V 1. 0 – Wire Bonding Pad pattern FE-I 4 B One side wire bonding; 74 bonding wires (35 Signal+ 36 Power/GND); Normal Pad: 100 um width, 150 um pitch; Power consumption: ~ 650 m. W (VDDA: 350 m. A x 1. 5 V, VDDD: 100 m. A x 1. 2 V) H 35 DEMO Three side wire bonding; 415 bonding wires (Left: 233, Up/Down: 91 x 2); Normal pad: 80 um width, 100 um pitch; Power consumption: 3. 3 V x ? m. A (> 200 m. A, then the power consumption is larger than FE-I 4 B) 24

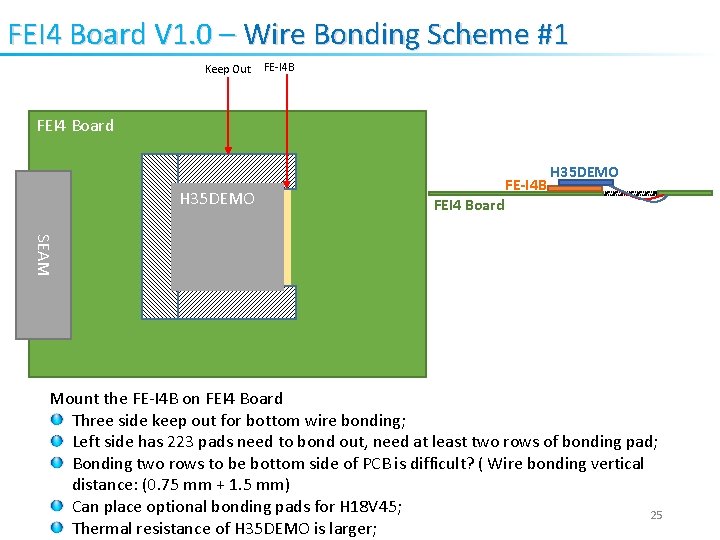

FEI 4 Board V 1. 0 – Wire Bonding Scheme #1 Keep Out FE-I 4 B FEI 4 Board H 35 DEMO FE-I 4 B H 35 DEMO FEI 4 Board SEAM FE-I 4 B Mount the FE-I 4 B on FEI 4 Board Three side keep out for bottom wire bonding; Left side has 223 pads need to bond out, need at least two rows of bonding pad; Bonding two rows to be bottom side of PCB is difficult? ( Wire bonding vertical distance: (0. 75 mm + 1. 5 mm) Can place optional bonding pads for H 18 V 45; 25 Thermal resistance of H 35 DEMO is larger;

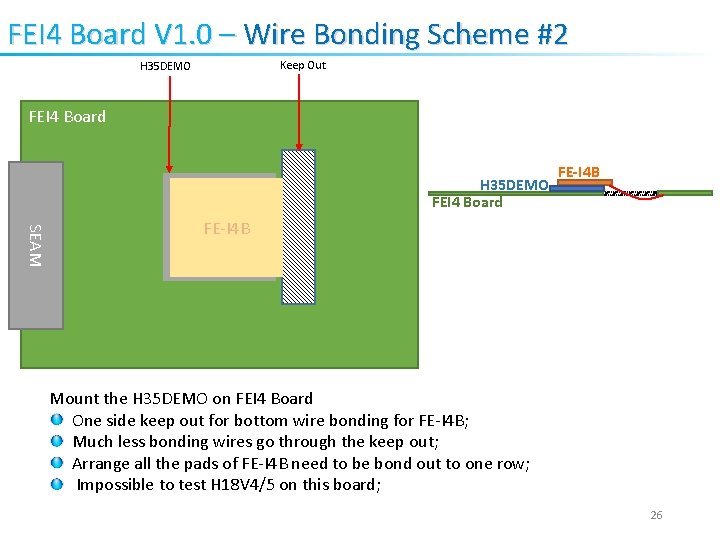

FEI 4 Board V 1. 0 – Wire Bonding Scheme #2 Keep Out H 35 DEMO FEI 4 Board H 35 DEMO H 35 DEMO FEI 4 Board FE-I 4 B SEAM FE-I 4 B Mount the H 35 DEMO on FEI 4 Board One side keep out for bottom wire bonding for FE-I 4 B; Much less bonding wires go through the keep out; Arrange all the pads of FE-I 4 B need to be bond out to one row; Impossible to test H 18 V 4/5 on this board; 26

Outline Ca. R Board V 1. 0 Status FEI 4 Board V 1. 0 Design Review Question List 27

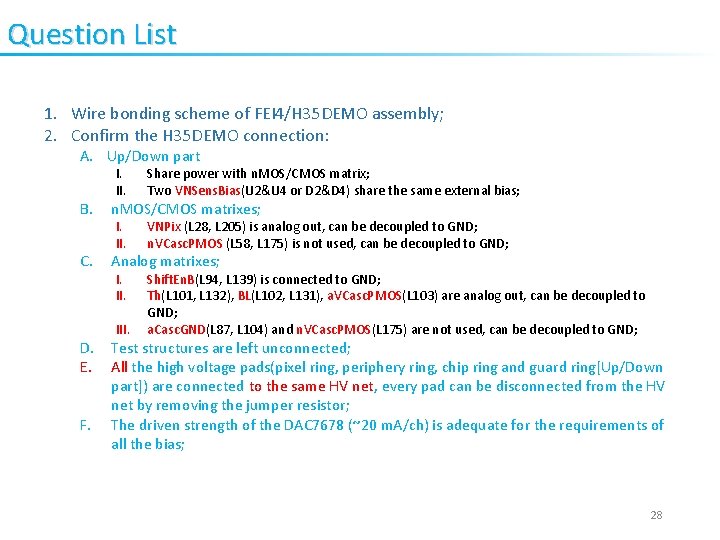

Question List 1. Wire bonding scheme of FEI 4/H 35 DEMO assembly; 2. Confirm the H 35 DEMO connection: A. Up/Down part I. II. Share power with n. MOS/CMOS matrix; Two VNSens. Bias(U 2&U 4 or D 2&D 4) share the same external bias; I. II. VNPix (L 28, L 205) is analog out, can be decoupled to GND; n. VCasc. PMOS (L 58, L 175) is not used, can be decoupled to GND; I. II. Shift. En. B(L 94, L 139) is connected to GND; Th(L 101, L 132), BL(L 102, L 131), a. VCasc. PMOS(L 103) are analog out, can be decoupled to GND; a. Casc. GND(L 87, L 104) and n. VCasc. PMOS(L 175) are not used, can be decoupled to GND; B. n. MOS/CMOS matrixes; C. Analog matrixes; D. E. F. III. Test structures are left unconnected; All the high voltage pads(pixel ring, periphery ring, chip ring and guard ring[Up/Down part]) are connected to the same HV net, every pad can be disconnected from the HV net by removing the jumper resistor; The driven strength of the DAC 7678 (~20 m. A/ch) is adequate for the requirements of all the bias; 28

Summary The layout of Ca. R board V 1. 0 is finished, will sent out for review this week; Schematic of the FEI 4 board V 1. 0 is finished and need to be cross checked with H 35 DEMO designer; Need to confirm the wire bonding scheme and H 35 DEMO connection ASAP; Schematic of the FMC Adapter board is finished; 29

Thank you!

- Slides: 30