C bus 31 0 32 32 A bus

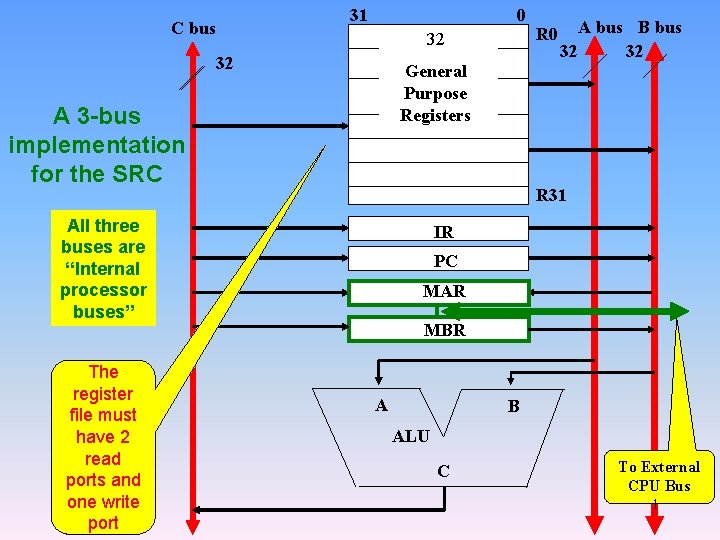

C bus 31 0 32 32 A bus B bus 32 32 General Purpose Registers A 3 -bus implementation for the SRC R 31 All three buses are “Internal processor buses” The register file must have 2 read ports and one write port R 0 IR PC MAR MBR A B ALU C To External CPU Bus 1

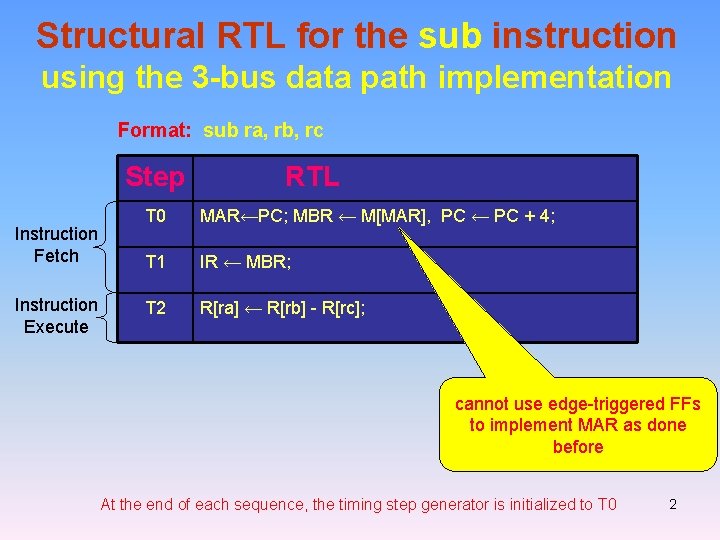

Structural RTL for the sub instruction using the 3 -bus data path implementation Format: sub ra, rb, rc Step Instruction Fetch Instruction Execute RTL T 0 MAR←PC; MBR ← M[MAR], PC ← PC + 4; T 1 IR ← MBR; T 2 R[ra] ← R[rb] - R[rc]; cannot use edge-triggered FFs to implement MAR as done before At the end of each sequence, the timing step generator is initialized to T 0 2

Review 3

CS 501 Advanced Computer Architecture Lecture 17 Dr. Noor Muhammad Sheikh 4

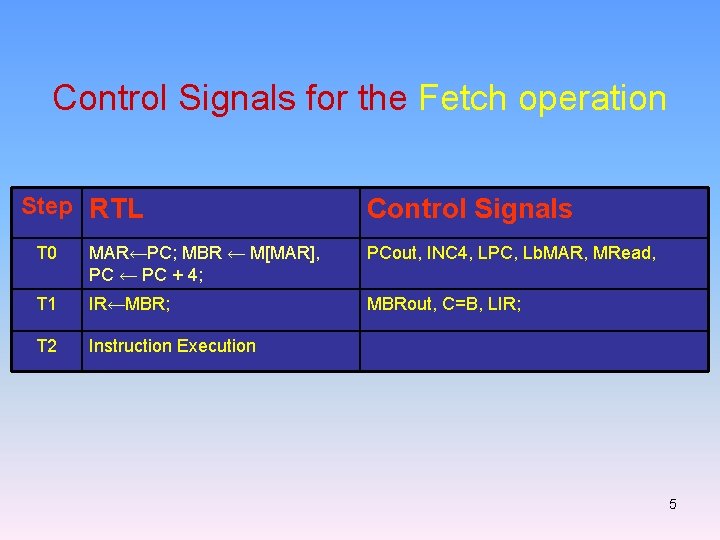

Control Signals for the Fetch operation Step RTL Control Signals T 0 MAR←PC; MBR ← M[MAR], PC ← PC + 4; PCout, INC 4, LPC, Lb. MAR, MRead, T 1 IR←MBR; MBRout, C=B, LIR; T 2 Instruction Execution 5

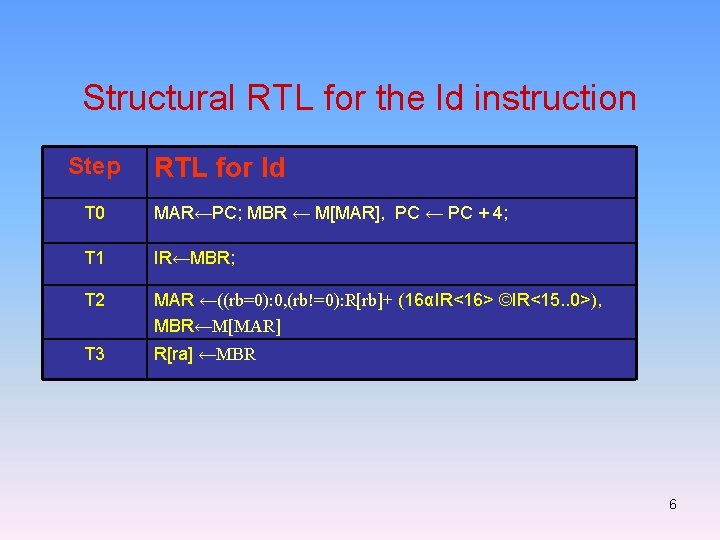

Structural RTL for the ld instruction Step RTL for ld T 0 MAR←PC; MBR ← M[MAR], PC ← PC + 4; T 1 IR←MBR; T 2 MAR ←((rb=0): 0, (rb!=0): R[rb]+ (16αIR<16> ©IR<15. . 0>), MBR←M[MAR] T 3 R[ra] ←MBR 6

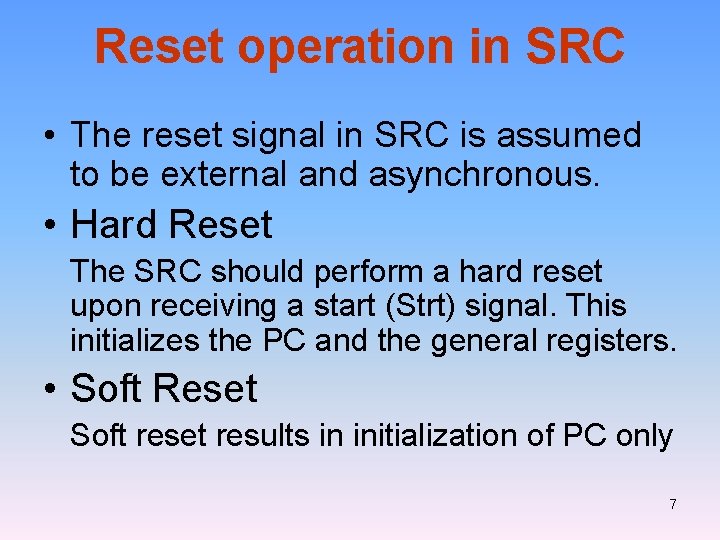

Reset operation in SRC • The reset signal in SRC is assumed to be external and asynchronous. • Hard Reset The SRC should perform a hard reset upon receiving a start (Strt) signal. This initializes the PC and the general registers. • Soft Reset Soft reset results in initialization of PC only 7

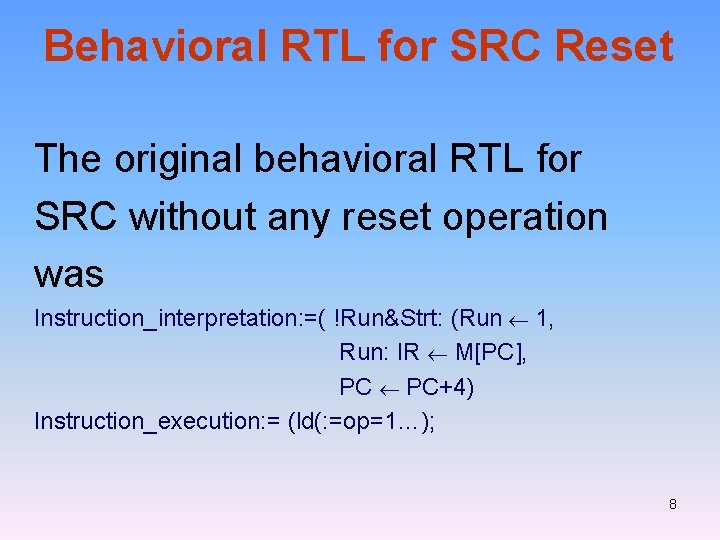

Behavioral RTL for SRC Reset The original behavioral RTL for SRC without any reset operation was Instruction_interpretation: =( !Run&Strt: (Run 1, Run: IR M[PC], PC PC+4) Instruction_execution: = (ld(: =op=1…); 8

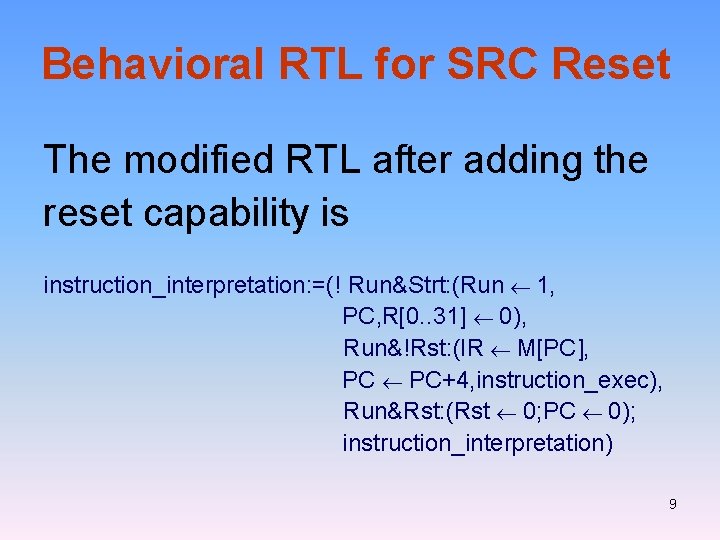

Behavioral RTL for SRC Reset The modified RTL after adding the reset capability is instruction_interpretation: =(! Run&Strt: (Run 1, PC, R[0. . 31] 0), Run&!Rst: (IR M[PC], PC PC+4, instruction_exec), Run&Rst: (Rst 0; PC 0); instruction_interpretation) 9

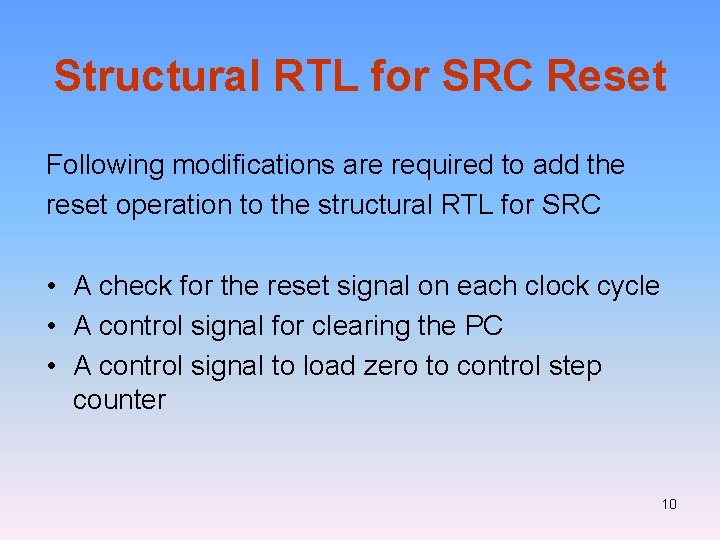

Structural RTL for SRC Reset Following modifications are required to add the reset operation to the structural RTL for SRC • A check for the reset signal on each clock cycle • A control signal for clearing the PC • A control signal to load zero to control step counter 10

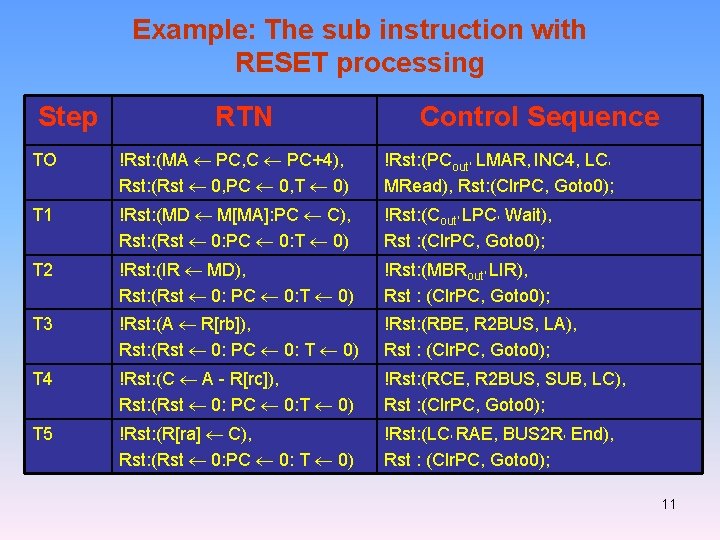

Example: The sub instruction with RESET processing Step RTN Control Sequence TO !Rst: (MA PC, C PC+4), Rst: (Rst 0, PC 0, T 0) !Rst: (PCout’ LMAR, INC 4, LC’ MRead), Rst: (Clr. PC, Goto 0); T 1 !Rst: (MD M[MA]: PC C), Rst: (Rst 0: PC 0: T 0) !Rst: (Cout’ LPC’ Wait), Rst : (Clr. PC, Goto 0); T 2 !Rst: (IR MD), Rst: (Rst 0: PC 0: T 0) !Rst: (MBRout’ LIR), Rst : (Clr. PC, Goto 0); T 3 !Rst: (A R[rb]), Rst: (Rst 0: PC 0: T 0) !Rst: (RBE, R 2 BUS, LA), Rst : (Clr. PC, Goto 0); T 4 !Rst: (C A - R[rc]), Rst: (Rst 0: PC 0: T 0) !Rst: (RCE, R 2 BUS, SUB, LC), Rst : (Clr. PC, Goto 0); T 5 !Rst: (R[ra] C), Rst: (Rst 0: PC 0: T 0) !Rst: (LC’ RAE, BUS 2 R’ End), Rst : (Clr. PC, Goto 0); 11

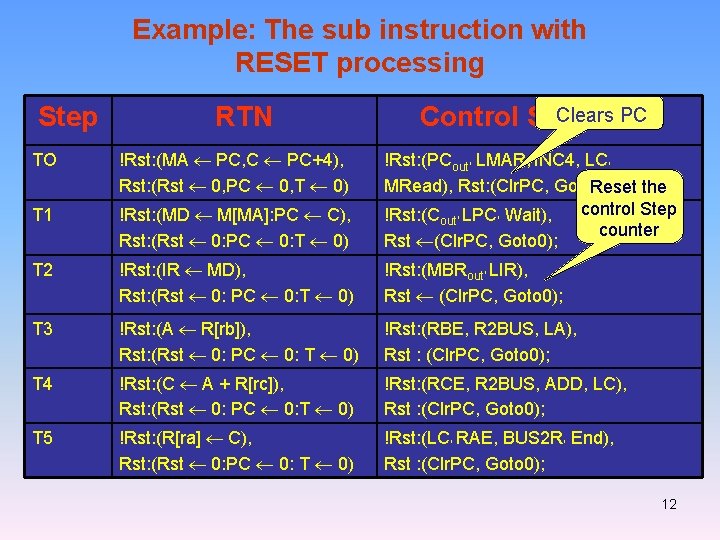

Example: The sub instruction with RESET processing Step RTN Clears PC Control Sequence TO !Rst: (MA PC, C PC+4), Rst: (Rst 0, PC 0, T 0) T 1 !Rst: (MD M[MA]: PC C), Rst: (Rst 0: PC 0: T 0) !Rst: (PCout’ LMAR, INC 4, LC’ MRead), Rst: (Clr. PC, Goto 0); Reset the control Step !Rst: (Cout’ LPC’ Wait), counter Rst (Clr. PC, Goto 0); T 2 !Rst: (IR MD), Rst: (Rst 0: PC 0: T 0) !Rst: (MBRout’ LIR), Rst (Clr. PC, Goto 0); T 3 !Rst: (A R[rb]), Rst: (Rst 0: PC 0: T 0) !Rst: (RBE, R 2 BUS, LA), Rst : (Clr. PC, Goto 0); T 4 !Rst: (C A + R[rc]), Rst: (Rst 0: PC 0: T 0) !Rst: (RCE, R 2 BUS, ADD, LC), Rst : (Clr. PC, Goto 0); T 5 !Rst: (R[ra] C), Rst: (Rst 0: PC 0: T 0) !Rst: (LC’ RAE, BUS 2 R’ End), Rst : (Clr. PC, Goto 0); 12

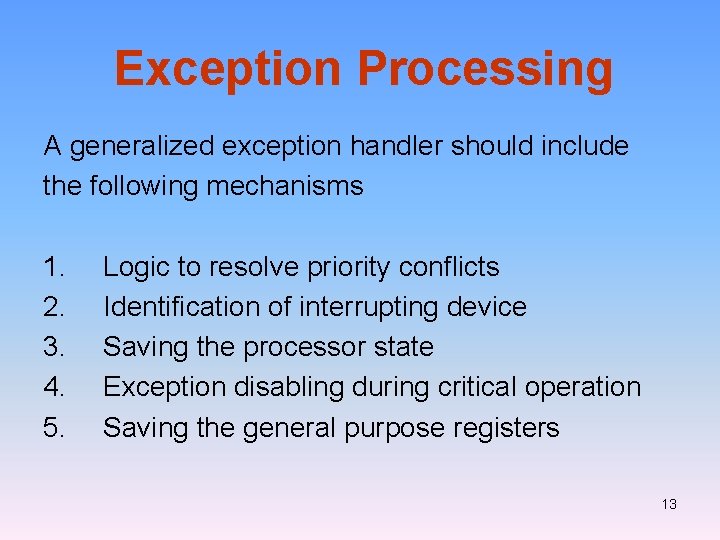

Exception Processing A generalized exception handler should include the following mechanisms 1. 2. 3. 4. 5. Logic to resolve priority conflicts Identification of interrupting device Saving the processor state Exception disabling during critical operation Saving the general purpose registers 13

Types of Exceptions • Reset Exception Reset operation is treated as an exception by some machines e. g. SPARC and MC 68000. • Machine Check This is an external exception caused by memory failure • Data Access Exception This exception is generated by memory management unit to protect against illegal accesses. • Instruction Access Exception Similar to data access exception • Alignment Exception Generated to block misaligned data access 14

Types of Exception • • • Program Exceptions Hardware Exceptions Trace and debugging Exceptions Nonmaskable Exceptions Interrupts (External Exceptions) 15

Exceptions 16

3 -Bus Implementation 17

CS 501 Advanced Computer Architecture 18

- Slides: 18