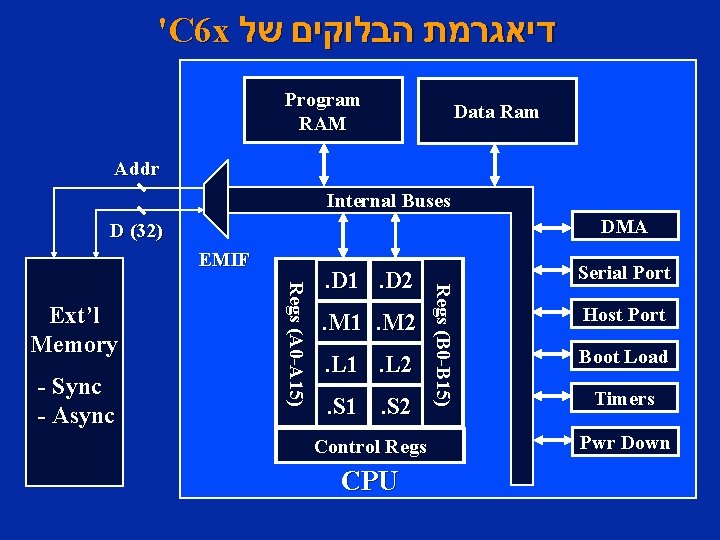

C 6 x Program RAM Data Ram Addr

- Slides: 22

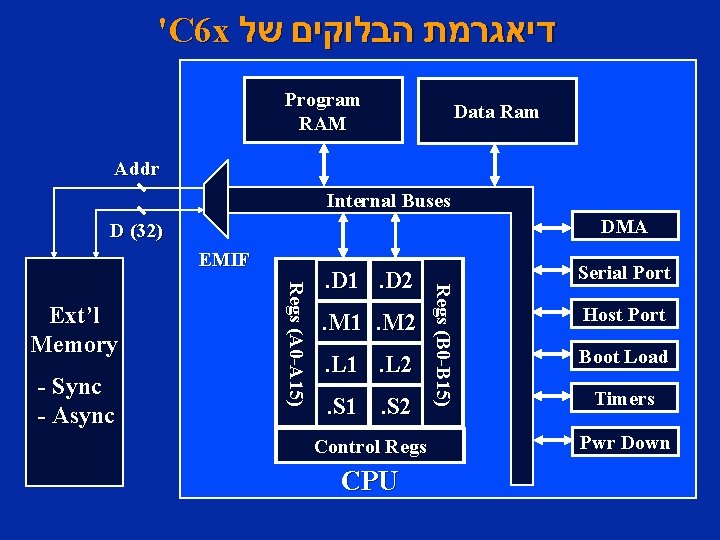

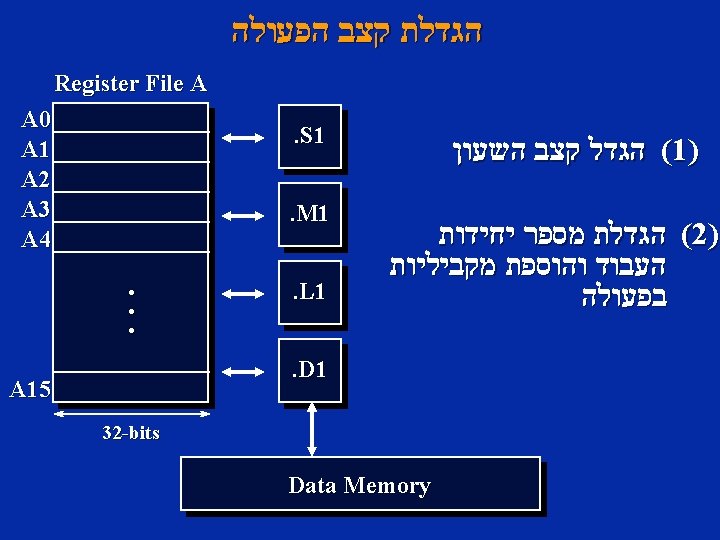

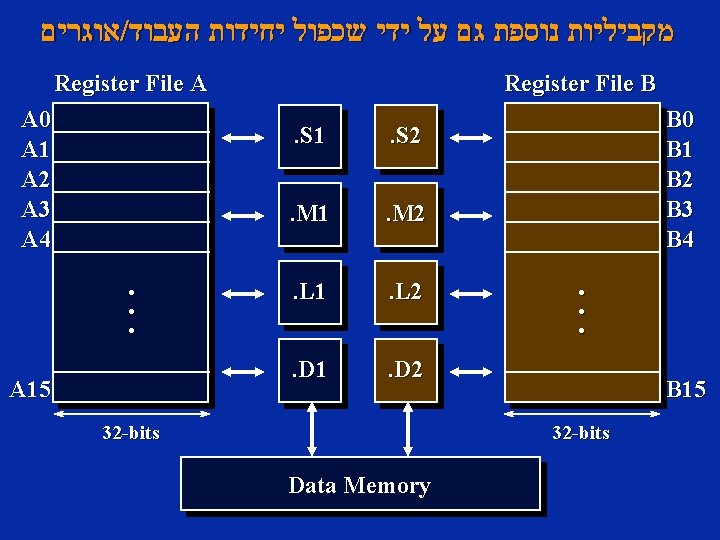

'C 6 x דיאגרמת הבלוקים של Program RAM Data Ram Addr Internal Buses DMA D (32) EMIF . M 1. M 2. L 1. L 2. S 1. S 2 Control Regs Serial Port Regs (B 0 -B 15) - Sync - Async Regs (A 0 -A 15) Ext’l Memory . D 1. D 2 Host Port Boot Load Timers Pwr Down CPU Chapter 2, Slide 3 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

'C 6 x דיאגרמת בלוקים מפורטת של Chapter 2, Slide 4 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

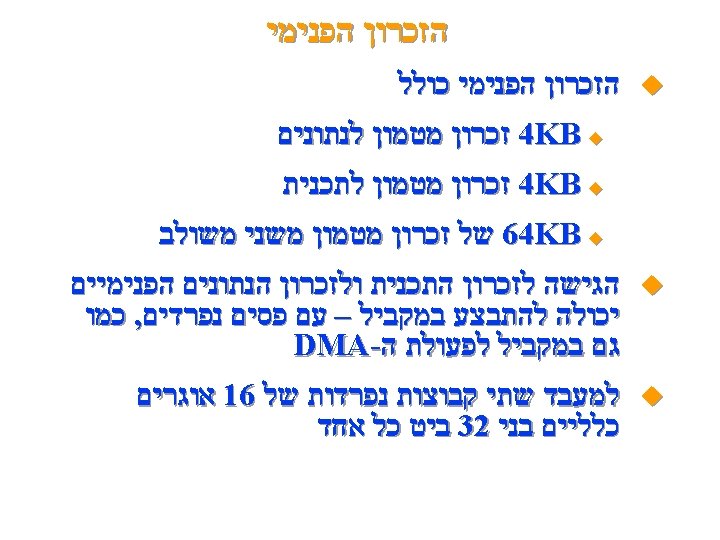

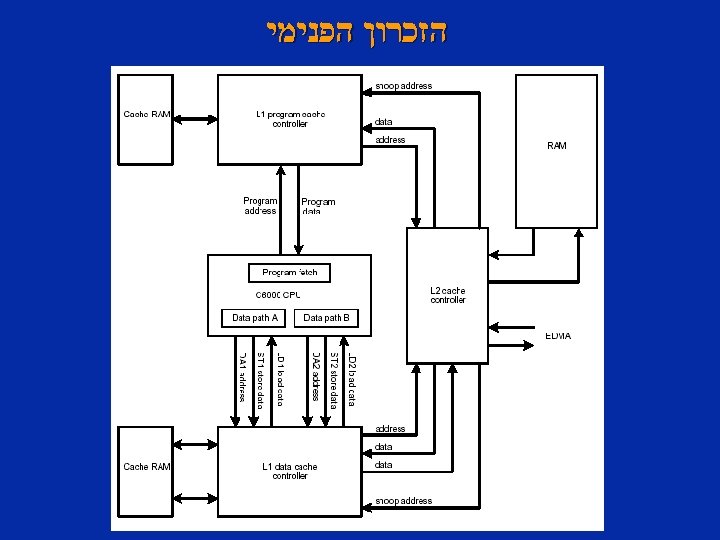

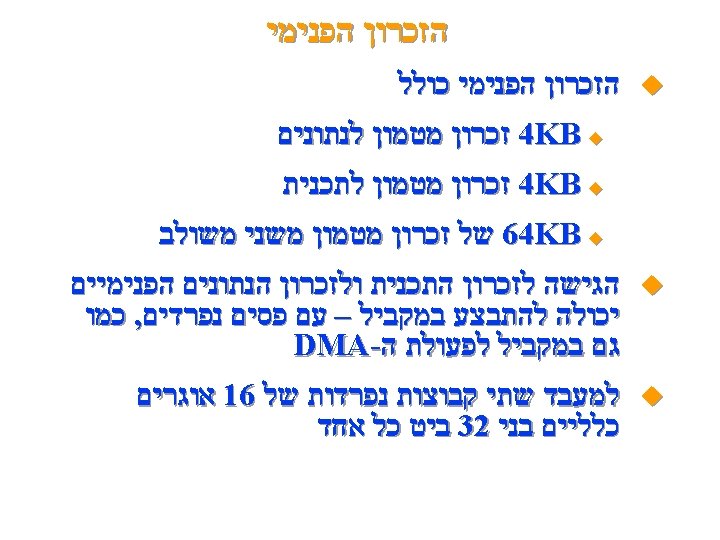

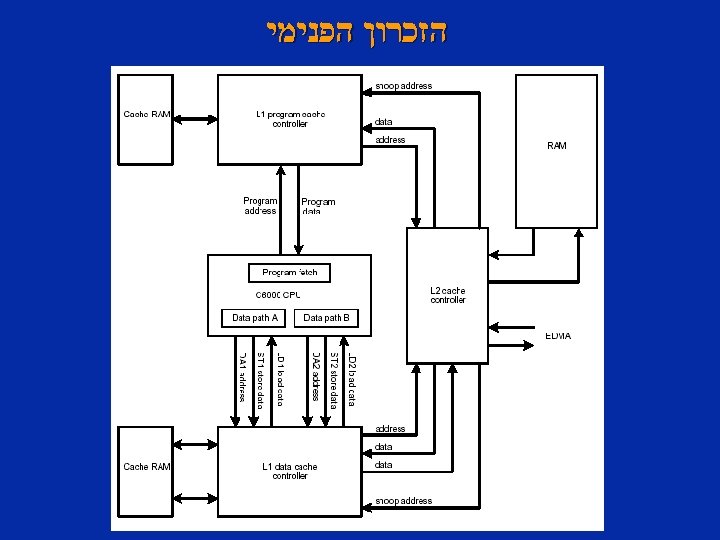

הזכרון הפנימי Chapter 2, Slide 6 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

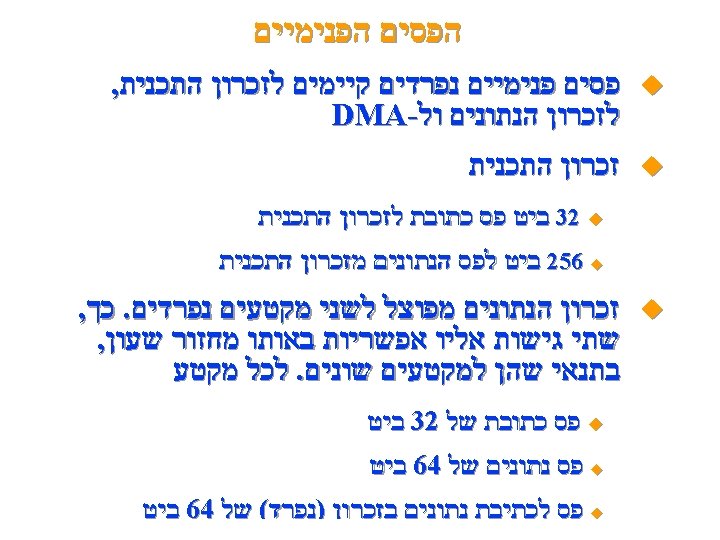

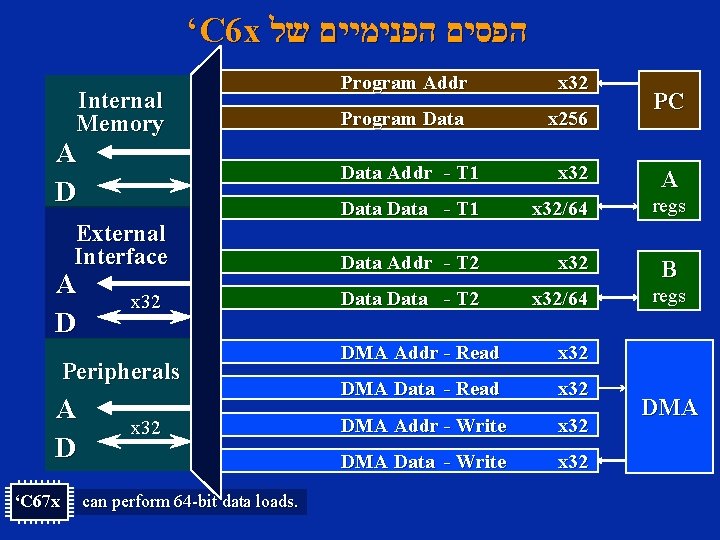

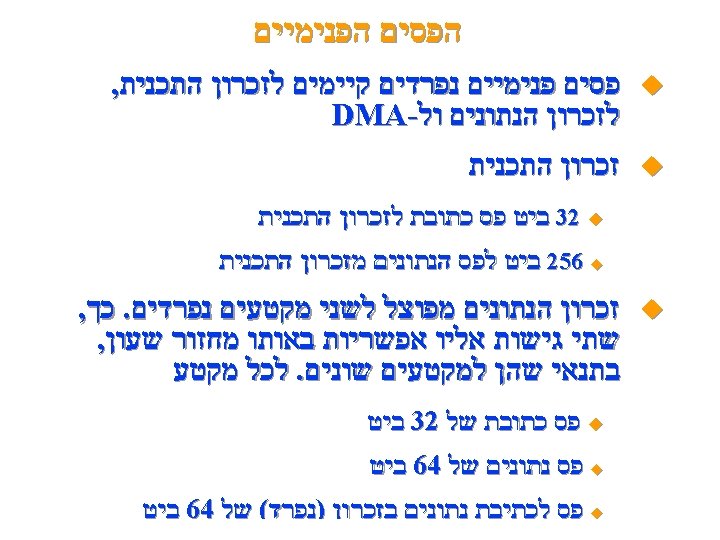

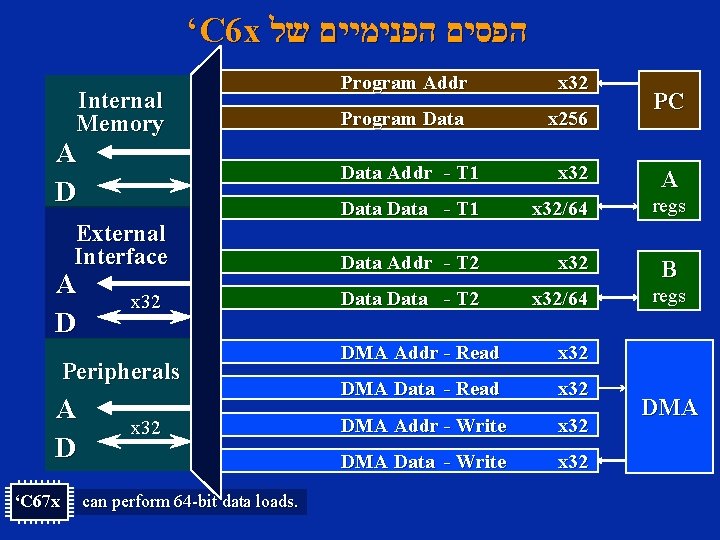

‘C 6 x הפסים הפנימיים של Internal Memory A D External Interface A D x 32 Peripherals A D ‘C 67 x x 32 Program Addr x 32 Program Data x 256 Data Addr - T 1 x 32 Data - T 1 x 32/64 Data Addr - T 2 x 32 Data - T 2 x 32/64 DMA Addr - Read x 32 DMA Data - Read x 32 DMA Addr - Write x 32 DMA Data - Write x 32 PC A regs B regs DMA can perform 64 -bit data loads. Chapter 2, Slide 8 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

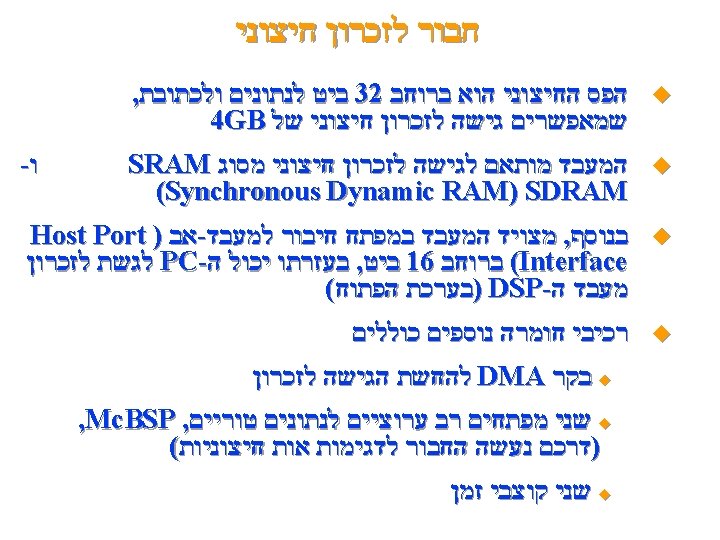

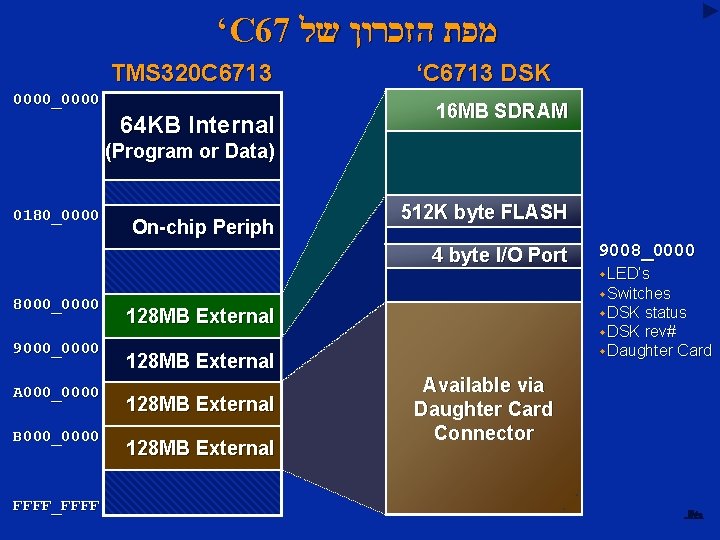

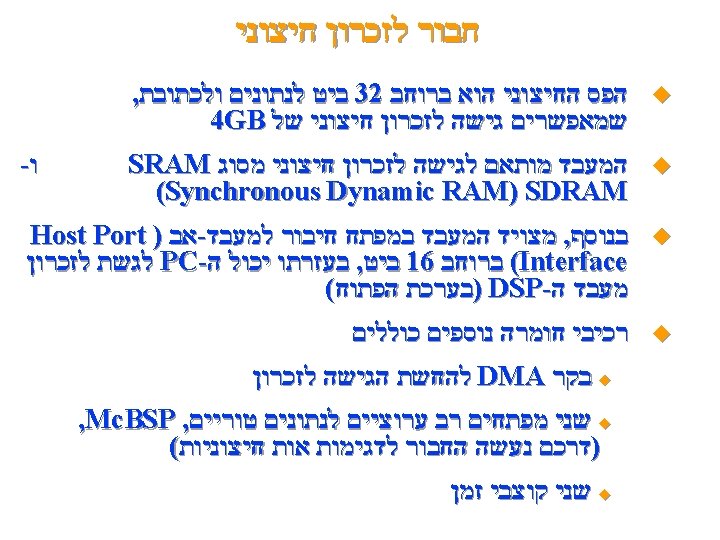

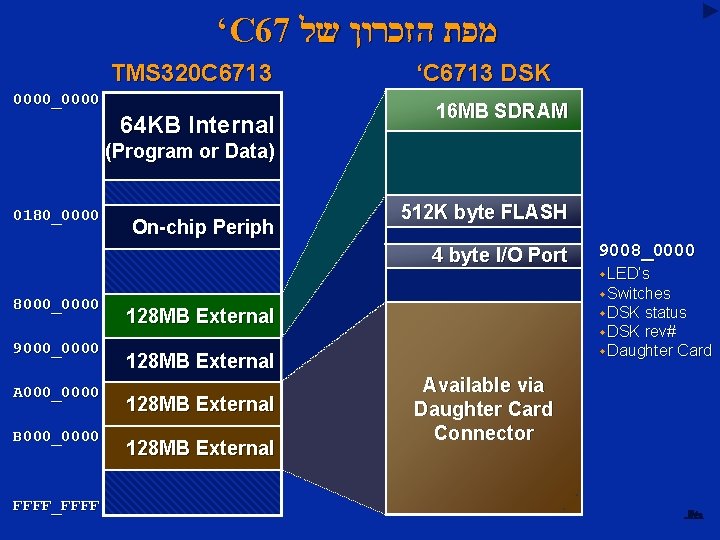

‘C 67 מפת הזכרון של TMS 320 C 6713 0000_0000 64 KB Internal ‘C 6713 DSK 16 MB SDRAM (Program or Data) 0180_0000 On-chip Periph 512 K byte FLASH 4 byte I/O Port 8000_0000 9000_0000 A 000_0000 B 000_0000 status rev# Daughter Card 128 MB External LED’s Switches DSK 128 MB External 9008_0000 Available via Daughter Card Connector FFFF_FFFF Chapter 2, Slide 10 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

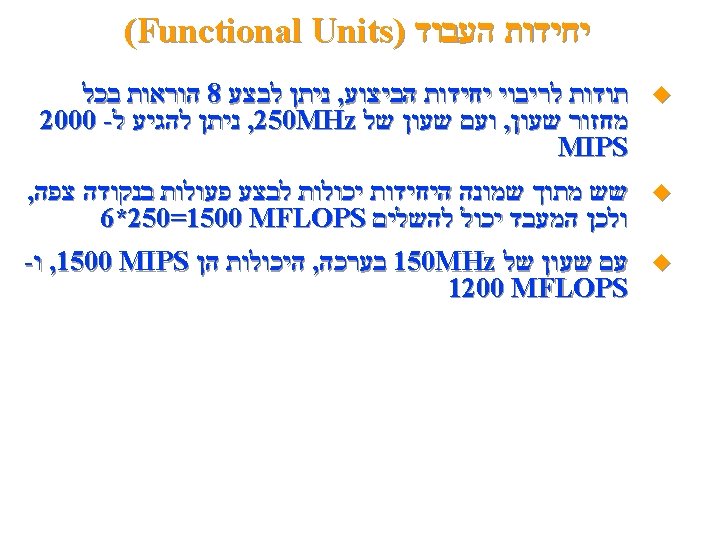

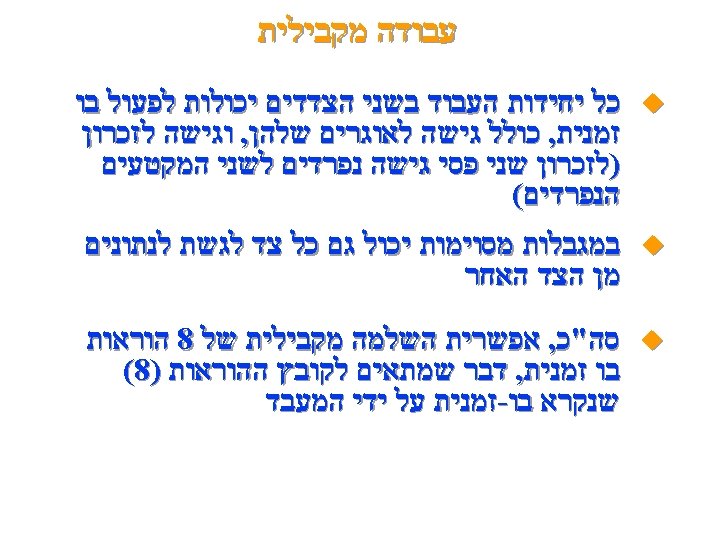

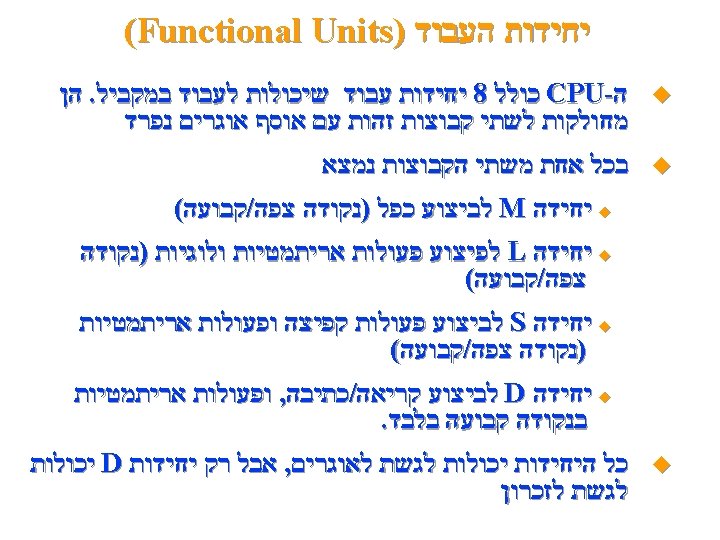

הגדלת קצב הפעולה Register File A A 0 A 1 A 2 A 3 A 4 . S 1. M 1 . . L 1 ( הגדל קצב השעון 1) ( הגדלת מספר יחידות 2) העבוד והוספת מקביליות בפעולה . D 1 A 15 32 -bits Data Memory Chapter 2, Slide 14 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

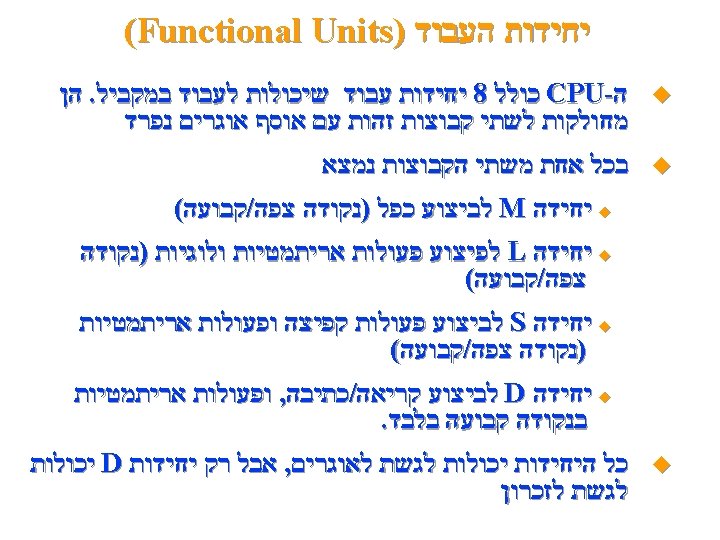

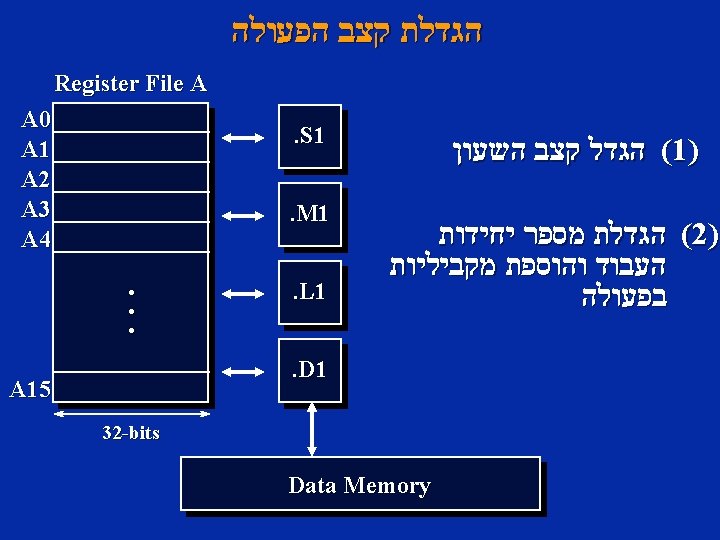

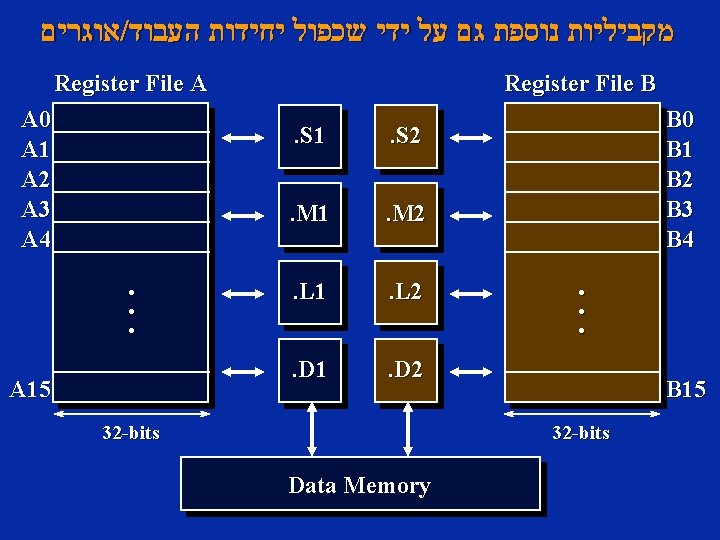

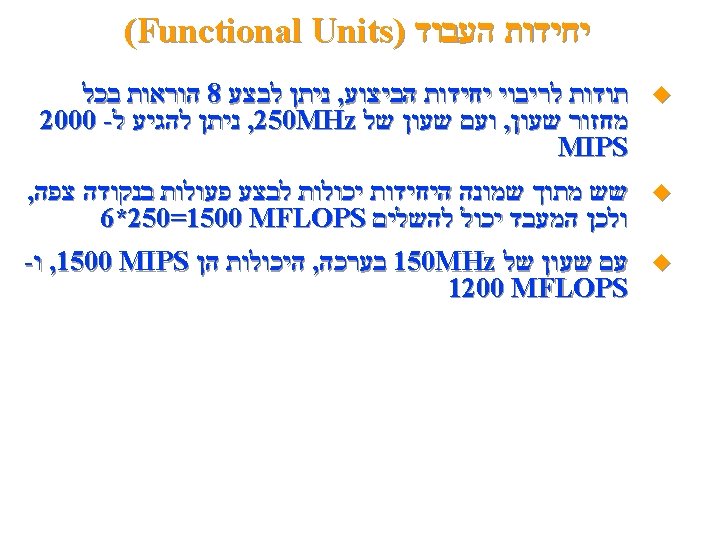

אוגרים / מקביליות נוספת גם על ידי שכפול יחידות העבוד Register File A A 0 A 1 A 2 A 3 A 4 . . . A 15 Register File B. S 1 . S 2 . M 1 . M 2 . L 1 . L 2 . D 1 . D 2 32 -bits B 0 B 1 B 2 B 3 B 4 . . . B 15 32 -bits Data Memory Chapter 2, Slide 15 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

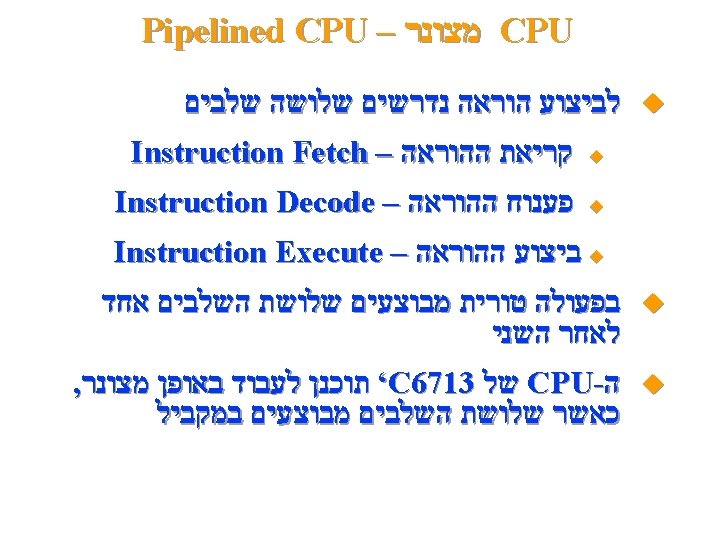

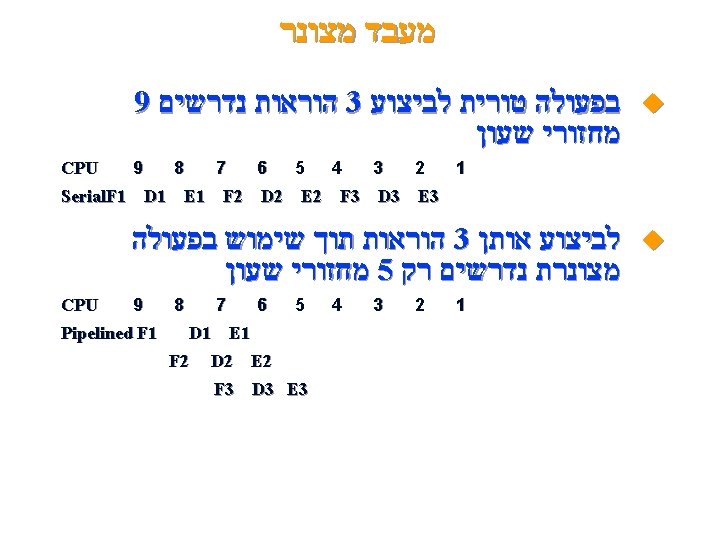

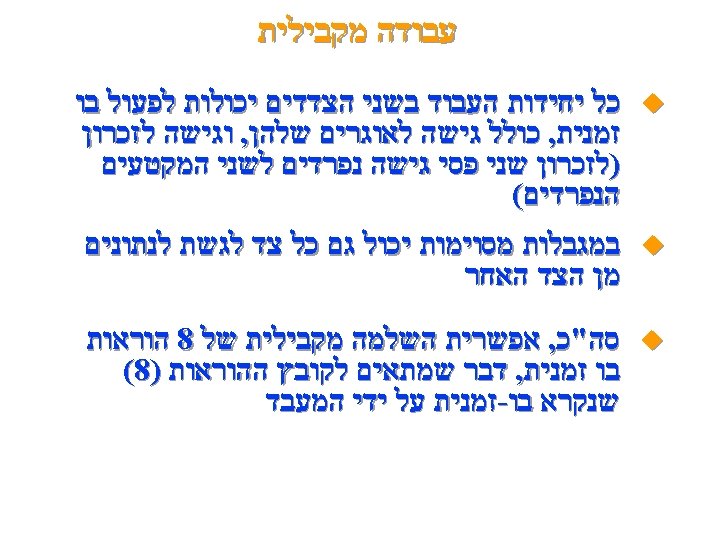

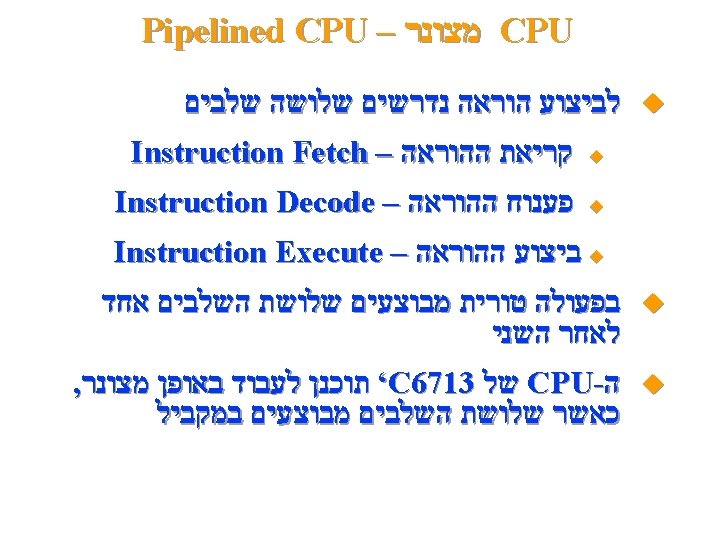

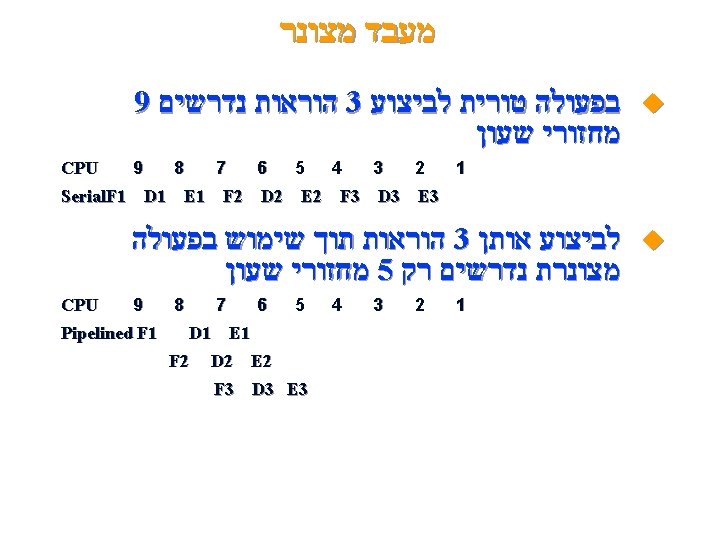

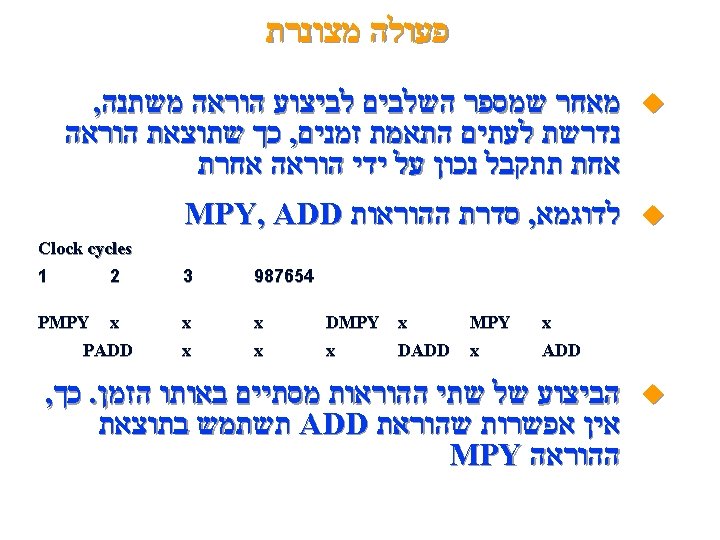

מעבד מצונר u בפעולה טורית לביצוע 3 הוראות נדרשים 9 מחזורי שעון 1 2 3 4 5 6 8 7 9 CPU Serial. F 1 D 1 E 1 F 2 D 2 E 2 F 3 D 3 E 3 u לביצוע אותן 3 הוראות תוך שימוש בפעולה מצונרת נדרשים רק 5 מחזורי שעון 1 2 3 4 5 6 8 7 D 1 E 1 D 2 E 2 9 CPU Pipelined F 1 F 2 F 3 D 3 E 3 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002 Chapter 2, Slide 18

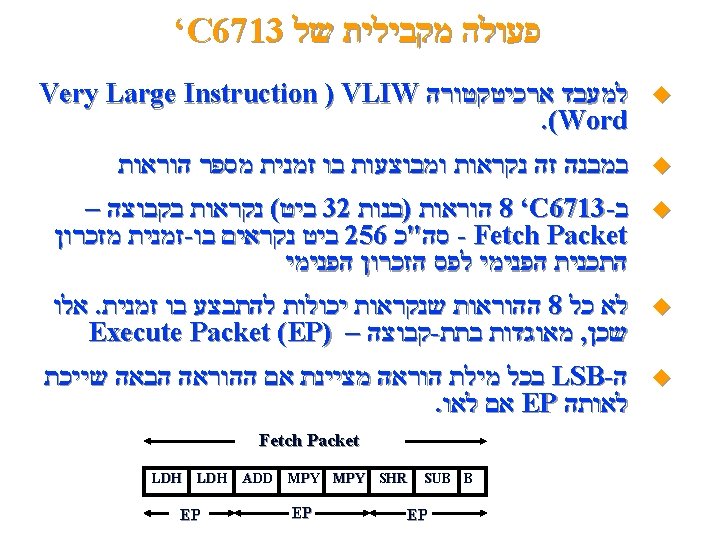

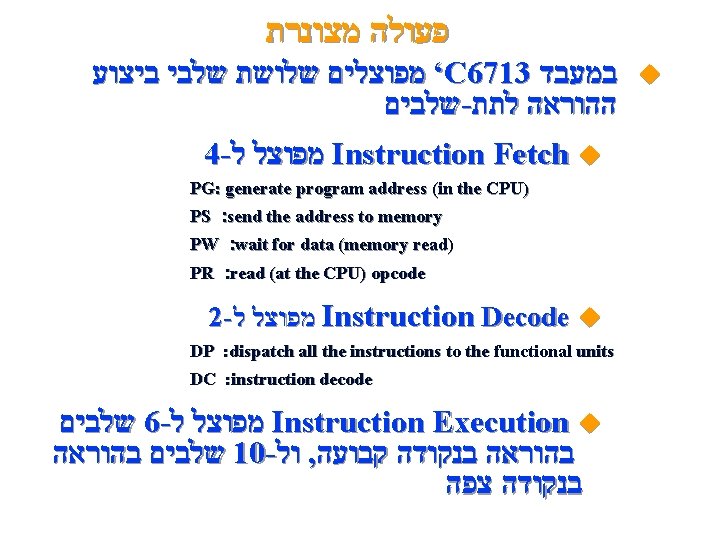

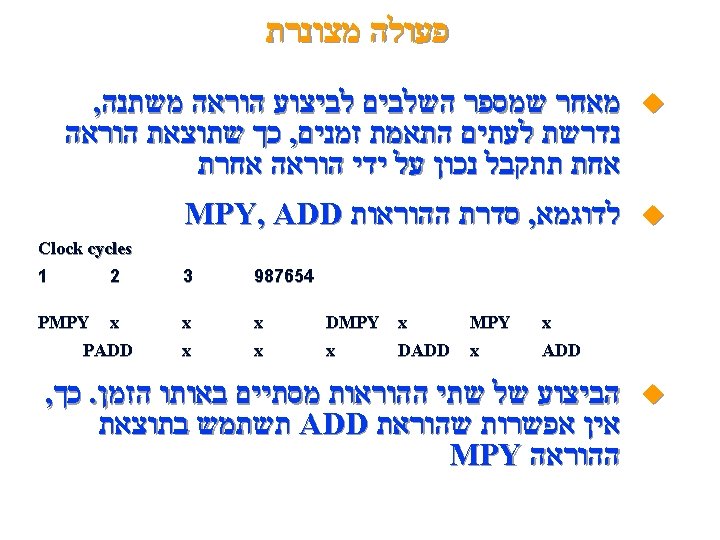

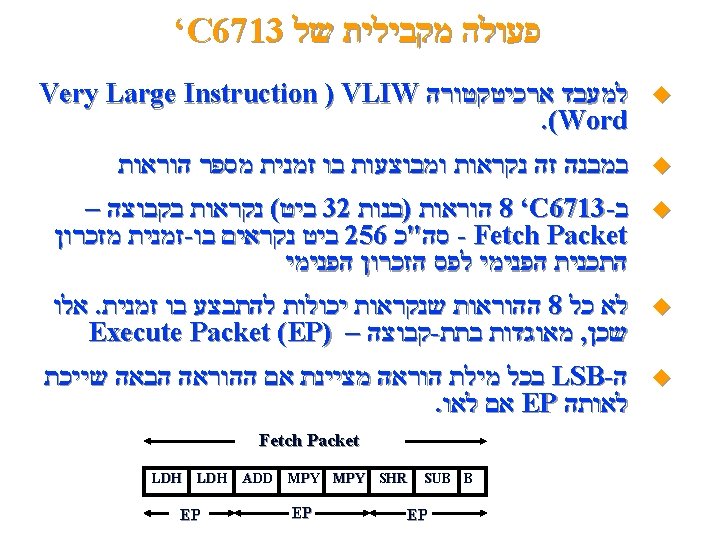

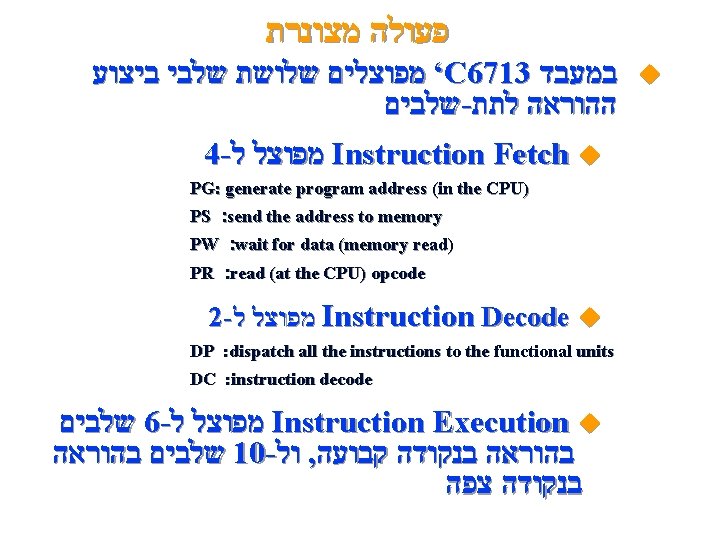

פעולה מצונרת ‘ מפוצלים שלושת שלבי ביצוע C 6713 במעבד שלבים - ההוראה לתת u 4 - מפוצל ל Instruction Fetch u PG: generate program address (in the CPU) PS : send the address to memory PW : wait for data (memory read) PR : read (at the CPU) opcode 2 - מפוצל ל Instruction Decode u DP : dispatch all the instructions to the functional units DC : instruction decode שלבים 6 - מפוצל ל Instruction Execution u שלבים בהוראה 10 - ול , בהוראה בנקודה קבועה בנקודה צפה Chapter 2, Slide 19 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002

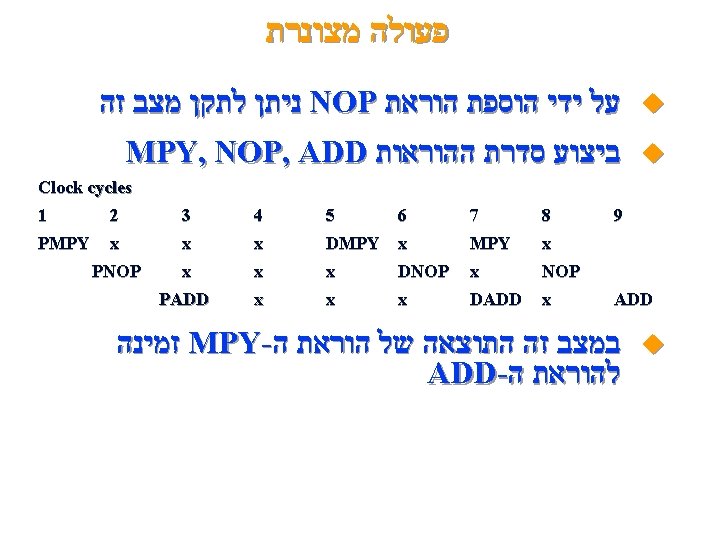

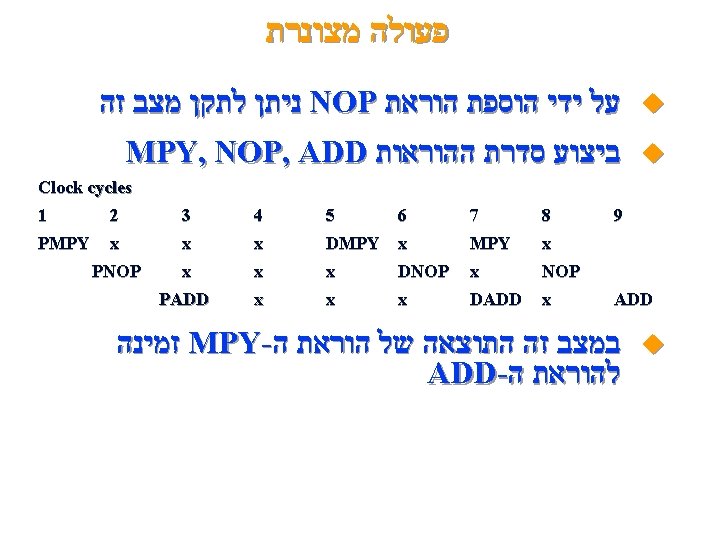

פעולה מצונרת ניתן לתקן מצב זה NOP על ידי הוספת הוראת u MPY, NOP, ADD ביצוע סדרת ההוראות u Clock cycles 1 2 3 4 5 PMPY x x x PNOP x PADD 6 7 8 DMPY x x x DNOP x x x DADD x 9 ADD זמינה MPY- במצב זה התוצאה של הוראת ה ADD- להוראת ה Chapter 2, Slide 21 u Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2002