Bunchbybunch feedbacks and Low Level RF Alessandro Drago

Bunch-by-bunch feedbacks and Low Level RF Alessandro Drago LNF, 1 -4 December 2009

Main topics • Feedback design basics • 12 -bit feedback ready to be tested for the new KLOE runs in DAFNE • Low noise longitudinal front-end / back-end ready to be tested for the new KLOE runs in DAFNE • FPGA design progress • Jitter measurements on Virtex-5 FPGA • Models & simulators • Low Level RF status • Conclusions

Super. B bunch-by-bunch feedback system general considerations • Dramatic acceleration of electronic component development, is making obsolete in short time ALL the existing DAFNE and PEPII transverse and longitudinal feedback systems (included the last versions), and Super. B commissioning will start not before 2014 • Low emittance beams ask for small impact feedback design • From DAFNE tests, we know that it is always possible manage more power in the feedbacks installing as many systems as necessary • Indeed we have proved that two separate feedback systems for the same oscillation plane can work in perfect collaboration doubling the feedback damping inverse time • New feedback design can’t be just a software porting but it must be based on robustness, flexibility, scalability and innovation, and, as consequence, the digital processing unit (DPU) will be the same for transverse and longitudinal feedback systems • New feedback systems needs internal and beam diagnostics tools and the legacy of the previous systems should be carefully implemented with the best compatibility

B-B-B Feedback Main R&D Topics R&D list includes the following upgrade points respect to the previous feedback versions: 1) very low noise analog front end @ n*RF [n=3 or 4 or 6] 2) maintain low cross-talk between adjacent bunches under 40 d. B (better 60 d. B) in front end 3) Only one pickup for each feedback system 4) digital processing unit with 12/16 bits ADC/DAC for high dynamic range feedback loop >=72 d. B 5) “dual gain” approach to minimize residual beam motion and feedback noise on the beam [to be implemented in DPU] 6) integrated beam-feedback model with easy code and parameter download to DPU 7) 500 W vs. 250 W power amplifiers 8) dual separated timing to pilot the backend power stage 9) Cavity kickers (for longitudinal systems) and stripline kickers (for transverse systems) for 2. 1 ns bunch spacing

Open questions 1) Type and growth rate of instabilities 2) How much power & how many feedbacks are necessary ? 3) Impact of b-b-b feedback systems on ultra-low emittance beams 4) Obsolescence of the hardware (chips) 5) Obsolescence of the project (software maintenance)

Design progress • Two converging ways to test the design topics: outsourcing R&D and in-house R&D • 1. ) outsourcing R&D: an upgrade of the i. GP system working at 12 bit (i. Gp 12) will be ready by next March to be evaluated at DAFNE for KLOE runs (two units funded by Super. B 2009 budget) • 1. 1) the i. Gp 12 is sw compatible with the previous 8 bit i. Gp system born by a KEK-SLAC-LNF collaboration • 1. 2) longitudinal front-end / back-end will be also ready and tested in the next DAFNE/KLOE run (Super. B budget) • 2) in-house R&D: a stand-alone development system, using a XILINX single-board, is under test at LNF (funded by INFN C. S. N. V with the SFEED project) • The two approaches are both necessary to evaluate at the best the design parameters versus the real FPGA computing power

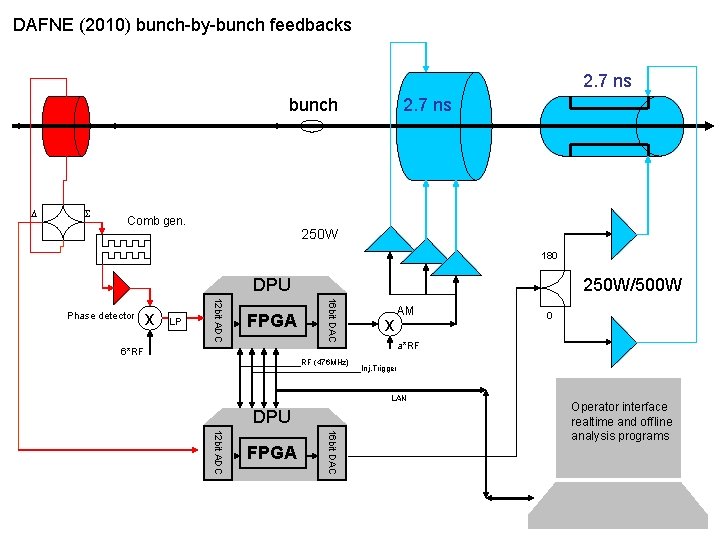

DAFNE (2010) bunch-by-bunch feedbacks 2. 7 ns bunch D S Comb gen. 2. 7 ns 250 W 180 DPU LP FPGA 16 bit DAC x 12 bit ADC Phase detector 250 W/500 W x Inj. Trigger LAN DPU 16 bit DAC 12 bit ADC FPGA 0 a*RF 6*RF RF (476 MHz) AM Operator interface realtime and offline analysis programs

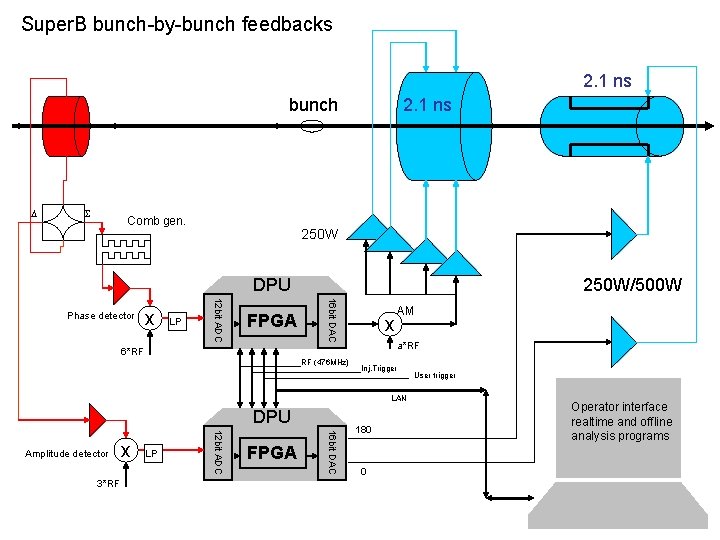

Super. B bunch-by-bunch feedbacks 2. 1 ns bunch D S Comb gen. 2. 1 ns 250 W DPU LP FPGA 16 bit DAC x 12 bit ADC Phase detector 250 W/500 W x a*RF 6*RF RF (476 MHz) AM Inj. Trigger LAN DPU LP FPGA 16 bit DAC 3*RF x 12 bit ADC Amplitude detector 180 0 User trigger Operator interface realtime and offline analysis programs

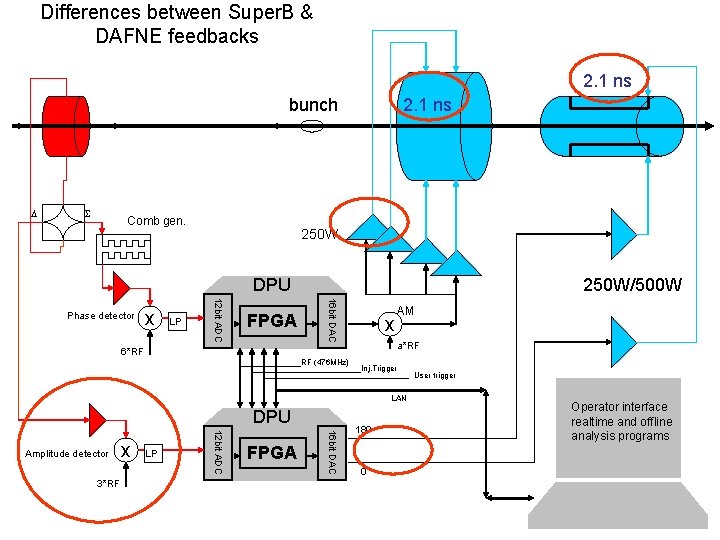

Differences between Super. B & DAFNE feedbacks 2. 1 ns bunch D S Comb gen. 2. 1 ns 250 W DPU LP FPGA 16 bit DAC x 12 bit ADC Phase detector 250 W/500 W x a*RF 6*RF RF (476 MHz) AM Inj. Trigger LAN DPU LP FPGA 16 bit DAC 3*RF x 12 bit ADC Amplitude detector 180 0 User trigger Operator interface realtime and offline analysis programs

In-house R&D • Based on XILINX ML 506 with Virtex-5 FPGA • Main features – The operator interface is based on a Web-Browser through a LAN (1 Gbps ethernet) connection (on the contrary in the i. Gp and i. Gp 12 systems the operator interface is made by EPICS) – The external pc, placed inside the i. Gp box, is not more necessary because Microblaze microprocessor is implemented in the FPGA itself – Low cost powerful board, commercially available – Easy reprogramming in-house – Many tests of the hardware performance are possible because it is not a black box

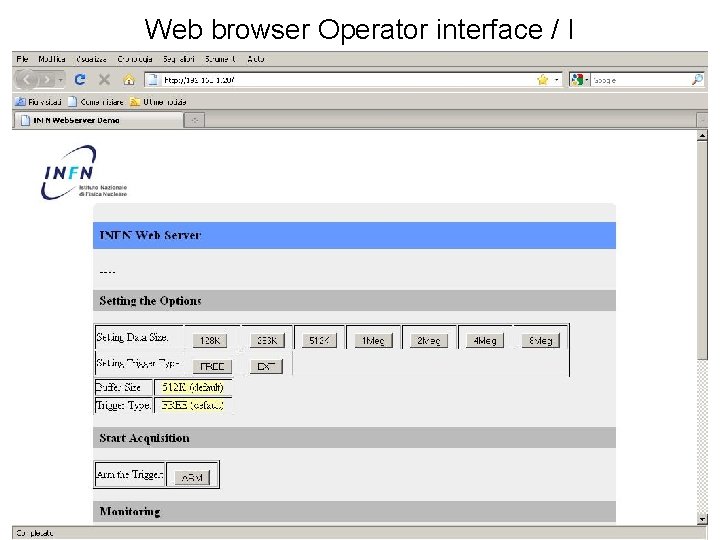

Web browser Operator interface / I

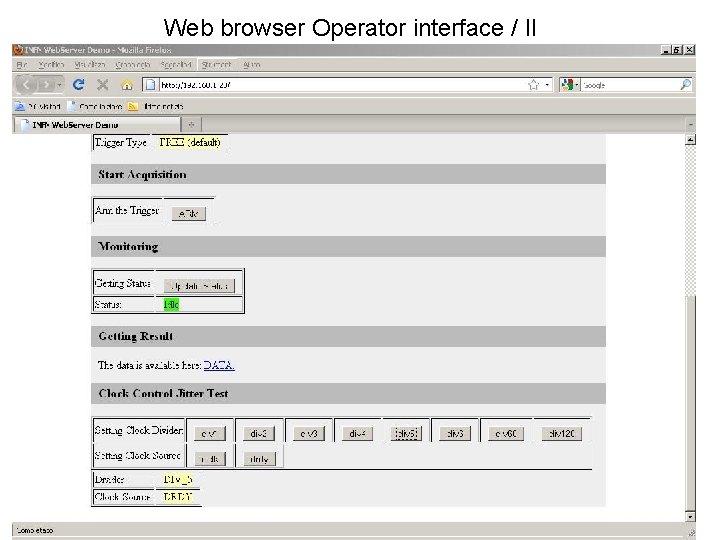

Web browser Operator interface / II

General Clock Divider (odd part) micro. Blaze N ext. CLK 1+(N-1)/2 CNT = en_tff 2 FF (toggle) div 1 CNT mod N CNT = 0 div 2 en_tff 1 FF (toggle) clkout

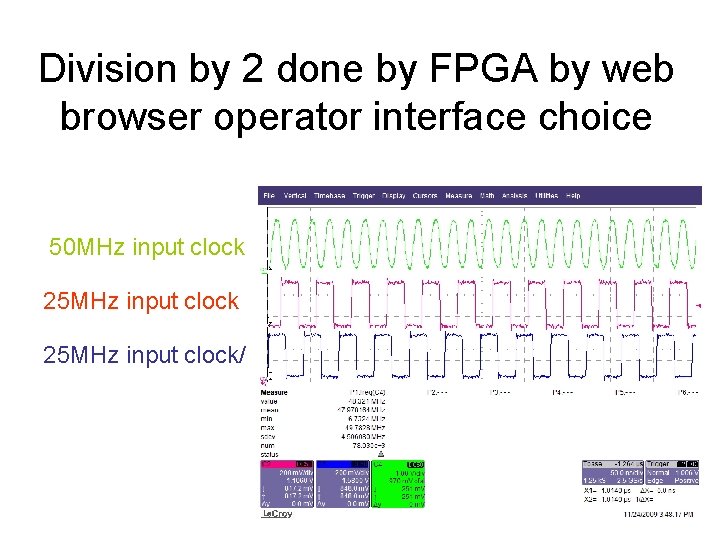

Division by 2 done by FPGA by web browser operator interface choice 50 MHz input clock 25 MHz input clock/

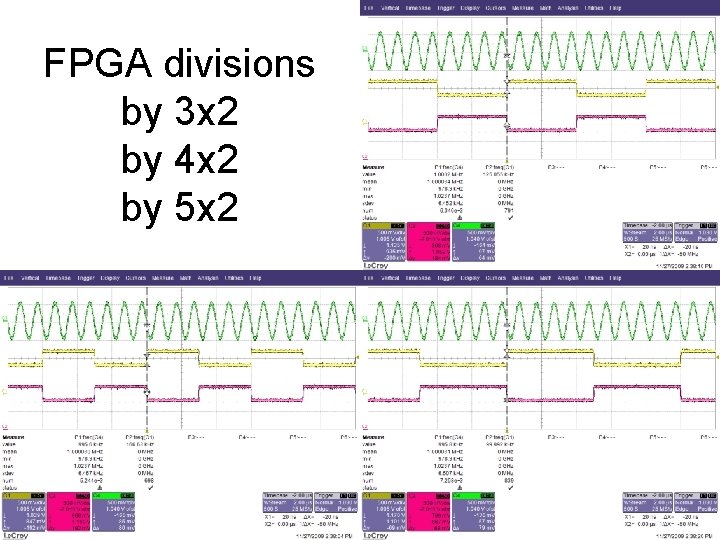

FPGA divisions by 3 x 2 by 4 x 2 by 5 x 2

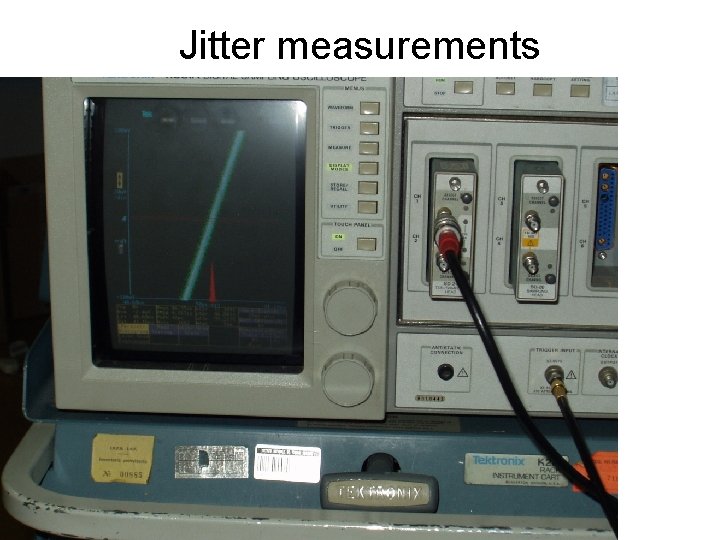

Jitter measurements

Jitter measurements made by high bandwidth (20 GHz) oscilloscope TEK 11801 A making a comparison between source RF signal and division reasult output signal ~40 ps peak-peak jitter ~5 ps RMS jitter

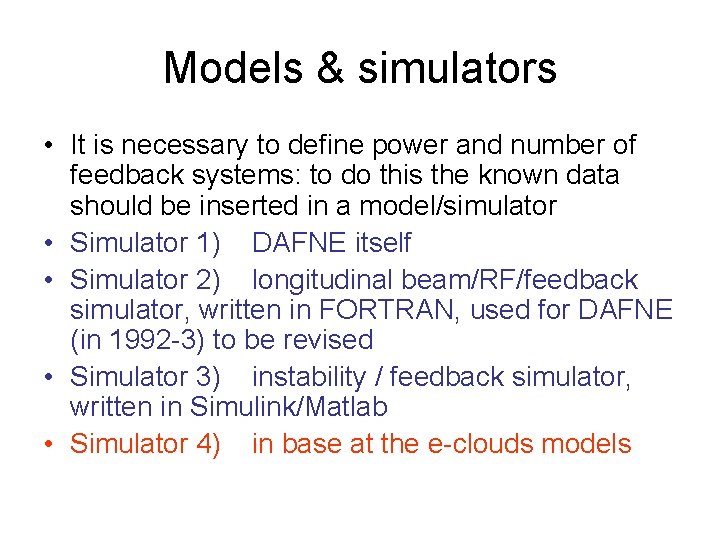

Models & simulators • It is necessary to define power and number of feedback systems: to do this the known data should be inserted in a model/simulator • Simulator 1) DAFNE itself • Simulator 2) longitudinal beam/RF/feedback simulator, written in FORTRAN, used for DAFNE (in 1992 -3) to be revised • Simulator 3) instability / feedback simulator, written in Simulink/Matlab • Simulator 4) in base at the e-clouds models

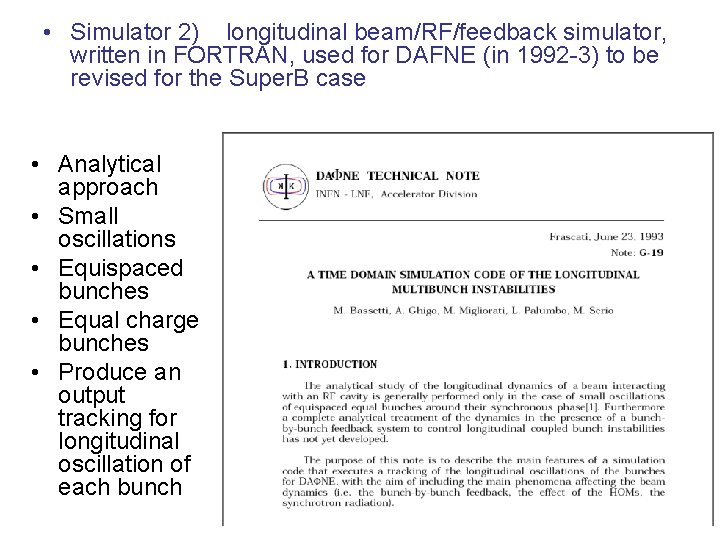

• Simulator 2) longitudinal beam/RF/feedback simulator, written in FORTRAN, used for DAFNE (in 1992 -3) to be revised for the Super. B case • Analytical approach • Small oscillations • Equispaced bunches • Equal charge bunches • Produce an output tracking for longitudinal oscillation of each bunch

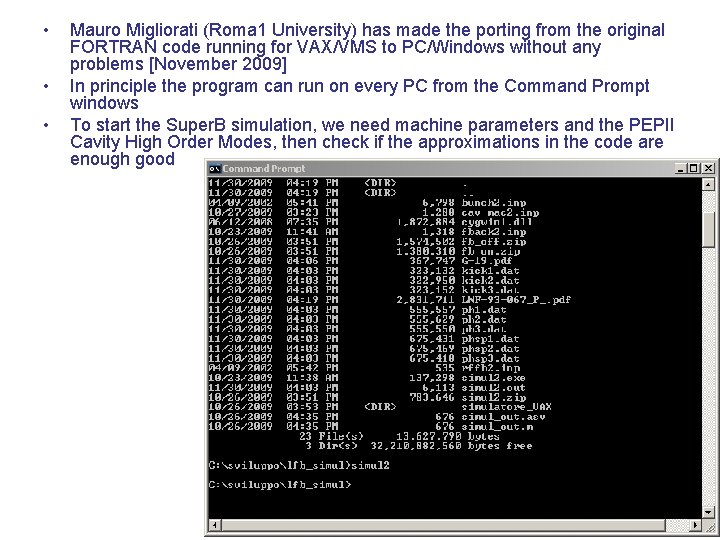

• • • Mauro Migliorati (Roma 1 University) has made the porting from the original FORTRAN code running for VAX/VMS to PC/Windows without any problems [November 2009] In principle the program can run on every PC from the Command Prompt windows To start the Super. B simulation, we need machine parameters and the PEPII Cavity High Order Modes, then check if the approximations in the code are enough good

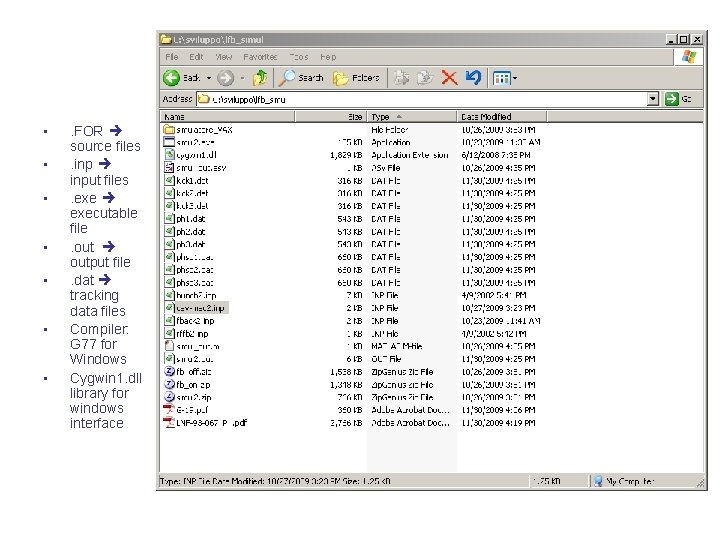

• • . FOR source files. input files. executable file. output file. dat tracking data files Compiler: G 77 for Windows Cygwin 1. dll library for windows interface

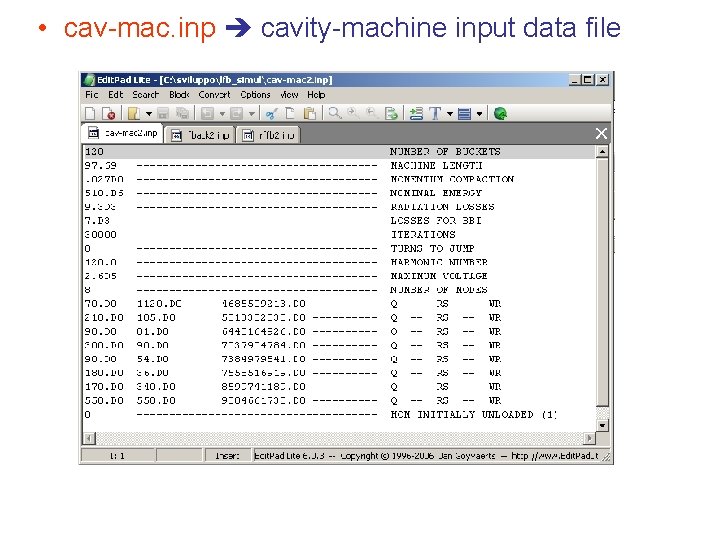

• cav-mac. inp cavity-machine input data file

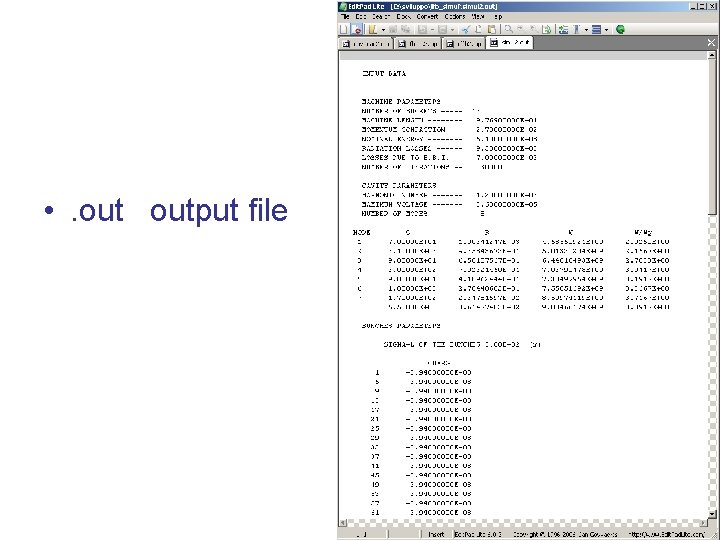

• . output file

• Easy file. data plot by MATLAB

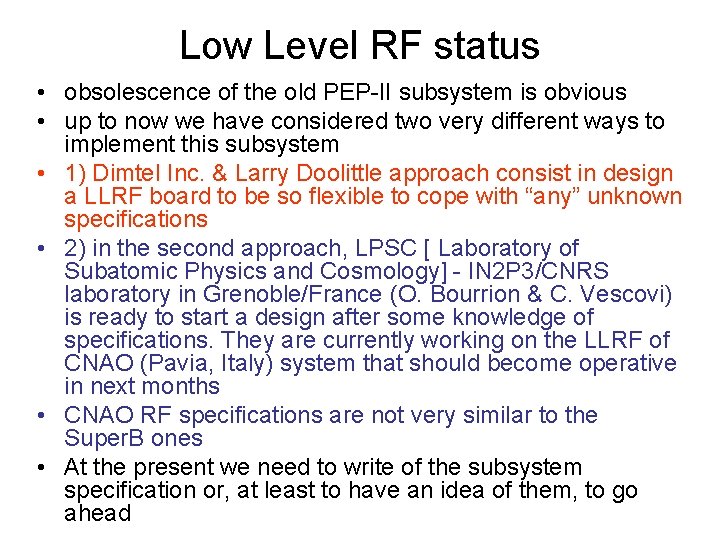

Low Level RF status • obsolescence of the old PEP-II subsystem is obvious • up to now we have considered two very different ways to implement this subsystem • 1) Dimtel Inc. & Larry Doolittle approach consist in design a LLRF board to be so flexible to cope with “any” unknown specifications • 2) in the second approach, LPSC [ Laboratory of Subatomic Physics and Cosmology] - IN 2 P 3/CNRS laboratory in Grenoble/France (O. Bourrion & C. Vescovi) is ready to start a design after some knowledge of specifications. They are currently working on the LLRF of CNAO (Pavia, Italy) system that should become operative in next months • CNAO RF specifications are not very similar to the Super. B ones • At the present we need to write of the subsystem specification or, at least to have an idea of them, to go ahead

Conclusions • Much work is in very quick progress for the bunch-by-bunch feedback • Next DAFNE runs will be important to evaluate what is still necessary for the final b-b-b feedback implementation • Some work on the longitudinal simulator can start just from now • LLRF design is waiting for spec’s

- Slides: 27