Builtin selftest of logic blocks in FPGAs Finally

Built-in self-test of logic blocks in FPGAs (Finally, a free lunch: BIST without overhead!) st Robu Low ECE er Pow 7502 LSI V S 2015 ECE 7502 Class Discussion Seyi Ayorinde Tuesday, February 3 rd, 2015

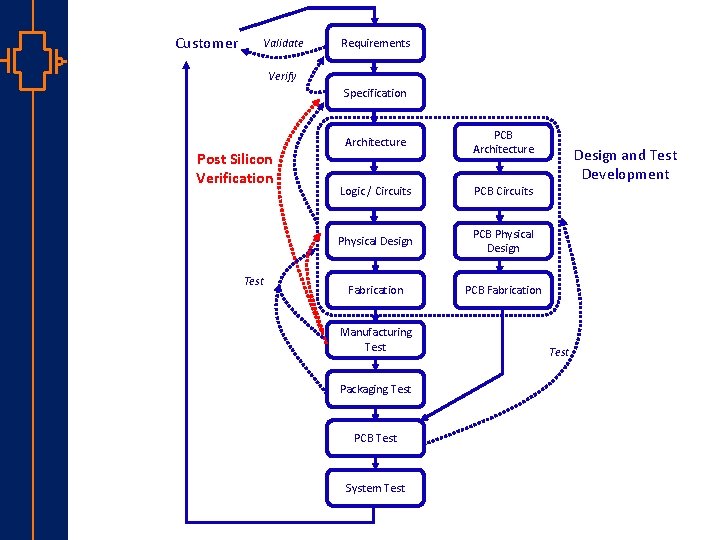

Customer Validate Requirements Verify Specification Post Silicon Verification Test Architecture PCB Architecture Logic / Circuits PCB Circuits Physical Design PCB Physical Design Fabrication PCB Fabrication Manufacturing Test Packaging Test st Robu Low er Pow VLSI PCB Test System Test Design and Test Development Test

Built-In Self Test (BIST) § Allows chips to test themselves § Purpose: reduce cost of testing § Reduce test cycle duration § Reduce complexity of test/probe setup § Reduced cost of expensive automatic test equipment (ATE) st Robu Low er Pow VLSI 3

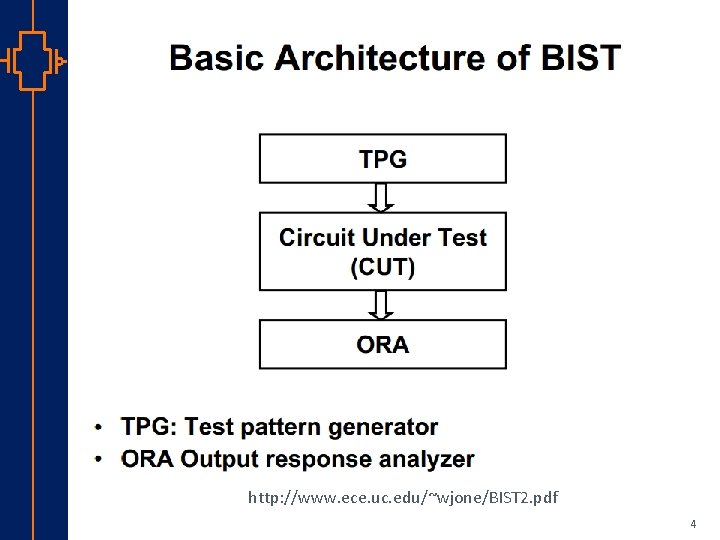

st Robu Low er Pow VLSI http: //www. ece. uc. edu/~wjone/BIST 2. pdf 4

Field Programmable Gate Arrays (FPGAs) § Reconfigurable integrated circuits (ICs) § Collection of look-up tables (LUTs) connected by reconfigurable interconnect § Distributed SRAM bitcells control interconnect and logic in LUTs § LUTs are grouped together into programmable logic blocks (PLBs) st Robu Low er Pow VLSI 5

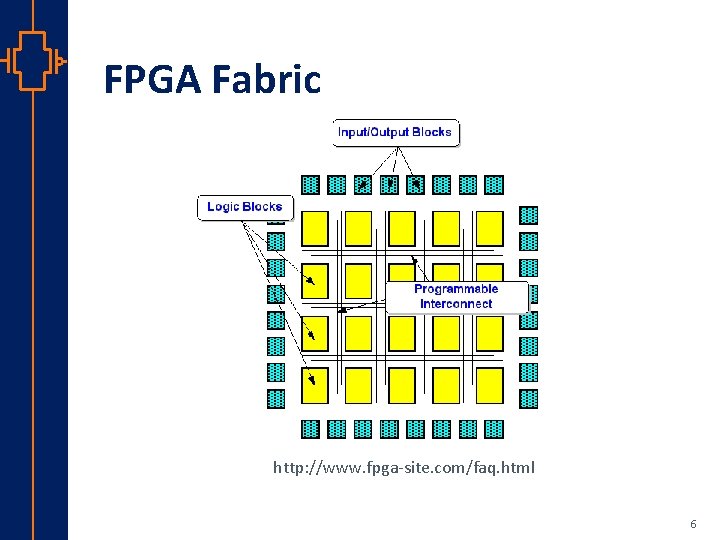

FPGA Fabric st Robu Low er Pow VLSI http: //www. fpga-site. com/faq. html 6

Challenges for FPGA Testing § More coverage needed than traditional IC testing § Multiple configurations § Current solution – configure several applications § Non-classical fault types § Interconnect faults § Configuration faults st Robu Low er Pow VLSI § Additional Development effort is required for on-board and system-level testing 7

BIST for FPGAs – FREE LUNCH!! § Programming logic blocks as TPGs and ORAs for other PLBs § Pseudoexhaustive Test Technique § Allows for complete testing for all logic blocks § Allows testing at-speed § BIST incurs no overhead § Logic blocks can be reconfigured for target functionality, BIST structures “disappear” st Robu Low er Pow VLSI 8

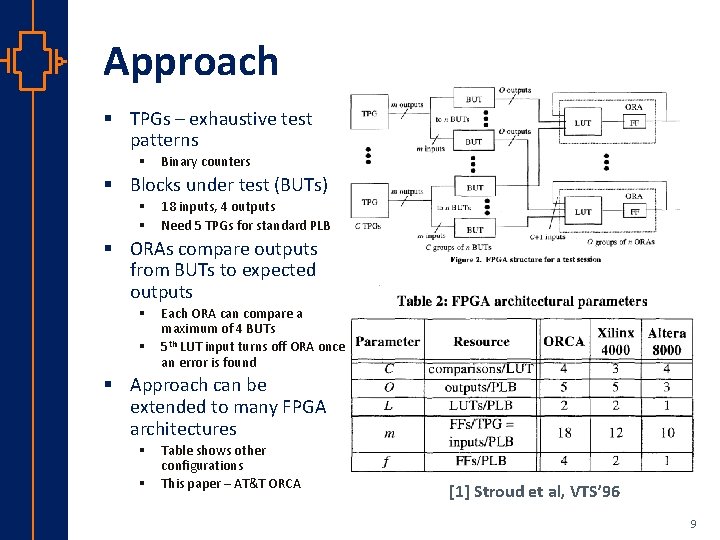

Approach § TPGs – exhaustive test patterns § Binary counters § Blocks under test (BUTs) § § 18 inputs, 4 outputs Need 5 TPGs for standard PLB § ORAs compare outputs from BUTs to expected outputs § § st Robu Low er Pow VLSI Each ORA can compare a maximum of 4 BUTs 5 th LUT input turns off ORA once an error is found § Approach can be extended to many FPGA architectures § § Table shows other configurations This paper – AT&T ORCA [1] Stroud et al, VTS’ 96 9

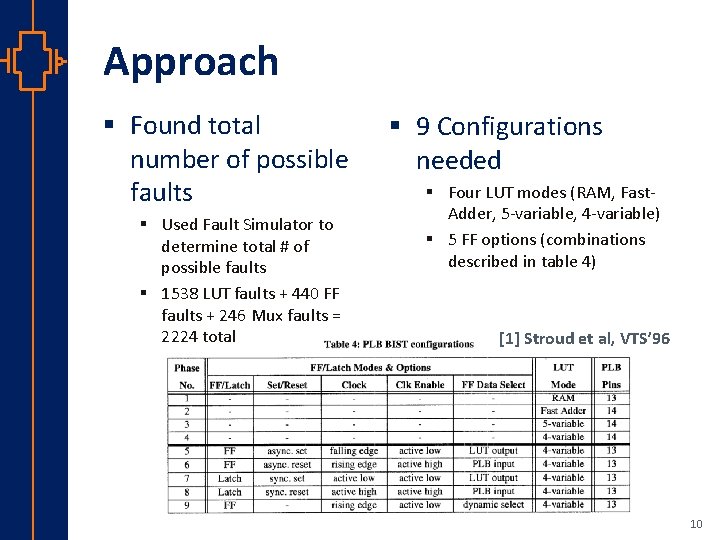

Approach § Found total number of possible faults § Used Fault Simulator to determine total # of possible faults § 1538 LUT faults + 440 FF faults + 246 Mux faults = 2224 total § 9 Configurations needed § Four LUT modes (RAM, Fast. Adder, 5 -variable, 4 -variable) § 5 FF options (combinations described in table 4) [1] Stroud et al, VTS’ 96 st Robu Low er Pow VLSI 10

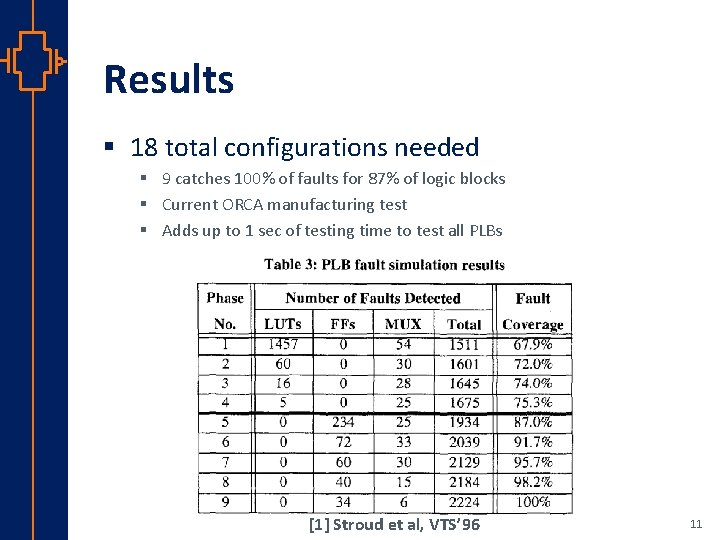

Results § 18 total configurations needed § 9 catches 100% of faults for 87% of logic blocks § Current ORCA manufacturing test § Adds up to 1 sec of testing time to test all PLBs st Robu Low er Pow VLSI [1] Stroud et al, VTS’ 96 11

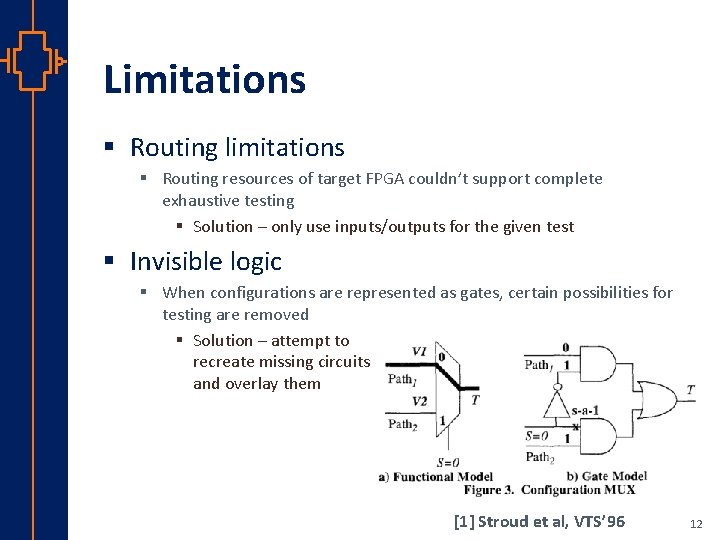

Limitations § Routing limitations § Routing resources of target FPGA couldn’t support complete exhaustive testing § Solution – only use inputs/outputs for the given test § Invisible logic § When configurations are represented as gates, certain possibilities for testing are removed § Solution – attempt to recreate missing circuits and overlay them st Robu Low er Pow VLSI [1] Stroud et al, VTS’ 96 12

Limitations § Lack of detailed configuration control § Can’t make sure that each input of the output mux (for example) will be exercised, because CAD tools don’t give that type of control § Solution – modify intermediate files or final configuration bit stream st Robu Low er Pow VLSI 13

Conclusions st Robu Low er Pow VLSI § FPGAs could theoretically be fully tested without the need for any DFT circuitry by configuring PLBs in the FPGA as TPGs and ORAs for other PLBs § For the AT&T ORCA FPGA, 9 configurations can result in 100% fault coverage for a given PLB § 18 total configurations for testing all PLBs (reduction from 32 configurations) § CAD tools made for FPGAs limit implementation 14

![Interesting Extensions § Menon et al, TCAD’ 06 [2] – Design specific path delay Interesting Extensions § Menon et al, TCAD’ 06 [2] – Design specific path delay](http://slidetodoc.com/presentation_image_h/f4d5abd33d76a3d547a5acb77e10688f/image-15.jpg)

Interesting Extensions § Menon et al, TCAD’ 06 [2] – Design specific path delay testing in LUT-based FPGAs § Testing delays of interconnect paths § Zhang et al, APCCAS’ 08 [3] – BIST approach for testing configurable logic and memory resources in FPGAs § Using hard-macro (physical-macro library provided by Xilinx) for added control over LUT and block RAM resources st Robu Low er Pow VLSI § Rehman et al, DFT’ 13 [4] – BIST for logic and local interconnect resources in a novel mesh of cluster FPGA § Compares BIST in tree-based interconnects to standard 2 -D interconnects 15

Self-heating Thermal-aware testing of FPGAs § Problem – Thermal testing is expensive and unreliable § Expensive -> thermal chambers, time § Unreliable -> low control § Solution – Configure logic blocks in the FPGA as heating elements to locally heat the FPGA in certain areas, removing the need for external temperature control st Robu Low er Pow VLSI 16

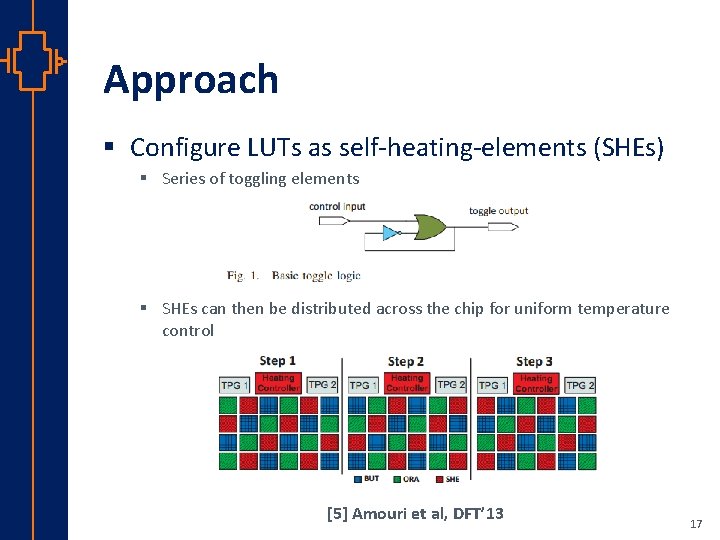

Approach § Configure LUTs as self-heating-elements (SHEs) § Series of toggling elements § SHEs can then be distributed across the chip for uniform temperature control st Robu Low er Pow VLSI [5] Amouri et al, DFT’ 13 17

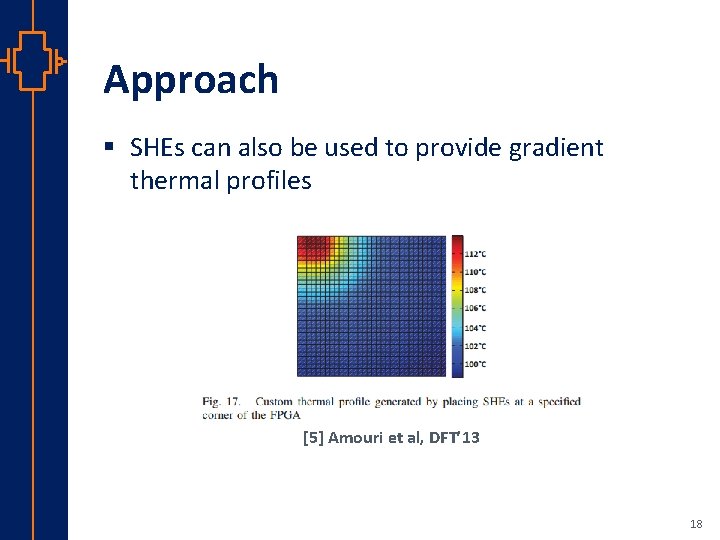

Approach § SHEs can also be used to provide gradient thermal profiles st Robu Low er Pow VLSI [5] Amouri et al, DFT’ 13 18

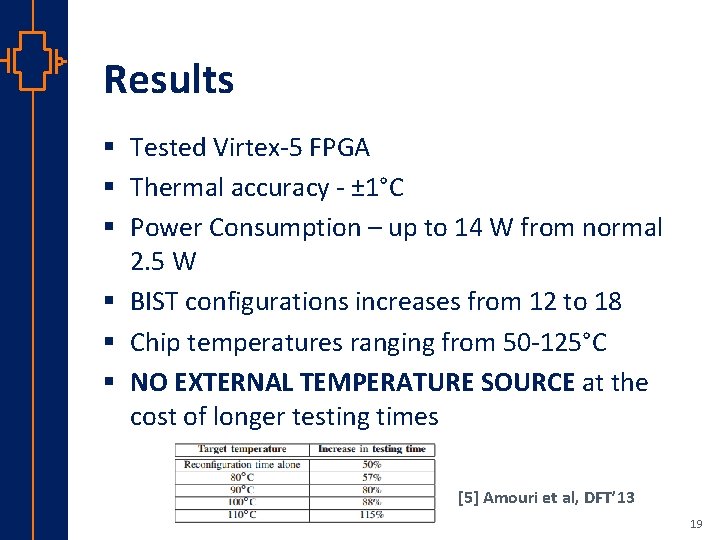

Results st Robu Low er Pow VLSI § Tested Virtex-5 FPGA § Thermal accuracy - ± 1°C § Power Consumption – up to 14 W from normal 2. 5 W § BIST configurations increases from 12 to 18 § Chip temperatures ranging from 50 -125°C § NO EXTERNAL TEMPERATURE SOURCE at the cost of longer testing times [5] Amouri et al, DFT’ 13 19

Discussion questions st Robu Low er Pow VLSI 1. Why are exhaustive RAM tests impractical? 2. In what way is figure 2 somewhat misleading? 3. Can we think of any possible ways to reduce the number of logic blocks necessary for TPGs? 4. What are the limitations to the manner in which the results are reported? 5. What other novel BIST structures (like selfheating) can we come up with? 20

Papers st Robu Low er Pow VLSI 1. Stroud, C. ; Konala, S. ; Ping Chen; Abramovici, M. , "Built-in self-test of logic blocks in FPGAs (Finally, a free lunch: BIST without overhead!), " VLSI Test Symposium, 1996. , Proceedings of 14 th , vol. , no. , pp. 387, 392, 28 Apr-1 May 1996 2. Menon, P. R. ; Weifeng Xu; Tessier, R. , "Design-specific path delay testing in lookup-table -based FPGAs, " Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol. 25, no. 5, pp. 867, 877, May 2006 3. Zhiquan Zhang; Zhiping Wen; Lei Chen; Tao Zhou; Fan Zhang, "BIST approach for testing configurable logic and memory resources in FPGAs, " Circuits and Systems, 2008. APCCAS 2008. IEEE Asia Pacific Conference on , vol. , no. , pp. 1767, 1770, Nov. 30 2008 Dec. 3 2008 4. Rehman, S. -U. ; Benabdenbi, M. ; Anghel, L. , "BIST for logic and local interconnect resources in a novel mesh of cluster FPGA, " Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2013 IEEE International Symposium on , vol. , no. , pp. 296, 301, 2 -4 Oct. 2013 5. Amouri, A. ; Hepp, J. ; Tahoori, M. , "Self-heating thermal-aware testing of FPGAs, " VLSI Test Symposium (VTS), 2014 IEEE 32 nd , vol. , no. , pp. 1, 6, 13 -17 April 2014 21

![Paper Map § § § [1] Lin, D. ; …"Effective Post-Silicon Validation of …, Paper Map § § § [1] Lin, D. ; …"Effective Post-Silicon Validation of …,](http://slidetodoc.com/presentation_image_h/f4d5abd33d76a3d547a5acb77e10688f/image-22.jpg)

Paper Map § § § [1] Lin, D. ; …"Effective Post-Silicon Validation of …, " ICASICS’ 14. [2] Oh, N. ; …"Control-flow checking by software …, " ITR’ 02. [3] Das, P. ; …"Gate delay modeling for pre- and …, " ICCD’ 13. [4] Keshava, J. ; … "Post-silicon validation challenges: …” DAC’ 10. [5] Mitra, S. ; … "Post-silicon validation …, " DAC’ 10. [4] BIST with novel FPGA arch. Uses different architecture, requires new approach [2] BIST for FPGA interconnect st Robu Low er Pow VLSI Addresses interconnect challenge [3] BIST for FPGA using hard-macro [5] Self-heating Thermal Aware FPGAs Expands design space for BIST in FPGAs to new axes Addresses CAD issue [1] Proposed BIST structures for FPGA logic blocks 22

Glossary § § § § BIST: built-in self test TPG: test pattern generator ORA: Output response analyzer FPGA: Field Programmable Gate Array LUT: Look-up Table PLB: Programmable Logic Block SHE: Self-heating elements st Robu Low er Pow VLSI 23

- Slides: 23