Building the Beta I wonder where this goes

Building the Beta I wonder where this goes? A ALU Bet B on 0 a Knstrumctoi ry I i. M te A 1 D Handouts: Lecture Slides 1

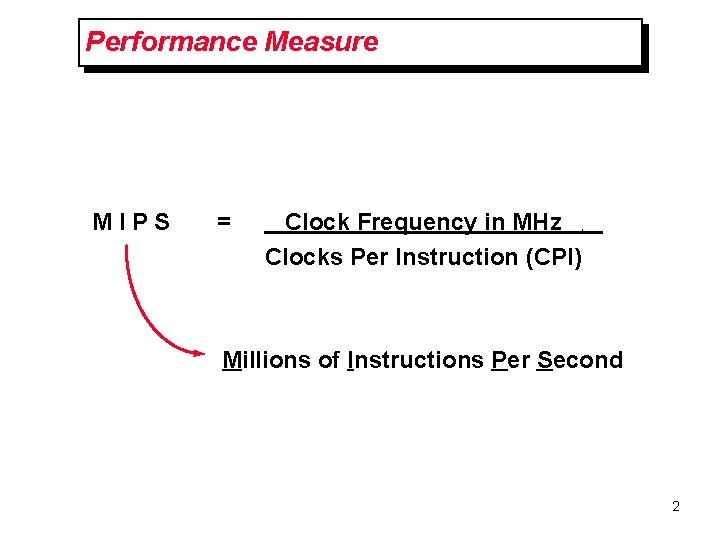

Performance Measure MIPS = Clock Frequency in MHz Clocks Per Instruction (CPI) . Millions of Instructions Per Second 2

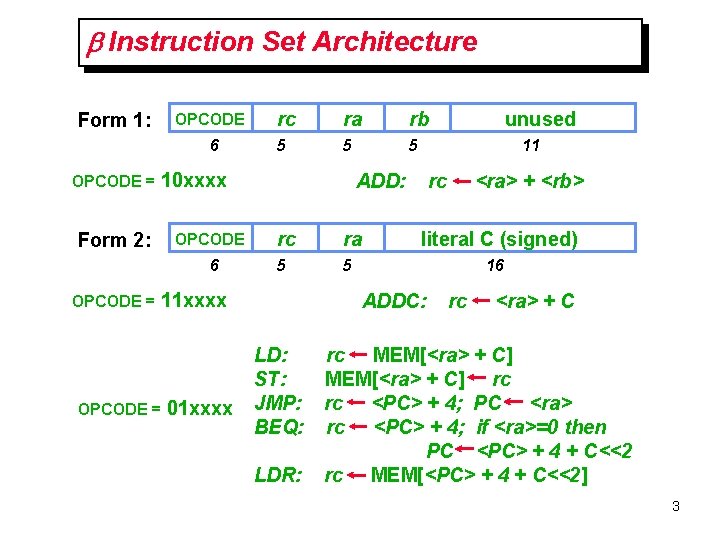

b Instruction Set Architecture Form 1: OPCODE 6 OPCODE = ra rb 5 5 5 10 xxxx Form 2: OPCODE 6 OPCODE = rc 11 xxxx OPCODE = 01 xxxx 11 ADD: rc ra 5 5 unused rc <ra> + <rb> literal C (signed) 16 ADDC: rc <ra> + C LD: rc MEM[<ra> + C] ST: MEM[<ra> + C] rc JMP: rc <PC> + 4; PC <ra> BEQ: rc <PC> + 4; if <ra>=0 then PC <PC> + 4 + C<<2 LDR: rc MEM[<PC> + 4 + C<<2] 3

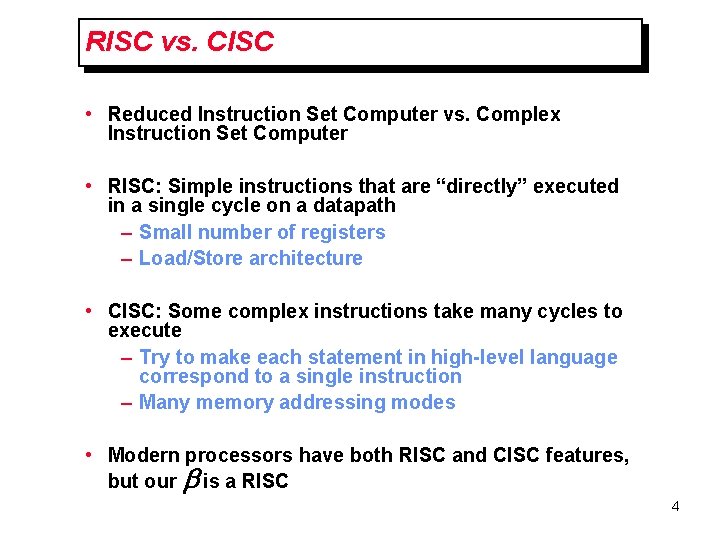

RISC vs. CISC • Reduced Instruction Set Computer vs. Complex Instruction Set Computer • RISC: Simple instructions that are “directly” executed in a single cycle on a datapath – Small number of registers – Load/Store architecture • CISC: Some complex instructions take many cycles to execute – Try to make each statement in high-level language correspond to a single instruction – Many memory addressing modes • Modern processors have both RISC and CISC features, but our b is a RISC 4

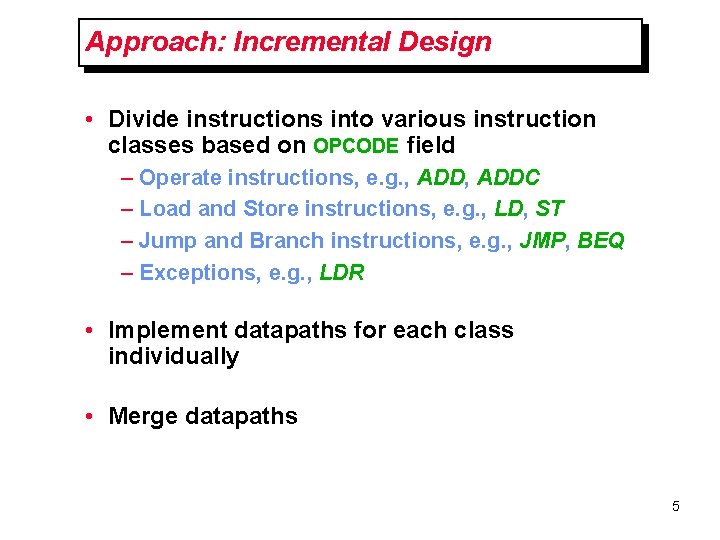

Approach: Incremental Design • Divide instructions into various instruction classes based on OPCODE field – Operate instructions, e. g. , ADDC – Load and Store instructions, e. g. , LD, ST – Jump and Branch instructions, e. g. , JMP, BEQ – Exceptions, e. g. , LDR • Implement datapaths for each class individually • Merge datapaths 5

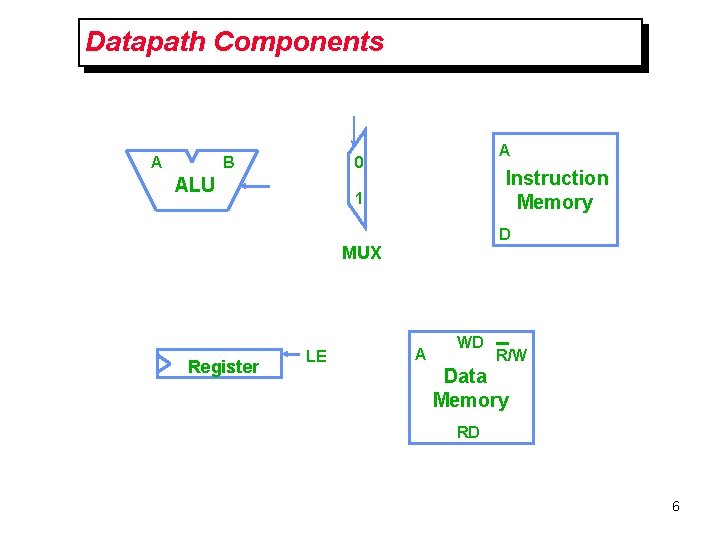

Datapath Components A B A 0 ALU Instruction Memory 1 D MUX Register LE A WD R/W Data Memory RD 6

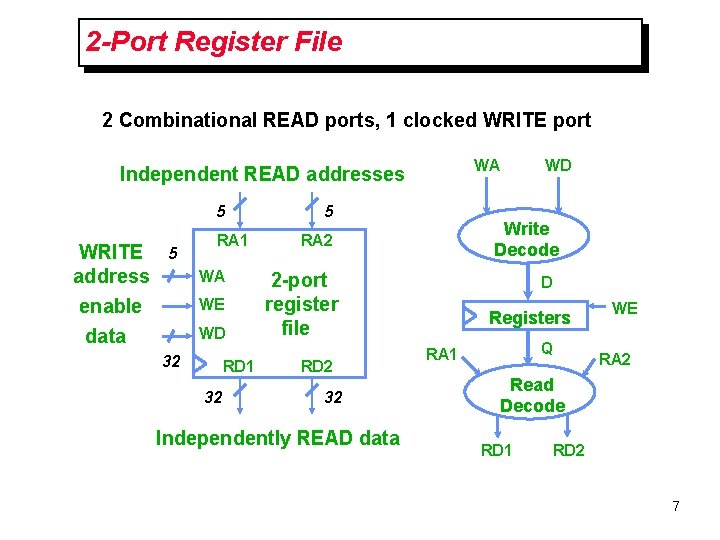

2 -Port Register File 2 Combinational READ ports, 1 clocked WRITE port WA Independent READ addresses 5 WRITE address enable data 5 RA 1 WA WE WD 32 RD 1 32 5 Write Decode RA 2 2 -port register file RD 2 32 Independently READ data WD D Registers Q RA 1 WE RA 2 Read Decode RD 1 RD 2 7

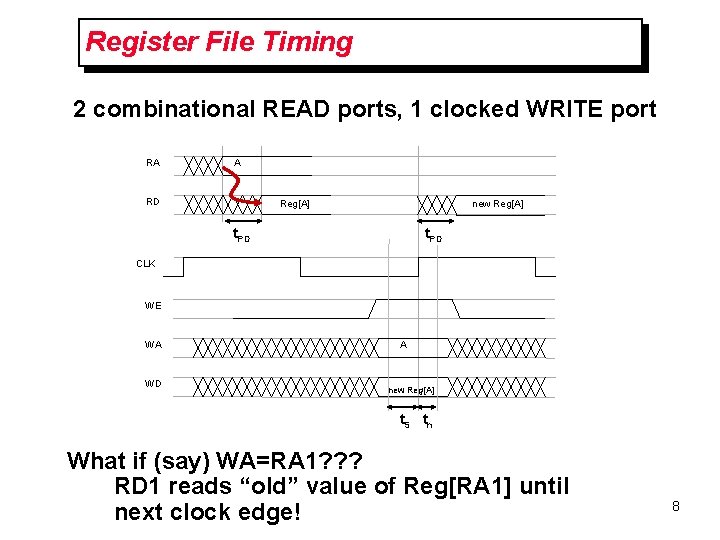

Register File Timing 2 combinational READ ports, 1 clocked WRITE port RA A RD Reg[A] new Reg[A] t. PD CLK WE WA WD A new Reg[A] t. S th What if (say) WA=RA 1? ? ? RD 1 reads “old” value of Reg[RA 1] until next clock edge! 8

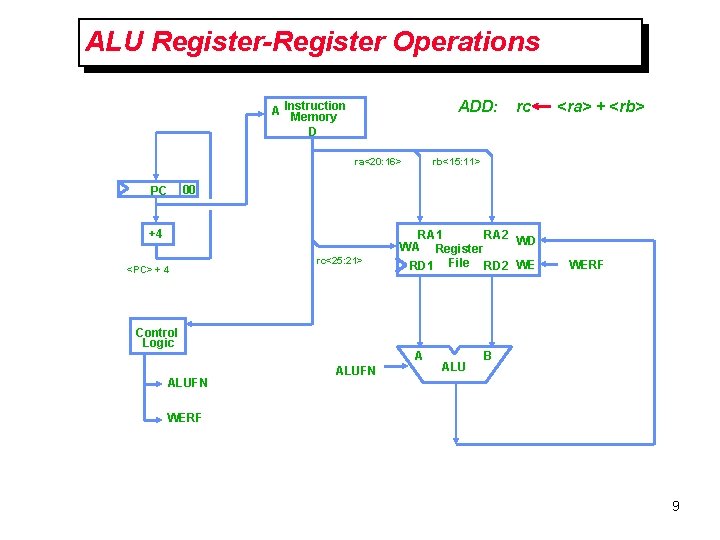

ALU Register-Register Operations ADD: A Instruction Memory D ra<20: 16> PC rc <ra> + <rb> rb<15: 11> 00 +4 <PC> + 4 rc<25: 21> Control Logic ALUFN RA 1 RA 2 WD WA Register RD 1 File RD 2 WE A ALUFN ALU WERF B WERF 9

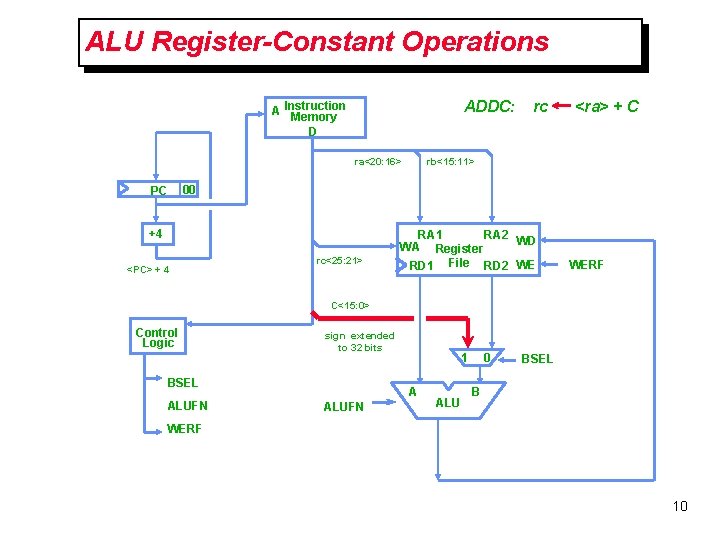

ALU Register-Constant Operations ADDC: A Instruction Memory D ra<20: 16> PC rc <ra> + C rb<15: 11> 00 +4 <PC> + 4 rc<25: 21> RA 1 RA 2 WD WA Register RD 1 File RD 2 WE WERF C<15: 0> Control Logic sign extended to 32 bits BSEL ALUFN 1 A ALUFN ALU 0 BSEL B WERF 10

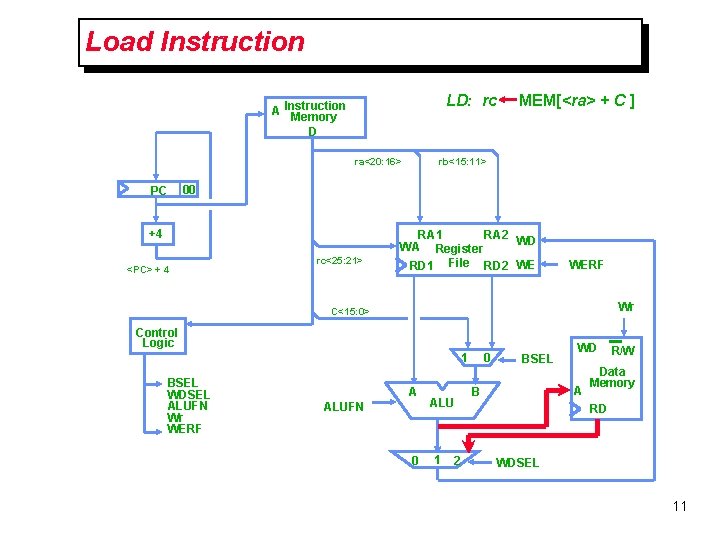

Load Instruction LD: rc A Instruction Memory D ra<20: 16> PC MEM[<ra> + C ] rb<15: 11> 00 +4 <PC> + 4 rc<25: 21> RA 1 RA 2 WD WA Register RD 1 File RD 2 WE WERF Wr C<15: 0> Control Logic 1 BSEL WDSEL ALUFN Wr WERF A ALUFN 0 ALU 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 11

![Store Instruction ST: MEM[<ra> + C] A Instruction Memory D ra<20: 16> PC rb<15: Store Instruction ST: MEM[<ra> + C] A Instruction Memory D ra<20: 16> PC rb<15:](http://slidetodoc.com/presentation_image_h2/a1dbe991532d1e0024cdbeb0fd7209ac/image-12.jpg)

Store Instruction ST: MEM[<ra> + C] A Instruction Memory D ra<20: 16> PC rb<15: 11> 00 <PC> + 4 rc<25: 21> 0 +4 rc<25: 21> 1 RA 2 SEL RA 1 RA 2 WD WA Register RD 1 File RD 2 WE WERF Wr C<15: 0> Control Logic RA 2 SEL BSEL WDSEL ALUFN Wr WERF rc 1 A ALUFN 0 ALU 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 12

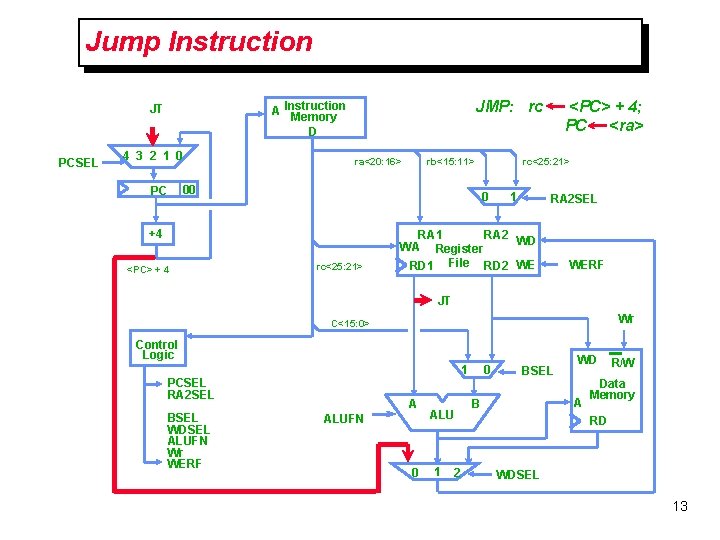

Jump Instruction PCSEL JMP: rc A Instruction Memory D JT 4 3 2 1 0 PC ra<20: 16> rb<15: 11> 00 <PC> + 4 rc<25: 21> 0 +4 rc<25: 21> <PC> + 4; PC <ra> 1 RA 2 SEL RA 1 RA 2 WD WA Register RD 1 File RD 2 WE WERF JT Wr C<15: 0> Control Logic 1 PCSEL RA 2 SEL BSEL WDSEL ALUFN Wr WERF A ALUFN 0 ALU 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 13

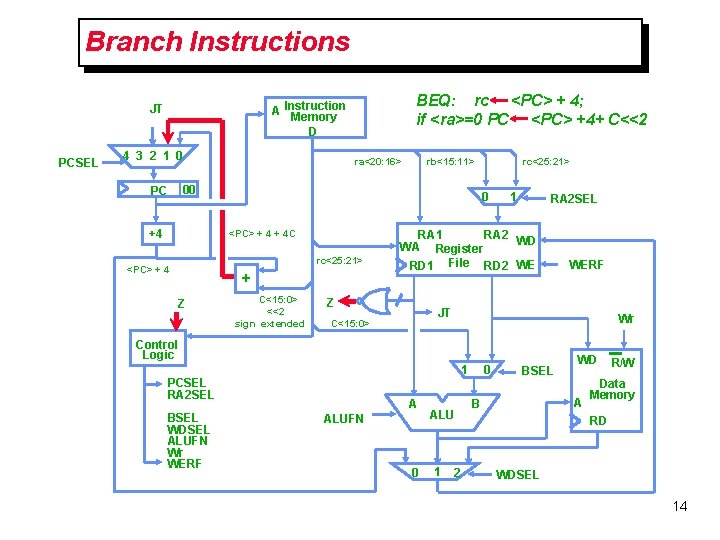

Branch Instructions PCSEL BEQ: rc <PC> + 4; if <ra>=0 PC <PC> +4+ C<<2 A Instruction Memory D JT 4 3 2 1 0 ra<20: 16> rb<15: 11> 00 PC +4 0 <PC> + 4 C rc<25: 21> <PC> + 4 + Z rc<25: 21> C<15: 0> <<2 sign extended 1 RA 2 SEL RA 1 RA 2 WD WA Register RD 1 File RD 2 WE Z JT C<15: 0> Wr Control Logic 1 PCSEL RA 2 SEL BSEL WDSEL ALUFN Wr WERF A ALUFN 0 ALU 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 14

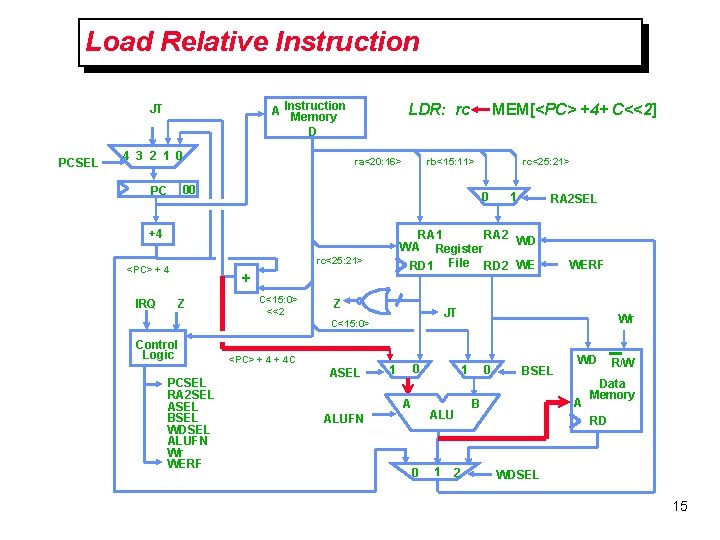

Load Relative Instruction A Instruction Memory D JT PCSEL 4 3 2 1 0 LDR: rc ra<20: 16> rb<15: 11> 00 PC + Z C<15: 0> <<2 Z PCSEL RA 2 SEL ASEL BSEL WDSEL ALUFN Wr WERF <PC> + 4 C ASEL RA 2 SEL WERF JT C<15: 0> Control Logic 1 RA 2 WD WA Register RD 1 File RD 2 WE rc<25: 21> <PC> + 4 rc<25: 21> 0 +4 IRQ MEM[<PC> +4+ C<<2] 0 1 ALU ALUFN 0 Wr 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 15

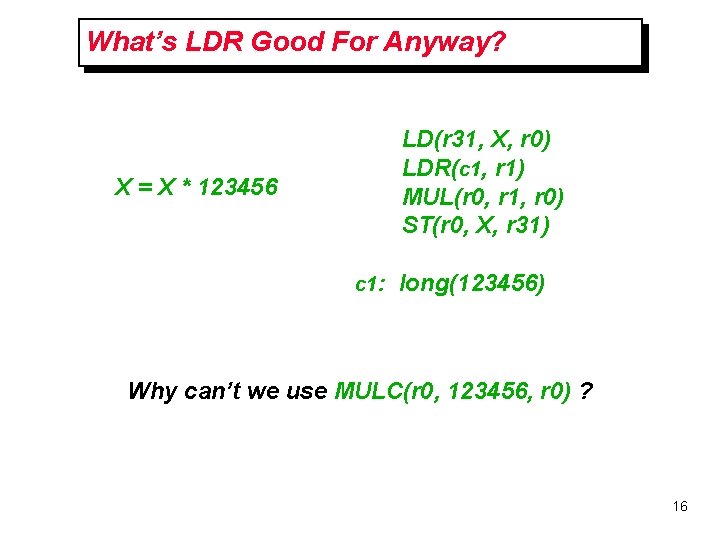

What’s LDR Good For Anyway? LD(r 31, X, r 0) LDR(c 1, r 1) MUL(r 0, r 1, r 0) ST(r 0, X, r 31) X = X * 123456 c 1: long(123456) Why can’t we use MULC(r 0, 123456, r 0) ? 16

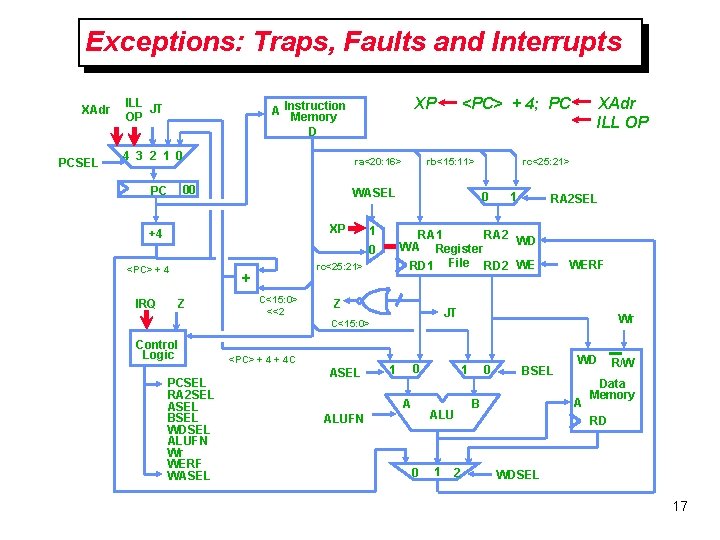

Exceptions: Traps, Faults and Interrupts XAdr PCSEL ILL JT OP XP A Instruction Memory D 4 3 2 1 0 ra<20: 16> 00 PC XP 1 rc<25: 21> + Z C<15: 0> <<2 0 Z PCSEL RA 2 SEL ASEL BSEL WDSEL ALUFN Wr WERF WASEL <PC> + 4 C ASEL 1 RA 2 SEL WERF JT C<15: 0> Control Logic XAdr ILL OP rc<25: 21> RA 1 RA 2 WD WA Register RD 1 File RD 2 WE 0 IRQ rb<15: 11> WASEL +4 <PC> + 4; PC 0 1 ALU ALUFN 0 Wr 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 17

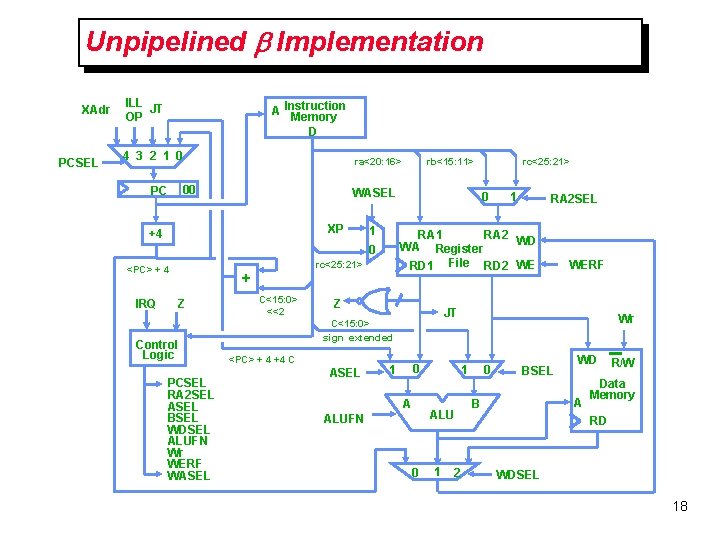

Unpipelined b Implementation XAdr PCSEL ILL JT OP A Instruction Memory D 4 3 2 1 0 ra<20: 16> 00 PC WASEL XP +4 1 0 IRQ + Z Control Logic PCSEL RA 2 SEL ASEL BSEL WDSEL ALUFN Wr WERF WASEL C<15: 0> <<2 0 Z ASEL 1 RA 2 SEL WERF JT C<15: 0> sign extended <PC> + 4 +4 C rc<25: 21> RA 1 RA 2 WD WA Register RD 1 File RD 2 WE rc<25: 21> <PC> + 4 rb<15: 11> 0 1 ALU ALUFN 0 Wr 1 2 0 BSEL WD A B R/W Data Memory RD WDSEL 18

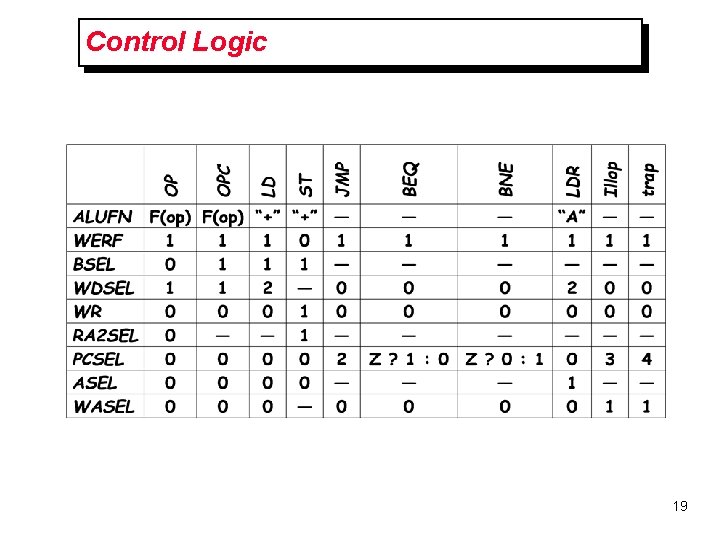

Control Logic 19

Next Time: Pipelined b Processor Dilbert : S. Adams 20

- Slides: 20