BUDAPESTI MSZAKI S GAZDASGTUDOMNYI EGYETEM VILLAMOSMRNKI S INFORMATIKAI

BUDAPESTI MŰSZAKI ÉS GAZDASÁGTUDOMÁNYI EGYETEM VILLAMOSMÉRNÖKI ÉS INFORMATIKAI KAR MÉRÉSTECHNIKA ÉS INFORMÁCIÓS RENDSZEREK TANSZÉK Az FPGA-k technológiai fejlődése Fehér Béla BME MIT FPGA laboratórium BME-MIT FPGA labor

Komplex programozható eszközök • 80 -as évek közepe a félvezetőipar fejlődésében az egyik legdinamikusabb korszak – Felhasználói igények folyamatosan nőttek • Nagyobb logikai és interfész kapacitás – Technológiai lehetőségek folyamatosan bővültek • Integráltság növelhető (Moore törvény) • Két megközelítés (a programozható áramkörökre) – Programozhatóság → Komplexitás CPLD – Komplexitás → Programozhatóság FPGA BME-MIT FPGA labor

Komplexitás → Programozhatóság • Hagyományos technológia – Felhasználói igények figyelembevétele • MPGA Maszk Programozott áramkör • Moore törvény hatása a PLD piacon – Tranzisztor költsége, mértete folyamatosan csökken – Redundancia, áramköri költség növelhető • Piacra jutási idő jelentősége nő – Prototípus, kis sorozat, induló termék – „Time to Market” BME-MIT FPGA labor

FPGA • Field Programmable Gate Array – 1984 Xilinx megalapítása • Ross Freeman feltaláló • Bernie Vonderschmitt „fabless company idea” • Jim Barnett csendestárs? ? • 1985 XC 2064 – 64 logikai cella • LUT + DFF – ~50 I/O – 5 V, 50 MHz „toggle rate” BME-MIT FPGA labor

FPGA technológiák • Felhasználó általi programozhatóság – Egyszer, nem javíthatóan (max. inkrementális jav. ) – Többször, de csak törlés után – Minden induláskor • Automatikusan master módban, vagy külső vezérlés alatt, slave módban – Működés közben • Teljes konfiguráció átkapcsolása ( indulási + egyéb) • Részleges, dinamikus átkonfigurálás BME-MIT FPGA labor

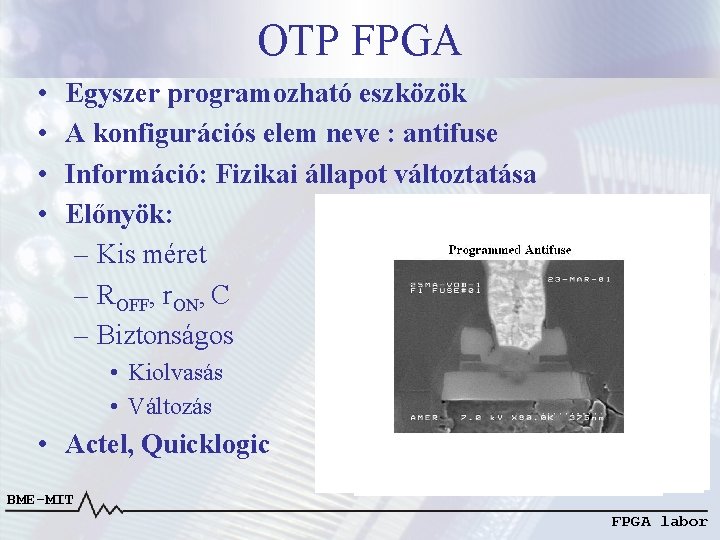

OTP FPGA • • Egyszer programozható eszközök A konfigurációs elem neve : antifuse Információ: Fizikai állapot változtatása Előnyök: – Kis méret – ROFF, r. ON, C – Biztonságos • Kiolvasás • Változás • Actel, Quicklogic BME-MIT FPGA labor

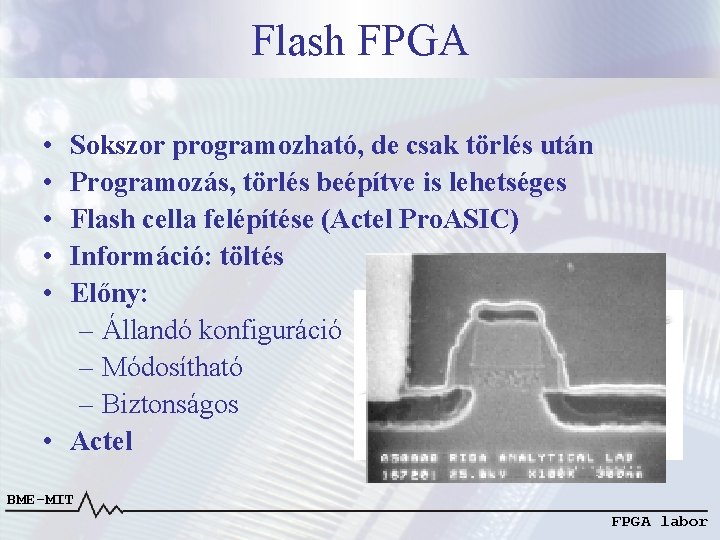

Flash FPGA • • • Sokszor programozható, de csak törlés után Programozás, törlés beépítve is lehetséges Flash cella felépítése (Actel Pro. ASIC) Információ: töltés Előny: – Állandó konfiguráció – Módosítható – Biztonságos • Actel BME-MIT FPGA labor

SRAM FPGA • A „hagyományos” FPGA megvalósítási elv • A legáltalánosabb CMOS technológia • Minden információ memória cellákban – Beolvasandó, betöltendő • Előny: – Bármikor átprogramozható – Olcsó technológia – Mindig a legjobb felbontás • Konfiguráció megváltozhat – Kozmikus sugárzás – SEU, egyedi változás BME-MIT FPGA labor

Értékelés technológia alapján • Technológia alapján (2017) – Elérhető komplexitásban az SRAM verhetetlen • Intel/Altera Stratix 10 14 nm 5. 5 millió LE • Xilinx Virtex Ultra. Scale+ 16 nm 3. 6 millió LC – Sebesség • Blokkok 600 - 700 MHz, rendszer 400 – 500 MHz – Tokozás, lábszám, interfészek SRAM • 1000 – 2800 láb BGA tokok • Speciális interfészek SERDES, DDR 4, HBM, PCIe Gen 3/Gen 4, 100 GE, 150 G Interlaken, BME-MIT FPGA labor

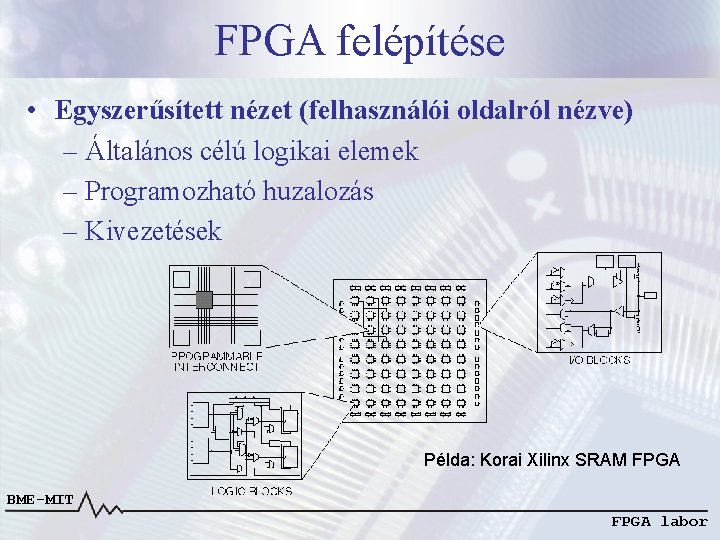

FPGA felépítése • Egyszerűsített nézet (felhasználói oldalról nézve) – Általános célú logikai elemek – Programozható huzalozás – Kivezetések Példa: Korai Xilinx SRAM FPGA BME-MIT FPGA labor

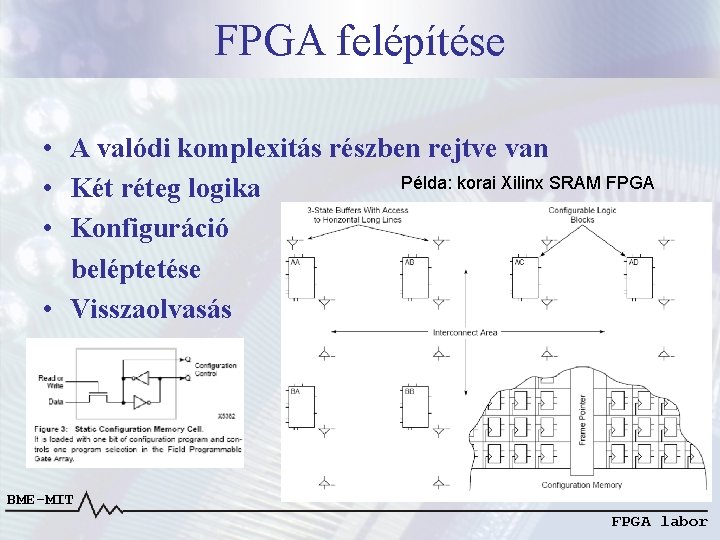

FPGA felépítése • A valódi komplexitás részben rejtve van Példa: korai Xilinx SRAM FPGA • Két réteg logika • Konfiguráció beléptetése • Visszaolvasás BME-MIT FPGA labor

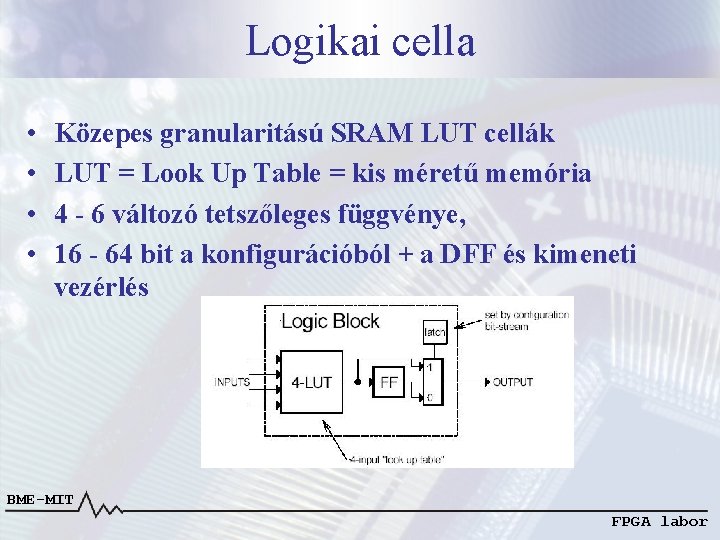

Logikai cella • • Közepes granularitású SRAM LUT cellák LUT = Look Up Table = kis méretű memória 4 - 6 változó tetszőleges függvénye, 16 - 64 bit a konfigurációból + a DFF és kimeneti vezérlés BME-MIT FPGA labor

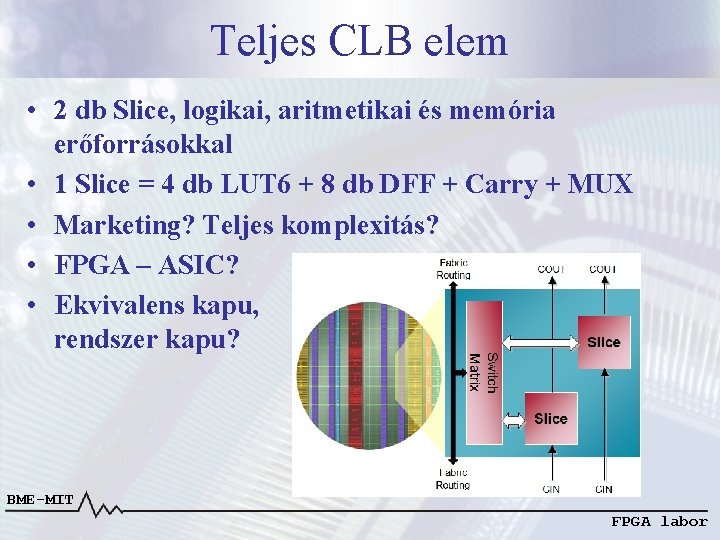

Teljes CLB elem • 2 db Slice, logikai, aritmetikai és memória erőforrásokkal • 1 Slice = 4 db LUT 6 + 8 db DFF + Carry + MUX • Marketing? Teljes komplexitás? • FPGA – ASIC? • Ekvivalens kapu, rendszer kapu? BME-MIT FPGA labor

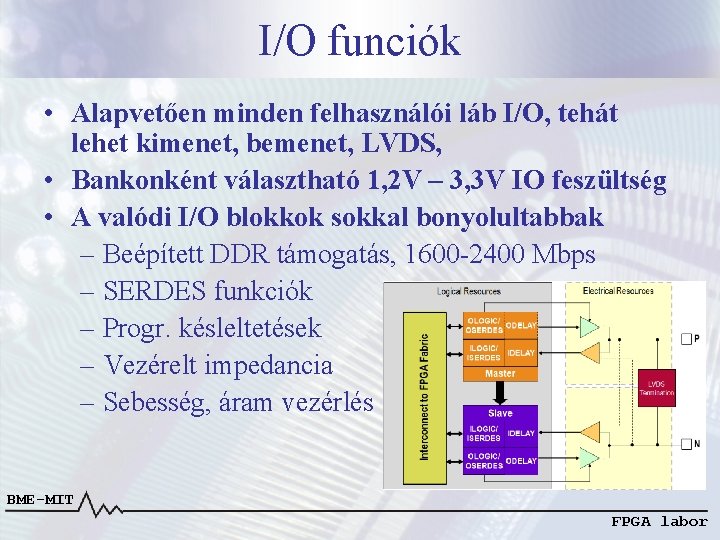

I/O funciók • Alapvetően minden felhasználói láb I/O, tehát lehet kimenet, bemenet, LVDS, • Bankonként választható 1, 2 V – 3, 3 V IO feszültség • A valódi I/O blokkok sokkal bonyolultabbak – Beépített DDR támogatás, 1600 -2400 Mbps – SERDES funkciók – Progr. késleltetések – Vezérelt impedancia – Sebesség, áram vezérlés BME-MIT FPGA labor

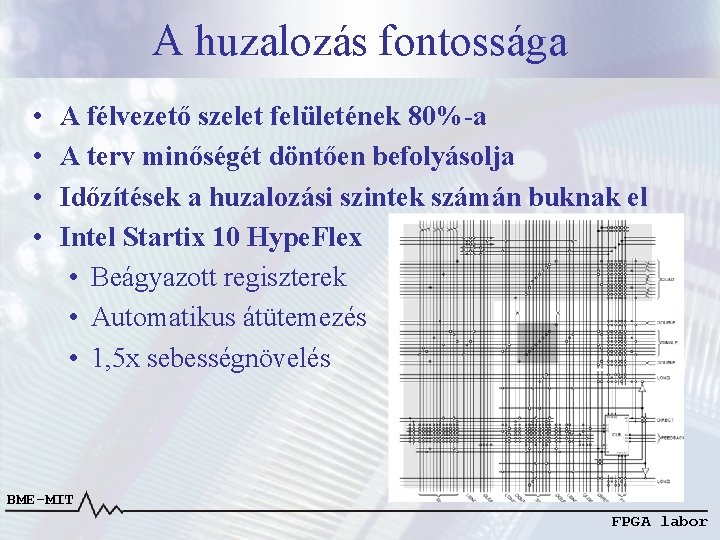

A huzalozás fontossága • • A félvezető szelet felületének 80%-a A terv minőségét döntően befolyásolja Időzítések a huzalozási szintek számán buknak el Intel Startix 10 Hype. Flex • Beágyazott regiszterek • Automatikus átütemezés • 1, 5 x sebességnövelés BME-MIT FPGA labor

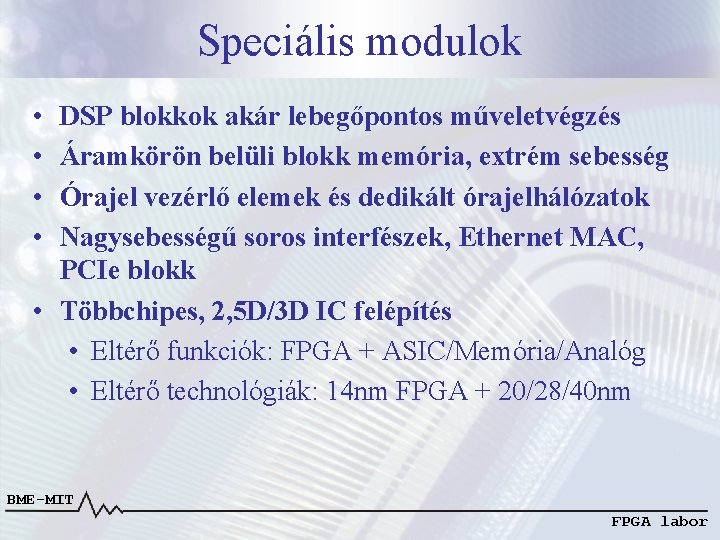

Speciális modulok • • DSP blokkok akár lebegőpontos műveletvégzés Áramkörön belüli blokk memória, extrém sebesség Órajel vezérlő elemek és dedikált órajelhálózatok Nagysebességű soros interfészek, Ethernet MAC, PCIe blokk • Többchipes, 2, 5 D/3 D IC felépítés • Eltérő funkciók: FPGA + ASIC/Memória/Analóg • Eltérő technológiák: 14 nm FPGA + 20/28/40 nm BME-MIT FPGA labor

Technológiai összefoglalás • Komplex rendszerek tervezéséhez különböző eszközeink vannak, ezek egyike az FPGA • Közepes, vagy kis sorozatoknál nem gazdaságos egyedi ASIC fejlesztése (idő, pénz, munka) • FPGA-k rugalmasan alkalmazhatók, gyors tervezés, megvalósítás, módosíthatóság, • Egyedi előnyök, alkalmazásfüggő specialitások – Nagy komplexitás – Nagy sebesség NEM EGYSZERRE! – Kis fogyasztás BME-MIT FPGA labor

FPGA-k az oktatásban • A tetszőlegesen programozható/konfigurálható áramkör tulajdonságai igen kedvezőek • Kis induló költség, többszöri újrahasználhatóság • Letöltés után azonnali működtethetőség, hibakeresés, javítás, újra fordítás, tesztelés • KIVÁLÓ OKTATÁSI PLATFORM • A digitális rendszertervezés minden lehetséges alkalmazási területén jól használható • Bizonyos értelemben a valódi VLSI áramkörtervezés sok területét is jól modellezi BME-MIT FPGA labor

A technológia megjelenése • A kezdetek: ~ 1990 FMFA (Felsőoktatási Műszaki Fejlesztési Alap) pályázat, több felsőoktatási intézmény együttes bevonásával (BME, …) • Xilinx 2000/3000 -es sorozatú demokártyák és áramkörök közvetlen fejlesztésekre BME-MIT FPGA labor

Eszközháttér • Az EDA technológia elemei: • DASH kapcsolási rajz szerkesztő • Hierarchikus tervezés, makro blokkok • Xilinx XACT • Áramkör generálás, elhelyezés, huzalozás, konfigurációs fájl generálás • Simu. CAD szimulátor • Logikai és időzítés szimuláció BME-MIT FPGA labor

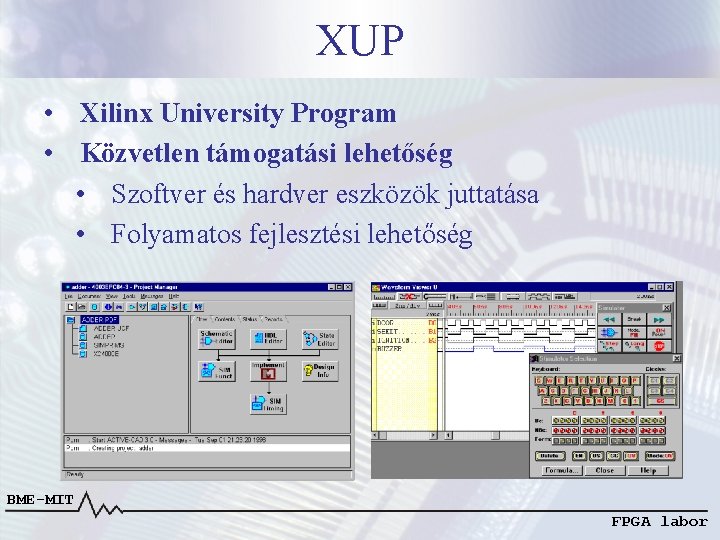

XUP • Xilinx University Program • Közvetlen támogatási lehetőség • Szoftver és hardver eszközök juttatása • Folyamatos fejlesztési lehetőség BME-MIT FPGA labor

FPGA-k az oktatásban • Kezdetben önálló laboratóriumi projektek • Első diplomatervek: 1992 • Algoritmusok hardver megvalósítása • Digitális aritmetika tetszőleges adatformátummal • Digitális jelfeldolgozás, szűrők, transzformációk • Mérőeszközök, áramkörök flexibilis kialakítása • Perifériaillesztők, egyedi perifériák • Képfeldolgozás, megjelenítők BME-MIT FPGA labor

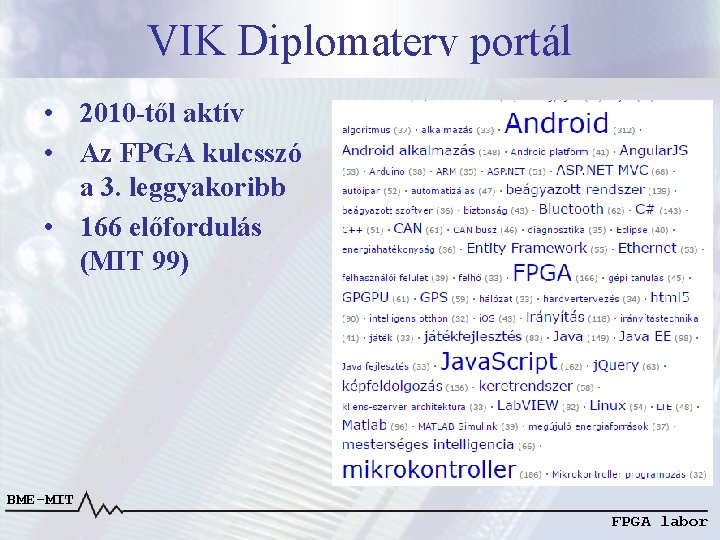

VIK Diplomaterv portál • 2010 -től aktív • Az FPGA kulcsszó a 3. leggyakoribb • 166 előfordulás (MIT 99) BME-MIT FPGA labor

FPGA-k az oktatásban • A MIT oktatási portfóliójába teljes mértékben beilleszthető • Mérés és rendszertervezés szakirány, 5 éves képzés • Logikai tervezés tárgy 1993 – Digitális rendszertervezés – Mikroprocesszoros rendszerek – Programozható áramkörök 30% BME-MIT FPGA labor

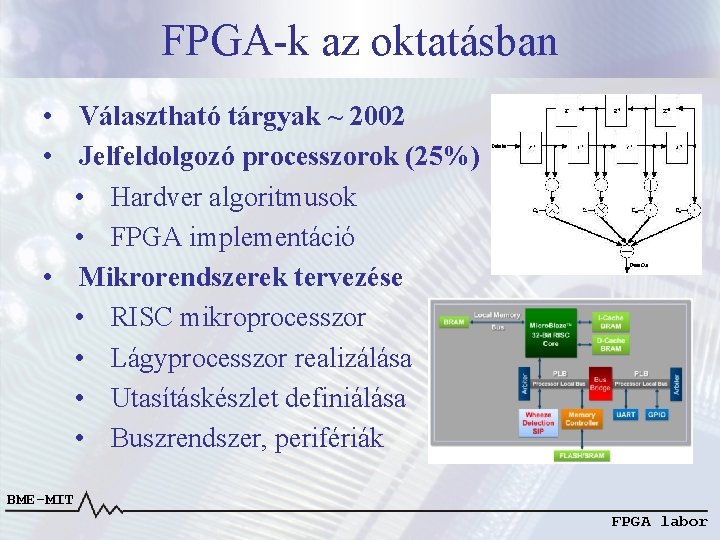

FPGA-k az oktatásban • Választható tárgyak ~ 2002 • Jelfeldolgozó processzorok (25%) • Hardver algoritmusok • FPGA implementáció • Mikrorendszerek tervezése • RISC mikroprocesszor • Lágyprocesszor realizálása • Utasításkészlet definiálása • Buszrendszer, perifériák BME-MIT FPGA labor

Mellékszakirány • Programozható logikai eszközök alkalmazástechnológiája • Indult 2008 -ban, az egyik legnépszerűbb, ~50 hallg. • Tárgyak: • Logikai tervezés • Mikrorendszerek tervezése • Heterogén számítási rendszerek • FPGA tervezői laboratórium BME-MIT FPGA labor

LOGSYS FPGA kártyák • Hallgatói projektként indult 2002 -ben • Résztvevők: • Molnár Gábor, Fülöp Tamás 2002 • Kis Gergely, Márton Tibor, Zigó Attila 2004 • Czakó Péter, Laczkó Péter 2007 • Fejér Attila 2014 • Raikovich Tamás 2007 – 2017 • Egyszerű demo alkalmazások, összetett projektek • Széleskörű használat BME-MIT FPGA labor

LOGSYS FPGA kártyák • Teljes laboratóriumi eszközháttér • Hardver alapkártyák Spartan 3 E, Spartan 6 • Kiegészítő modulok (VGA, Audio, Ethernet, …) • LOGSYS GUI szoftver alkalmazás • • USB táp JTAG konfig. UART komm. CLK/RST BME-MIT FPGA labor

LOGSYS FPGA-KINTEX 7 kártya • • A projekt keretében kifejlesztett FPGA kártya Minden oktatási feladatra alkalmas Digitális rendszerek (Multi) Processzoros rendszerek • Nagysebességű HW gyorsító eszköz • Dinamikus átkonfigurálás • Partnerek: NHIT, NI BME-MIT FPGA labor

Összefoglalás • Az FPGA labor munkatársai • Szántó Péter, • Raikovich Tamás, • Wacha Gábor • Lazányi János (2015 -ig) • Doktorandusz hallgatók • Szedő Gábor, Antoni Lőrinc, Széll András, Dancsi György, Pechan Imre, Laczkó Péter, Kiss Gergely, Szikra István, BME-MIT FPGA labor

- Slides: 30