Breakout Session Controls Physics Requirements and Technology Choices

Breakout Session: Controls Physics Requirements and Technology Choices for LCLS Instrumentation & Controls October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Accelerator Physics Driving Controls Design Precision beams • Low emittance • Short bunch Single pass Every shot different Compatibility • Other programs • Old controls Simultaneous Single shot Read all devices PS control Process/respond in < 1/120 th sec. • Timing distribution • RF Phase control Applications • Machine tuning Feedback • Trajectory • Bunch length • Energy October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Critical design choices for instrumentation Power supply control and regulation Stability and latency time for fast feedback control Beam position monitor signal processing Resolution, drift, calibration Timing distribution Precision, stability, synchronization, SLC compatibility RF stabilization Beam based feedback Single-shot CSR bunch length monitors October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Power supply system requirements Stability requirements 10 ppm in the chicane bends Response time Low control-system latency for feedback <1 ms Commercial components Reliability October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

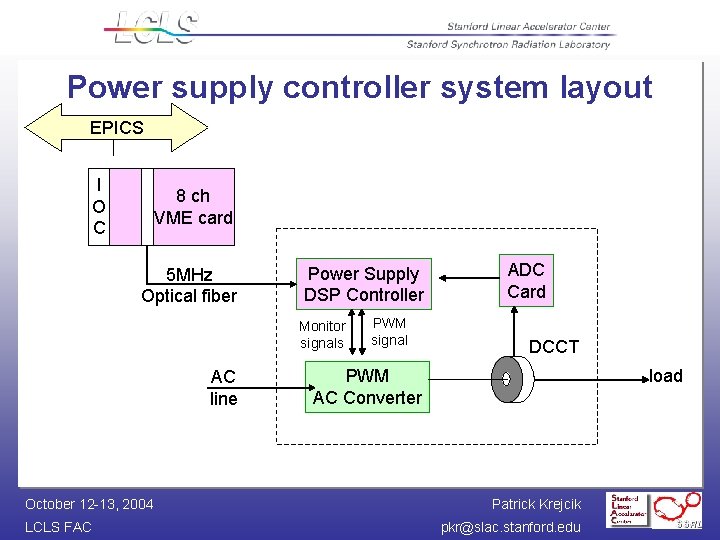

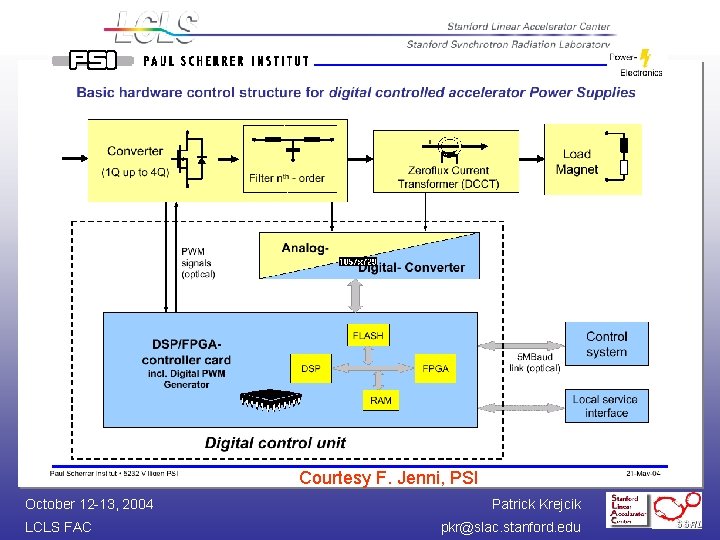

Digital PS controller developed by SLS PWM digital regulation loop controls AC converter power module PWM is a digital process already Avoids unnecessary digital => analog => digital conversion Only source of drift in an all digital system is ADC reference voltage High-speed links, minimal latency Fully developed at SLS with proven performance Fully integrated into EPICS controls Now adopted by several large accelerator projects, including Diamond Light Source October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Power supply controller system layout EPICS I O C 8 ch VME card 5 MHz Optical fiber Power Supply DSP Controller Monitor signals AC line October 12 -13, 2004 LCLS FAC PWM signal ADC Card DCCT load PWM AC Converter Patrick Krejcik pkr@slac. stanford. edu

Courtesy F. Jenni, PSI October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

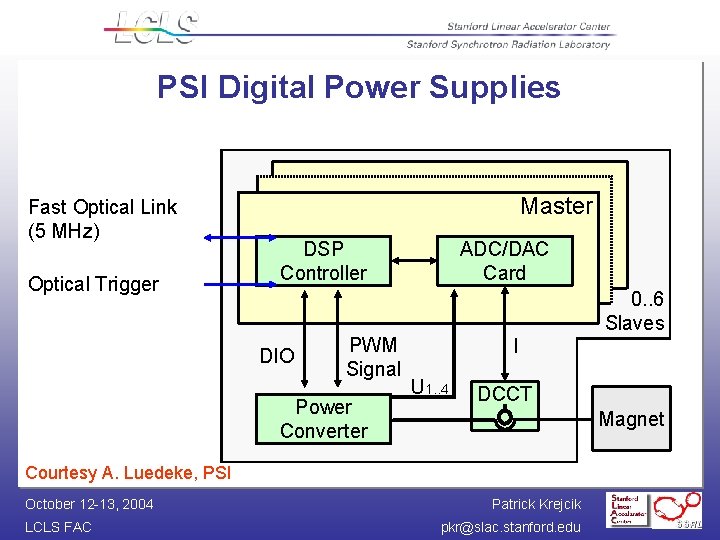

PSI Digital Power Supplies Fast Optical Link (5 MHz) Optical Trigger Master DSP Controller DIO PWM Signal Power Converter ADC/DAC Card 0. . 6 Slaves I U 1. . 4 DCCT Magnet Courtesy A. Luedeke, PSI October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

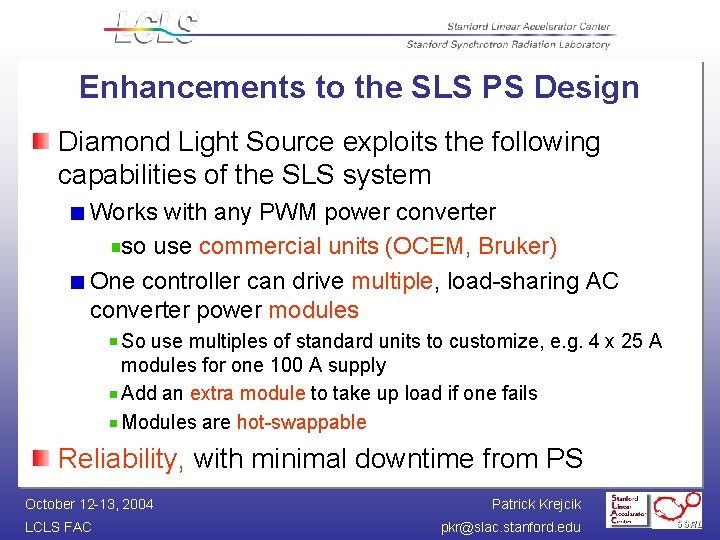

Enhancements to the SLS PS Design Diamond Light Source exploits the following capabilities of the SLS system Works with any PWM power converter so use commercial units (OCEM, Bruker) One controller can drive multiple, load-sharing AC converter power modules So use multiples of standard units to customize, e. g. 4 x 25 A modules for one 100 A supply Add an extra module to take up load if one fails Modules are hot-swappable Reliability, with minimal downtime from PS October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

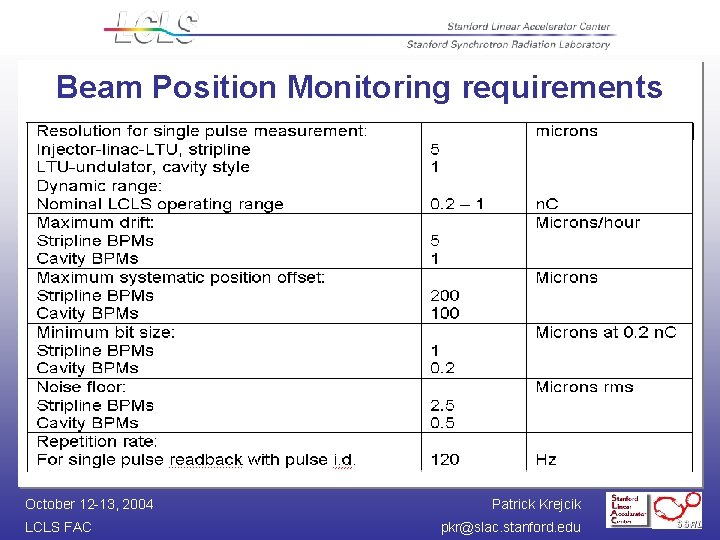

Beam Position Monitoring requirements October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

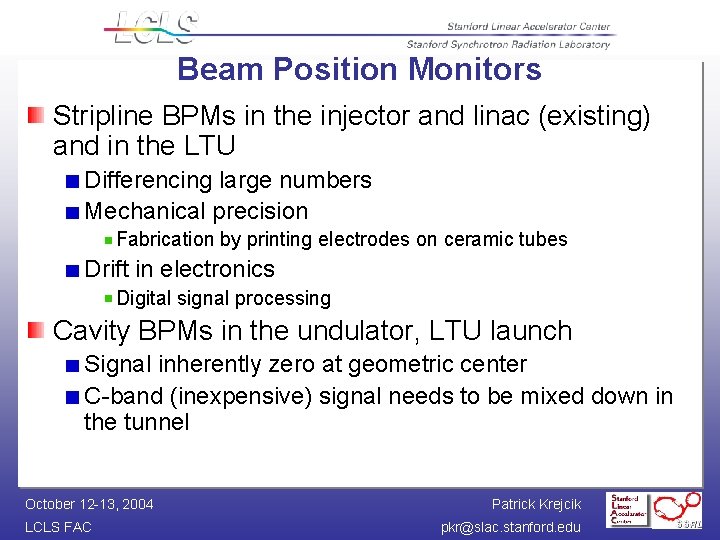

Beam Position Monitors Stripline BPMs in the injector and linac (existing) and in the LTU Differencing large numbers Mechanical precision Fabrication by printing electrodes on ceramic tubes Drift in electronics Digital signal processing Cavity BPMs in the undulator, LTU launch Signal inherently zero at geometric center C-band (inexpensive) signal needs to be mixed down in the tunnel October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

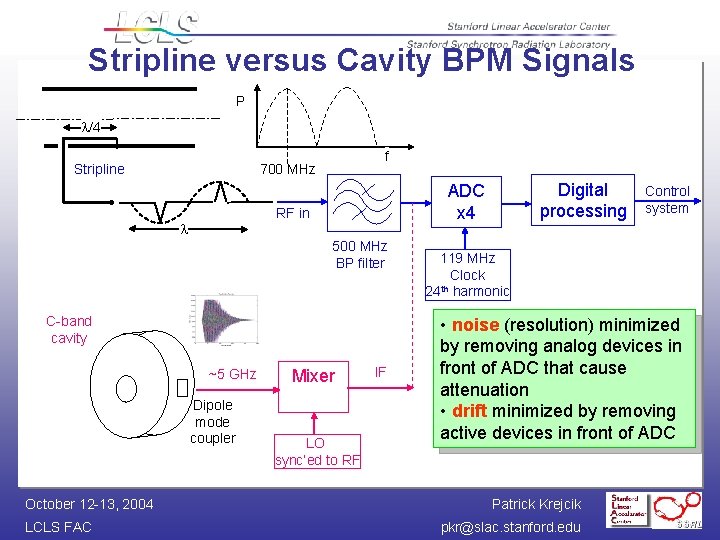

Stripline versus Cavity BPM Signals P l/4 Stripline f 700 MHz RF in l 500 MHz BP filter C-band cavity ~5 GHz Dipole mode coupler October 12 -13, 2004 LCLS FAC Digital processing ADC x 4 Mixer LO sync’ed to RF IF Control system 119 MHz Clock 24 th harmonic • noise (resolution) minimized by removing analog devices in front of ADC that cause attenuation • drift minimized by removing active devices in front of ADC Patrick Krejcik pkr@slac. stanford. edu

Simplistic View of Digital BPMs Is the purely digital approach the best way to go? Must always maximize signal to noise for best resolution So minimize any cause of attenuation: couplers, hybrids, active devices etc. This also eliminates drift which causes offsets Other approaches also try to do this: e. g. AM to PM conversion with a hybrid and then digitize Might as well digitize first, eliminate the middle men, and do the conversions digitally Ultimately left with calibrating the drift in the BPM cables, because ADCs are now very stable. October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

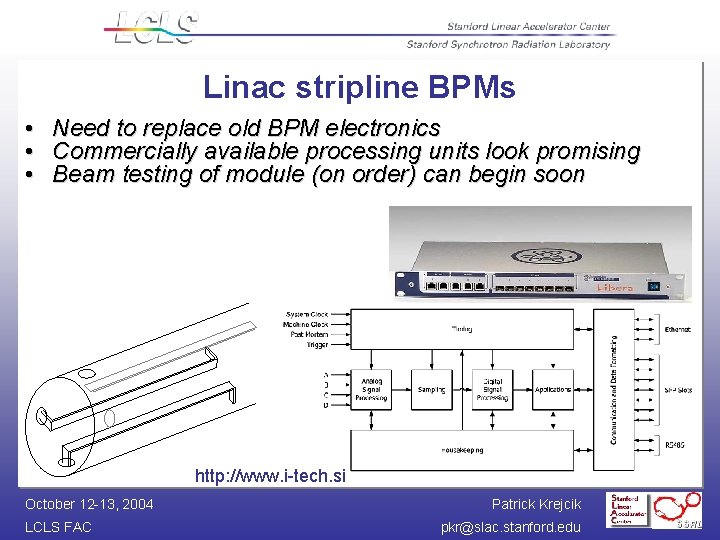

Linac stripline BPMs • • • Need to replace old BPM electronics Commercially available processing units look promising Beam testing of module (on order) can begin soon http: //www. i-tech. si October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

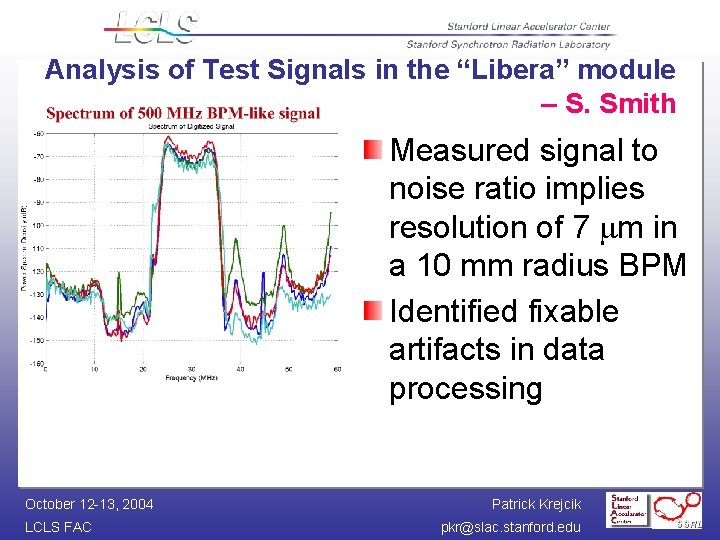

Analysis of Test Signals in the “Libera” module – S. Smith Measured signal to noise ratio implies resolution of 7 mm in a 10 mm radius BPM Identified fixable artifacts in data processing October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Pros and Cons of the Libera concept Complete, integrated commercial package which comes close to requirements RF processing, digitization, calibration, control software and feedback DSP all in one box Makes it hard for us get inside and tweak it Access to fast signals for feedback systems Difficult to provide timestamps and interrupts in their O/S Might be better to separate out the functions into different modules October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Fabricating a Digital BPM processor out of commercially available modules – Till Straumann RF filter, local oscillator and mixer stage VME based ADC board e. g. Joerger, Echotek handle 8 channels IOC Calculates signal amplitude & beam position, tmit. interfaces to EPICS, procedures for calibration, process feedback algorithm October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

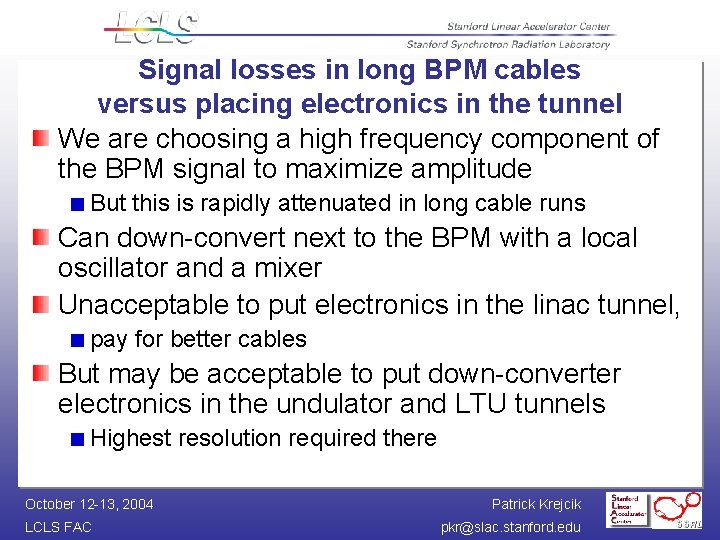

Signal losses in long BPM cables versus placing electronics in the tunnel We are choosing a high frequency component of the BPM signal to maximize amplitude But this is rapidly attenuated in long cable runs Can down-convert next to the BPM with a local oscillator and a mixer Unacceptable to put electronics in the linac tunnel, pay for better cables But may be acceptable to put down-converter electronics in the undulator and LTU tunnels Highest resolution required there October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

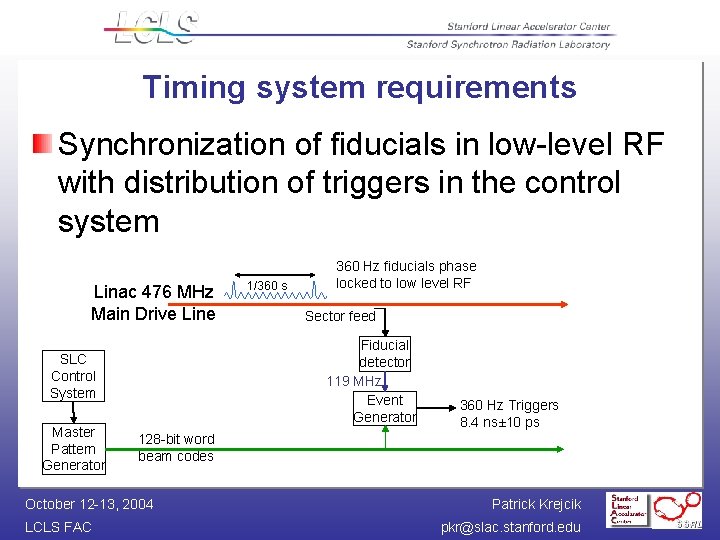

Timing system requirements Synchronization of fiducials in low-level RF with distribution of triggers in the control system Linac 476 MHz Main Drive Line 360 Hz Triggers 8. 4 ns± 10 ps 128 -bit word beam codes October 12 -13, 2004 LCLS FAC Sector feed Fiducial detector 119 MHz Event Generator SLC Control System Master Pattern Generator 1/360 s 360 Hz fiducials phase locked to low level RF Patrick Krejcik pkr@slac. stanford. edu

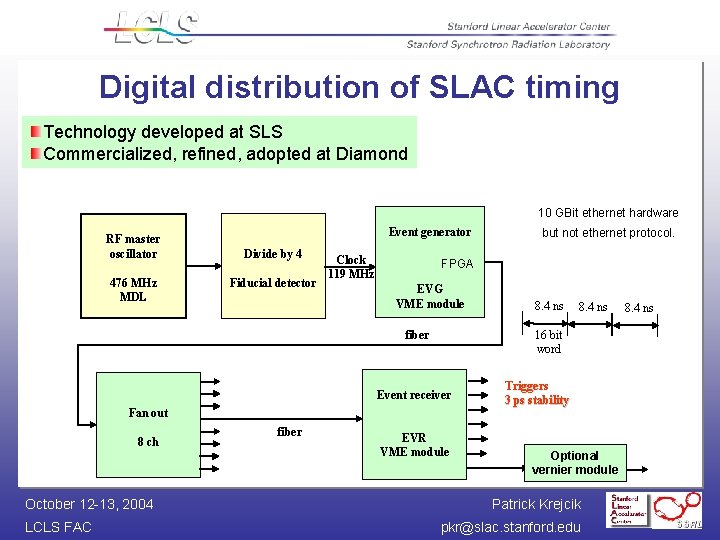

Digital distribution of SLAC timing Technology developed at SLS Commercialized, refined, adopted at Diamond 10 GBit ethernet hardware RF master oscillator 476 MHz MDL Event generator Divide by 4 Fiducial detector Clock 119 MHz FPGA EVG VME module fiber Fan out October 12 -13, 2004 LCLS FAC fiber 8. 4 ns 16 bit word Event receiver 8 ch but not ethernet protocol. EVR VME module Triggers 3 ps stability Optional vernier module Patrick Krejcik pkr@slac. stanford. edu 8. 4 ns

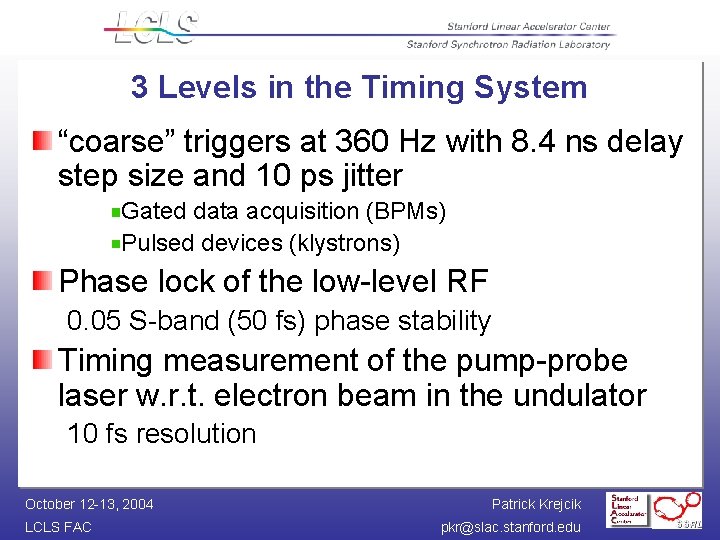

3 Levels in the Timing System “coarse” triggers at 360 Hz with 8. 4 ns delay step size and 10 ps jitter Gated data acquisition (BPMs) Pulsed devices (klystrons) Phase lock of the low-level RF 0. 05 S-band (50 fs) phase stability Timing measurement of the pump-probe laser w. r. t. electron beam in the undulator 10 fs resolution October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

LCLS Machine Stability Tolerance Budget From P. Emma: X-band X- RMS tolerance budget for <12% rms peak-current jitter or <0. 1% rms final e− energy jitter. All tolerances are rms levels and the voltage and phase tolerances per klystron for L 2 and L 3 are Nk larger, assuming uncorrelated errors, where Nk is the number of klystrons per linac. 125 fs tolerance on X-band system October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Energy and Bunch Length Feedback Loops E Vrf(L 1) Φrf(L 2) E Φrf(L 3) E DL 1 E Vrf(L 0) Φrf(L 1) sz DL 1 Spectr. L 1 L 0 Φrf(L 2) sz BC 2 BC 1 L 2 L 3 BSY 50 B 1 DL 2 Beam based feedback will stabilize RF F, A Against drift and jitter up to ~10 Hz But no diagnostic to distinguish drift of X-band Linearization, higher-harmonic RF has the tightest tolerance No unique beam measurement October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

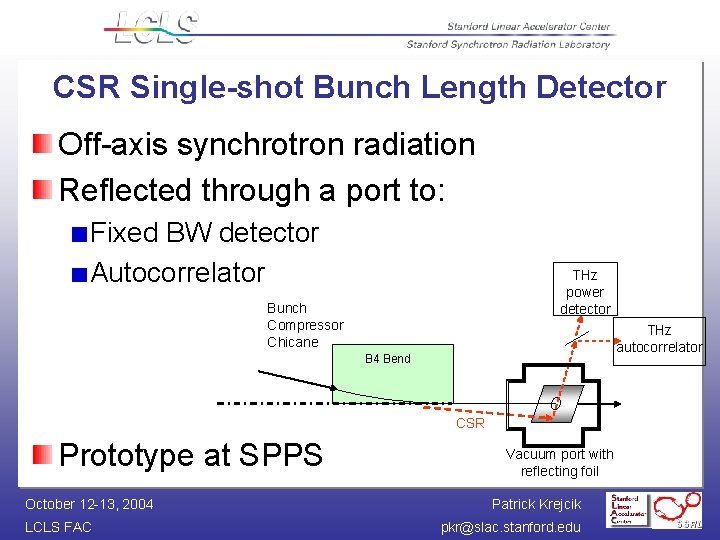

CSR Single-shot Bunch Length Detector Off-axis synchrotron radiation Reflected through a port to: Fixed BW detector Autocorrelator THz power detector Bunch Compressor Chicane THz autocorrelator B 4 Bend CSR Prototype at SPPS October 12 -13, 2004 LCLS FAC Vacuum port with reflecting foil Patrick Krejcik pkr@slac. stanford. edu

End of presentation! Additional backup material follows October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Linac type stripline BPMs Resolution achievable with existing processor New BPM processor design challenges: • large dynamic range • Low noise, high gain • 20 ps timing jitter limit LCLS range October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

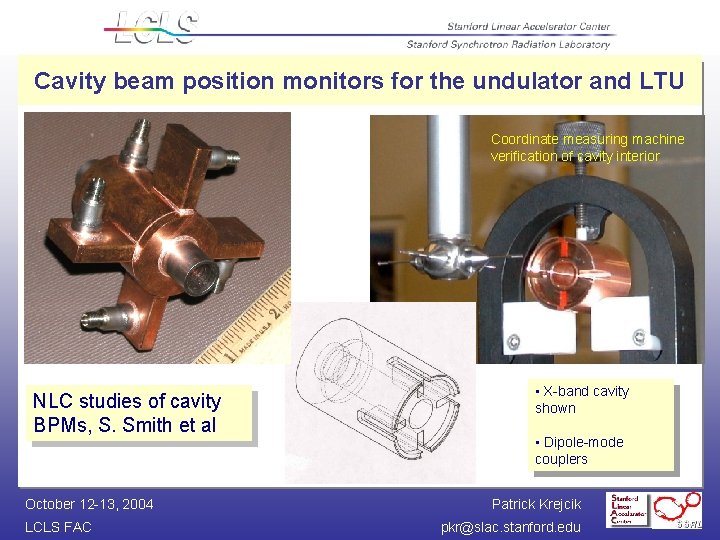

Cavity beam position monitors for the undulator and LTU R&D at SLAC – S. Smith NLC studies of cavity BPMs, S. Smith et al October 12 -13, 2004 LCLS FAC Coordinate measuring machine verification of cavity interior • X-band cavity shown • Dipole-mode couplers Patrick Krejcik pkr@slac. stanford. edu

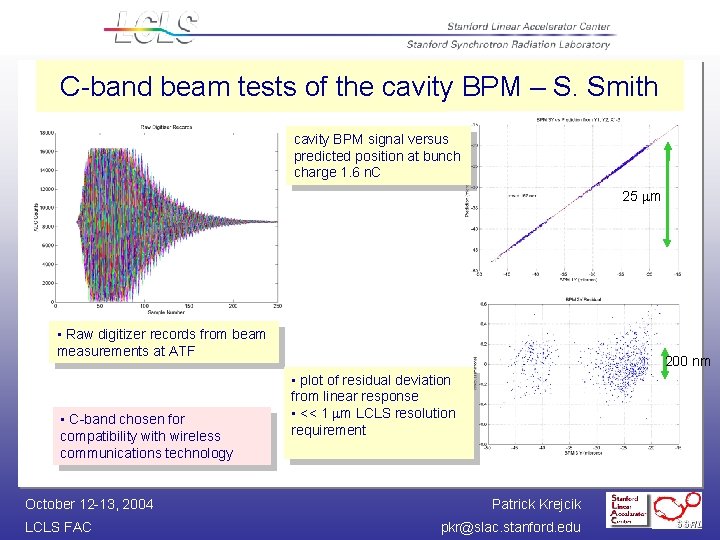

C-band beam tests of the cavity BPM – S. Smith cavity BPM signal versus predicted position at bunch charge 1. 6 n. C 25 mm • Raw digitizer records from beam measurements at ATF • C-band chosen for compatibility with wireless communications technology October 12 -13, 2004 LCLS FAC 200 nm • plot of residual deviation from linear response • << 1 mm LCLS resolution requirement Patrick Krejcik pkr@slac. stanford. edu

Synchronization of the Laser timing Jitter in the laser timing effects Electro optic bunch timing measurement Pump-probe timing for the users Enhancement schemes using short pulse lasers October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

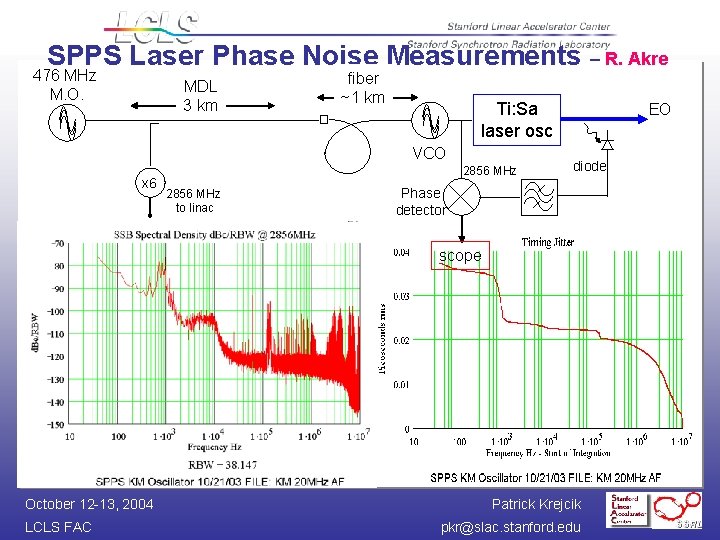

SPPS Laser Phase Noise Measurements – R. Akre 476 MHz M. O. MDL 3 km fiber ~1 km Ti: Sa laser osc VCO x 6 2856 MHz to linac EO diode Phase detector scope October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

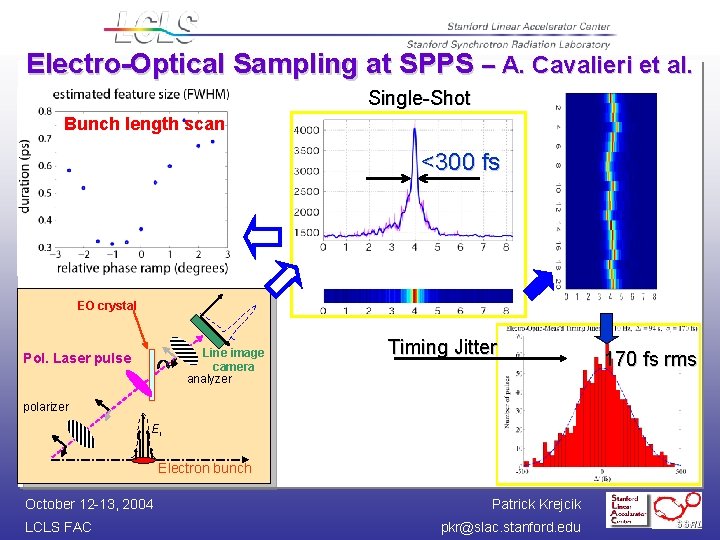

Electro-Optical Sampling at SPPS – A. Cavalieri et al. Single-Shot Bunch length scan <300 fs EO crystal Line image camera analyzer Pol. Laser pulse Timing Jitter polarizer Er Electron bunch October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu 170 fs rms

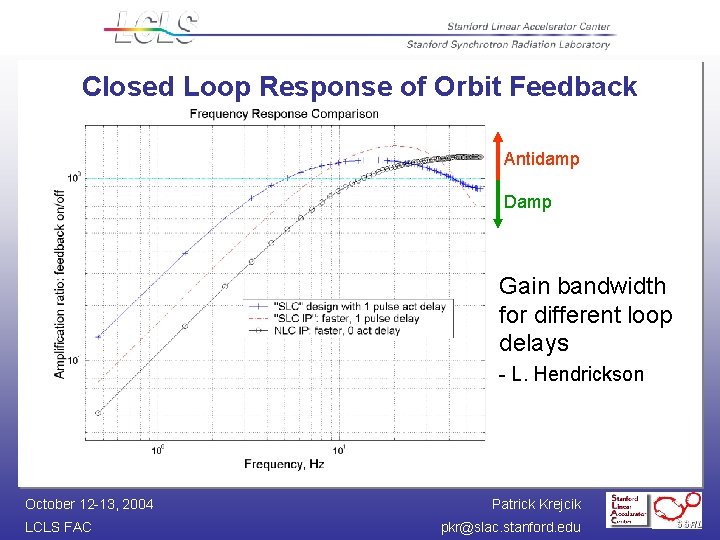

Closed Loop Response of Orbit Feedback Antidamp Damp Gain bandwidth for different loop delays - L. Hendrickson October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Control of Digital Power Supplies Andreas Lüdeke Swiss Light Source / PSI 20 May 2003 EPICS Collaboration Meeting October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

PSI Digital Power Supplies Andreas Lüdeke Fast Optical Link (5 MHz) Optical Trigger Master DSP Controller ADC/DAC Card PWM I DIO Signal U 1. . 4 DCCT Power Converter October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu 0. . 6 Slaves Magne t

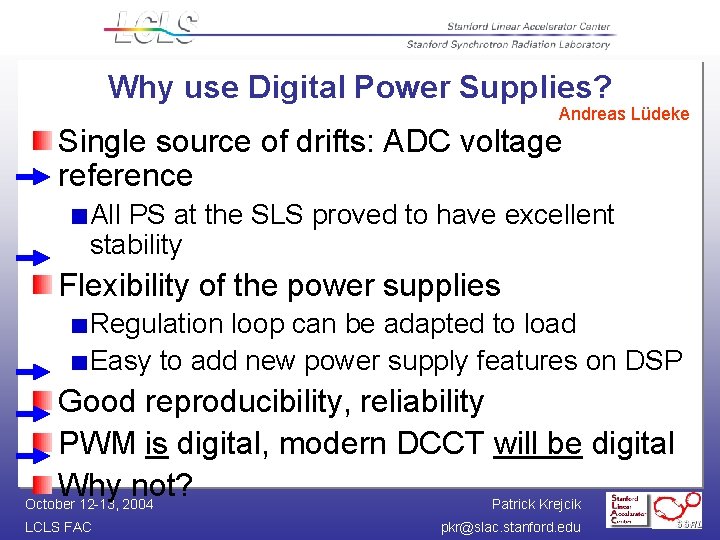

Why use Digital Power Supplies? Andreas Lüdeke Single source of drifts: ADC voltage reference All PS at the SLS proved to have excellent stability Flexibility of the power supplies Regulation loop can be adapted to load Easy to add new power supply features on DSP Good reproducibility, reliability PWM is digital, modern DCCT will be digital Why not? October 12 -13, 2004 Patrick Krejcik LCLS FAC pkr@slac. stanford. edu

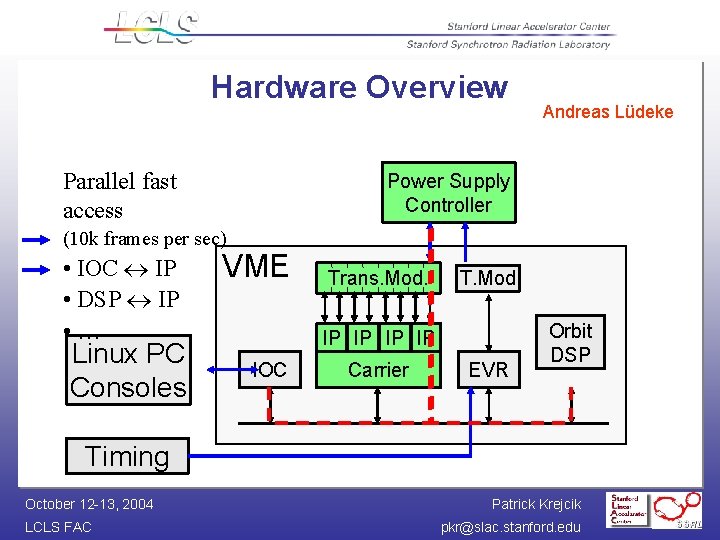

Hardware Overview Parallel fast access Andreas Lüdeke Power Supply Controller (10 k frames per sec) • IOC IP • DSP IP • … Linux PC Consoles VME Trans. Mod. T. Mod IP IP IOC Carrier EVR Orbit DSP Timing October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

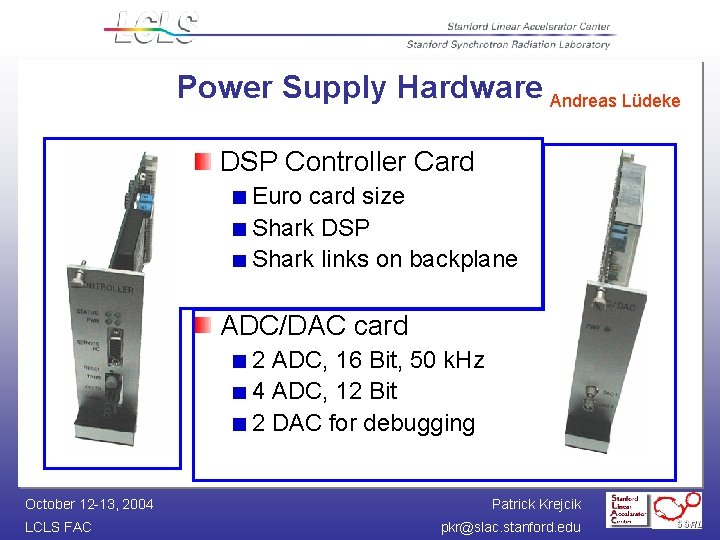

Power Supply Hardware Andreas Lüdeke DSP Controller Card Euro card size Shark DSP Shark links on backplane ADC/DAC card 2 ADC, 16 Bit, 50 k. Hz 4 ADC, 12 Bit 2 DAC for debugging October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

![Fast and precise ADC UADC [V] Andreas Lüdeke 10 µV 1 ppm 20 th Fast and precise ADC UADC [V] Andreas Lüdeke 10 µV 1 ppm 20 th](http://slidetodoc.com/presentation_image/bb4984ba94a663610c6f272d76fe4001/image-38.jpg)

Fast and precise ADC UADC [V] Andreas Lüdeke 10 µV 1 ppm 20 th Bit Umax 4. 7895 4. 7894 - 10 µV 4. 7893 1 k. Hz Filter 4. 7892 - 10 µV 4. 7891 - 40 µV 4. 789 Umin 4. 7889 4. 7888 0 200 400 600 800 1000 1200 33 min October 12 -13, 2004 LCLS FAC 1400 1600 1800 2000 t [s] Patrick Krejcik pkr@slac. stanford. edu 600 µV + 20 µV

VME Hardware Industry Pack Carrier VME 64 x 4 slot boards “off-the-shelf”: • Greenspring Vipc 664 • Hytec 8002 October 12 -13, 2004 LCLS FAC Andreas Lüdeke Industry Pack Module for 2 power supplies VME 64 x Transition module for 8 power supplies Patrick Krejcik pkr@slac. stanford. edu

DSP Software Andreas Lüdeke Local intelligence: 50 k. Hz pulse width modulation loop Sophisticated alarms, like change in load resistance Triggered current waveform (DSP ramp) Scaleable, arbitrary waveform 16000 times 80 µsec steps > 1 second waveform The same DSP program for all PS Locally stored parameter settings for each PS October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

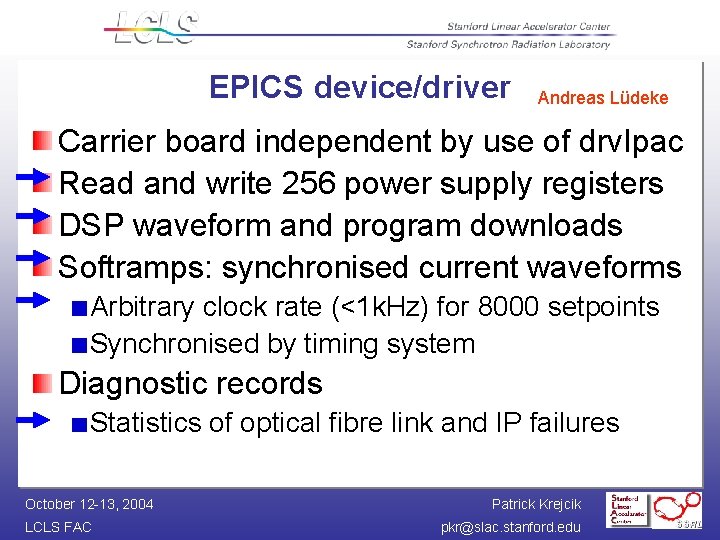

EPICS device/driver Andreas Lüdeke Carrier board independent by use of drv. Ipac Read and write 256 power supply registers DSP waveform and program downloads Softramps: synchronised current waveforms Arbitrary clock rate (<1 k. Hz) for 8000 setpoints Synchronised by timing system Diagnostic records Statistics of optical fibre link and IP failures October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

EPICS database Andreas Lüdeke One template for 500 power supplies Each power supply supports Download and save of DSP programs, parameter sets, DSP ID current waveform: download, scaling, offset, length, … reading max. and min. current from PS reading actual magnet resistance from controller. . . Magnet cycling configurable for each PS Detailed fault diagnostic for PS, link and driver October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Software Management Andreas Lüdeke DSP software is documented by Excel sheets Script transforms sheets into a C include file Easy upgrade of the driver for new PS functions Identical DSP and EPICS software for all PS Configuration by parameter set October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

Outlook Andreas Lüdeke PSI type digital PS are “en vogue” Each manufacturer can get a PSI licence Diamond will use exclusively digital PS for magnets Soleil is evaluating the PSI digital PS Industry Pack module can be used on CPCI Driver source can be reused for Tango Customized DSP programs For specific application To drive several PS with one DSP card October 12 -13, 2004 LCLS FAC Patrick Krejcik pkr@slac. stanford. edu

- Slides: 44