Breaking the Cost Barrier LowCost HighSpeed Programmable Solutions

Breaking the Cost Barrier Low-Cost, High-Speed Programmable Solutions No Compromises 1 Breaking the Cost Barrier

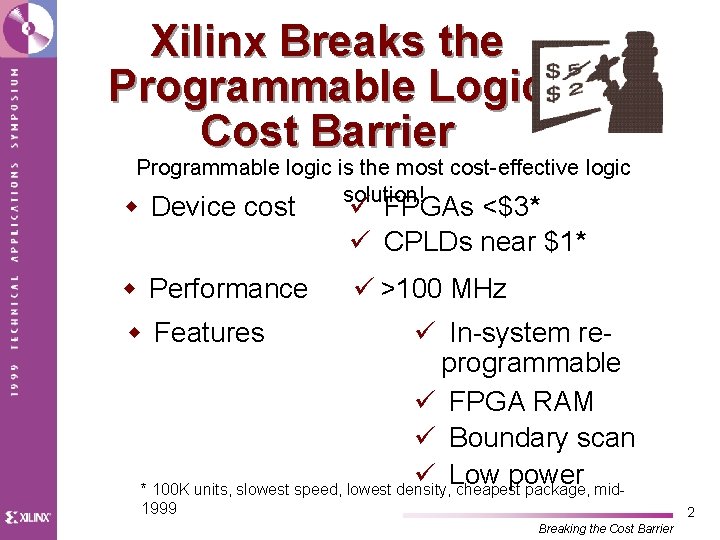

Xilinx Breaks the Programmable Logic Cost Barrier Programmable logic is the most cost-effective logic solution! w Device cost ü FPGAs <$3* ü CPLDs near $1* w Performance ü >100 MHz ü In-system reprogrammable ü FPGA RAM ü Boundary scan ü Low power * 100 K units, slowest speed, lowest density, cheapest package, mid- w Features 1999 2 Breaking the Cost Barrier

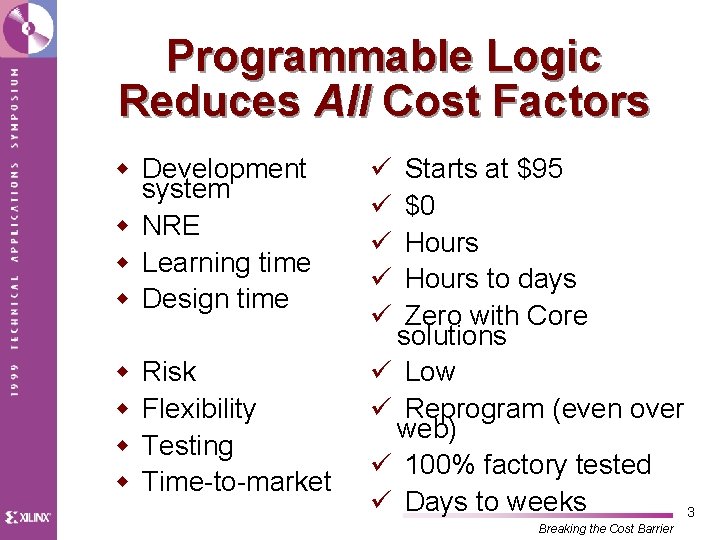

Programmable Logic Reduces All Cost Factors w Development system w NRE w Learning time w Design time w w Risk Flexibility Testing Time-to-market ü ü ü Starts at $95 $0 Hours to days Zero with Core solutions ü Low ü Reprogram (even over web) ü 100% factory tested ü Days to weeks 3 Breaking the Cost Barrier

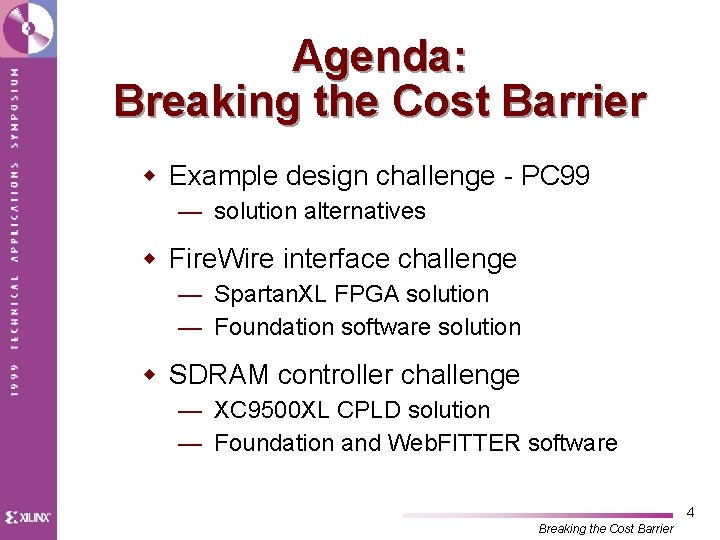

Agenda: Breaking the Cost Barrier w Example design challenge - PC 99 — solution alternatives w Fire. Wire interface challenge — Spartan. XL FPGA solution — Foundation software solution w SDRAM controller challenge — XC 9500 XL CPLD solution — Foundation and Web. FITTER software 4 Breaking the Cost Barrier

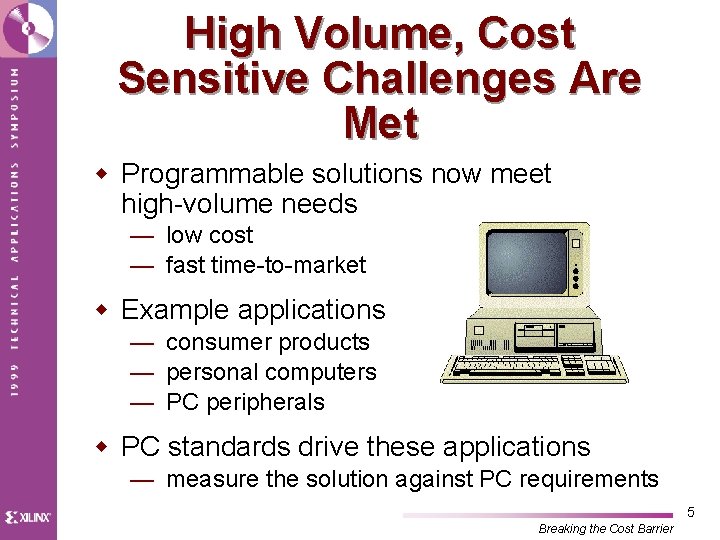

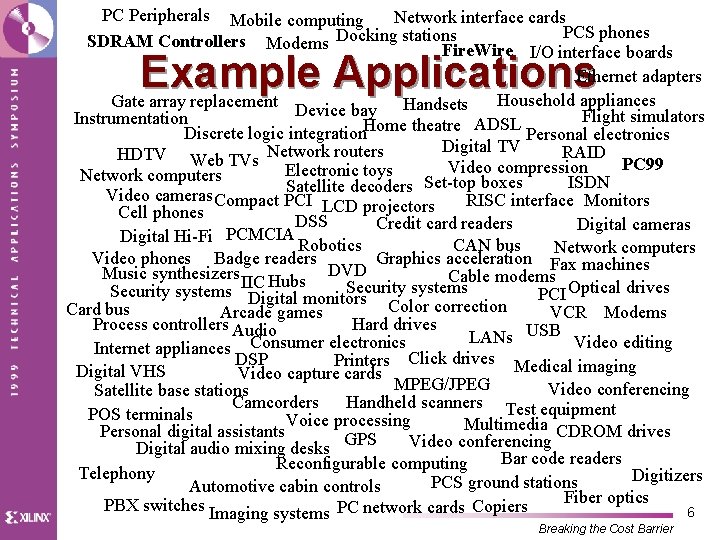

High Volume, Cost Sensitive Challenges Are Met w Programmable solutions now meet high-volume needs — low cost — fast time-to-market w Example applications — consumer products — personal computers — PC peripherals w PC standards drive these applications — measure the solution against PC requirements 5 Breaking the Cost Barrier

PC Peripherals Mobile computing Network interface cards PCS phones SDRAM Controllers Modems Docking stations Fire. Wire I/O interface boards Ethernet adapters Household appliances Gate array replacement Handsets Device bay Flight simulators Instrumentation ADSL Home theatre Discrete logic integration Personal electronics Digital TV RAID HDTV Web TVs Network routers PC 99 Video compression Electronic toys Network computers ISDN Satellite decoders Set-top boxes Video cameras Compact PCI RISC interface Monitors LCD projectors Cell phones DSS Credit card readers Digital cameras PCMCIA Digital Hi-Fi Robotics CAN bus Network computers Video phones Badge readers Graphics acceleration Fax machines Music synthesizers IIC Hubs DVD Cable modems Security systems Digital monitors PCI Optical drives Color correction Card bus Arcade games VCR Modems Hard drives Process controllers Audio LANs USB Video editing Consumer electronics Internet appliances DSP Printers Click drives Medical imaging Digital VHS Video capture cards MPEG/JPEG Video conferencing Satellite base stations Camcorders Handheld scanners Test equipment POS terminals Voice processing Multimedia CDROM drives Personal digital assistants Video conferencing Digital audio mixing desks GPS Bar code readers Reconfigurable computing Telephony Digitizers PCS ground stations Automotive cabin controls Fiber optics PBX switches Imaging systems PC network cards Copiers 6 Example Applications Breaking the Cost Barrier

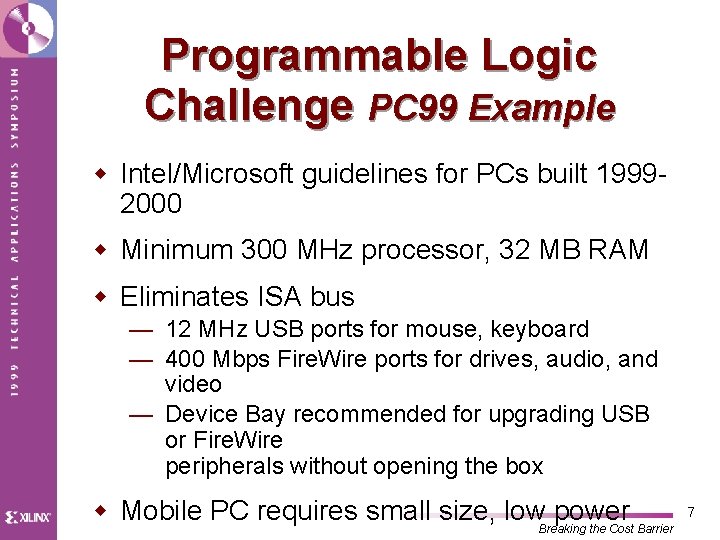

Programmable Logic Challenge PC 99 Example w Intel/Microsoft guidelines for PCs built 19992000 w Minimum 300 MHz processor, 32 MB RAM w Eliminates ISA bus — 12 MHz USB ports for mouse, keyboard — 400 Mbps Fire. Wire ports for drives, audio, and video — Device Bay recommended for upgrading USB or Fire. Wire peripherals without opening the box w Mobile PC requires small size, low. Breaking power the Cost Barrier 7

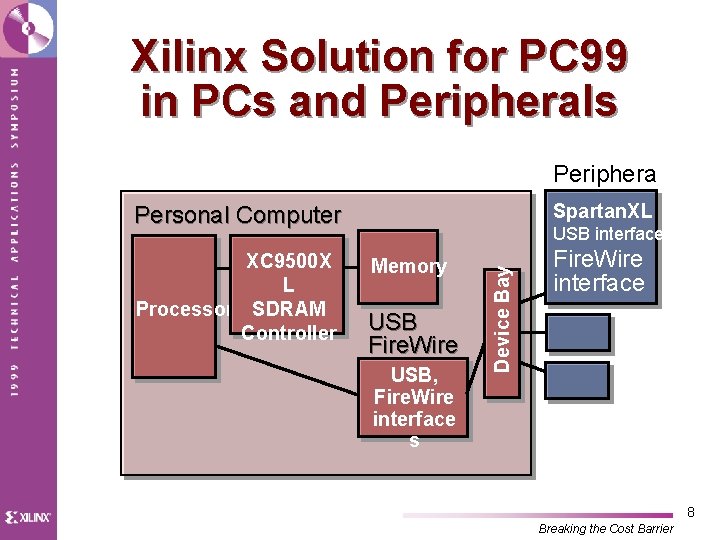

Xilinx Solution for PC 99 in PCs and Peripherals Periphera ls Spartan. XL Personal Computer Memory USB Fire. Wire USB, Fire. Wire interface s Device Bay XC 9500 X L Processor SDRAM Controller USB interface/ Fire. Wire interface 8 Breaking the Cost Barrier

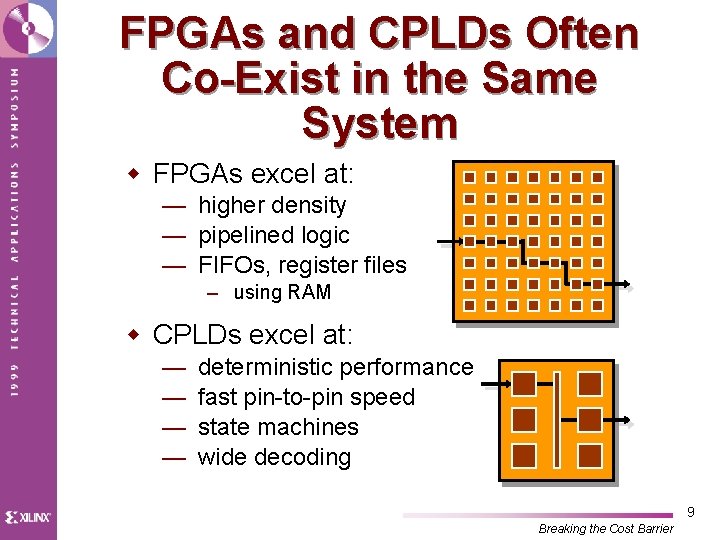

FPGAs and CPLDs Often Co-Exist in the Same System w FPGAs excel at: — higher density — pipelined logic — FIFOs, register files – using RAM w CPLDs excel at: — — deterministic performance fast pin-to-pin speed state machines wide decoding 9 Breaking the Cost Barrier

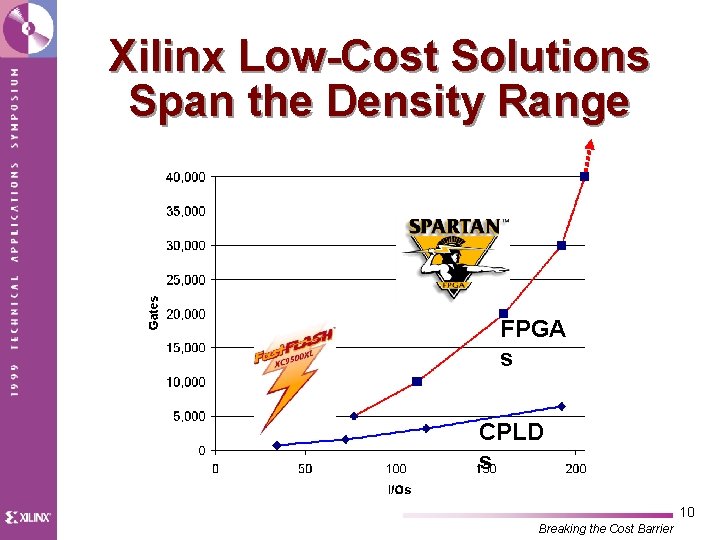

Xilinx Low-Cost Solutions Span the Density Range FPGA s CPLD s 10 Breaking the Cost Barrier

FPGA Challenge Fire. Wire Example w Fire. Wire part of PC 99 spec is used to demonstrate the benefits of Xilinx FPGAs w IEEE 1394 standard — based on Apple’s original definition of Fire. Wire w High speed serial bus — 400 Mbits/s required for PC 99; increasing to 3. 2 Gbits/s w For emerging consumer electronics — digital camcorders, DVD players, digital VCRs, HDTV, set-top boxes, video conferencing w For traditional PC peripherals — hard drives, printers, scanners, modems 11 Breaking the Cost Barrier

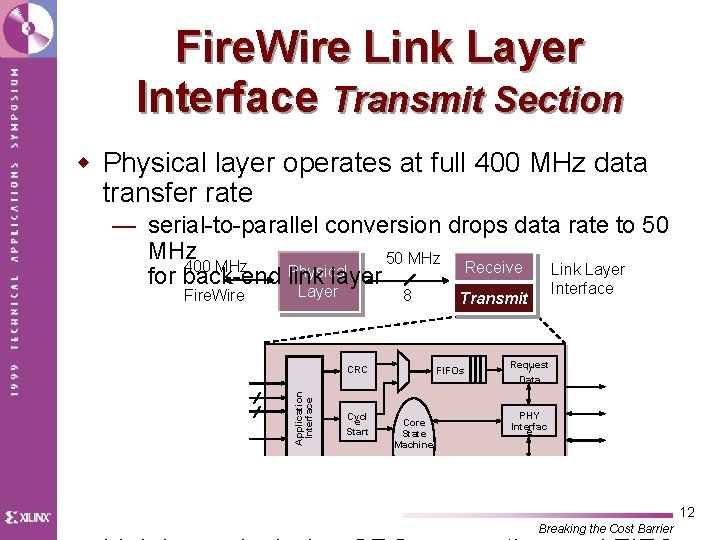

Fire. Wire Link Layer Interface Transmit Section w Physical layer operates at full 400 MHz data transfer rate — serial-to-parallel conversion drops data rate to 50 MHz 400 MHz Receive Link Layer Physical for back-end link layer Interface Layer 8 CRC Application Interface Fire. Wire Cycl e Start Transmit FIFOs Core State Machine Request / Data PHY Interfac e 12 Breaking the Cost Barrier

Challenges Facing the Design Engineer Design complexity HDL entry Design time Flexibility for an evolving standard Cost control High performance FIFOs Low power Design tools Design cycle time 13 Breaking the Cost Barrier

Potential Solutions w Discrete logic — not practical approach any longer — few available 3. 3 V/2. 5 V devices available w Chip sets — few available — expensive w Custom ASIC — long design cycle — costly to rework w Programmable Logic 14 Breaking the Cost Barrier

Spartan Series FPGAs Provide Solution üReprogrammable: instant updates üFlexibility and design complexity — feature-rich programmable architecture üHigh performance: >100 MHz parallel logic üDesign tools — established, easy-to-use development tools — complete software support and extensive cores (IP) üCost control — advanced process technology for small, low cost die — streamlined manufacturing provides total cost management Breaking the Cost Barrier 15

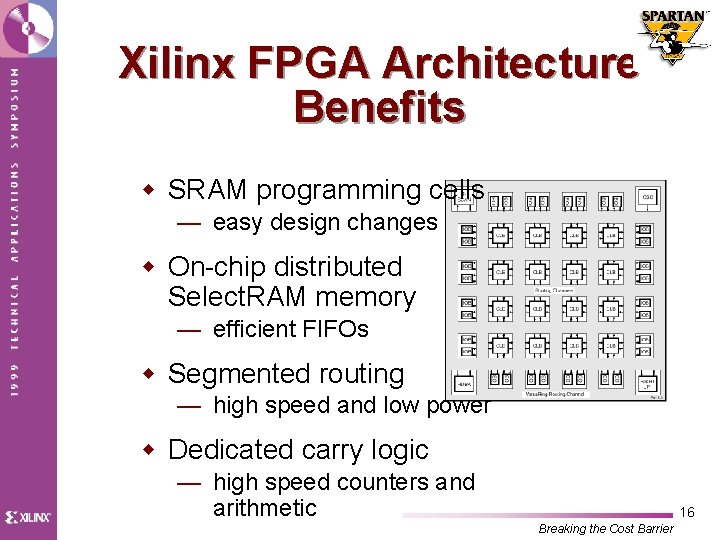

Xilinx FPGA Architecture Benefits w SRAM programming cells — easy design changes w On-chip distributed Select. RAM memory — efficient FIFOs w Segmented routing — high speed and low power w Dedicated carry logic — high speed counters and arithmetic 16 Breaking the Cost Barrier

Reprogrammability w Fast time to market — immediate design changes — no cost penalty for mistakes and updates w Immediate production — no conversion costs — off-the-shelf — no inventory risk w 100% tested — streamlined Xilinx testing reduces costs 17 Breaking the Cost Barrier

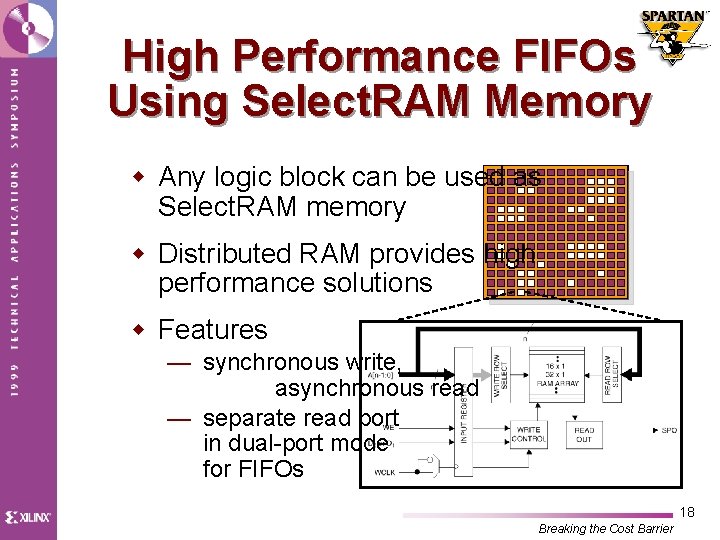

High Performance FIFOs Using Select. RAM Memory w Any logic block can be used as Select. RAM memory w Distributed RAM provides high performance solutions w Features — synchronous write, asynchronous read — separate read port in dual-port mode for FIFOs 18 Breaking the Cost Barrier

CLB RAM Provides 16 x the Storage of Flip-Flops w Configurable Logic Block (CLB) storage: — Select. RAM: 32 bits per CLB — flip-flops: 2 bits per CLB w 100 -784 CLBs in Spartan. XL series CLB D 1 A 0 A 1 A 2 A 3 A 4 CLB D 1 32 bits O 1 Logic Q 1 2 bits D 2 WE D Q Q 2 CLK 19 Breaking the Cost Barrier

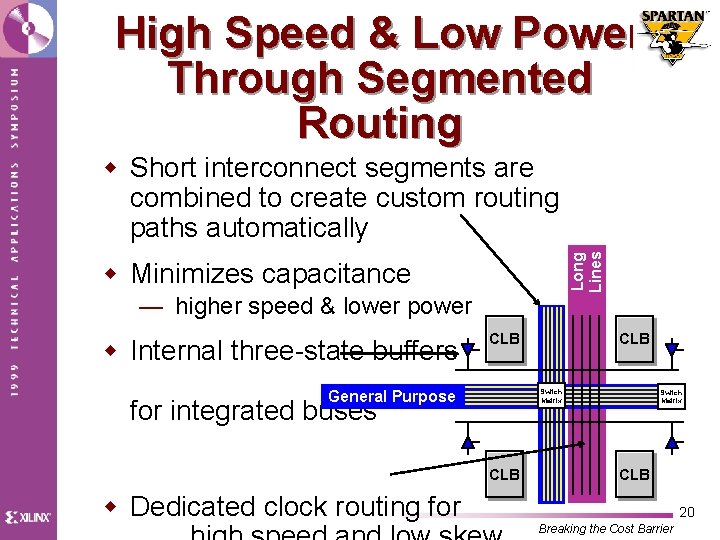

High Speed & Low Power Through Segmented Routing Long Lines w Short interconnect segments are combined to create custom routing paths automatically w Minimizes capacitance — higher speed & lower power w Internal three-state buffers CLB General Purpose CLB Switch Matrix for integrated buses CLB Switch Matrix CLB w Dedicated clock routing for 20 Breaking the Cost Barrier

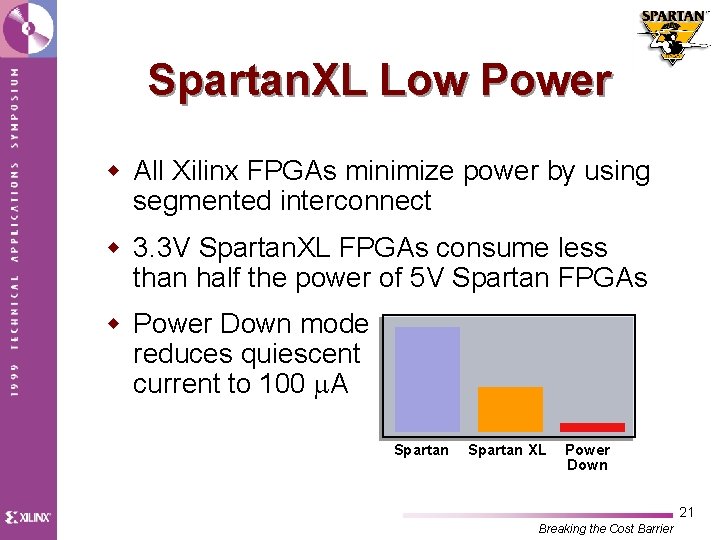

Spartan. XL Low Power w All Xilinx FPGAs minimize power by using segmented interconnect w 3. 3 V Spartan. XL FPGAs consume less than half the power of 5 V Spartan FPGAs w Power Down mode reduces quiescent current to 100 m. A Spartan XL Power Down 21 Breaking the Cost Barrier

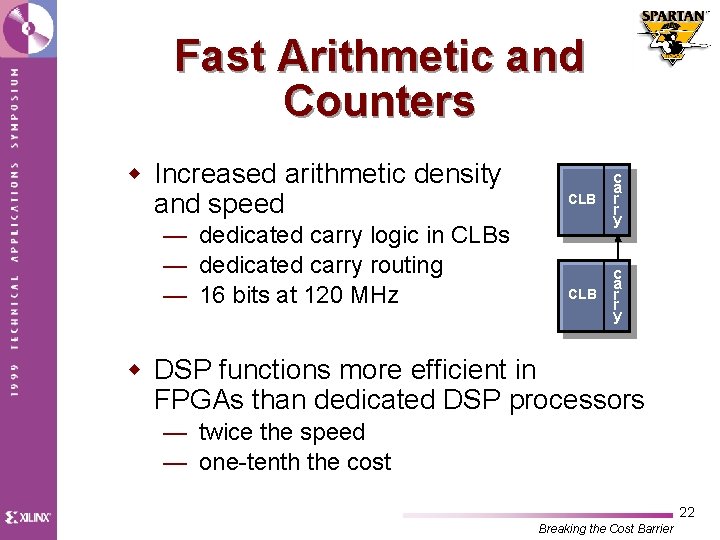

Fast Arithmetic and Counters w Increased arithmetic density and speed — dedicated carry logic in CLBs — dedicated carry routing — 16 bits at 120 MHz CLB c a r r y w DSP functions more efficient in FPGAs than dedicated DSP processors — twice the speed — one-tenth the cost 22 Breaking the Cost Barrier

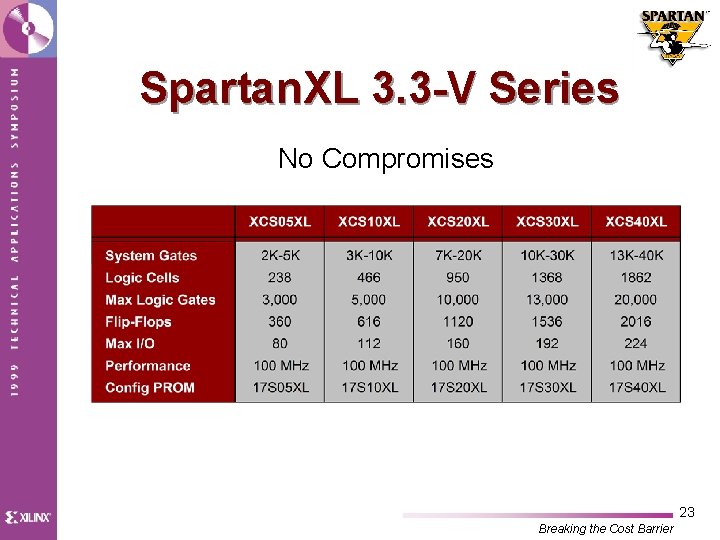

Spartan. XL 3. 3 -V Series No Compromises 23 Breaking the Cost Barrier

Spartan. XL Implementation w Implement FIFO part of Fire. Wire design as an example w 50 MHz required 24 Breaking the Cost Barrier

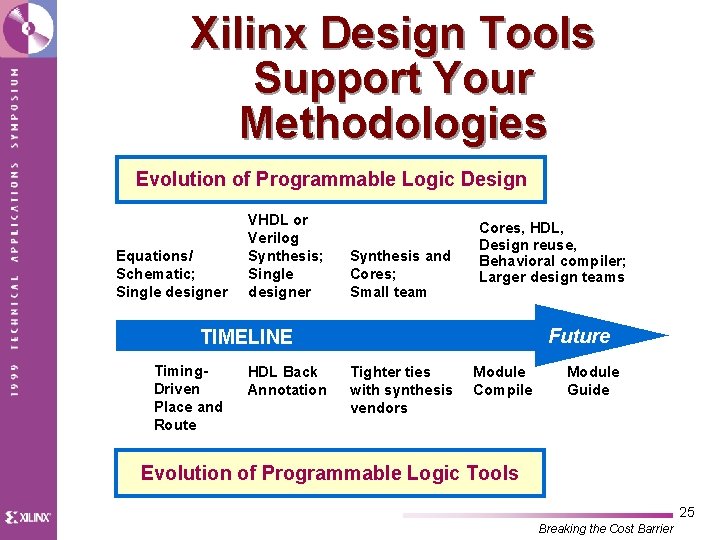

Xilinx Design Tools Support Your Methodologies Evolution of Programmable Logic Design Equations/ Schematic; Single designer VHDL or Verilog Synthesis; Single designer Synthesis and Cores; Small team Cores, HDL, Design reuse, Behavioral compiler; Larger design teams Future TIMELINE Timing. Driven Place and Route HDL Back Annotation Tighter ties with synthesis vendors Module Compile Module Guide Evolution of Programmable Logic Tools 25 Breaking the Cost Barrier

Xilinx Foundation Series w Ready-to-Use w Push-button, highperformance design w Mixed-level design — easy schematic entry — superior HDL solution w Low-cost Base system supports all Spartan. XL and XC 9500 XL devices 26 Breaking the Cost Barrier

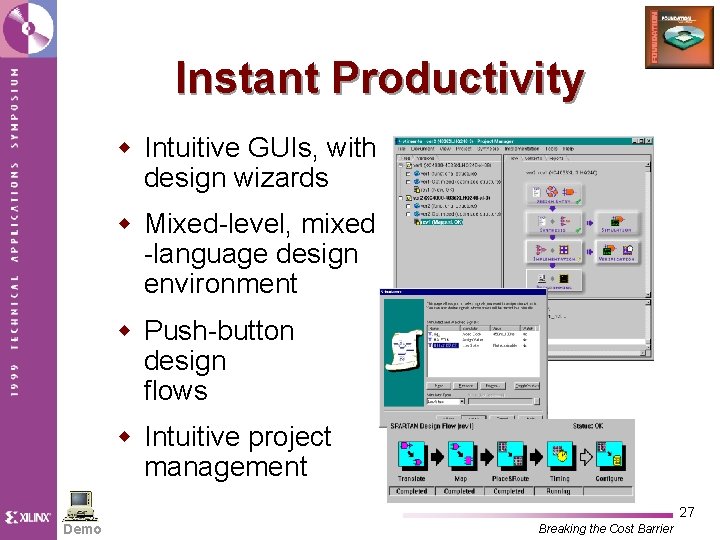

Instant Productivity w Intuitive GUIs, with design wizards w Mixed-level, mixed -language design environment w Push-button design flows w Intuitive project management 27 Demo Breaking the Cost Barrier

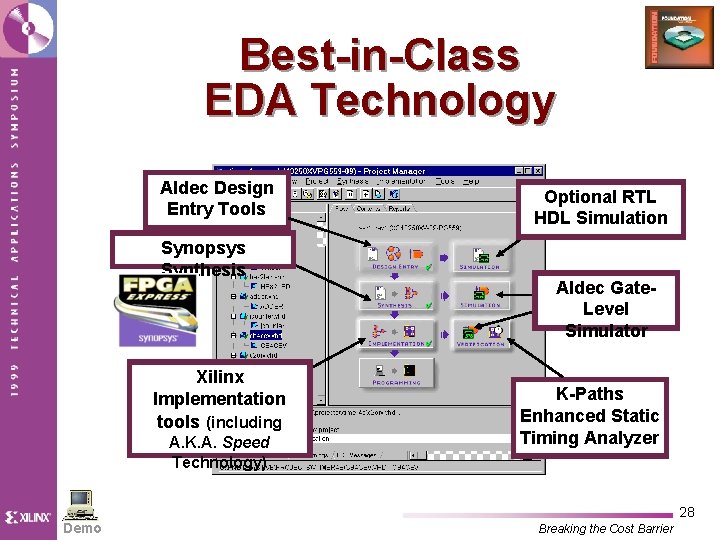

Best-in-Class EDA Technology Aldec Design Entry Tools Synopsys Synthesis Xilinx Implementation tools (including A. K. A. Speed Technology) Optional RTL HDL Simulation Aldec Gate. Level Simulator K-Paths Enhanced Static Timing Analyzer 28 Demo Breaking the Cost Barrier

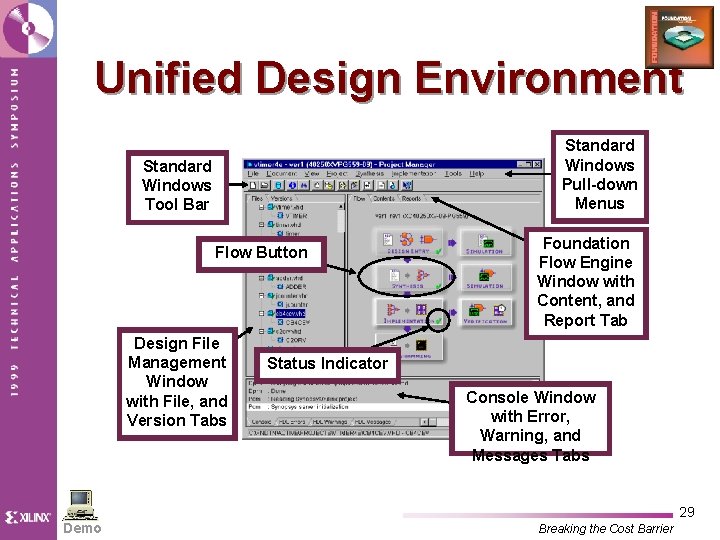

Unified Design Environment Standard Windows Pull-down Menus Standard Windows Tool Bar Flow Button Design File Management Window with File, and Version Tabs Foundation Flow Engine Window with Content, and Report Tab Status Indicator Console Window with Error, Warning, and Messages Tabs 29 Demo Breaking the Cost Barrier

Foundation On-Line Help w On-line help includes link to support. xilinx. com — dedicated support web site — result of Silicon Xpresso initiative 30 Demo Breaking the Cost Barrier

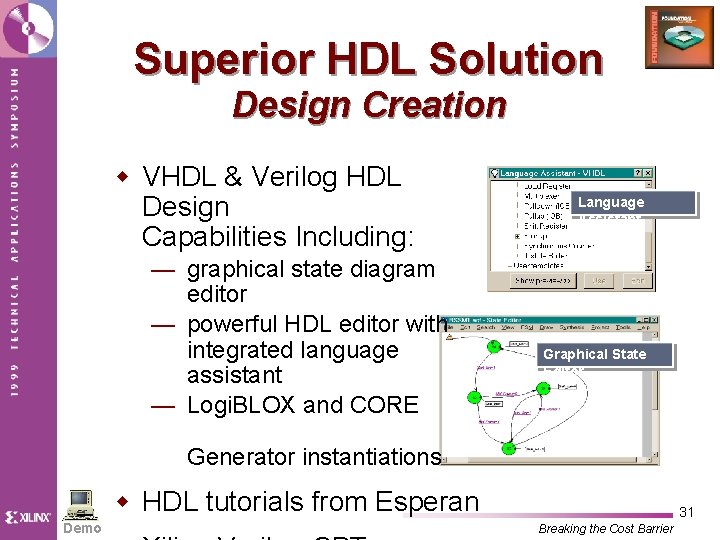

Superior HDL Solution Design Creation w VHDL & Verilog HDL Design Capabilities Including: — graphical state diagram editor — powerful HDL editor with integrated language assistant — Logi. BLOX and CORE Language Assistant Graphical State Editor Generator instantiations w HDL tutorials from Esperan Demo 31 Breaking the Cost Barrier

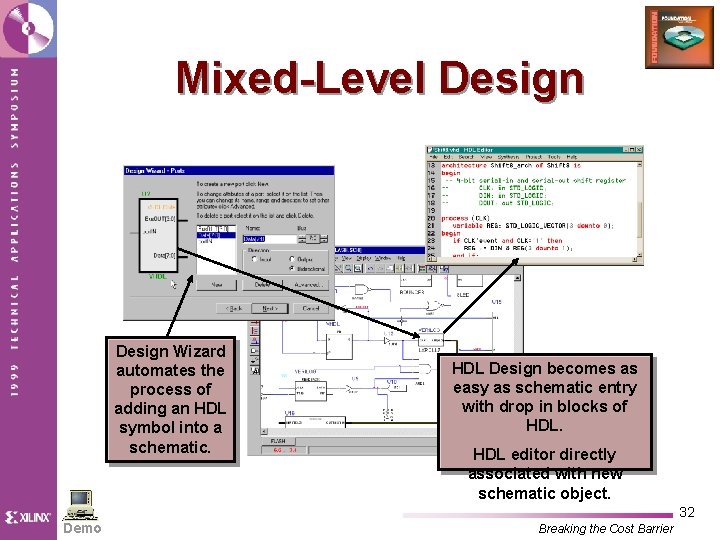

Mixed-Level Design Wizard automates the process of adding an HDL symbol into a schematic. HDL Design becomes as easy as schematic entry with drop in blocks of HDL editor Editor directly associated with new schematic object 32 Demo Breaking the Cost Barrier

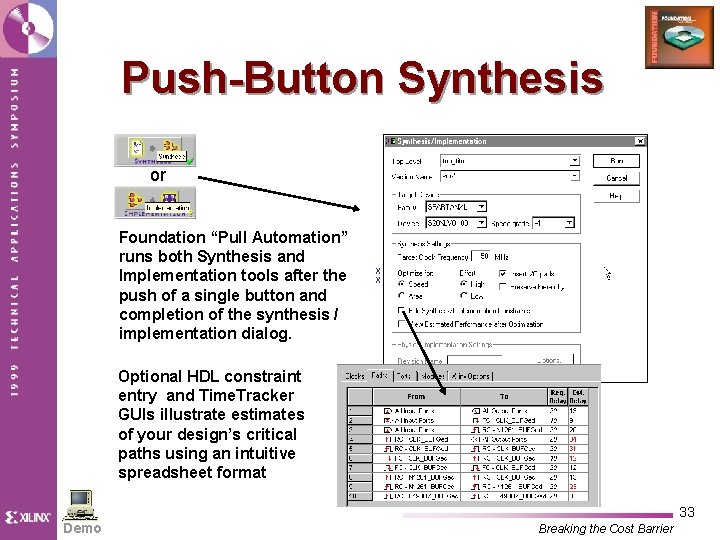

Push-Button Synthesis or Foundation “Pull Automation” runs both Synthesis and Implementation tools after the push of a single button and completion of the synthesis / implementation dialog. X X Optional HDL constraint entry and Time. Tracker GUIs illustrate estimates of your design’s critical paths using an intuitive spreadsheet format 33 Demo Breaking the Cost Barrier

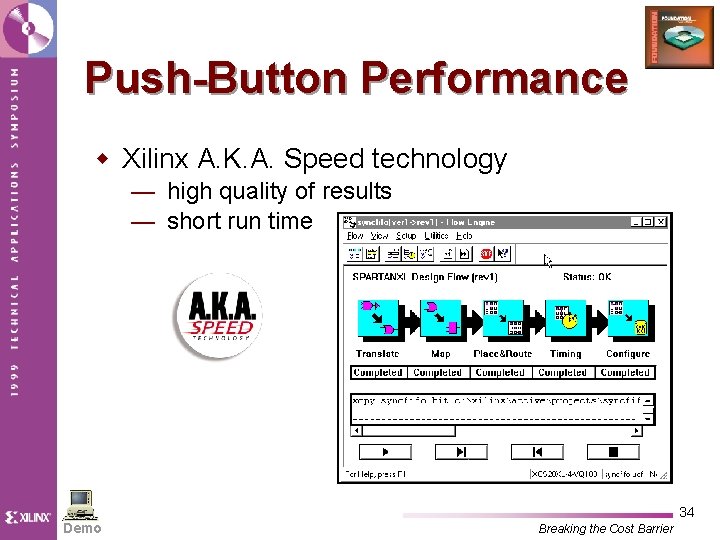

Push-Button Performance w Xilinx A. K. A. Speed technology — high quality of results — short run time 34 Demo Breaking the Cost Barrier

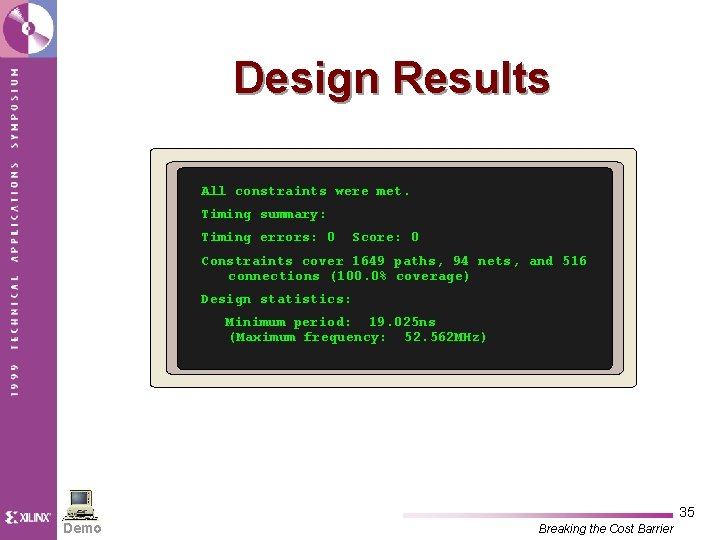

Design Results All constraints were met. Timing summary: Timing errors: 0 Score: 0 Constraints cover 1649 paths, 94 nets, and 516 connections (100. 0% coverage) Design statistics: Minimum period: 19. 025 ns (Maximum frequency: 52. 562 MHz) 35 Demo Breaking the Cost Barrier

Beyond Push-Button Implementation w FPGAs allow for extensive optimization through creative design and implementation w Standard library counter runs at 120 MHz in Spartan. XL using default options w Asynchronous frequency counter runs at over 36 400 MHz! Breaking the Cost Barrier

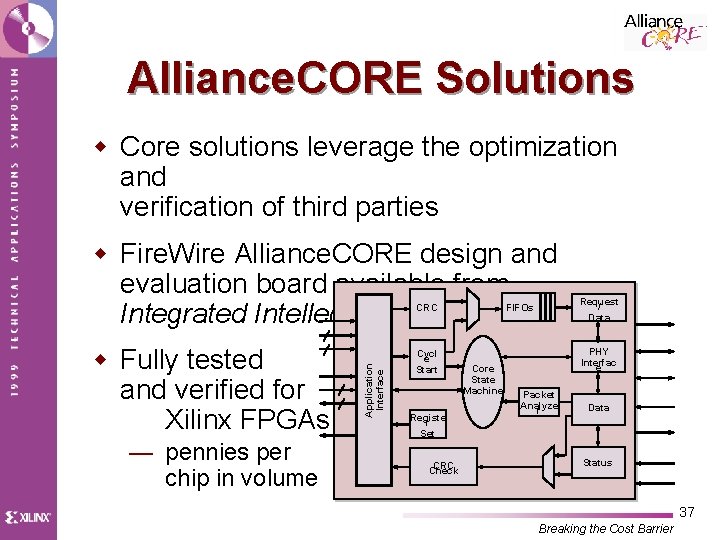

Alliance. CORE Solutions w Core solutions leverage the optimization and verification of third parties w Fire. Wire Alliance. CORE design and evaluation board available from Integrated Intellectual Property w Fully tested and verified for Xilinx FPGAs — pennies per chip in volume Application Interface CRC Cycl e Start Registe r Set CRC Check FIFOs Core State Machine Request / Data PHY Interfac e Packet Analyze r Data Status 37 Breaking the Cost Barrier

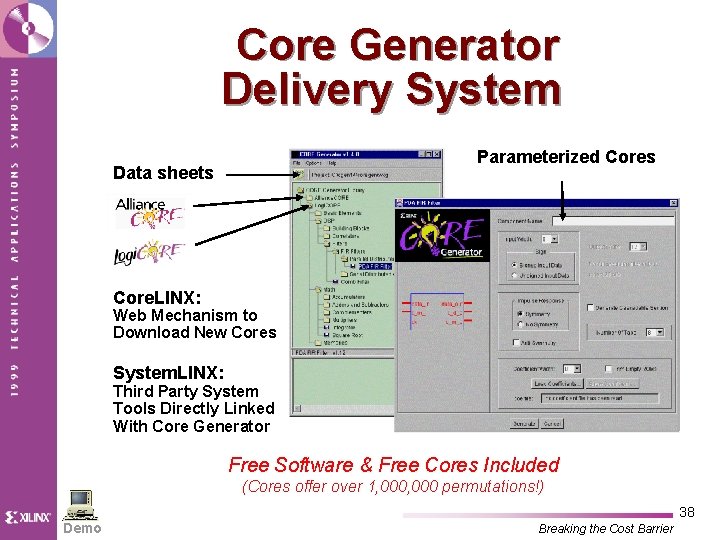

Core Generator Delivery System Parameterized Cores Data sheets Core. LINX: Web Mechanism to Download New Cores System. LINX: Third Party System Tools Directly Linked With Core Generator Free Software & Free Cores Included (Cores offer over 1, 000 permutations!) 38 Demo Breaking the Cost Barrier

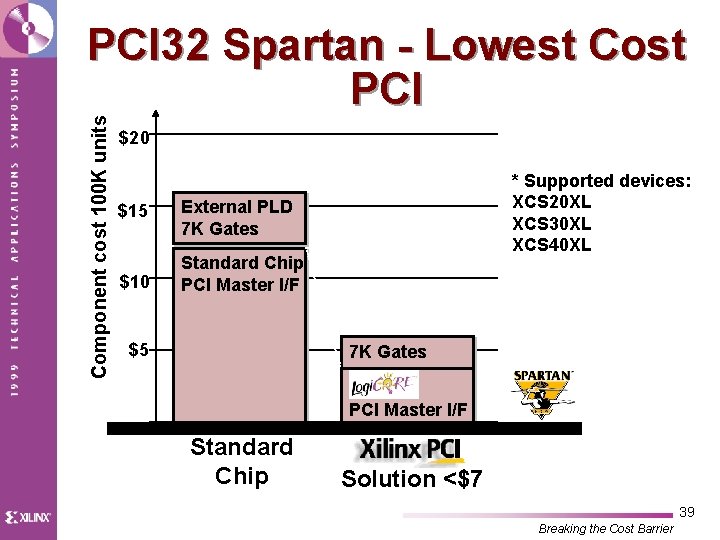

Component cost 100 K units PCI 32 Spartan - Lowest Cost PCI $20 $15 External PLD 7 K Gates $10 Standard Chip PCI Master I/F * Supported devices: XCS 20 XL XCS 30 XL XCS 40 XL XCS 20 XL-4 TQ 144* $5 7 K Gates Logic Power by PCI Master I/F Standard Chip Solution <$7 39 Breaking the Cost Barrier

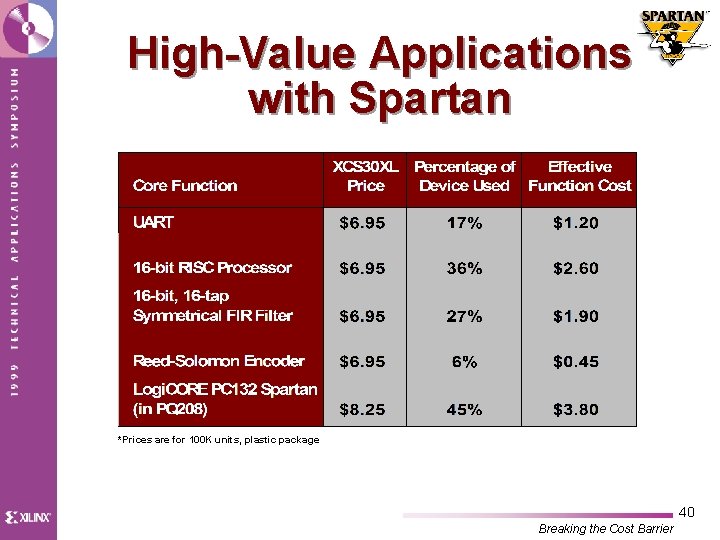

High-Value Applications with Spartan *Prices are for 100 K units, plastic package 40 Breaking the Cost Barrier

Spartan. XL Benefits w Fast time-to-market — user programmable w Low cost w Features for complex logic — high speed — low power w Easy to use — fully supported by Xilinx and third-party software 41 Breaking the Cost Barrier

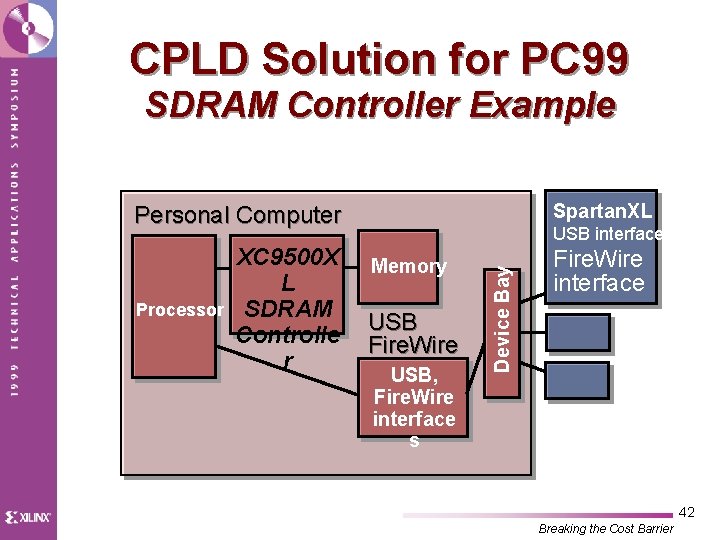

CPLD Solution for PC 99 SDRAM Controller Example Spartan. XL Personal Computer Memory USB Fire. Wire USB, Fire. Wire interface s Device Bay Processor XC 9500 X L SDRAM Controlle r USB interface/ Fire. Wire interface 42 Breaking the Cost Barrier

Challenges Facing the Design Engineer Small 3. 3 V/2. package Design 5 V HDL entry timeminimum 100 MHz speed Board layout before design is complete Cost control Multiple SDRAM protocols Minimal programming overhead Sufficient address width Three-state Clock flexibility Resources for future flexibility expansion 43 Breaking the Cost Barrier

![Address[23: 0] Clock Reset Write Data[15: 0] Address[11: 0] CPLD SDRAM Controller CS RAS Address[23: 0] Clock Reset Write Data[15: 0] Address[11: 0] CPLD SDRAM Controller CS RAS](http://slidetodoc.com/presentation_image_h2/02c1291dbfac9fdf93a688554827c9fd/image-44.jpg)

Address[23: 0] Clock Reset Write Data[15: 0] Address[11: 0] CPLD SDRAM Controller CS RAS CAS WE SDRAMs Microprocessor Memory Interface Block Diagram Complete SDRAM Controller in a single CPLD 44 Breaking the Cost Barrier

![SDRAM Interface Closeup Address[23: 0] ADDR[23: 12] ADDR[11: 0] Data[15: 0] Refresh Counter Clock SDRAM Interface Closeup Address[23: 0] ADDR[23: 12] ADDR[11: 0] Data[15: 0] Refresh Counter Clock](http://slidetodoc.com/presentation_image_h2/02c1291dbfac9fdf93a688554827c9fd/image-45.jpg)

SDRAM Interface Closeup Address[23: 0] ADDR[23: 12] ADDR[11: 0] Data[15: 0] Refresh Counter Clock Reset Write Address Decode Chip Mode Select. Register State Machine CS RAS CAS WE 45 Breaking the Cost Barrier

3. 3 -V XC 9500 XL Solution w Optimized for 3. 3 -V systems — compatible levels with 5. 0/2. 5 V — no power sequencing restrictions! w Meets performance requirements — high f. MAX = 200 MHz — fast t. PD = 4 ns w Best ISP/JTAG support in industry w Best pinlocking in industry w Advanced packaging - New CSPs ! 46 Breaking the Cost Barrier

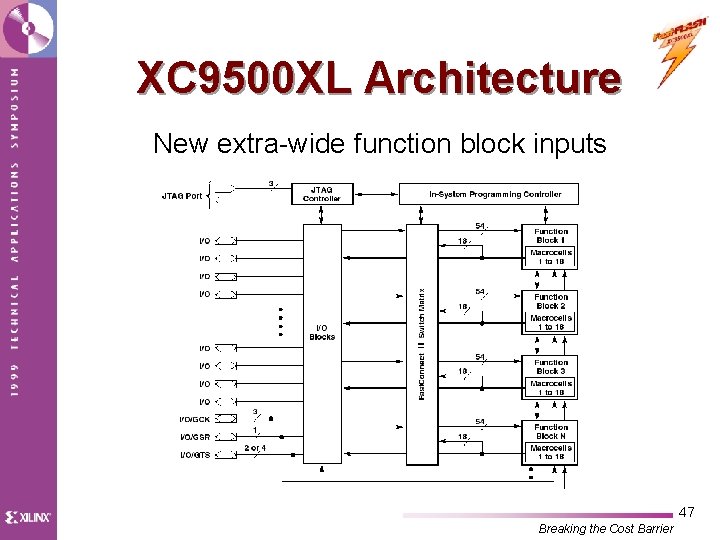

XC 9500 XL Architecture New extra-wide function block inputs 47 Breaking the Cost Barrier

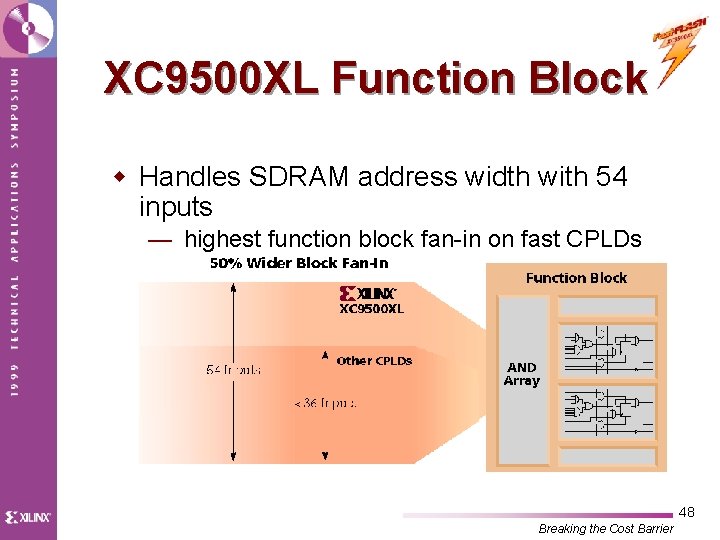

XC 9500 XL Function Block w Handles SDRAM address width with 54 inputs — highest function block fan-in on fast CPLDs 48 Breaking the Cost Barrier

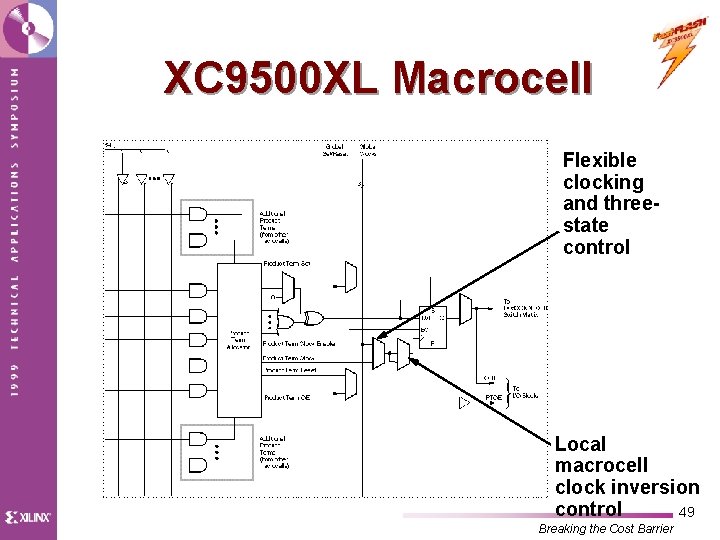

XC 9500 XL Macrocell Flexible clocking and threestate control Local macrocell clock inversion control 49 Breaking the Cost Barrier

XC 9500 XL Special System Designer Benefits w Input hysteresis w Fully compliant ISP/JTAG guarantees no ISP lock out w No power sequencing restrictions w Hot plug-in 50 Breaking the Cost Barrier

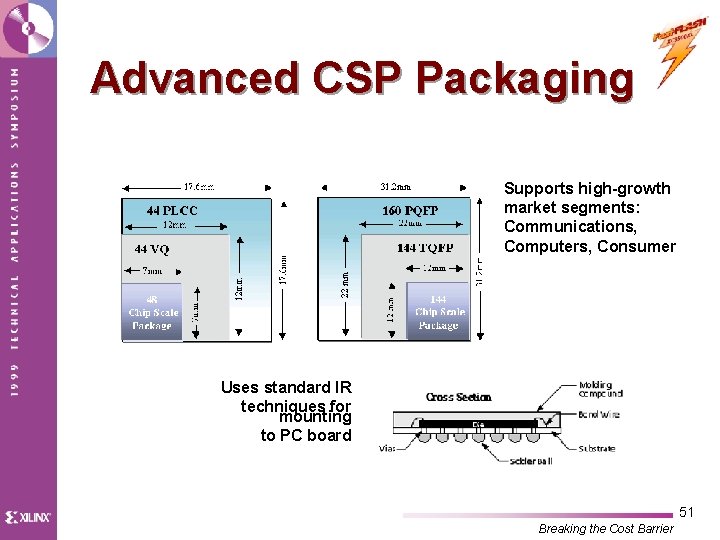

Advanced CSP Packaging Supports high-growth market segments: Communications, Computers, Consumer Uses standard IR techniques for mounting to PC board 51 Breaking the Cost Barrier

XC 9500 XL Solution Meets Design Challenges ü 3. 3/2. 5 V electrical compatibility — no power-sequencing restriction ü Chip scale packaging ü Pin-locking allows design change flexibility ü No programmer necessary with JTAG-based programming ü Fast design time ü VHDL, Verilog or ABEL design entry Breaking the Cost Barrier 52

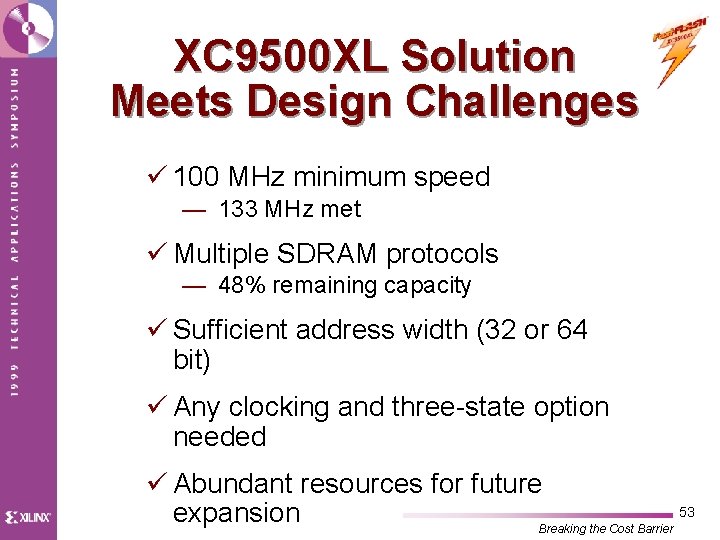

XC 9500 XL Solution Meets Design Challenges ü 100 MHz minimum speed — 133 MHz met ü Multiple SDRAM protocols — 48% remaining capacity ü Sufficient address width (32 or 64 bit) ü Any clocking and three-state option needed ü Abundant resources for future 53 expansion Breaking the Cost Barrier

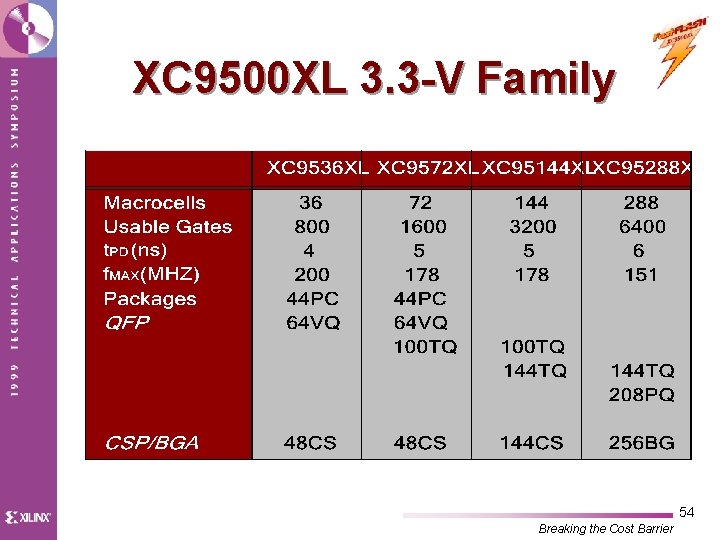

XC 9500 XL 3. 3 -V Family 54 Breaking the Cost Barrier

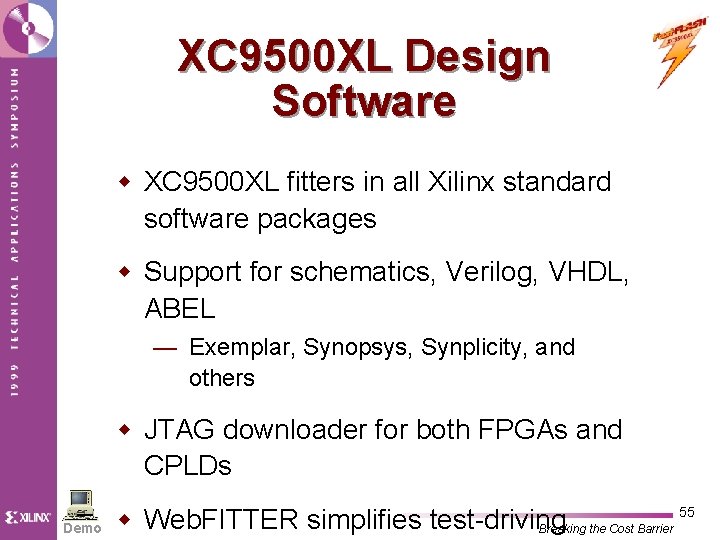

XC 9500 XL Design Software w XC 9500 XL fitters in all Xilinx standard software packages w Support for schematics, Verilog, VHDL, ABEL — Exemplar, Synopsys, Synplicity, and others w JTAG downloader for both FPGAs and CPLDs Demo 55 w Web. FITTER simplifies test-driving Breaking the Cost Barrier

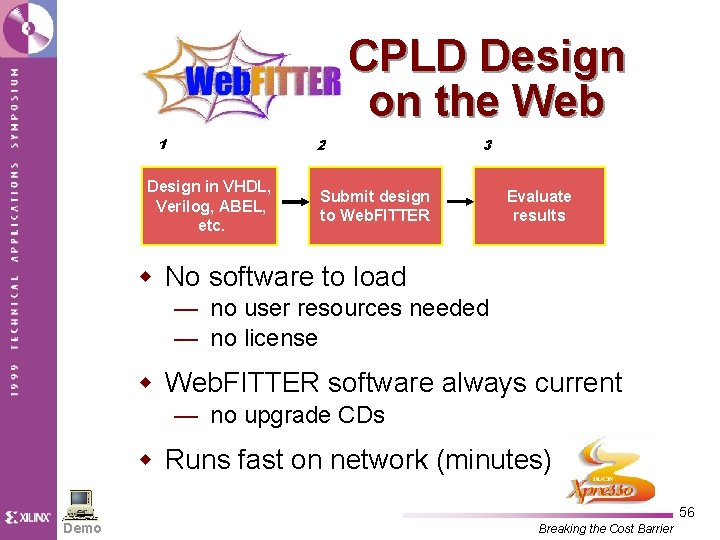

CPLD Design on the Web 1 2 Design in VHDL, Verilog, ABEL, etc. 3 Submit design to Web. FITTER Evaluate results w No software to load — no user resources needed — no license w Web. FITTER software always current — no upgrade CDs w Runs fast on network (minutes) 56 Demo Breaking the Cost Barrier

Web. FITTER Intro Page 57 Demo Breaking the Cost Barrier

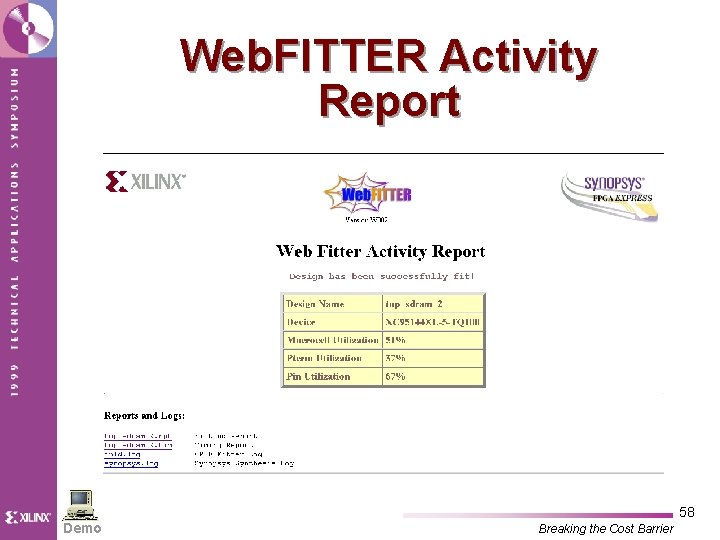

Web. FITTER Activity Report 58 Demo Breaking the Cost Barrier

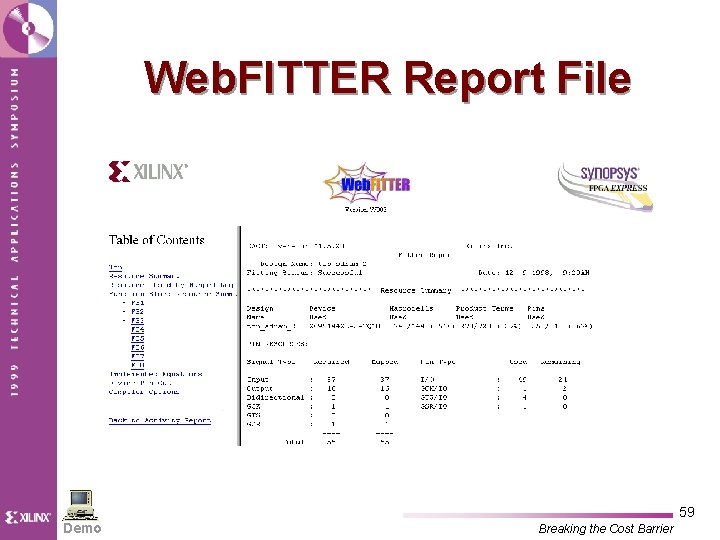

Web. FITTER Report File 59 Demo Breaking the Cost Barrier

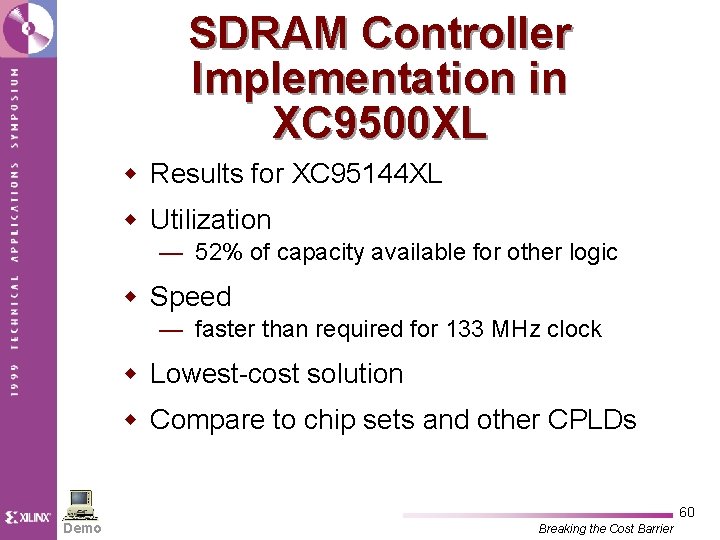

SDRAM Controller Implementation in XC 9500 XL w Results for XC 95144 XL w Utilization — 52% of capacity available for other logic w Speed — faster than required for 133 MHz clock w Lowest-cost solution w Compare to chip sets and other CPLDs 60 Demo Breaking the Cost Barrier

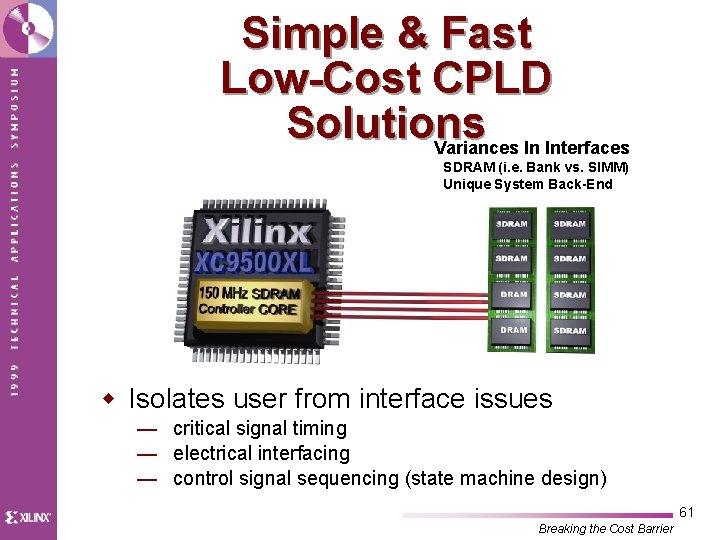

Simple & Fast Low-Cost CPLD Solutions Variances In Interfaces SDRAM (i. e. Bank vs. SIMM) Unique System Back-End w Isolates user from interface issues — critical signal timing — electrical interfacing — control signal sequencing (state machine design) 61 Breaking the Cost Barrier

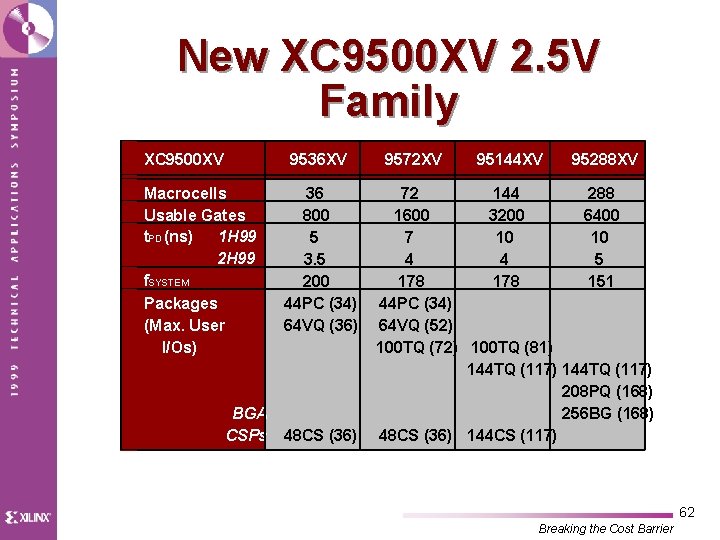

New XC 9500 XV 2. 5 V Family XC 9500 XV 9536 XV Macrocells Usable Gates t. PD (ns) 1 H 99 2 H 99 f. SYSTEM Packages (Max. User I/Os) BGA CSPs 36 800 5 3. 5 200 44 PC (34) 64 VQ (36) 48 CS (36) 9572 XV 95144 XV 95288 XV 72 144 288 1600 3200 6400 7 10 10 4 4 5 178 151 44 PC (34) 64 VQ (52) 100 TQ (72) 100 TQ (81) 144 TQ (117) 208 PQ (168) 256 BG (168) 48 CS (36) 144 CS (117) 62 Breaking the Cost Barrier

PC Peripherals Mobile computing Network interface cards PCS phones SDRAM Controllers Modems Docking stations Fire. Wire I/O interface boards Ethernet adapters Household appliances Gate array replacement Handsets Device bay Flight simulators Instrumentation ADSL Home theatre Discrete logic integration Personal electronics Digital TV RAID HDTV Web TVs Network routers PC 99 Video compression Electronic toys Network computers ISDN Satellite decoders Set-top boxes Video cameras Compact PCI RISC interface Monitors LCD projectors Cell phones DSS Credit card readers Digital cameras PCMCIA Digital Hi-Fi Robotics CAN bus Network computers Video phones Badge readers Graphics acceleration Fax machines Music synthesizers IIC Hubs DVD Cable modems Security systems Digital monitors PCI Optical drives Color correction Card bus Arcade games VCR Modems Hard drives Process controllers Audio LANs USB Video editing Consumer electronics Internet appliances DSP Printers Click drives Medical imaging Digital VHS Video capture cards MPEG/JPEG Video conferencing Satellite base stations Camcorders Handheld scanners Test equipment POS terminals Voice processing Multimedia CDROM drives Personal digital assistants Video conferencing Digital audio mixing desks GPS Bar code readers Reconfigurable computing Telephony Digitizers PCS ground stations Automotive cabin controls Fiber optics PBX switches Imaging systems PC network cards Copiers 63 Example Applications Breaking the Cost Barrier

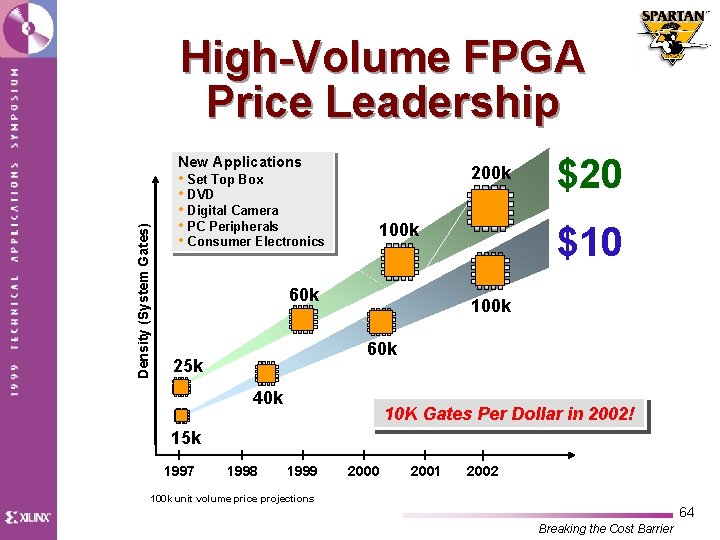

High-Volume FPGA Price Leadership Density (System Gates) New Applications • Set Top Box • DVD • Digital Camera • PC Peripherals • Consumer Electronics 200 k $10 100 k 60 k $20 100 k 60 k 25 k 40 k 10 K Gates Per Dollar in 2002! 15 k 1997 1998 1999 2000 2001 2002 100 k unit volume price projections 64 Breaking the Cost Barrier

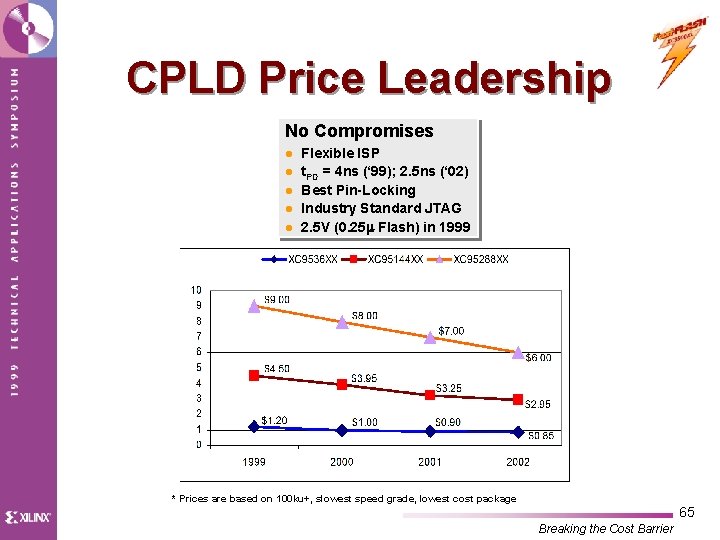

CPLD Price Leadership No Compromises l l l Flexible ISP t. PD = 4 ns (‘ 99); 2. 5 ns (‘ 02) Best Pin-Locking Industry Standard JTAG 2. 5 V (0. 25 m Flash) in 1999 * Prices are based on 100 ku+, slowest speed grade, lowest cost package 65 Breaking the Cost Barrier

Solutions for Low-Cost, High-Volume Applications w Low cost programmable logic — Spartan. XL FPGAs available — XC 9500 XL CPLDs available w High performance w System-level features w Ease of evaluation and design — Web. FITTER, Foundation 1. 5 i software available 66 Breaking the Cost Barrier

- Slides: 66