Branch Hazards Branch Prediction 1 So far the

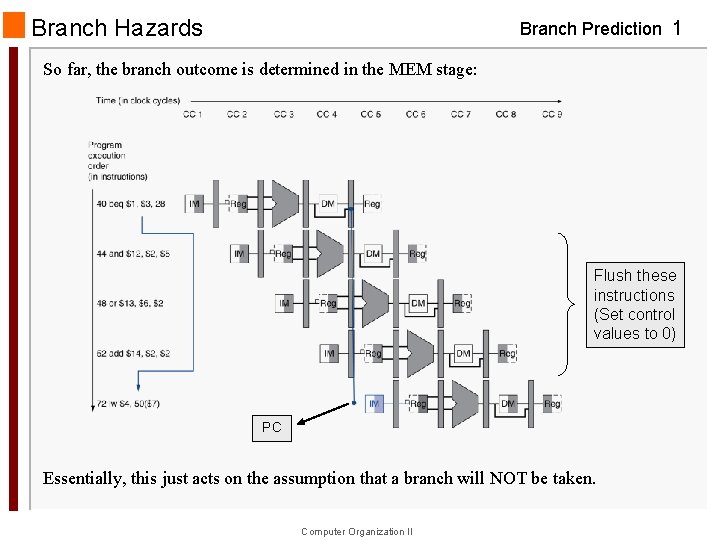

Branch Hazards Branch Prediction 1 So far, the branch outcome is determined in the MEM stage: Flush these instructions (Set control values to 0) PC Essentially, this just acts on the assumption that a branch will NOT be taken. Computer Organization II

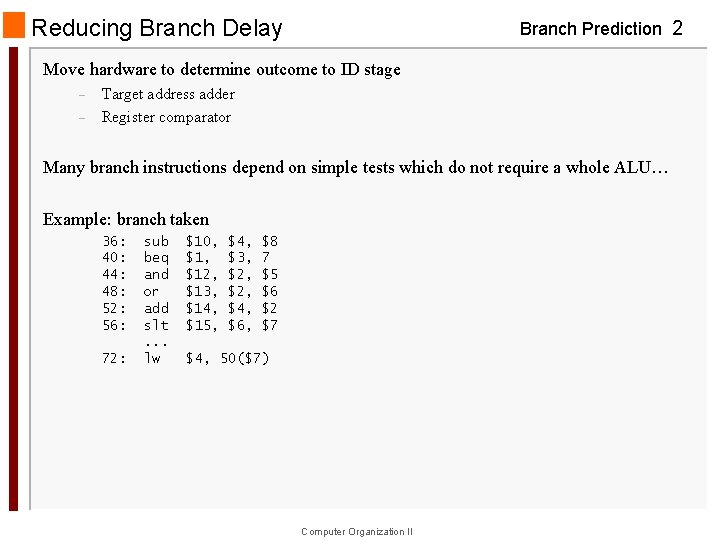

Reducing Branch Delay Branch Prediction 2 Move hardware to determine outcome to ID stage – – Target address adder Register comparator Many branch instructions depend on simple tests which do not require a whole ALU… Example: branch taken 36: 40: 44: 48: 52: 56: 72: sub beq and or add slt. . . lw $10, $12, $13, $14, $15, $4, $3, $2, $4, $6, $8 7 $5 $6 $2 $7 $4, 50($7) Computer Organization II

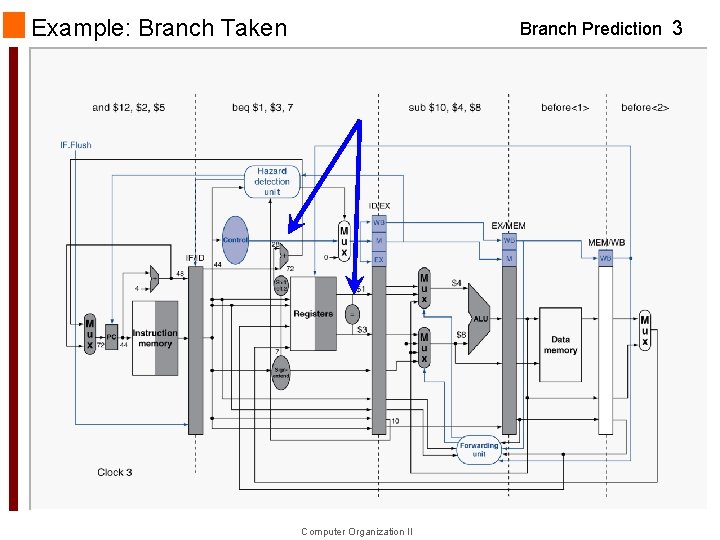

Example: Branch Taken Branch Prediction 3 Computer Organization II

Example: Branch Taken Branch Prediction 4 Computer Organization II

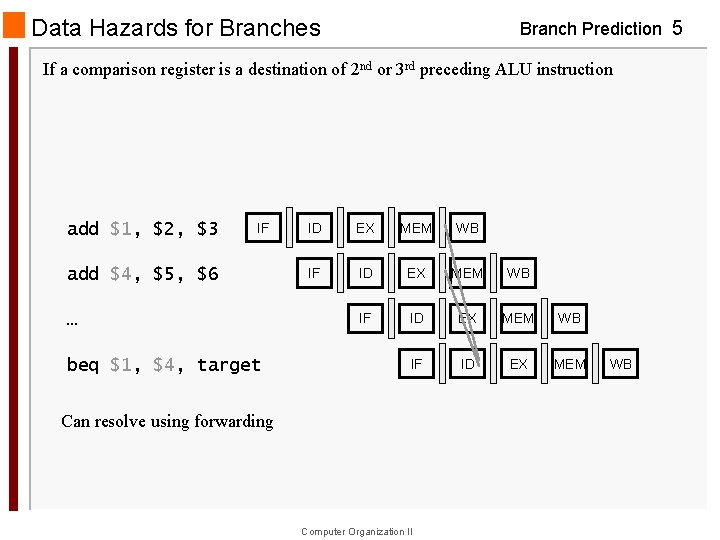

Data Hazards for Branches Branch Prediction 5 If a comparison register is a destination of 2 nd or 3 rd preceding ALU instruction add $1, $2, $3 IF add $4, $5, $6 … beq $1, $4, target ID EX MEM WB IF ID EX MEM Can resolve using forwarding Computer Organization II WB

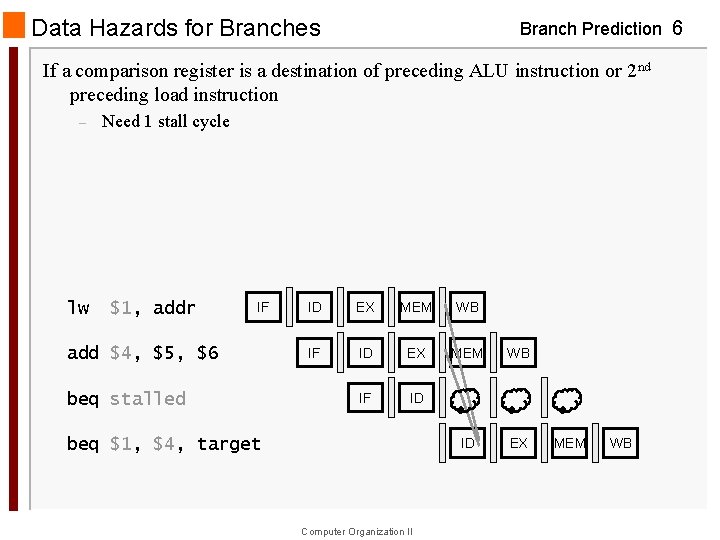

Data Hazards for Branches Branch Prediction 6 If a comparison register is a destination of preceding ALU instruction or 2 nd preceding load instruction – lw Need 1 stall cycle $1, addr IF add $4, $5, $6 beq stalled ID EX MEM WB IF ID ID EX beq $1, $4, target Computer Organization II MEM WB

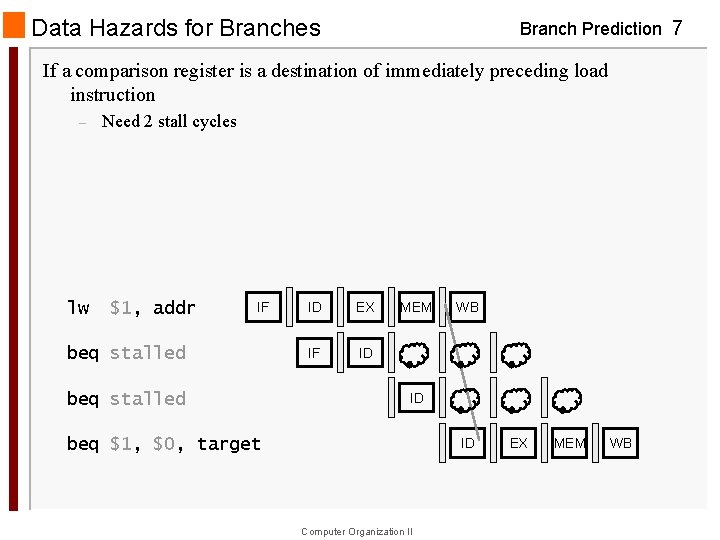

Data Hazards for Branches Branch Prediction 7 If a comparison register is a destination of immediately preceding load instruction – lw Need 2 stall cycles $1, addr IF beq stalled ID EX IF ID MEM WB ID ID beq $1, $0, target Computer Organization II EX MEM WB

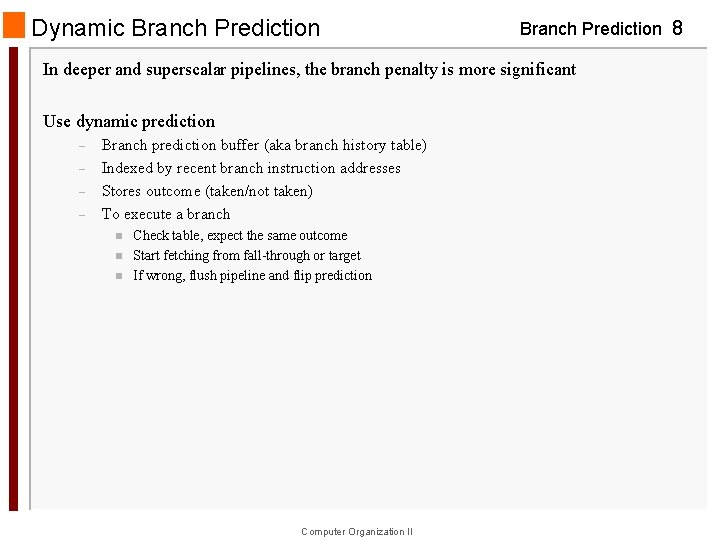

Dynamic Branch Prediction 8 In deeper and superscalar pipelines, the branch penalty is more significant Use dynamic prediction – – Branch prediction buffer (aka branch history table) Indexed by recent branch instruction addresses Stores outcome (taken/not taken) To execute a branch n n n Check table, expect the same outcome Start fetching from fall-through or target If wrong, flush pipeline and flip prediction Computer Organization II

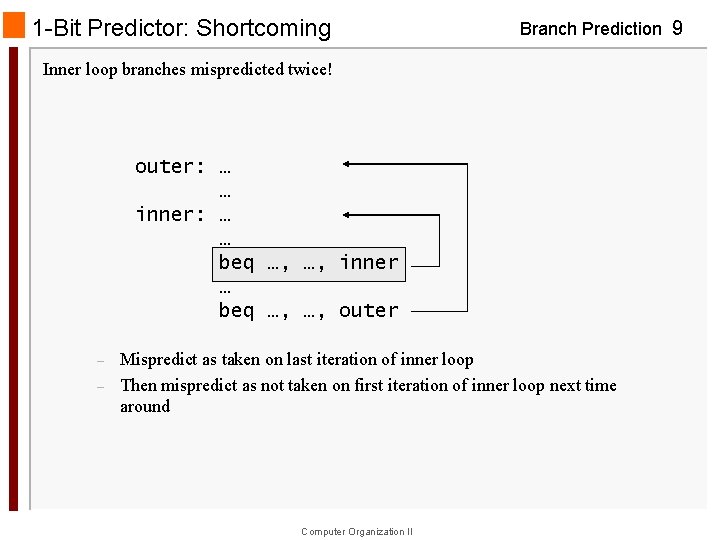

1 -Bit Predictor: Shortcoming Branch Prediction 9 Inner loop branches mispredicted twice! outer: … … inner: … … beq …, …, inner … beq …, …, outer – – Mispredict as taken on last iteration of inner loop Then mispredict as not taken on first iteration of inner loop next time around Computer Organization II

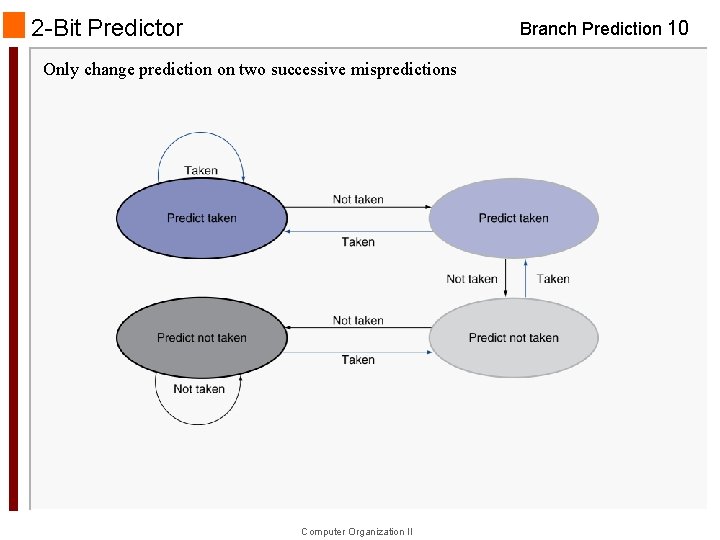

2 -Bit Predictor Branch Prediction 10 Only change prediction on two successive mispredictions Computer Organization II

Calculating the Branch Target Branch Prediction 11 Even with predictor, still need to calculate the target address – 1 -cycle penalty for a taken branch Branch target buffer – – Cache of target addresses Indexed by PC when instruction fetched n If hit and instruction is branch predicted taken, can fetch target immediately Computer Organization II

- Slides: 11