BMS Business Unit Overview Eric Marcelot Marketing Manager

BMS Business Unit Overview Eric Marcelot Marketing Manager Broadband Data Converters, Microprocessors & Services

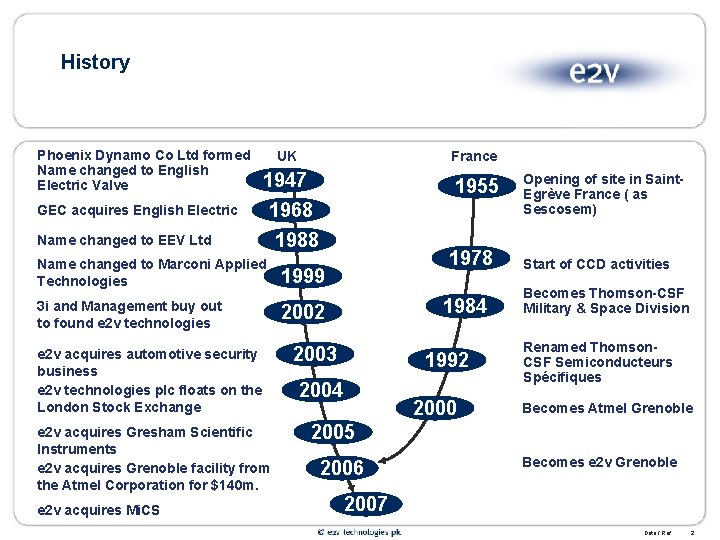

History Phoenix Dynamo Co Ltd formed Name changed to English Electric Valve GEC acquires English Electric Name changed to EEV Ltd UK France 1947 1968 1988 1955 Name changed to Marconi Applied Technologies 1999 3 i and Management buy out to found e 2 v technologies 2002 e 2 v acquires automotive security business e 2 v technologies plc floats on the London Stock Exchange e 2 v acquires Gresham Scientific Instruments e 2 v acquires Grenoble facility from the Atmel Corporation for $140 m. e 2 v acquires Mi. CS 1978 1984 2003 1992 2004 2000 Opening of site in Saint. Egrève France ( as Sescosem) Start of CCD activities Becomes Thomson-CSF Military & Space Division Renamed Thomson. CSF Semiconducteurs Spécifiques Becomes Atmel Grenoble 2005 2006 Becomes e 2 v Grenoble 2007 Date / Ref 2

Business overview Medical and Science Aerospace and Defence Commercial and Industrial Sensors and semiconductors Electronic tubes Date / Ref 3

Revenue Europe: Group sales £ 105 m Asia Pacific: Group sales £ 15 m Americas: Group sales £ 51 m Middle East & Africa: Group sales £ 3 m e 2 v group annual sales 2006/7: £ 174 m Date / Ref 4

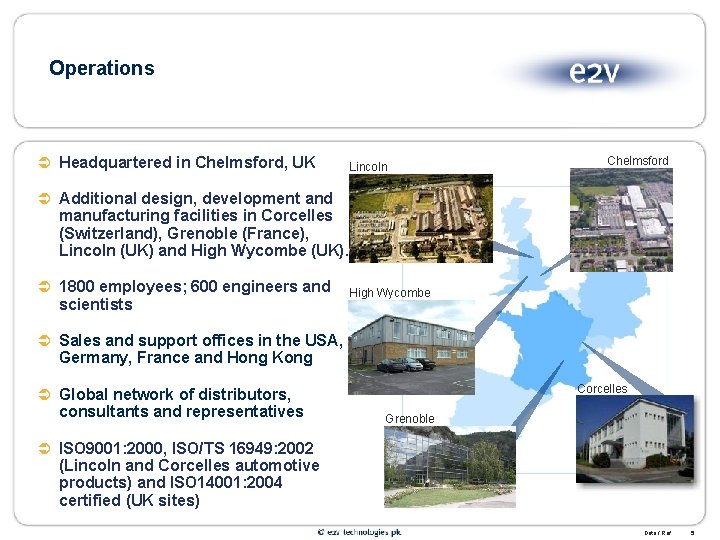

Operations Ü Headquartered in Chelmsford, UK Lincoln Chelmsford Ü Additional design, development and manufacturing facilities in Corcelles (Switzerland), Grenoble (France), Lincoln (UK) and High Wycombe (UK). Ü 1800 employees; 600 engineers and scientists High Wycombe Ü Sales and support offices in the USA, Germany, France and Hong Kong Corcelles Ü Global network of distributors, consultants and representatives Grenoble Ü ISO 9001: 2000, ISO/TS 16949: 2002 (Lincoln and Corcelles automotive products) and ISO 14001: 2004 certified (UK sites) Date / Ref 5

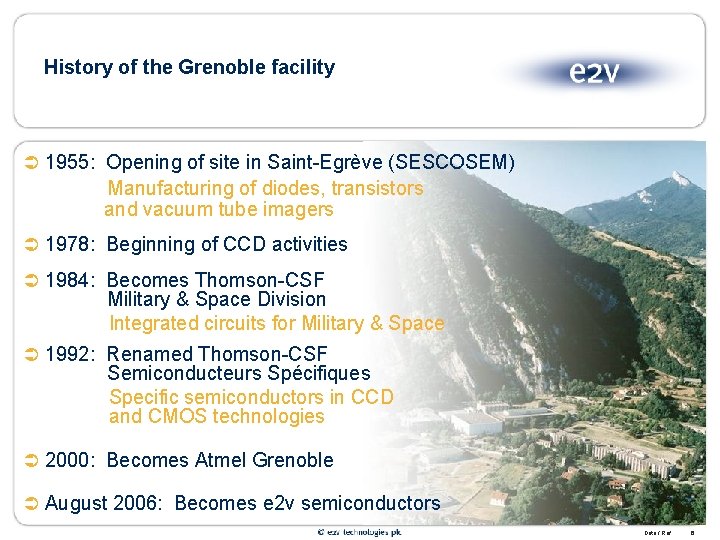

History of the Grenoble facility Ü 1955: Opening of site in Saint-Egrève (SESCOSEM) Manufacturing of diodes, transistors and vacuum tube imagers Ü 1978: Beginning of CCD activities Ü 1984: Becomes Thomson-CSF Military & Space Division Integrated circuits for Military & Space Ü 1992: Renamed Thomson-CSF Semiconducteurs Spécifiques Specific semiconductors in CCD and CMOS technologies Ü 2000: Becomes Atmel Grenoble Ü August 2006: Becomes e 2 v semiconductors Date / Ref 6

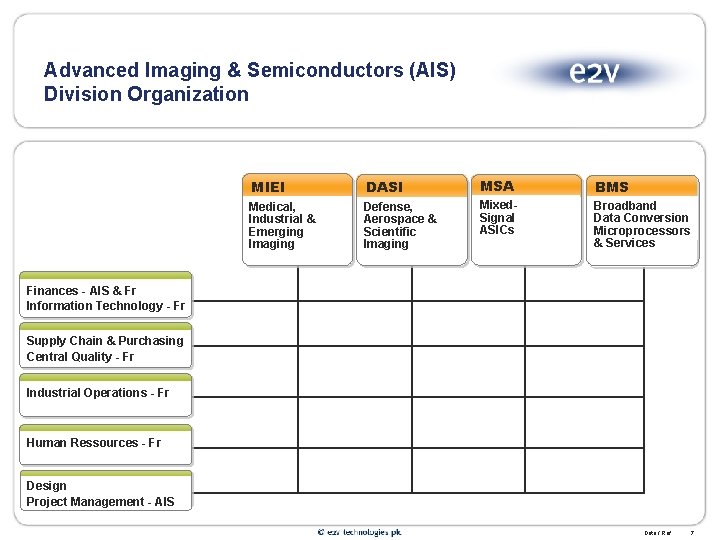

Advanced Imaging & Semiconductors (AIS) Division Organization MIEI DASI MSA BMS Medical, Industrial & Emerging Imaging Defense, Aerospace & Scientific Imaging Mixed. Signal ASICs Broadband Data Conversion Microprocessors & Services Finances - AIS & Fr Information Technology - Fr Supply Chain & Purchasing Central Quality - Fr Industrial Operations - Fr Human Ressources - Fr Design Project Management - AIS Date / Ref 7

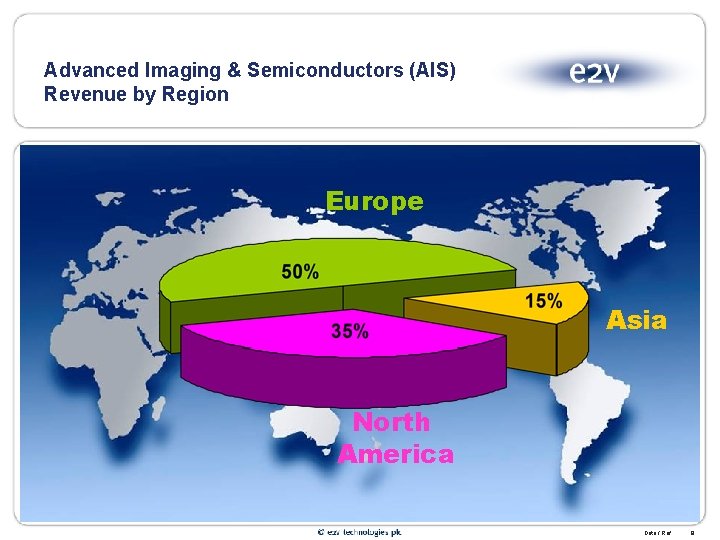

Advanced Imaging & Semiconductors (AIS) Revenue by Region Europe Asia North America Date / Ref 8

Grenoble Industrial Facilities Wafer Fab Ü Front-end Ü Class 10 and 1 clean rooms Ü CCD technology Ü CMOS imager and sensor post-processing Date / Ref 9

Grenoble Industrial Facilities Package Assembly Ü #1 Hi-Rel assembly facility in Europe Ü 600 sq. meters, Class 100 clean room Ü Die processing capability Ü Screening levels up to Space-grade (QML Class V) Ü Low and Medium volume (up to 1 M/year) Ü Hermetic ceramic packages DIL CPGA CQFP CLCC Ü Flip-Chip ceramic BGA packages CBGA Hi-TCE CBGA Date / Ref 10

Grenoble Industrial Facilities Electrical Test & Screening Ü Automatic Test Equipment CCD & CMOS image sensor Ü Teradyne A 393, A 565 IH, IP 750 and dedicated test-bench Mixed & RF IC Ü Teradyne A 567 (x 3), A 585 Digital IC Ü Teradyne J 971, J 973, Tiger Next. Test PTHF 64 Ü Low/high temperature handlers and probers Ü EG 4080/4090 probers Ü Multitest, Delta design, Aseco S 130 Ü Reliability and burn-in Date / Ref 11

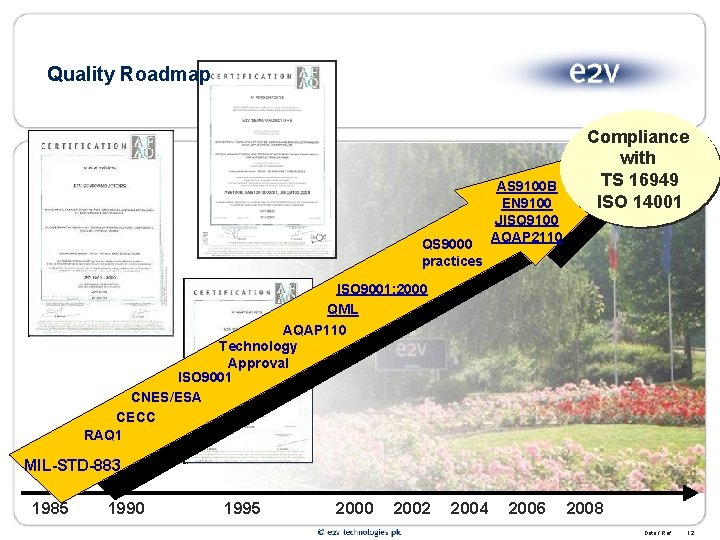

Quality Roadmap QS 9000 practices AS 9100 B EN 9100 JISQ 9100 AQAP 2110 Compliance with TS 16949 ISO 14001 ISO 9001: 2000 QML AQAP 110 Technology Approval ISO 9001 CNES/ESA CECC RAQ 1 MIL-STD-883 1985 1990 1995 2000 2002 2004 2006 2008 Date / Ref 12

BMS Business Unit Broadband Data Conversion Microprocessors and Services Date / Ref 13

BMS at glance Hi-Rel Microprocessors product offer • • • T M Freescale upscreened Microprocessors : 68 K, Power. PC G 2, G 3 and G 4 (since 1980) Integrated Processors and Communication Controllers : 68 K and 82 xx Peripheral devices: Tundra PCI Bridge & Memory Controllers, Clock Drivers… Added-value services and solutions • • Electrical Test and Characterization over wide temperature range Enhanced Reliability Packaging: Hi-TCE Ceramic, Column-Interposer, hermetic packages Die Processing : High and Low temperature electrical test and screening Long term availability : Long life time item selection and die-banking capability Broadband Data Converter product offer • • Commercial & Industrial grade data converters: 8 -bit 5 Gsps to 12 -bit 500 Msps Military & Space grade data converters: 8 -bit 1 Gsps to 10 -bit 2. 2 Gsps ASSPs (Application Specific Standard Product): commercial through space grades ASICs: commercial through space grades Date / Ref 14

Hi-Rel Microprocessors – Mission Statement The Hi-Rel Microprocessors Product Line of e 2 v delivers a wide range of Extended Reliability Products and Services based on Power. PC and 68 K microprocessors for Professional Electronics markets Ü Host Processors and Integrated Processors Üin partnership with Freescale since 1980 T M Ü System Interconnect Products Üin partnership with Tundra, formal agreement signed in July 2006 Ü Added-Value services and solutions ÜElectrical Test and Characterization over wide temperature range ÜEnhanced Reliability Packaging: Hi-TCE Ceramic, Column-Interposer, hermetic packages ÜDie Processing : High and Low temperature electrical test and screening ÜLong term availability : Long life time item selection and die-banking capability ÜCompanion devices Assembly & Test Services (FSRAM’s, SDRAM’s, ASIC’s, . . . ) Date / Ref 15

Broadband Data Converters - over 45 years of combined expertise Ü 15 data converter design engineers for custom and COTS development: Ü Dedicated solely to ADC, DAC and peripherals designs (no timesharing) Ü High speed (>500 Msps to 2. 2 Gsps and beyond) data converter designs (4 designs per year on average) Ü Peripheral devices design (HSSL, DMUX, memory, etc. . ) Ü Over 35 patents registered in high speed high linearity data converters: Ü Data converter core design & architecture Ü Data converter T/H design Ü etc. . Ü State-of-the-art development labs for characterization of: Ü High speed ADC characterization Ü High speed DAC characterization Ü Temperature extremes/mechanical shock/design limits validation Date / Ref 16

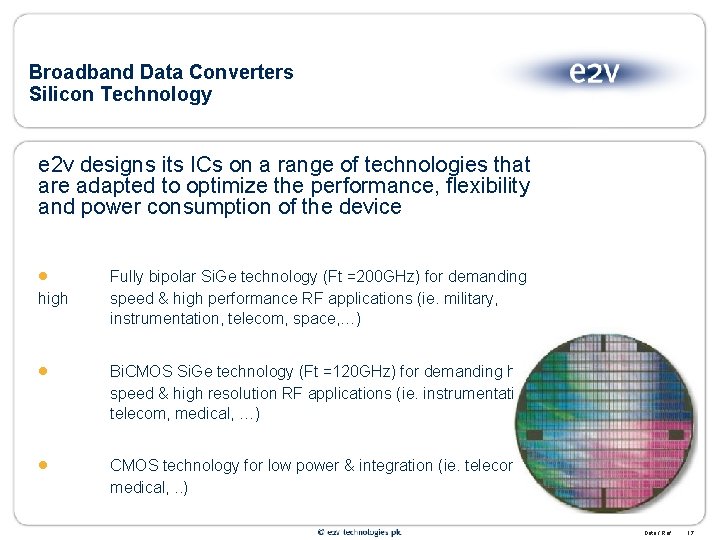

Broadband Data Converters Silicon Technology e 2 v designs its ICs on a range of technologies that are adapted to optimize the performance, flexibility and power consumption of the device · high Fully bipolar Si. Ge technology (Ft =200 GHz) for demanding speed & high performance RF applications (ie. military, instrumentation, telecom, space, …) · Bi. CMOS Si. Ge technology (Ft =120 GHz) for demanding high speed & high resolution RF applications (ie. instrumentation, telecom, medical, …) · CMOS technology for low power & integration (ie. telecom, medical, . . ) Date / Ref 17

Broadband Data Converters Applications Defense : Radar & ECW Guided weapons Space: Comsat & military satellites Terrestrial base stations Radio antenna arrays Test Equipment: Digital oscilloscope ATE (semi-conductor) Industrial: Telecom infrastructures Medical imaging (MRI. . ) Date / Ref 18

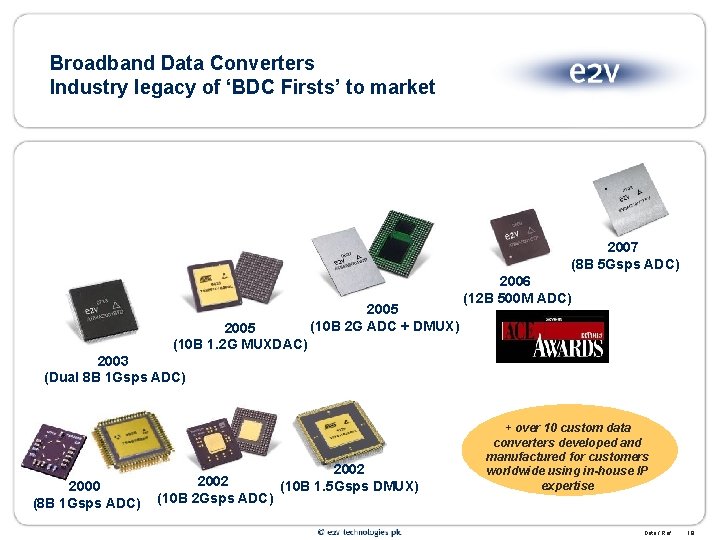

Broadband Data Converters Industry legacy of ‘BDC Firsts’ to market 2007 (8 B 5 Gsps ADC) 2005 (10 B 1. 2 G MUXDAC) 2005 (10 B 2 G ADC + DMUX) 2006 (12 B 500 M ADC) 2003 (Dual 8 B 1 Gsps ADC) 2000 (8 B 1 Gsps ADC) 2002 (10 B 1. 5 Gsps DMUX) (10 B 2 Gsps ADC) + over 10 custom data converters developed and manufactured for customers worldwide using in-house IP expertise Date / Ref 19

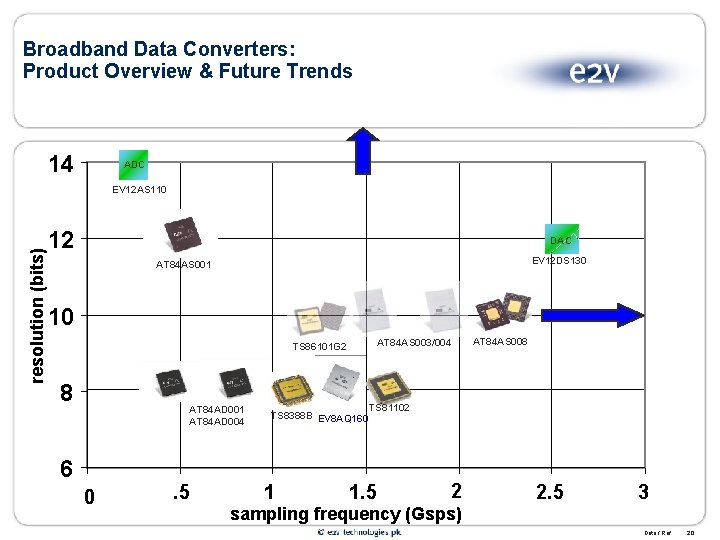

Broadband Data Converters: Product Overview & Future Trends 14 ADC resolution (bits) EV 12 AS 110 12 DAC EV 12 DS 130 AT 84 AS 001 10 AT 84 AS 003/004 TS 86101 G 2 8 AT 84 AD 001 AT 84 AD 004 6 0 . 5 TS 8388 B EV 8 AQ 160 1 AT 84 AS 008 TS 81102 1. 5 2 2. 5 3 sampling frequency (Gsps) Date / Ref 20

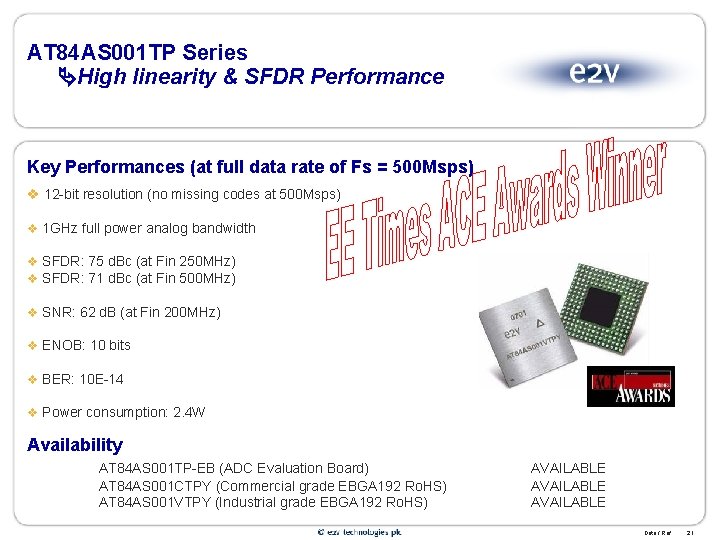

AT 84 AS 001 TP Series High linearity & SFDR Performance Key Performances (at full data rate of Fs = 500 Msps) v 12 -bit resolution (no missing codes at 500 Msps) v 1 GHz full power analog bandwidth v SFDR: 75 d. Bc (at Fin 250 MHz) v SFDR: 71 d. Bc (at Fin 500 MHz) v SNR: 62 d. B (at Fin 200 MHz) v ENOB: 10 bits v BER: 10 E-14 v Power consumption: 2. 4 W Availability AT 84 AS 001 TP-EB (ADC Evaluation Board) AT 84 AS 001 CTPY (Commercial grade EBGA 192 Ro. HS) AT 84 AS 001 VTPY (Industrial grade EBGA 192 Ro. HS) AVAILABLE Date / Ref 21

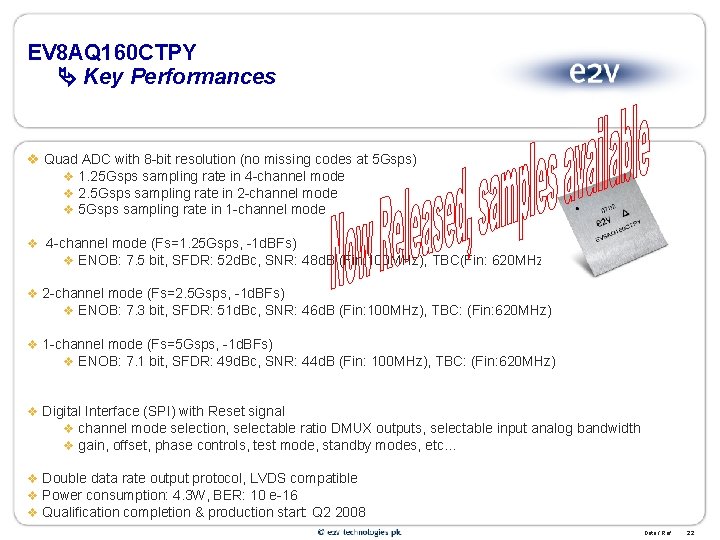

EV 8 AQ 160 CTPY Key Performances v Quad ADC with 8 -bit resolution (no missing codes at 5 Gsps) v 1. 25 Gsps sampling rate in 4 -channel mode v 2. 5 Gsps sampling rate in 2 -channel mode v 5 Gsps sampling rate in 1 -channel mode v 4 -channel mode (Fs=1. 25 Gsps, -1 d. BFs) v ENOB: 7. 5 bit, SFDR: 52 d. Bc, SNR: 48 d. B (Fin: 100 MHz), TBC(Fin: 620 MHz) v 2 -channel mode (Fs=2. 5 Gsps, -1 d. BFs) v ENOB: 7. 3 bit, SFDR: 51 d. Bc, SNR: 46 d. B (Fin: 100 MHz), TBC: (Fin: 620 MHz) v 1 -channel mode (Fs=5 Gsps, -1 d. BFs) v ENOB: 7. 1 bit, SFDR: 49 d. Bc, SNR: 44 d. B (Fin: 100 MHz), TBC: (Fin: 620 MHz) v Digital Interface (SPI) with Reset signal v channel mode selection, selectable ratio DMUX outputs, selectable input analog bandwidth v gain, offset, phase controls, test mode, standby modes, etc… v Double data rate output protocol, LVDS compatible v Power consumption: 4. 3 W, BER: 10 e-16 v Qualification completion & production start: Q 2 2008 Date / Ref 22

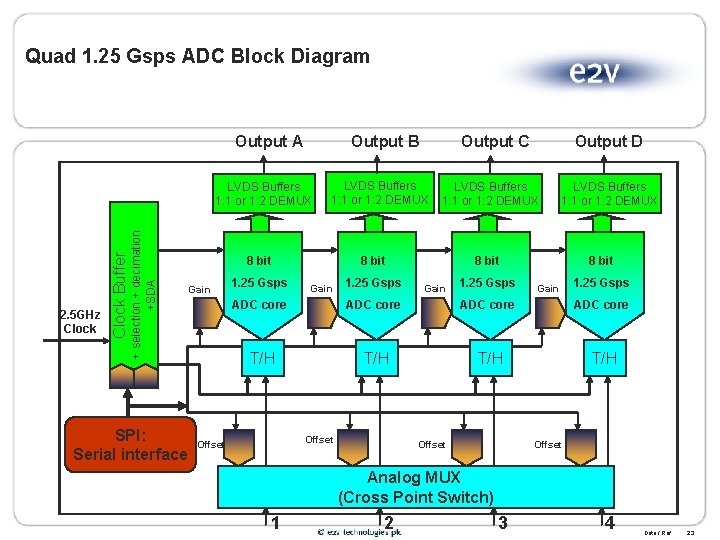

Quad 1. 25 Gsps ADC Block Diagram Output A Output B + selection + decimation +SDA 2. 5 GHz Clock Buffer LVDS Buffers 1: 1 or 1: 2 DEMUX SPI: Serial interface LVDS Buffers 1: 1 or 1: 2 DEMUX 8 bit Gain 1. 25 Gsps Output C LVDS Buffers 1: 1 or 1: 2 DEMUX 8 bit Gain 1. 25 Gsps Output D LVDS Buffers 1: 1 or 1: 2 DEMUX 8 bit Gain 1. 25 Gsps ADC core T/H T/H Offset Analog MUX (Cross Point Switch) 1 2 3 4 Date / Ref 23

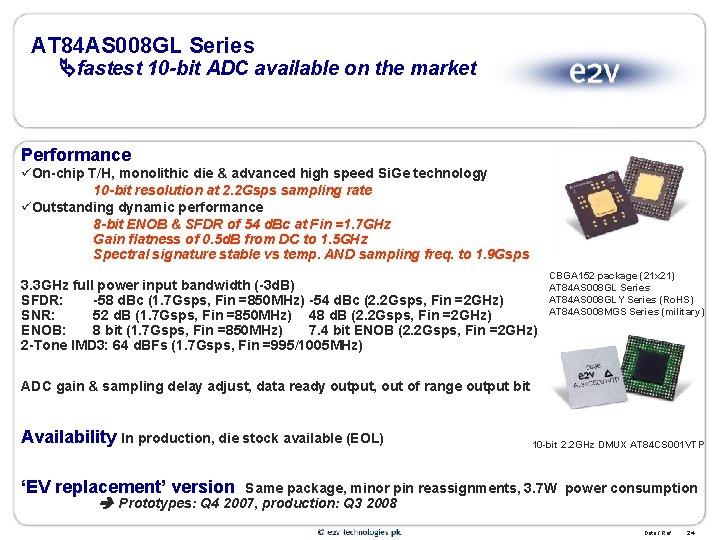

AT 84 AS 008 GL Series fastest 10 -bit ADC available on the market Performance üOn-chip T/H, monolithic die & advanced high speed Si. Ge technology 10 -bit resolution at 2. 2 Gsps sampling rate üOutstanding dynamic performance 8 -bit ENOB & SFDR of 54 d. Bc at Fin =1. 7 GHz Gain flatness of 0. 5 d. B from DC to 1. 5 GHz Spectral signature stable vs temp. AND sampling freq. to 1. 9 Gsps 3. 3 GHz full power input bandwidth (-3 d. B) SFDR: -58 d. Bc (1. 7 Gsps, Fin =850 MHz) -54 d. Bc (2. 2 Gsps, Fin =2 GHz) SNR: 52 d. B (1. 7 Gsps, Fin =850 MHz) 48 d. B (2. 2 Gsps, Fin =2 GHz) ENOB: 8 bit (1. 7 Gsps, Fin =850 MHz) 7. 4 bit ENOB (2. 2 Gsps, Fin =2 GHz) 2 -Tone IMD 3: 64 d. BFs (1. 7 Gsps, Fin =995/1005 MHz) CBGA 152 package (21 x 21) AT 84 AS 008 GL Series AT 84 AS 008 GLY Series (Ro. HS) AT 84 AS 008 MGS Series (military) ADC gain & sampling delay adjust, data ready output, out of range output bit Availability In production, die stock available (EOL) 10 -bit 2. 2 GHz DMUX AT 84 CS 001 VTP ‘EV replacement’ version Same package, minor pin reassignments, 3. 7 W power consumption Prototypes: Q 4 2007, production: Q 3 2008 Date / Ref 24

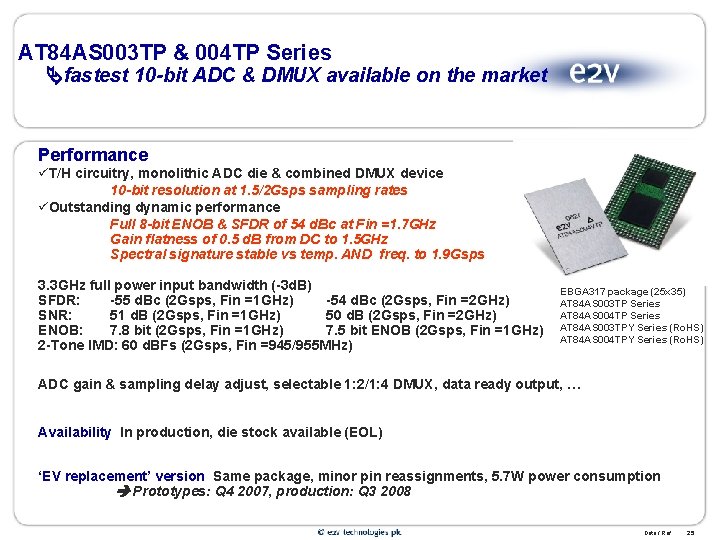

AT 84 AS 003 TP & 004 TP Series fastest 10 -bit ADC & DMUX available on the market Performance üT/H circuitry, monolithic ADC die & combined DMUX device 10 -bit resolution at 1. 5/2 Gsps sampling rates üOutstanding dynamic performance Full 8 -bit ENOB & SFDR of 54 d. Bc at Fin =1. 7 GHz Gain flatness of 0. 5 d. B from DC to 1. 5 GHz Spectral signature stable vs temp. AND freq. to 1. 9 Gsps 3. 3 GHz full power input bandwidth (-3 d. B) SFDR: -55 d. Bc (2 Gsps, Fin =1 GHz) -54 d. Bc (2 Gsps, Fin =2 GHz) SNR: 51 d. B (2 Gsps, Fin =1 GHz) 50 d. B (2 Gsps, Fin =2 GHz) ENOB: 7. 8 bit (2 Gsps, Fin =1 GHz) 7. 5 bit ENOB (2 Gsps, Fin =1 GHz) 2 -Tone IMD: 60 d. BFs (2 Gsps, Fin =945/955 MHz) EBGA 317 package (25 x 35) AT 84 AS 003 TP Series AT 84 AS 004 TP Series AT 84 AS 003 TPY Series (Ro. HS) AT 84 AS 004 TPY Series (Ro. HS) ADC gain & sampling delay adjust, selectable 1: 2/1: 4 DMUX, data ready output, … Availability In production, die stock available (EOL) ‘EV replacement’ version Same package, minor pin reassignments, 5. 7 W power consumption Prototypes: Q 4 2007, production: Q 3 2008 Date / Ref 25

Hi-Rel Microprocessors - Applications Defense & Aerospace • • • Radars Electronic warfare Counter measures Avionics • • • Flight computers Flight control systems Voice data recorders Displays Engine control Industrial & Communication • • Transportation Systems Heavy industries Industrial Computers Power plant control Date / Ref 26

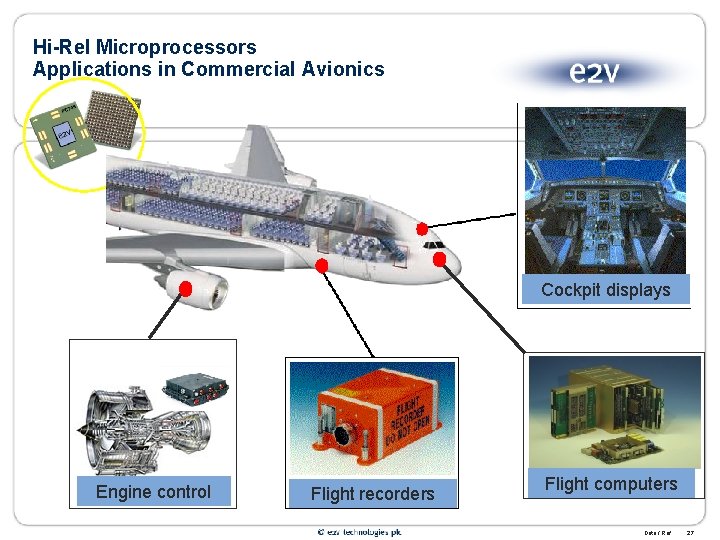

Hi-Rel Microprocessors Applications in Commercial Avionics Cockpit displays Engine control Motor control Flight recorders Ordinateurs de Bord Flight computers Date / Ref 27

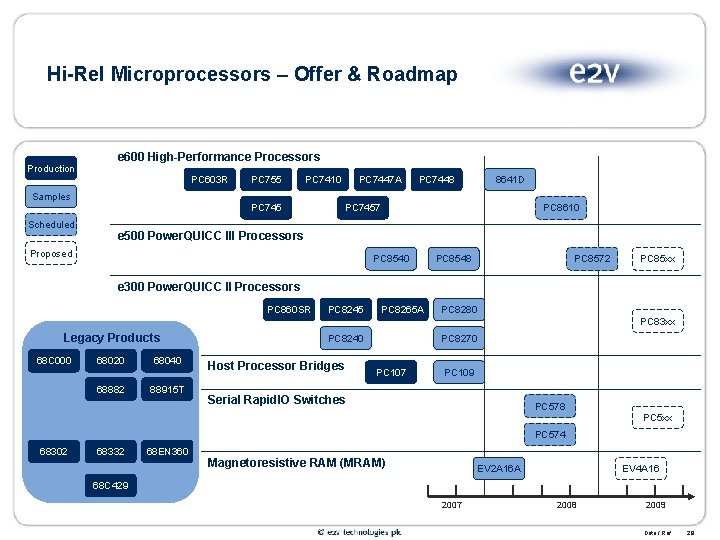

Hi-Rel Microprocessors – Offer & Roadmap Production e 600 High-Performance Processors PC 603 R PC 755 PC 7410 PC 7447 A PC 7448 PC 8641 D Samples PC 745 Scheduled PC 7457 PC 8610 e 500 Power. QUICC III Processors Proposed PC 8540 PC 8548 PC 8572 PC 85 xx e 300 Power. QUICC II Processors PC 860 SR PC 8245 PC 8265 A PC 8280 PC 83 xx Legacy Products 68 C 000 68020 68882 68040 88915 T PC 8240 Host Processor Bridges PC 8270 PC 107 PC 109 Serial Rapid. IO Switches PC 578 PC 5 xx PC 574 68302 68332 68 EN 360 Magnetoresistive RAM (MRAM) EV 2 A 16 A EV 4 A 16 68 C 429 2007 2008 2009 Date / Ref 28

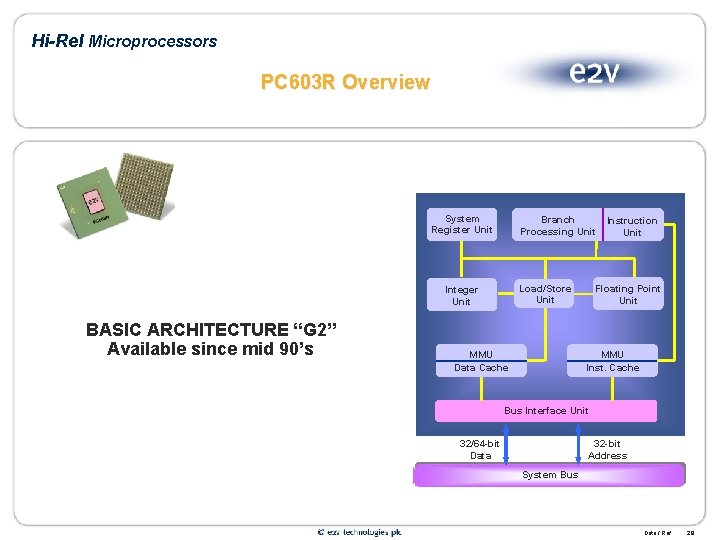

Hi-Rel Microprocessors PC 603 R Overview System Register Unit Branch Processing Unit Load/Store Unit Integer Unit BASIC ARCHITECTURE “G 2” Available since mid 90’s MMU Data Cache Instruction Unit Floating Point Unit MMU Inst. Cache Bus Interface Unit 32 -bit Address 32/64 -bit Data System Bus Date / Ref 29

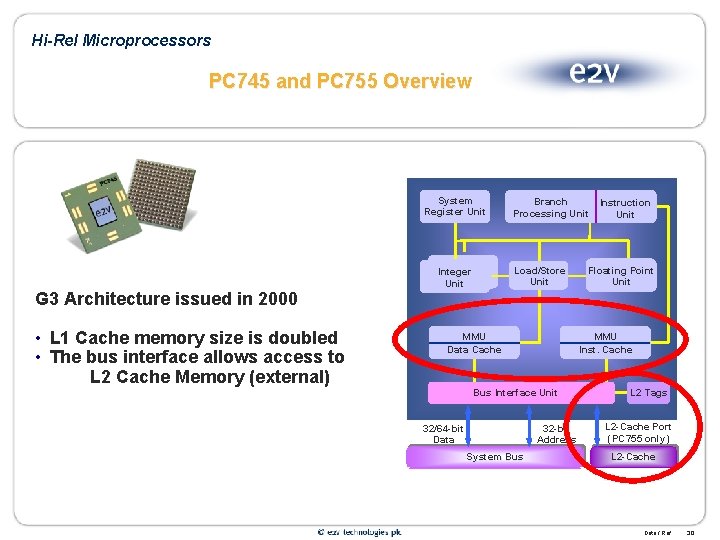

Hi-Rel Microprocessors PC 745 and PC 755 Overview System Register Unit G 3 Architecture issued in 2000 • L 1 Cache memory size is doubled • The bus interface allows access to L 2 Cache Memory (external) Integer Unit Branch Processing Unit Load/Store Unit MMU Data Cache 32 -bit Address System Bus Floating Point Unit MMU Inst. Cache Bus Interface Unit 32/64 -bit Data Instruction Unit L 2 Tags L 2 -Cache Port (PC 755 only) L 2 -Cache Date / Ref 30

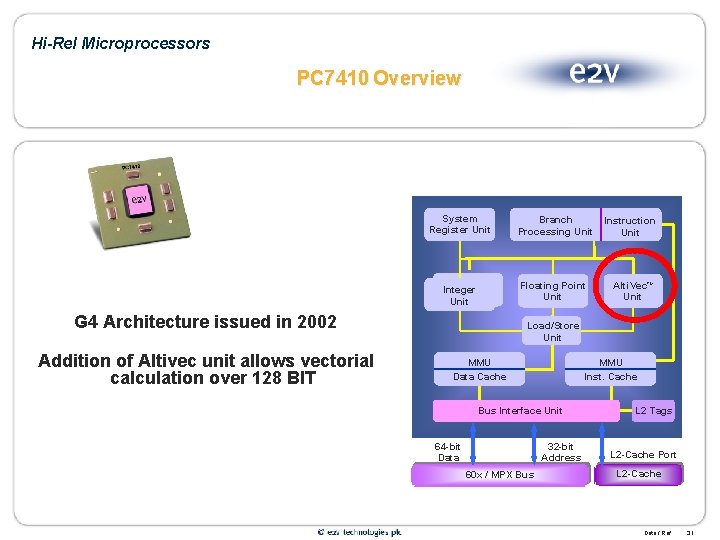

Hi-Rel Microprocessors PC 7410 Overview System Register Unit Integer Unit G 4 Architecture issued in 2002 Addition of Altivec unit allows vectorial calculation over 128 BIT Branch Processing Unit Instruction Unit Floating Point Unit Alti. Vec Unit TM Load/Store Unit MMU Data Cache MMU Inst. Cache Bus Interface Unit 64 -bit Data 32 -bit Address 60 x / MPX Bus L 2 Tags L 2 -Cache Port L 2 -Cache Date / Ref 31

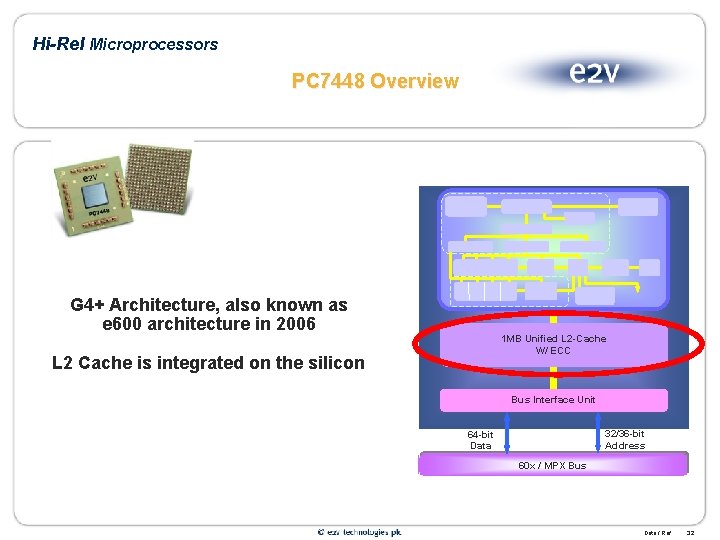

Hi-Rel Microprocessors PC 7448 Overview G 4+ Architecture, also known as e 600 architecture in 2006 1 MB Unified L 2 -Cache W/ ECC L 2 Cache is integrated on the silicon Bus Interface Unit 32/36 -bit Address 64 -bit Data 60 x / MPX Bus Date / Ref 32

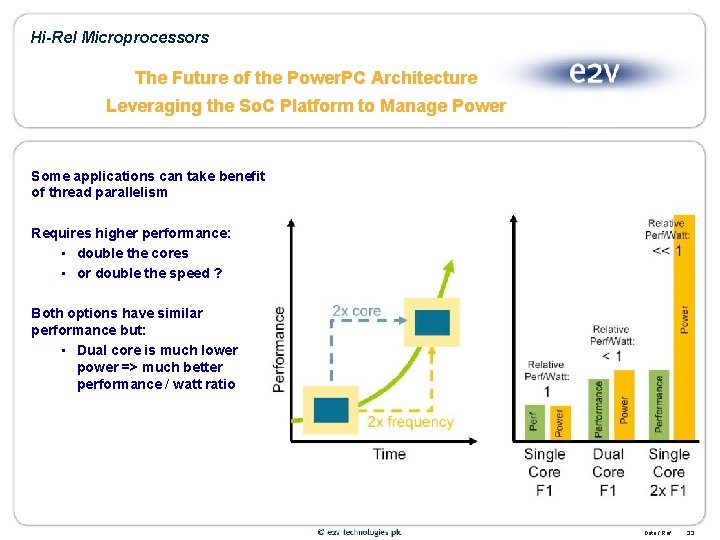

Hi-Rel Microprocessors The Future of the Power. PC Architecture Leveraging the So. C Platform to Manage Power Some applications can take benefit of thread parallelism Requires higher performance: • double the cores • or double the speed ? Both options have similar performance but: • Dual core is much lower power => much better performance / watt ratio Date / Ref 33

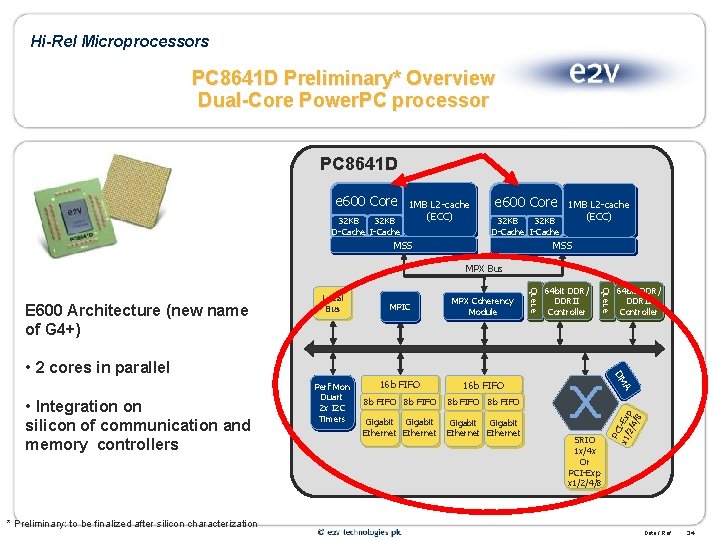

Hi-Rel Microprocessors PC 8641 D Preliminary* Overview Dual-Core Power. PC processor PC 8641 D e 600 Core 32 KB D-Cache I-Cache 1 MB L 2 -cache (ECC) e 600 Core 32 KB D-Cache I-Cache MSS 1 MB L 2 -cache (ECC) MSS MPX Bus 16 b FIFO 8 b FIFO Gigabit Ethernet • Integration on silicon of communication and memory controllers Perf Mon Duart 2 x I 2 C Timers A DM • 2 cores in parallel 64 bit DDR/ DDRII Controller SRIO 1 x/4 x Or PCI-Exp x 1/2/4/8 PC x 1 I-Exp /2/ 4/8 16 b FIFO 64 bit DDR/ DDRII Controller Queue MPIC MPX Coherency Module Queue E 600 Architecture (new name of G 4+) Local Bus * Preliminary: to be finalized after silicon characterization Date / Ref 34

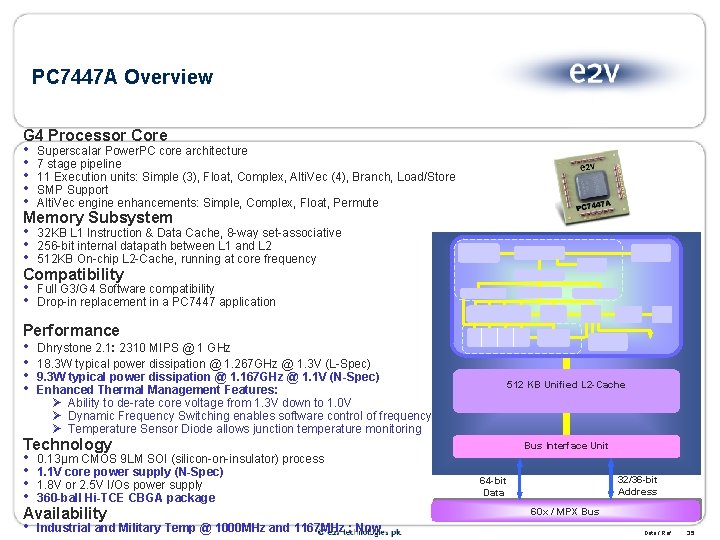

PC 7447 A Overview G 4 Processor Core • Superscalar Power. PC core architecture • 7 stage pipeline • 11 Execution units: Simple (3), Float, Complex, Alti. Vec (4), Branch, Load/Store • SMP Support • Alti. Vec engine enhancements: Simple, Complex, Float, Permute Memory Subsystem • 32 KB L 1 Instruction & Data Cache, 8 -way set-associative • 256 -bit internal datapath between L 1 and L 2 • 512 KB On-chip L 2 -Cache, running at core frequency Compatibility • Full G 3/G 4 Software compatibility • Drop-in replacement in a PC 7447 application Performance • Dhrystone 2. 1: 2310 MIPS @ 1 GHz • 18. 3 W typical power dissipation @ 1. 267 GHz @ 1. 3 V (L-Spec) • 9. 3 W typical power dissipation @ 1. 167 GHz @ 1. 1 V (N-Spec) • Enhanced Thermal Management Features: 512 KB Unified L 2 -Cache Ø Ability to de-rate core voltage from 1. 3 V down to 1. 0 V Ø Dynamic Frequency Switching enables software control of frequency Ø Temperature Sensor Diode allows junction temperature monitoring Technology • 0. 13µm CMOS 9 LM SOI (silicon-on-insulator) process • 1. 1 V core power supply (N-Spec) • 1. 8 V or 2. 5 V I/Os power supply • 360 -ball Hi-TCE CBGA package Availability • Industrial and Military Temp @ 1000 MHz and 1167 MHz : Now Bus Interface Unit 32/36 -bit Address 64 -bit Data 60 x / MPX Bus Date / Ref 35

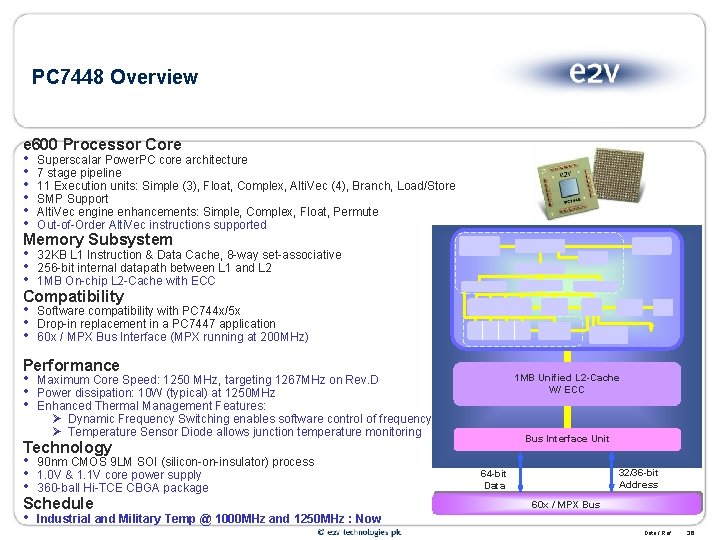

PC 7448 Overview e 600 Processor Core • Superscalar Power. PC core architecture • 7 stage pipeline • 11 Execution units: Simple (3), Float, Complex, Alti. Vec (4), Branch, Load/Store • SMP Support • Alti. Vec engine enhancements: Simple, Complex, Float, Permute • Out-of-Order Alti. Vec instructions supported Memory Subsystem • 32 KB L 1 Instruction & Data Cache, 8 -way set-associative • 256 -bit internal datapath between L 1 and L 2 • 1 MB On-chip L 2 -Cache with ECC Compatibility • Software compatibility with PC 744 x/5 x • Drop-in replacement in a PC 7447 application • 60 x / MPX Bus Interface (MPX running at 200 MHz) Performance • Maximum Core Speed: 1250 MHz, targeting 1267 MHz on Rev. D • Power dissipation: 10 W (typical) at 1250 MHz • Enhanced Thermal Management Features: 1 MB Unified L 2 -Cache W/ ECC Ø Dynamic Frequency Switching enables software control of frequency Ø Temperature Sensor Diode allows junction temperature monitoring Technology • 90 nm CMOS 9 LM SOI (silicon-on-insulator) process • 1. 0 V & 1. 1 V core power supply • 360 -ball Hi-TCE CBGA package Schedule • Industrial and Military Temp @ 1000 MHz and 1250 MHz : Now Bus Interface Unit 32/36 -bit Address 64 -bit Data 60 x / MPX Bus Date / Ref 36

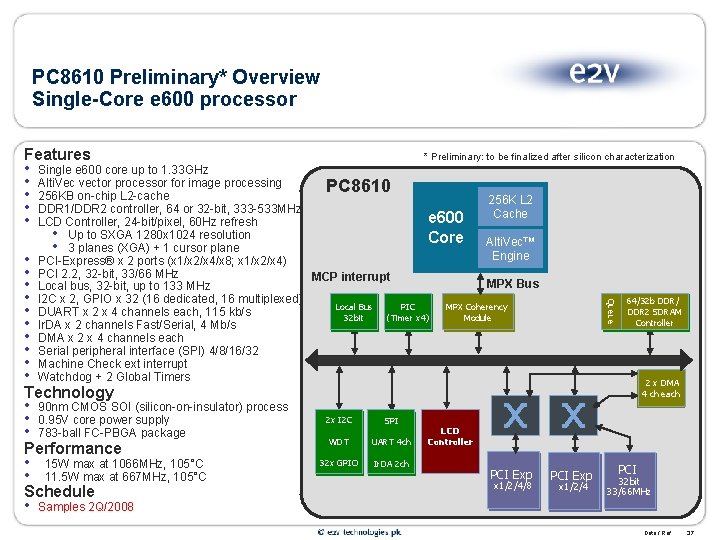

PC 8610 Preliminary* Overview Single-Core e 600 processor * Preliminary: to be finalized after silicon characterization PC 8610 e 600 Core MCP interrupt Local Bus 32 bit 256 K L 2 Cache Alti. Vec™ Engine MPX Bus PIC (Timer x 4) Queue Features • Single e 600 core up to 1. 33 GHz • Alti. Vec vector processor for image processing • 256 KB on-chip L 2 -cache • DDR 1/DDR 2 controller, 64 or 32 -bit, 333 -533 MHz • LCD Controller, 24 -bit/pixel, 60 Hz refresh • Up to SXGA 1280 x 1024 resolution • 3 planes (XGA) + 1 cursor plane • PCI-Express® x 2 ports (x 1/x 2/x 4/x 8; x 1/x 2/x 4) • PCI 2. 2, 32 -bit, 33/66 MHz • Local bus, 32 -bit, up to 133 MHz • I 2 C x 2, GPIO x 32 (16 dedicated, 16 multiplexed) • DUART x 2 x 4 channels each, 115 kb/s • Ir. DA x 2 channels Fast/Serial, 4 Mb/s • DMA x 2 x 4 channels each • Serial peripheral interface (SPI) 4/8/16/32 • Machine Check ext interrupt • Watchdog + 2 Global Timers Technology • 90 nm CMOS SOI (silicon-on-insulator) process • 0. 95 V core power supply • 783 -ball FC-PBGA package Performance • 15 W max at 1066 MHz, 105°C • 11. 5 W max at 667 MHz, 105°C Schedule • Samples 2 Q/2008 MPX Coherency Module 64/32 b DDR/ DDR 2 SDRAM Controller 2 x DMA 4 ch each 2 x I 2 C SPI WDT UART 4 ch 32 x GPIO Ir. DA 2 ch LCD Controller PCI Exp x 1/2/4/8 PCI Exp x 1/2/4 PCI 32 bit 33/66 MHz Date / Ref 37

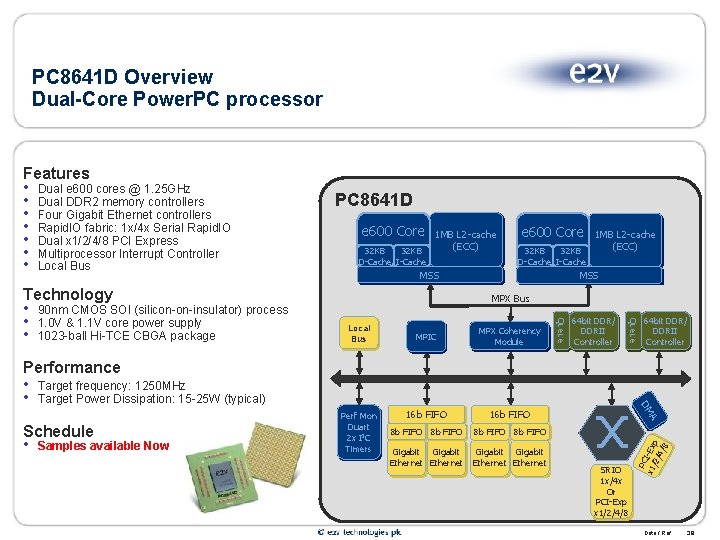

PC 8641 D Overview Dual-Core Power. PC processor e 600 Core 32 KB D-Cache I-Cache 1 MB L 2 -cache (ECC) e 600 Core 32 KB D-Cache I-Cache MSS 1 MB L 2 -cache (ECC) MSS MPX Bus MPIC MPX Coherency Module 16 b FIFO 8 b FIFO Gigabit Ethernet 64 bit DDR/ DDRII Controller Queue Local Bus Queue Technology • 90 nm CMOS SOI (silicon-on-insulator) process • 1. 0 V & 1. 1 V core power supply • 1023 -ball Hi-TCE CBGA package PC 8641 D Schedule • Samples available Now Perf Mon Duart 2 x I 2 C Timers A DM Performance • Target frequency: 1250 MHz • Target Power Dissipation: 15 -25 W (typical) 64 bit DDR/ DDRII Controller SRIO 1 x/4 x Or PCI-Exp x 1/2/4/8 PC x 1 I-Exp /2/ 4/8 Features • Dual e 600 cores @ 1. 25 GHz • Dual DDR 2 memory controllers • Four Gigabit Ethernet controllers • Rapid. IO fabric: 1 x/4 x Serial Rapid. IO • Dual x 1/2/4/8 PCI Express • Multiprocessor Interrupt Controller • Local Bus Date / Ref 38

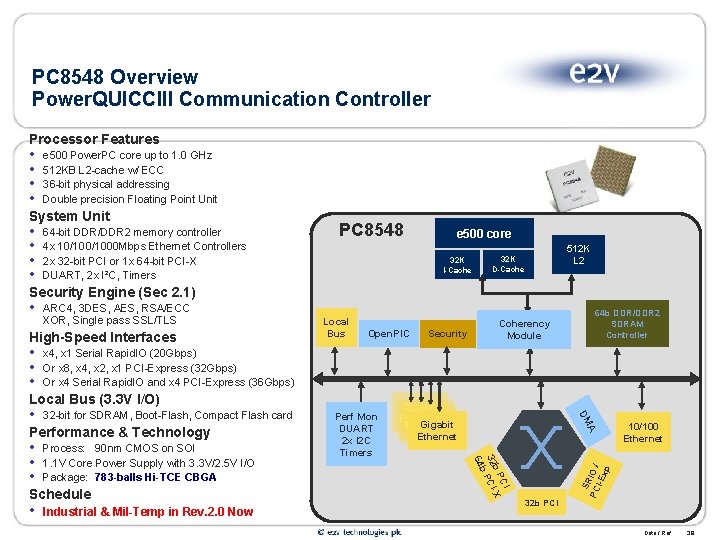

PC 8548 Overview Power. QUICCIII Communication Controller Processor Features • • e 500 Power. PC core up to 1. 0 GHz 512 KB L 2 -cache w/ ECC 36 -bit physical addressing Double precision Floating Point Unit System Unit • • 64 -bit DDR/DDR 2 memory controller 4 x 10/1000 Mbps Ethernet Controllers 2 x 32 -bit PCI or 1 x 64 -bit PCI-X DUART, 2 x I²C, Timers PC 8548 e 500 core 32 K I-Cache 512 K L 2 32 K D-Cache Security Engine (Sec 2. 1) ARC 4, 3 DES, AES, RSA/ECC XOR, Single pass SSL/TLS High-Speed Interfaces • • • Local Bus Open. PIC Schedule • Industrial & Mil-Temp in Rev. 2. 0 Now Gigabit Ethernet CI b. P X 32 PCIb 64 Process: 90 nm CMOS on SOI 1. 1 V Core Power Supply with 3. 3 V/2. 5 V I/O Package: 783 -balls Hi-TCE CBGA Perf Mon DUART 2 x I 2 C Timers A DM 32 -bit for SDRAM, Boot-Flash, Compact Flash card Performance & Technology • • • 64 b DDR/DDR 2 SDRAM Controller x 4, x 1 Serial Rapid. IO (20 Gbps) Or x 8, x 4, x 2, x 1 PCI-Express (32 Gbps) Or x 4 Serial Rapid. IO and x 4 PCI-Express (36 Gbps) Local Bus (3. 3 V I/O) • Security Coherency Module 32 b PCI 10/100 Ethernet SR PC IO / I-E xp • Date / Ref 39

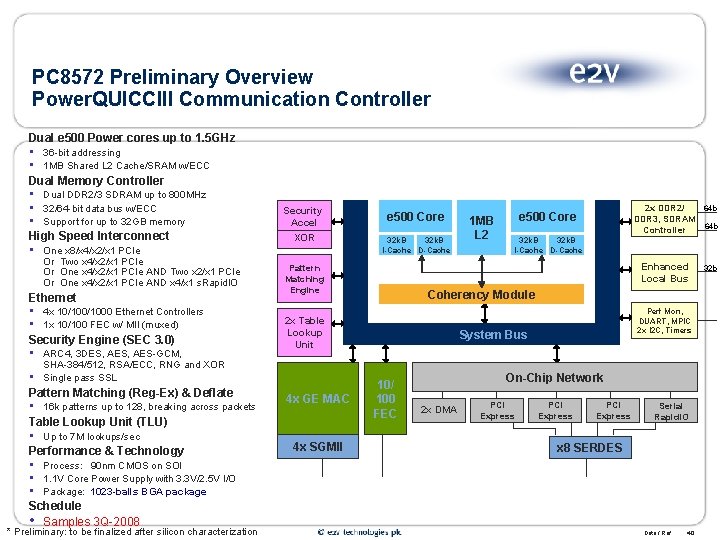

PC 8572 Preliminary Overview Power. QUICCIII Communication Controller Dual e 500 Power cores up to 1. 5 GHz • • 36 -bit addressing 1 MB Shared L 2 Cache/SRAM w/ECC Dual Memory Controller • • • Dual DDR 2/3 SDRAM up to 800 MHz 32/64 -bit data bus w/ECC Support for up to 32 GB memory High Speed Interconnect • One x 8/x 4/x 2/x 1 PCIe Or Two x 4/x 2/x 1 PCIe Or One x 4/x 2/x 1 PCIe AND Two x 2/x 1 PCIe Or One x 4/x 2/x 1 PCIe AND x 4/x 1 s. Rapid. IO Ethernet • • 4 x 10/1000 Ethernet Controllers 1 x 10/100 FEC w/ MII (muxed) Security Engine (SEC 3. 0) • • ARC 4, 3 DES, AES-GCM, SHA-384/512, RSA/ECC, RNG and XOR Single pass SSL Pattern Matching (Reg-Ex) & Deflate • 16 k patterns up to 128, breaking across packets Security Accel XOR Up to 7 M lookups/sec Performance & Technology • • • 32 k. B I-Cache D-Cache 4 x SGMII 32 k. B I-Cache D-Cache Coherency Module 2 x Table Lookup Unit 4 x GE MAC 1 MB L 2 64 b 2 x DDR 2/ DDR 3, SDRAM 64 b Controller e 500 Core Enhanced Local Bus Pattern Matching Engine Table Lookup Unit (TLU) • e 500 Core Perf Mon, DUART, MPIC 2 x I 2 C, Timers System Bus 10/ 100 FEC On-Chip Network 2 x DMA PCI Express Serial Rapid. IO x 8 SERDES Process: 90 nm CMOS on SOI 1. 1 V Core Power Supply with 3. 3 V/2. 5 V I/O Package: 1023 -balls BGA package Schedule • Samples 3 Q-2008 * Preliminary: to be finalized after silicon characterization Date / Ref 40 32 b

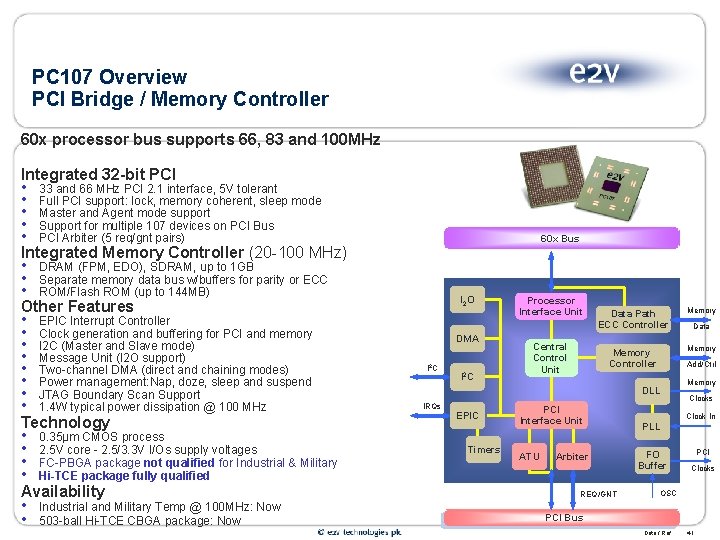

PC 107 Overview PCI Bridge / Memory Controller 60 x processor bus supports 66, 83 and 100 MHz Integrated 32 -bit PCI • 33 and 66 MHz PCI 2. 1 interface, 5 V tolerant • Full PCI support: lock, memory coherent, sleep mode • Master and Agent mode support • Support for multiple 107 devices on PCI Bus • PCI Arbiter (5 req/gnt pairs) Integrated Memory Controller (20 -100 MHz) • DRAM (FPM, EDO), SDRAM, up to 1 GB • Separate memory data bus w/buffers for parity or ECC • ROM/Flash ROM (up to 144 MB) Other Features • EPIC Interrupt Controller • Clock generation and buffering for PCI and memory • I 2 C (Master and Slave mode) • Message Unit (I 2 O support) • Two-channel DMA (direct and chaining modes) • Power management: Nap, doze, sleep and suspend • JTAG Boundary Scan Support • 1. 4 W typical power dissipation @ 100 MHz Technology • 0. 35µm CMOS process • 2. 5 V core - 2. 5/3. 3 V I/Os supply voltages • FC-PBGA package not qualified for Industrial & Military • Hi-TCE package fully qualified Availability • Industrial and Military Temp @ 100 MHz: Now • 503 -ball Hi-TCE CBGA package: Now 60 x Bus I 2 O DMA I 2 C Processor Interface Unit Central Control Unit Data Path ECC Controller Memory Add/Ctrl DLL IRQs EPIC Timers PCI Interface Unit ATU Arbiter REQ/GNT Data Memory Clocks Clock In PLL FO Buffer PCI Clocks OSC PCI Bus Date / Ref 41

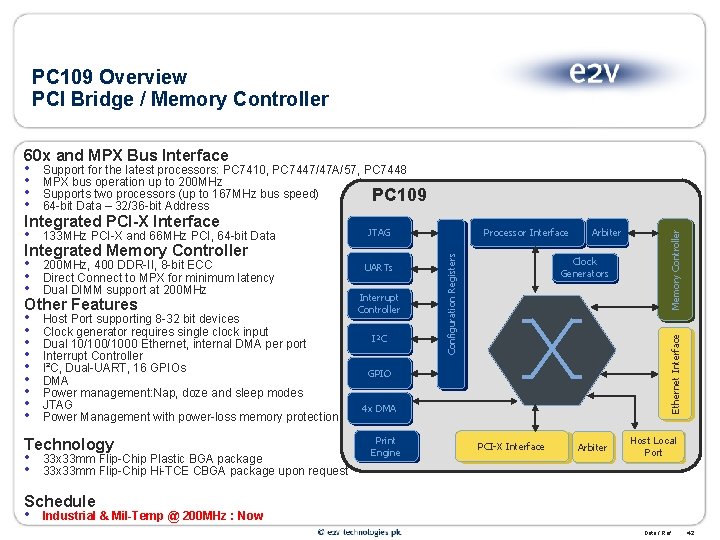

Technology • 33 x 33 mm Flip-Chip Plastic BGA package • 33 x 33 mm Flip-Chip Hi-TCE CBGA package upon request Print Engine Processor Interface Configuration Registers Arbiter Clock Generators Ethernet Interface 60 x and MPX Bus Interface • Support for the latest processors: PC 7410, PC 7447/47 A/57, PC 7448 • MPX bus operation up to 200 MHz • Supports two processors (up to 167 MHz bus speed) PC 109 • 64 -bit Data – 32/36 -bit Address Integrated PCI-X Interface JTAG • 133 MHz PCI-X and 66 MHz PCI, 64 -bit Data Integrated Memory Controller • 200 MHz, 400 DDR-II, 8 -bit ECC UARTs • Direct Connect to MPX for minimum latency • Dual DIMM support at 200 MHz Interrupt Other Features Controller • Host Port supporting 8 -32 bit devices • Clock generator requires single clock input I²C • Dual 10/1000 Ethernet, internal DMA per port • Interrupt Controller • I²C, Dual-UART, 16 GPIOs GPIO • DMA • Power management: Nap, doze and sleep modes • JTAG 4 x DMA • Power Management with power-loss memory protection Memory Controller PC 109 Overview PCI Bridge / Memory Controller PCI-X Interface Arbiter Host Local Port Schedule • Industrial & Mil-Temp @ 200 MHz : Now Date / Ref 42

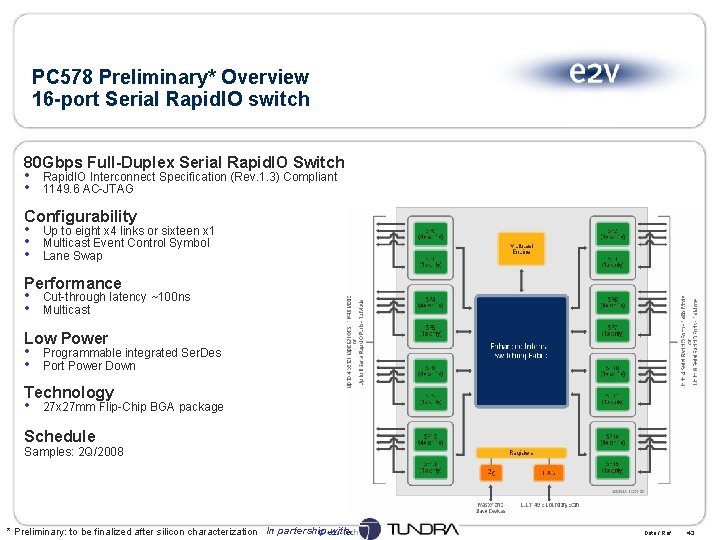

PC 578 Preliminary* Overview 16 -port Serial Rapid. IO switch 80 Gbps Full-Duplex Serial Rapid. IO Switch • Rapid. IO Interconnect Specification (Rev. 1. 3) Compliant • 1149. 6 AC-JTAG Configurability • Up to eight x 4 links or sixteen x 1 • Multicast Event Control Symbol • Lane Swap Performance • Cut-through latency ~100 ns • Multicast Low Power • Programmable integrated Ser. Des • Port Power Down Technology • 27 x 27 mm Flip-Chip BGA package Schedule Samples: 2 Q/2008 * Preliminary: to be finalized after silicon characterization In partership with Date / Ref 43

MRAM: High-Density, Fast, Non-Volatile RAM Date / Ref 44

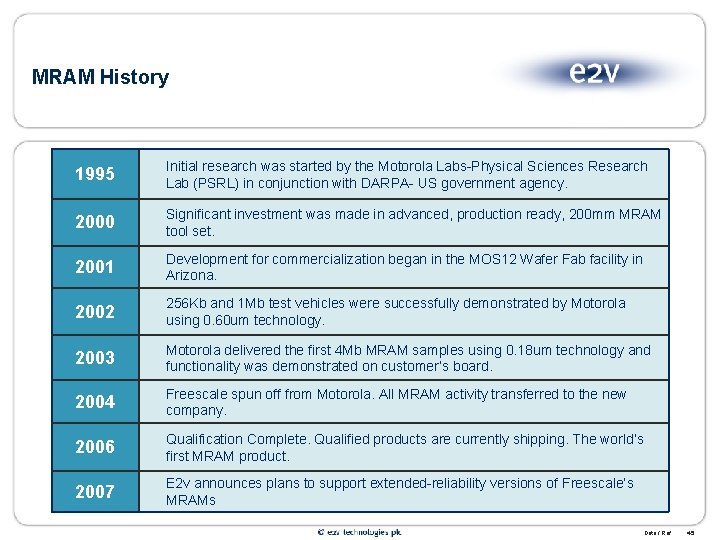

MRAM History 1995 Initial research was started by the Motorola Labs-Physical Sciences Research Lab (PSRL) in conjunction with DARPA- US government agency. 2000 Significant investment was made in advanced, production ready, 200 mm MRAM tool set. 2001 Development for commercialization began in the MOS 12 Wafer Fab facility in Arizona. 2002 256 Kb and 1 Mb test vehicles were successfully demonstrated by Motorola using 0. 60 um technology. 2003 Motorola delivered the first 4 Mb MRAM samples using 0. 18 um technology and functionality was demonstrated on customer’s board. 2004 Freescale spun off from Motorola. All MRAM activity transferred to the new company. 2006 Qualification Complete. Qualified products are currently shipping. The world’s first MRAM product. 2007 E 2 v announces plans to support extended-reliability versions of Freescale’s MRAMs Date / Ref 45

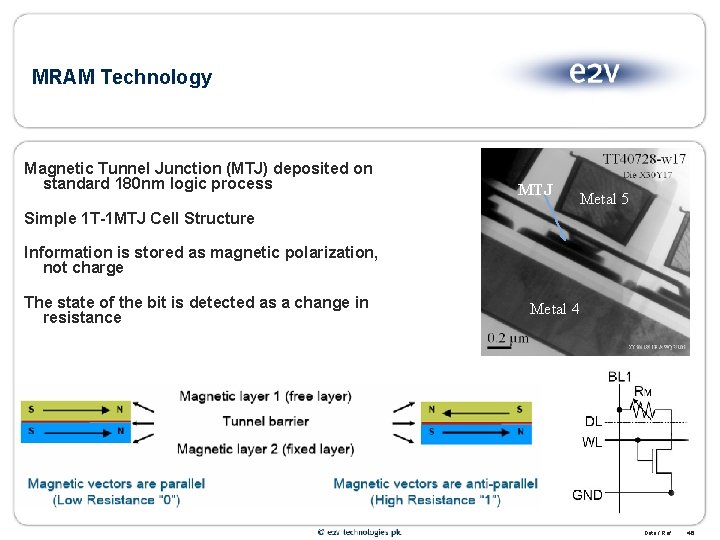

MRAM Technology Magnetic Tunnel Junction (MTJ) deposited on standard 180 nm logic process MTJ Metal 5 Simple 1 T-1 MTJ Cell Structure Information is stored as magnetic polarization, not charge The state of the bit is detected as a change in resistance Metal 4 Date / Ref 46

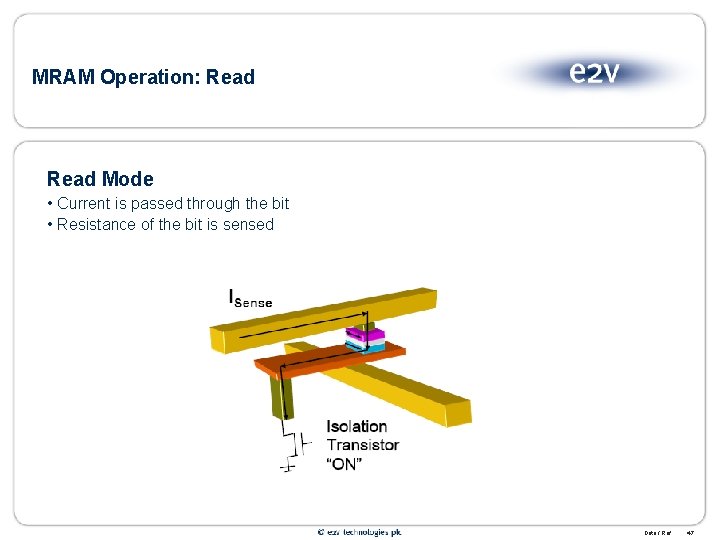

MRAM Operation: Read Mode • Current is passed through the bit • Resistance of the bit is sensed Date / Ref 47

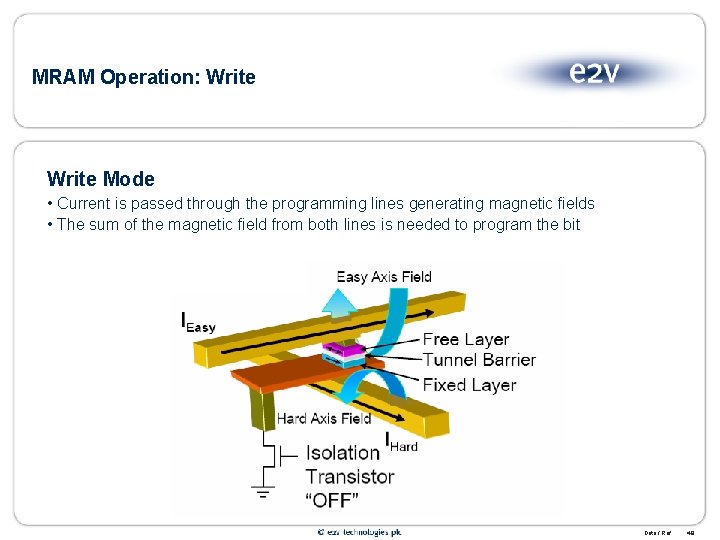

MRAM Operation: Write Mode • Current is passed through the programming lines generating magnetic fields • The sum of the magnetic field from both lines is needed to program the bit Date / Ref 48

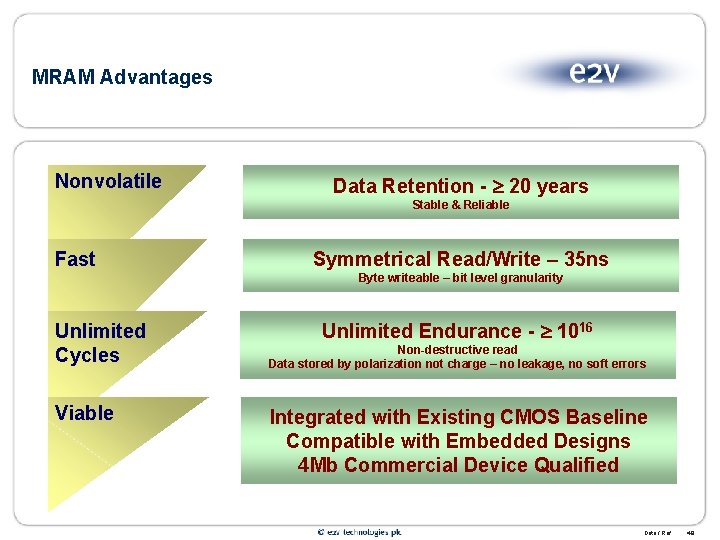

MRAM Advantages Nonvolatile Data Retention - 20 years Stable & Reliable Fast Symmetrical Read/Write – 35 ns Byte writeable – bit level granularity Unlimited Cycles Viable Unlimited Endurance - 1016 Non-destructive read Data stored by polarization not charge – no leakage, no soft errors Integrated with Existing CMOS Baseline Compatible with Embedded Designs 4 Mb Commercial Device Qualified Date / Ref 49

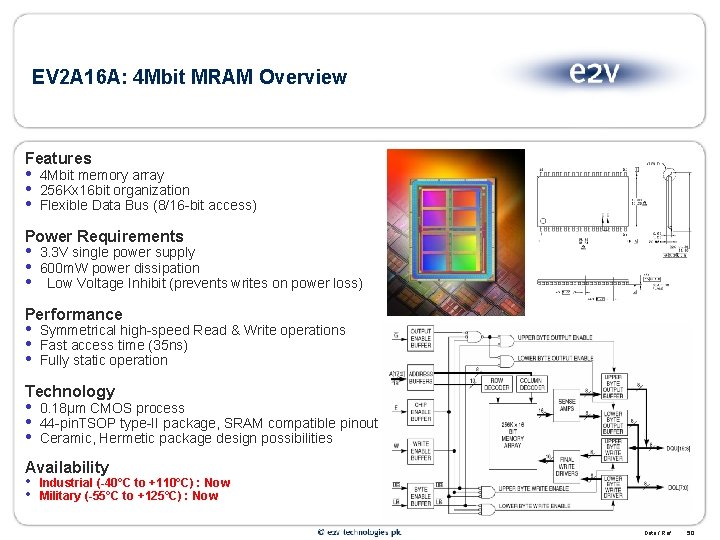

EV 2 A 16 A: 4 Mbit MRAM Overview Features • • • 4 Mbit memory array 256 Kx 16 bit organization Flexible Data Bus (8/16 -bit access) Power Requirements • • • 3. 3 V single power supply 600 m. W power dissipation Low Voltage Inhibit (prevents writes on power loss) Performance • • • Symmetrical high-speed Read & Write operations Fast access time (35 ns) Fully static operation Technology • • • 0. 18µm CMOS process 44 -pin. TSOP type-II package, SRAM compatible pinout Ceramic, Hermetic package design possibilities Availability • Industrial (-40°C to +110°C) : Now • Military (-55°C to +125°C) : Now Date / Ref 50

3 Reasons to Choose e 2 v’s Hi-Rel Microprocessors • e 2 v’s Product Offering – Extensive high performance product portfolio and roadmaps Ø Thanks to our agreements with Freescale Semiconductor and Tundra – All parts are certified by 100% electrical testing using original test vectors to ensure the highest level of fault coverage. • e 2 v’s Focus on Extended-Reliability Market – Unique Assembly & Test facility for Hi-Rel products. – For 25 years, our business has been to support this market segment. – We continue to have the flexibility to support specific customer needs • Our Commitment to the “Long- term” – We make products that are available for 20+ years Ø“First” life is 7 to 10 years of active foundry Øe 2 v adds another 5 to 10 years of “second” life thanks to our obsolescence management process Date / Ref 51

www. e 2 v. com Date / Ref 52

- Slides: 52