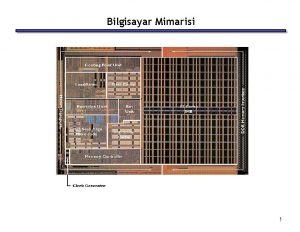

BLGM 325 Bilgisayar Mimarisi ve Organizasyonu Bilgisayar Mhendislii

BLGM 325 Bilgisayar Mimarisi ve Organizasyonu Bilgisayar Mühendisliği Bölümü Doğu Akdeniz Üniversitesi Çarpma & Bölme Algoritmaları

İkilik Tabanda Çarpma ¡ Her adımda çarpan ile çarpılan sayılar çarpılır. l İkilik tabanda, 1 veya 0 ile çarpma yaparız. 2

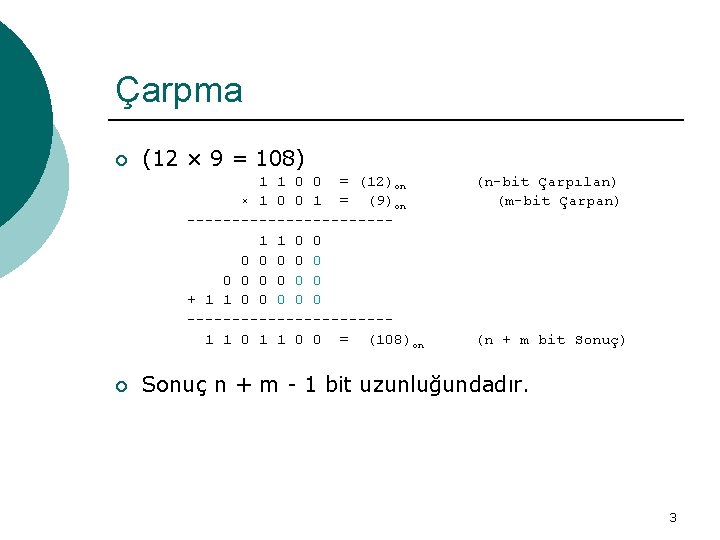

Çarpma ¡ (12 × 9 = 108) 1 1 0 0 = (12)on × 1 0 0 1 = (9)on -----------1 1 0 0 0 0 + 1 1 0 0 0 -----------1 1 0 0 = (108)on ¡ (n-bit Çarpılan) (m-bit Çarpan) (n + m bit Sonuç) Sonuç n + m - 1 bit uzunluğundadır. 3

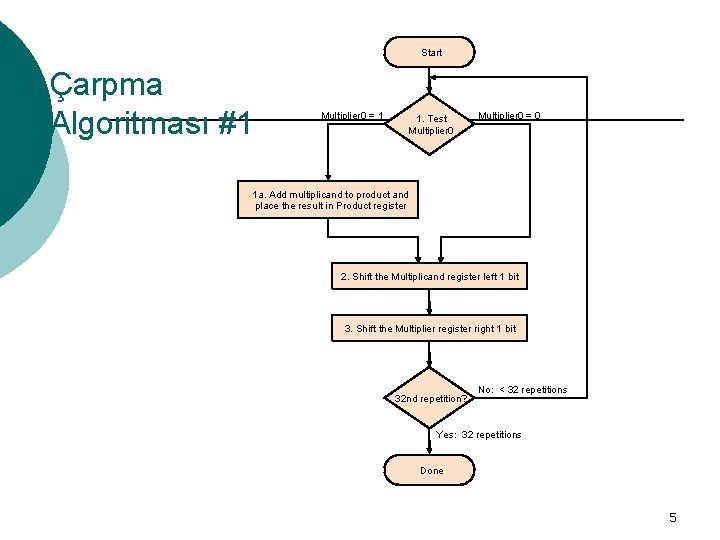

Çarpma Algoritması #1 ¡ İşaretsiz çarpma (12 × 9 = 108) 1 1 0 0 = (12)on × 1 0 0 1 = (9)on -----------1 1 0 0 0 0 + 1 1 0 0 0 -----------1 1 0 0 = (108)on (n-bit Çarpılan) (m-bit Çarpan) 4

Start Çarpma Algoritması #1 Multiplier 0 = 1 1. Test Multiplier 0 = 0 1 a. Add multiplicand to product and place the result in Product register 2. Shift the Multiplicand register left 1 bit 3. Shift the Multiplier register right 1 bit 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done 5

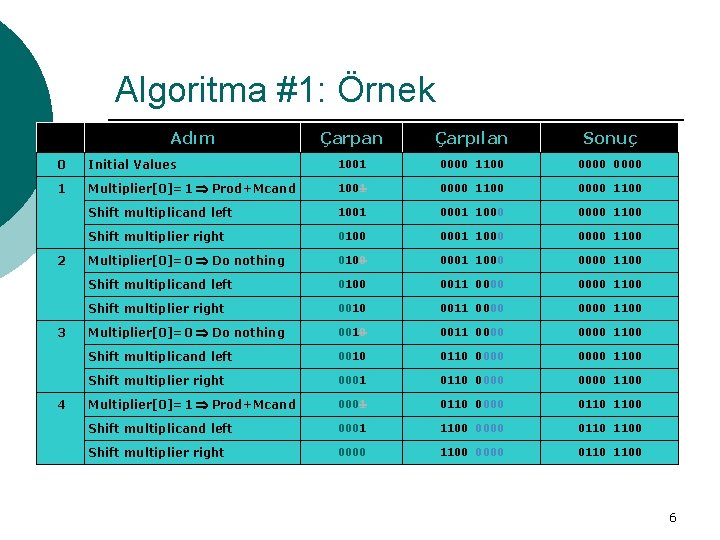

Algoritma #1: Örnek Adım Çarpan Çarpılan Sonuç 0 Initial Values 1001 0000 1100 0000 1 Multiplier[0]=1 Prod+Mcand 1001 0000 1100 Shift multiplicand left 1001 0001 1000 0000 1100 Shift multiplier right 0100 0001 1000 0000 1100 Multiplier[0]=0 Do nothing 0100 0001 1000 0000 1100 Shift multiplicand left 0100 0011 0000 1100 Shift multiplier right 0010 0011 0000 1100 Multiplier[0]=0 Do nothing 0010 0011 0000 1100 Shift multiplicand left 0010 0110 0000 1100 Shift multiplier right 0001 0110 0000 1100 Multiplier[0]=1 Prod+Mcand 0001 0110 0000 0110 1100 Shift multiplicand left 0001 1100 0000 0110 1100 Shift multiplier right 0000 1100 0000 0110 1100 2 3 4 6

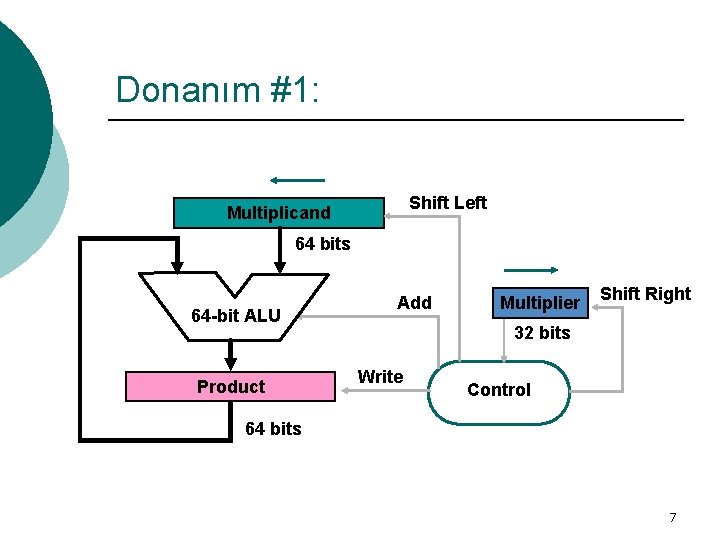

Donanım #1: Shift Left Multiplicand 64 bits 64 -bit ALU Product Add Multiplier Shift Right 32 bits Write Control 64 bits 7

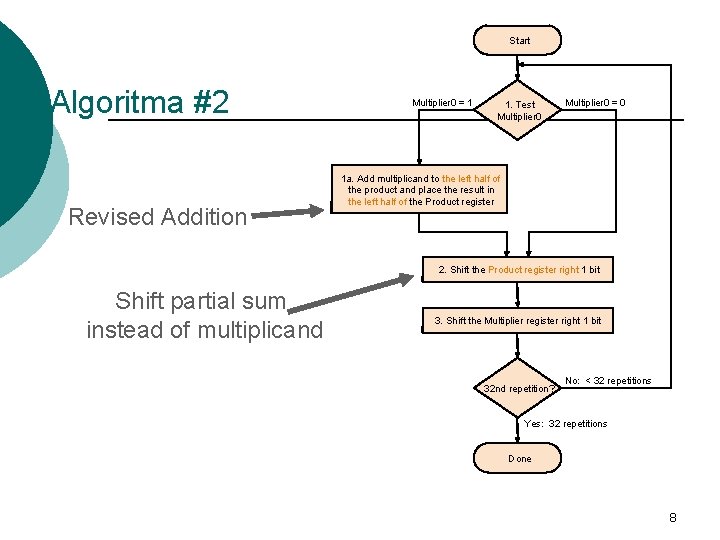

Start Algoritma #2 Revised Addition Multiplier 0 = 1 1. Test Multiplier 0 = 0 1 a. Add multiplicand to the left half of the product and place the result in the left half of the Product register 2. Shift the Product register right 1 bit Shift partial sum instead of multiplicand 3. Shift the Multiplier register right 1 bit 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done 8

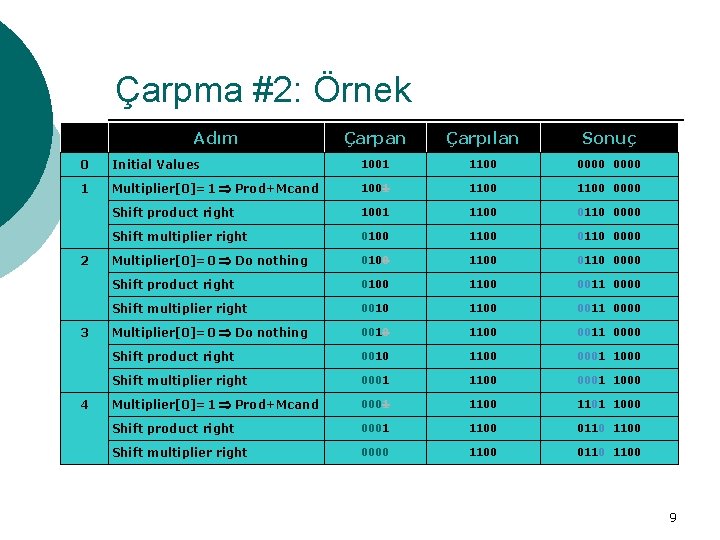

Çarpma #2: Örnek Adım Çarpan Çarpılan Sonuç 0 Initial Values 1001 1100 0000 1 Multiplier[0]=1 Prod+Mcand 1001 1100 0000 Shift product right 1001 1100 0110 0000 Shift multiplier right 0100 1100 0110 0000 Multiplier[0]=0 Do nothing 0100 1100 0110 0000 Shift product right 0100 1100 0011 0000 Shift multiplier right 0010 1100 0011 0000 Multiplier[0]=0 Do nothing 0010 1100 0011 0000 Shift product right 0010 1100 0001 1000 Shift multiplier right 0001 1100 0001 1000 Multiplier[0]=1 Prod+Mcand 0001 1100 1101 1000 Shift product right 0001 1100 0110 1100 Shift multiplier right 0000 1100 0110 1100 2 3 4 9

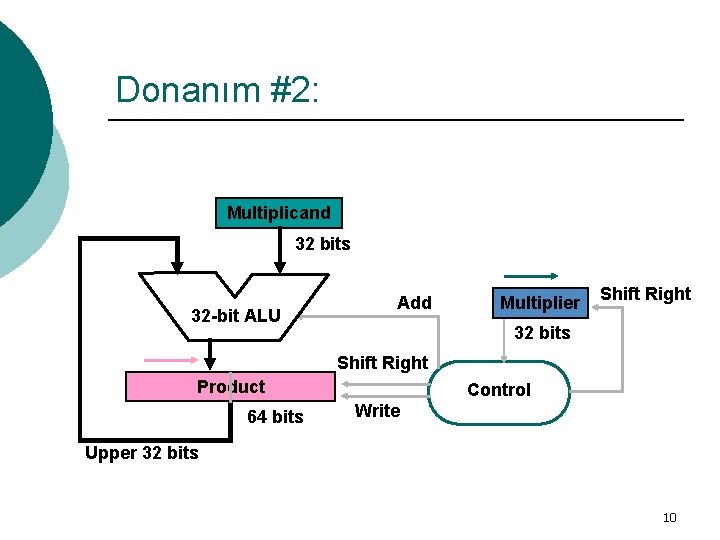

Donanım #2: Multiplicand 32 bits 32 -bit ALU Add Multiplier Shift Right 32 bits Shift Right Product 64 bits Control Write Upper 32 bits 10

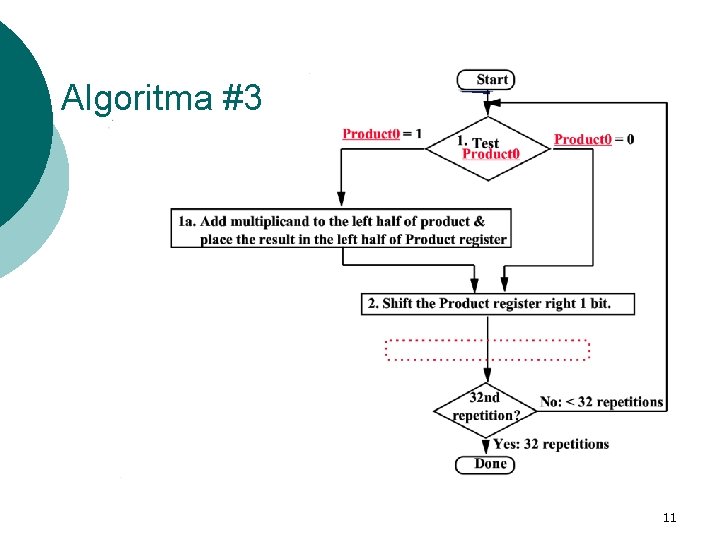

Algoritma #3 11

![Algoritma #3: Örnek Adım Çarpılan Sonuç 0 Initial Values 1100 0000 1001 1 Product[0]=1 Algoritma #3: Örnek Adım Çarpılan Sonuç 0 Initial Values 1100 0000 1001 1 Product[0]=1](http://slidetodoc.com/presentation_image/81e92183842dc1e2fa171d20ed83cfe4/image-12.jpg)

Algoritma #3: Örnek Adım Çarpılan Sonuç 0 Initial Values 1100 0000 1001 1 Product[0]=1 Prod+Mcand 1100 1001 Shift product right 1100 0110 0100 Product[0]=0 Do nothing 1100 0110 0100 Shift product right 1100 0011 0010 Product[0]=0 Do nothing 1100 0011 0010 Shift product right 1100 0001 1001 Product[0]=1 Prod+Mcand 1100 1101 1001 Shift product right 1100 0110 1100 2 3 4 12

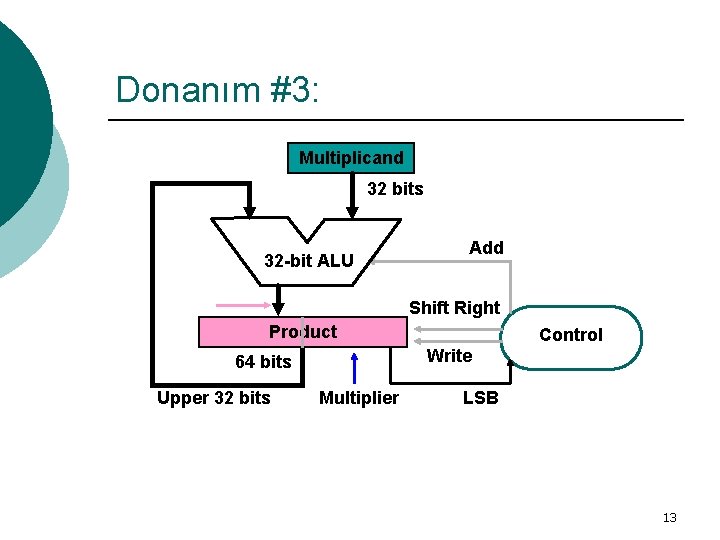

Donanım #3: Multiplicand 32 bits 32 -bit ALU Add Shift Right Product Write 64 bits Upper 32 bits Control Multiplier LSB 13

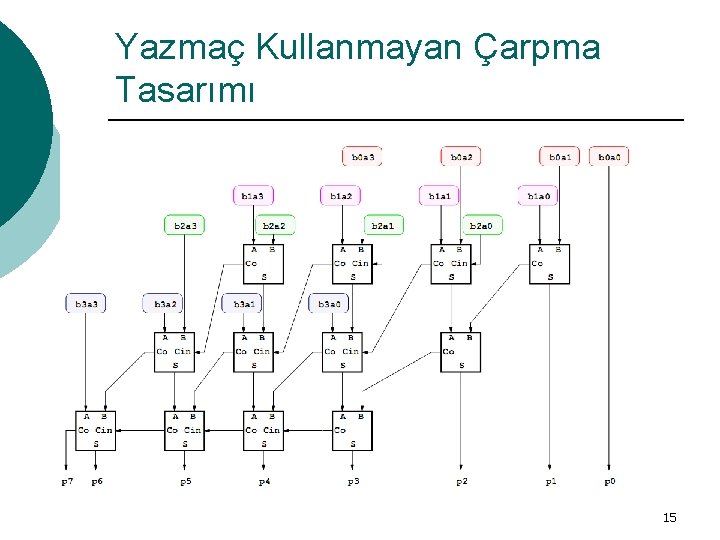

Yazmaç Kullanmayan Çarpma Tasarımı 14

Yazmaç Kullanmayan Çarpma Tasarımı 15

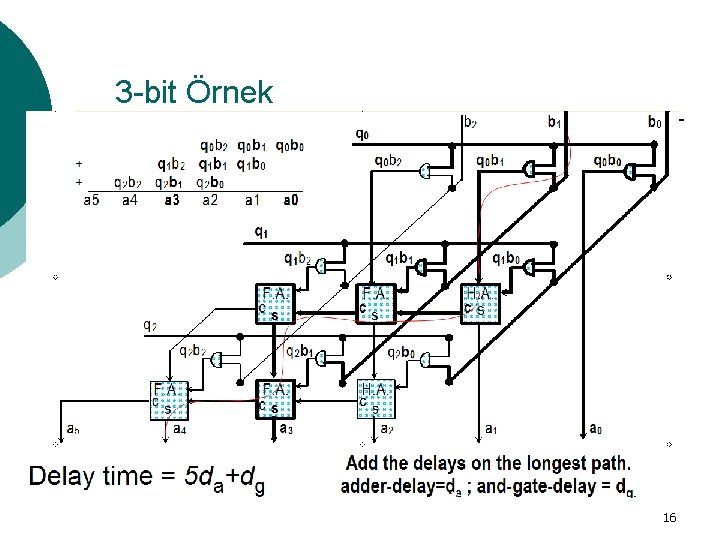

3 -bit Örnek 16

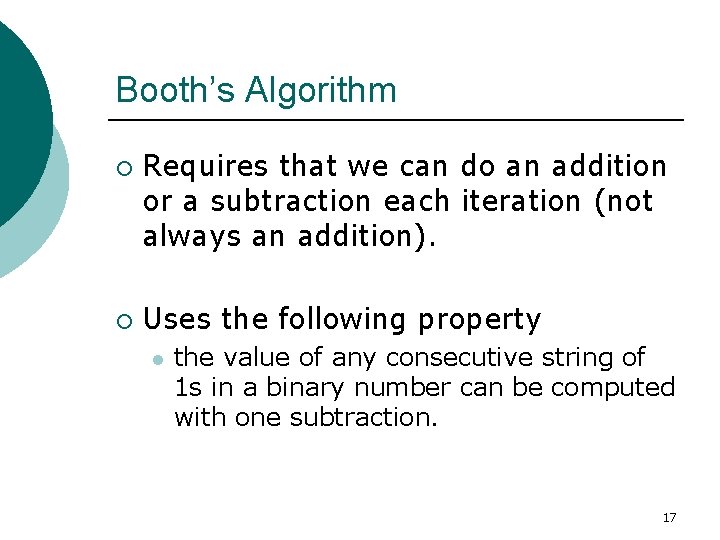

Booth’s Algorithm ¡ ¡ Requires that we can do an addition or a subtraction each iteration (not always an addition). Uses the following property l the value of any consecutive string of 1 s in a binary number can be computed with one subtraction. 17

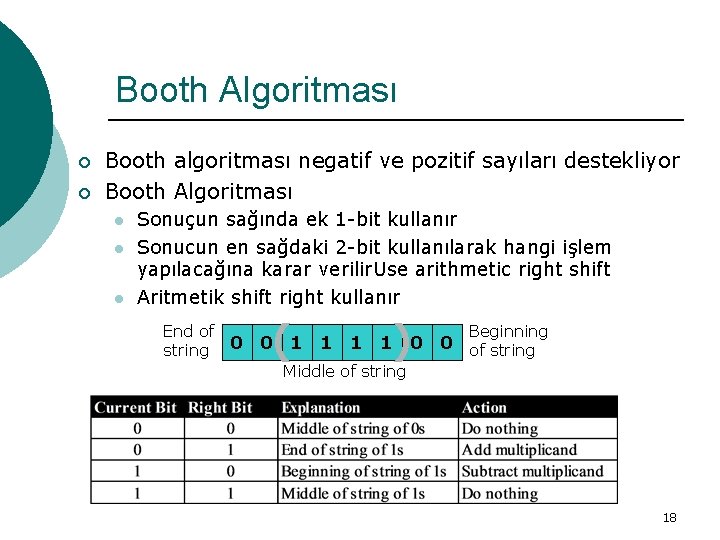

Booth Algoritması ¡ ¡ Booth algoritması negatif ve pozitif sayıları destekliyor Booth Algoritması l l l Sonuçun sağında ek 1 -bit kullanır Sonucun en sağdaki 2 -bit kullanılarak hangi işlem yapılacağına karar verilir. Use arithmetic right shift Aritmetik shift right kullanır End of string ( ) Beginning 0 0 1 1 0 0 of string Middle of string 18

Booth Algoritması ¡ Algoritmanın 2. adımı daha öncekiyle ayni: shift the product/multiplier right one bit. l l Arithmetic shift needed for signed arithmetic. The bit shifted off the right is saved and used by the next step 1 (which looks at 2 bits). 19

Booth Algoritması: Örnek ¡ (-4×-7=28) Iter Step Multiplicand Product 0 Initial Values 1100 0000 1001 0 1 Product=10 Prod-Mcand 1100 0100 1001 0 Shift product right 1100 0010 0100 1 Product=01 Prod+Mcand 1100 1110 0100 1 Shift product right 1100 1111 0010 0 Product=00 Do nothing 1100 1111 0010 0 Shift product right 1100 1111 1001 0 Product=10 Prod-Mcand 1100 0011 1001 0 Shift product right 1100 0001 1100 1 2 3 4 20

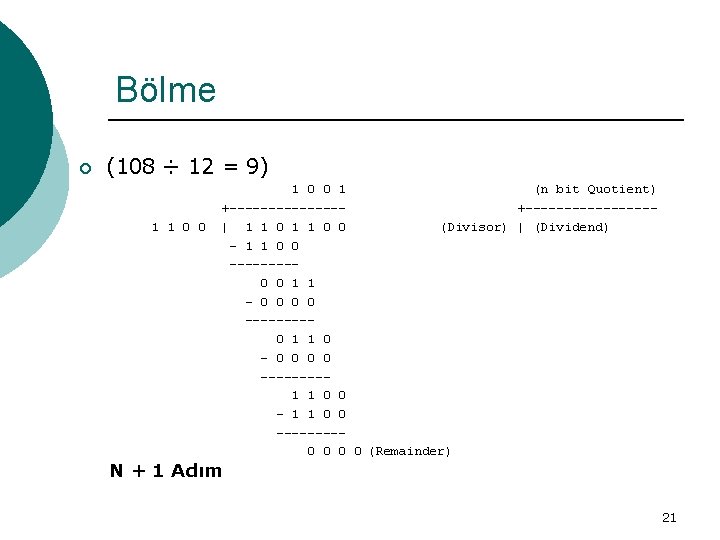

Bölme ¡ (108 ÷ 12 = 9) 1 1 0 0 1 (n bit Quotient) +----------------| 1 1 0 0 (Divisor) | (Dividend) - 1 1 0 0 ----0 0 1 1 - 0 0 ----0 1 1 0 - 0 0 ----1 1 0 0 ----0 0 (Remainder) N + 1 Adım 21

Aloritma #1 22

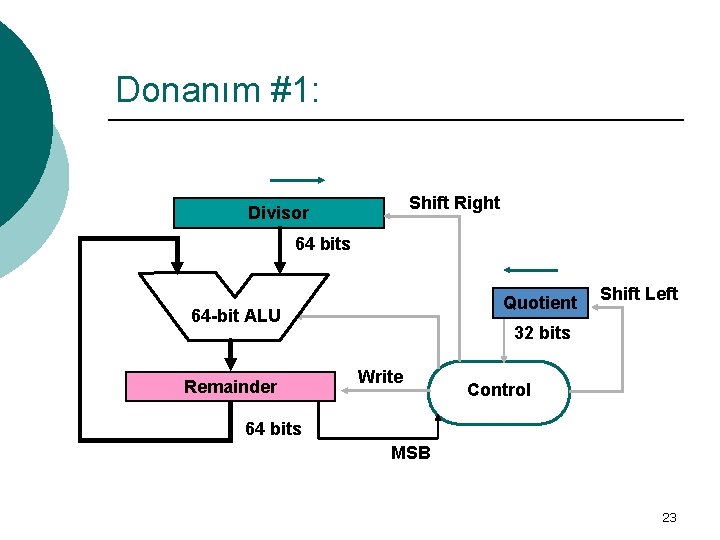

Donanım #1: Shift Right Divisor 64 bits Quotient 64 -bit ALU Remainder Shift Left 32 bits Write Control 64 bits MSB 23

0000 24

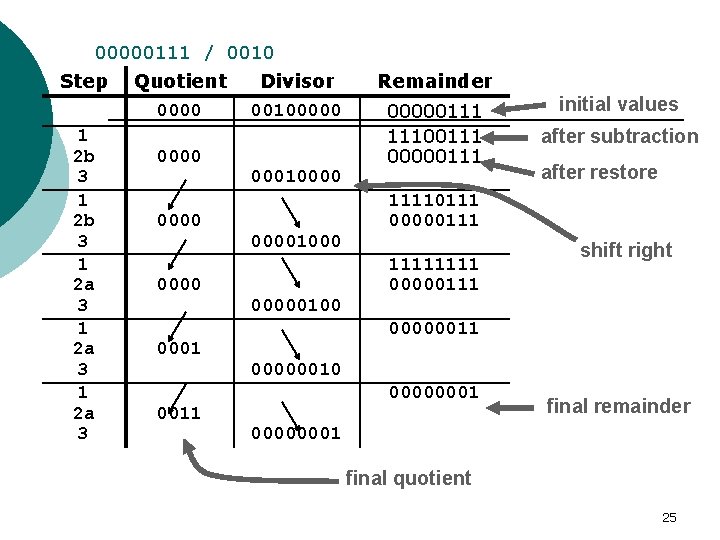

00000111 / 0010 Step 1 2 b 3 1 2 a 3 Quotient 0000 0001 0011 Divisor 00100000 000100001000 00000100 Remainder 00000111 11100111 00000111 initial values after subtraction after restore 11110111 00000111 1111 00000111 shift right 00000011 00000010 00000001 final remainder 00000001 final quotient 25

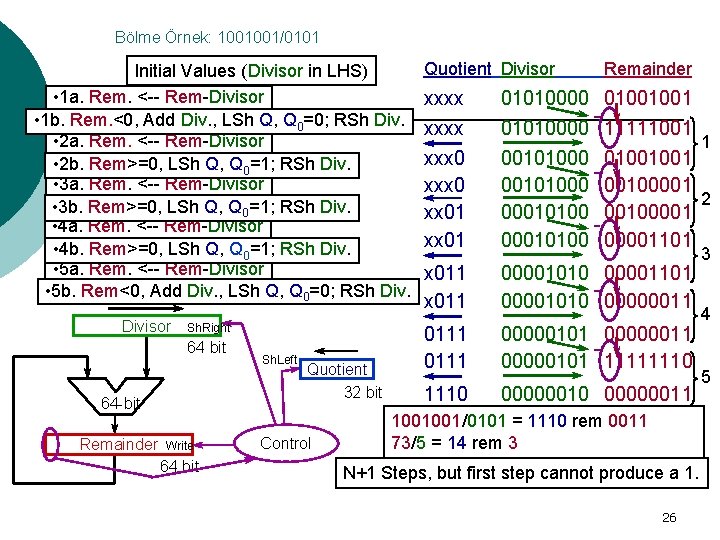

Bölme Örnek: 1001001/0101 Initial Values (Divisor in LHS) • 1 a. Rem. <-- Rem-Divisor • 1 b. Rem. <0, Add Div. , LSh Q, Q 0=0; RSh Div. • 2 a. Rem. <-- Rem-Divisor • 2 b. Rem>=0, LSh Q, Q 0=1; RSh Div. • 3 a. Rem. <-- Rem-Divisor • 3 b. Rem>=0, LSh Q, Q 0=1; RSh Div. • 4 a. Rem. <-- Rem-Divisor • 4 b. Rem>=0, LSh Q, Q 0=1; RSh Div. • 5 a. Rem. <-- Rem-Divisor • 5 b. Rem<0, Add Div. , LSh Q, Q 0=0; RSh Divisor Sh. Right 64 bit 64 -bit Remainder Write 64 bit Sh. Left Quotient 32 bit Control Quotient Divisor Remainder xxxx 01010000 01001001 01010000 11111001 xxx 01 00101000 01001001 00101000 00100001 2 00010100 001000010100 00001101 x 011 00001010 00001101 00001010 00000011 0111 00000101 00000011 00000101 11111110 00000010 00000011 1001001/0101 = 1110 rem 0011 73/5 = 14 rem 3 N+1 Steps, but first step cannot produce a 1. 26 1 3 4 5

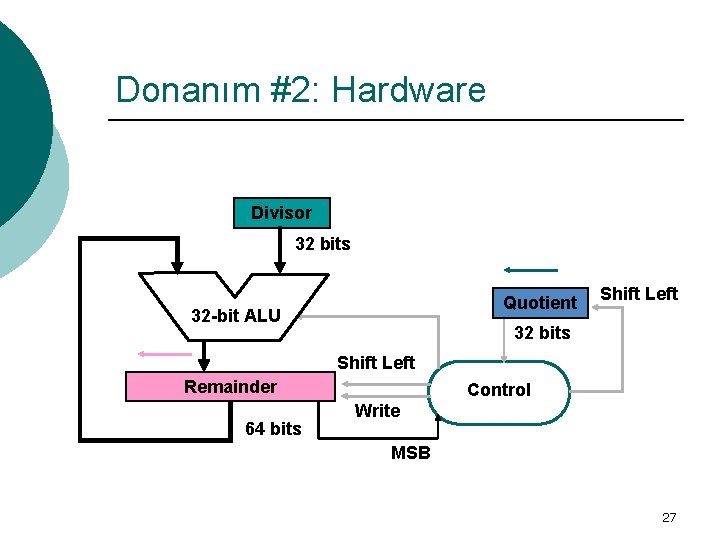

Donanım #2: Hardware Divisor 32 bits Quotient 32 -bit ALU Shift Left 32 bits Shift Left Remainder 64 bits Control Write MSB 27

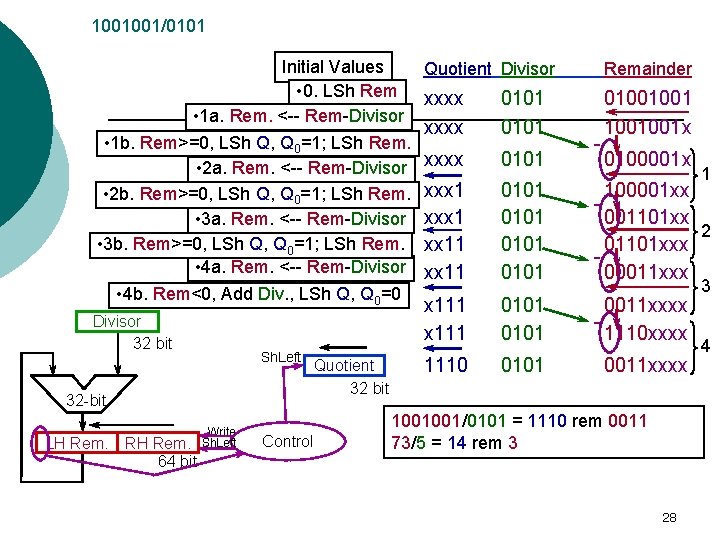

1001001/0101 Initial Values • 0. LSh Rem • 1 a. Rem. <-- Rem-Divisor • 1 b. Rem>=0, LSh Q, Q 0=1; LSh Rem. • 2 a. Rem. <-- Rem-Divisor • 2 b. Rem>=0, LSh Q, Q 0=1; LSh Rem. • 3 a. Rem. <-- Rem-Divisor • 3 b. Rem>=0, LSh Q, Q 0=1; LSh Rem. • 4 a. Rem. <-- Rem-Divisor • 4 b. Rem<0, Add Div. , LSh Q, Q 0=0 Divisor 32 bit Sh. Left 32 -bit LH Rem. RH Rem. 64 bit Write Sh. Left Control Quotient 32 bit Quotient Divisor Remainder xxxx 0101 01001001 x xxxx 0101 xxx 11 0101 x 111 0101 0011 xxxx 1110 0101 0011 xxxx - 0100001 x 1 100001 xx 001101 xx 2 01101 xxx 00011 xxx - 1001001/0101 = 1110 rem 0011 73/5 = 14 rem 3 28 3 4

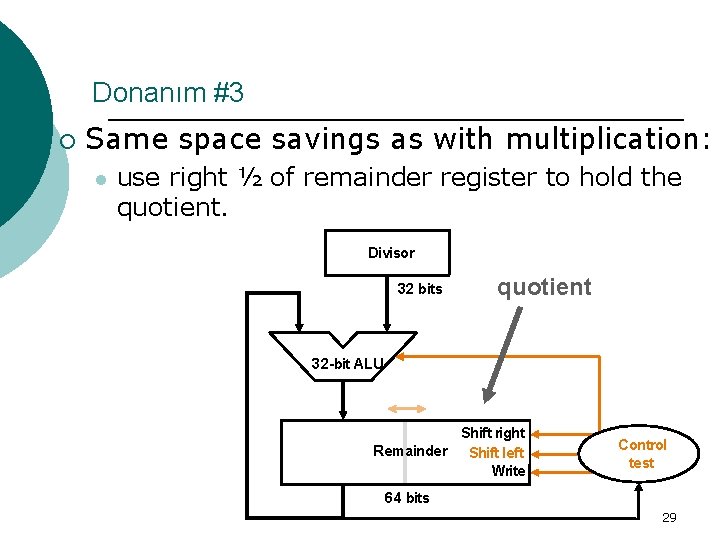

Donanım #3 ¡ Same space savings as with multiplication: l use right ½ of remainder register to hold the quotient. Divisor 32 bits quotient 32 -bit ALU Shift right Remainder Shift left Write Control test 64 bits 29

Start Algoritma #3 1. Shift the Remainder register left 1 bit rem <<= 1 rem -= (div >> 32) if rem < 0 then 2. Subtract the Divisor register from the left half of the Remainder register and place the result in the left half of the Remainder register rem += (div >> 32) rem <<= 1 Remainder > – 0 Test Remainder < 0 LSB(rem) = 0 else rem <<= 1 3 a. Shift the Remainder register to the left, setting the new rightmost bit to 1 3 b. Restore the original value by adding the Divisor register to the left half of the Remainder register and place the sum in the left half of the Remainder register. Also shift the Remainder register to the left, setting the new rightmost bit to 0 LSB(rem) = 1 fi repeat unless done Correct remainder 32 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done. Shift left half of Remainder right 1 bit 30

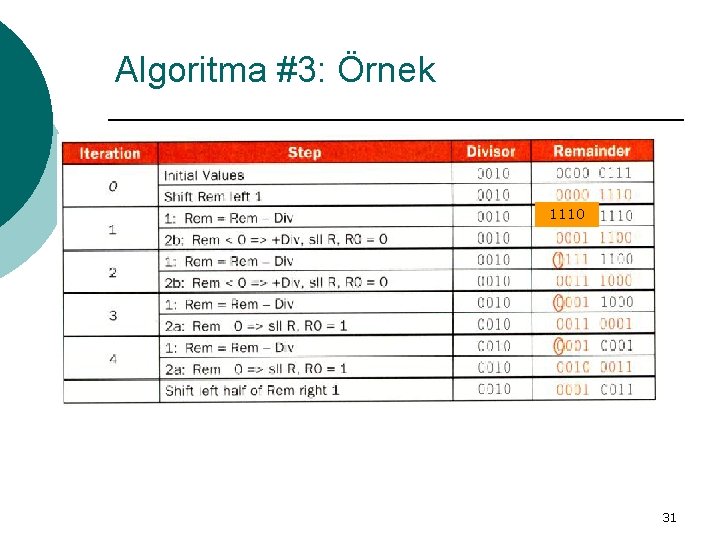

Algoritma #3: Örnek 1110 31

1001001/0101 Initial Values • 0. LSh Rem-Quo. • 1 a. Rem <-- Rem-Divisor • 1 b. Rem>=0, LSh Rem-Quo, Q 0=1 • 2 a. Rem. <-- Rem-Divisor • 2 b. Rem>=0, LSh Rem-Quo, Q 0=1 • 3 a. Rem. <-- Rem-Divisor • 3 b. Rem>=0, LSh Rem-Quo, Q 0=1 • 4 a. Rem. <-- Rem-Divisor • 4 b. Rem<0, Add Div. , LSh Rem-Quo, Q 0=0 Divisor 32 bit • Final: RSh Rem 1 32 -bit LH Rem-Quot. 64 bit Write Sh. Left Control Divisor Remainder-Quotient 0101 010010010 0101 0101 - 01000010 1 10000101 00110101 2 01101011 00011011 - 0101 00110111 11100111 0101 01101110 00111110 3 4 1001001/0101 = 1110 rem 0011 73/5 = 14 rem 3 32

- Slides: 32