Blackfin BF 533 EZKIT Control The O in

Blackfin BF 533 EZ-KIT Control The O in I/O Activating a FLASH memory “output line” Part 3 – New instruction recap Tutorial

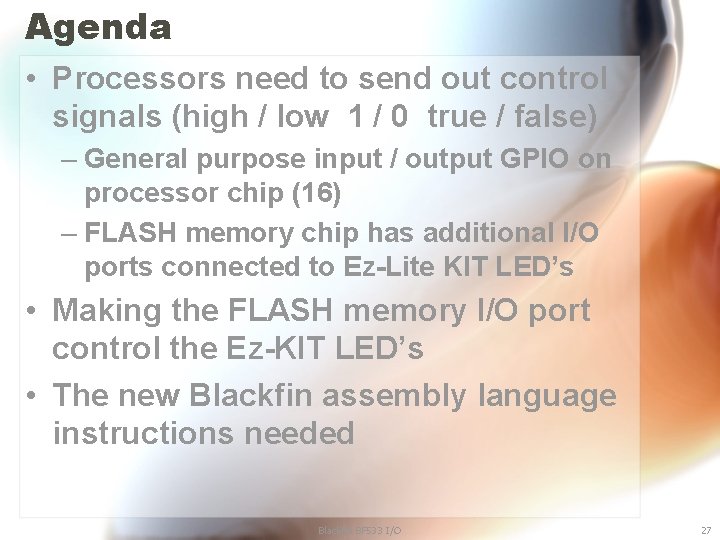

Agenda • Processors need to send out control signals (high / low 1 / 0 true / false) – General purpose input / output GPIO on processor chip (16) – FLASH memory chip has additional I/O ports connected to Ez-Lite KIT LED’s • Making the FLASH memory I/O port control the Ez-KIT LED’s • The new Blackfin assembly language instructions needed Blackfin BF 533 I/O 2

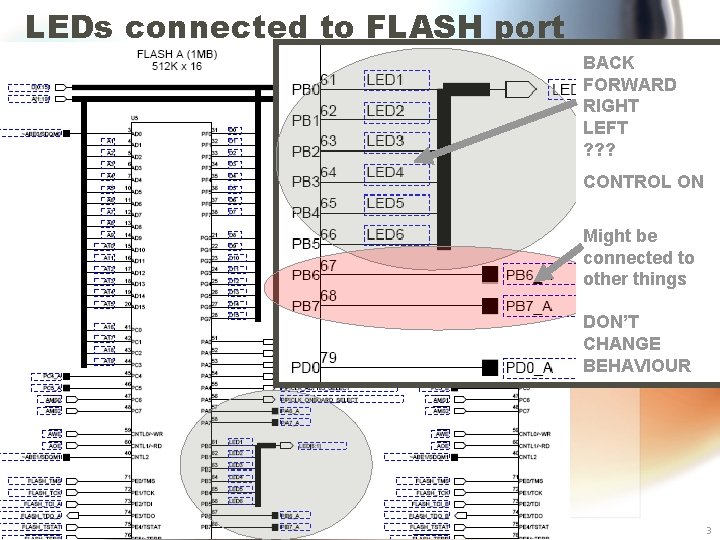

LEDs connected to FLASH port BACK FORWARD RIGHT LEFT ? ? ? CONTROL ON Might be connected to other things DON’T CHANGE BEHAVIOUR Blackfin BF 533 I/O 3

Activating LEDs -- REVIEW • Get the FLASH to work correctly – Init. Flash. ASM( ) • Get the Port to work correctly as output for pins PB 5 PB 0, leaving other pins unchanged – Init. Flash. Port. ASM( ) • Write the value we want to LEDs – Write. Flash. LEDASM( int value) • Read back the value the LEDs show – int Read. Flash. LEDASM( ) Blackfin BF 533 I/O 4

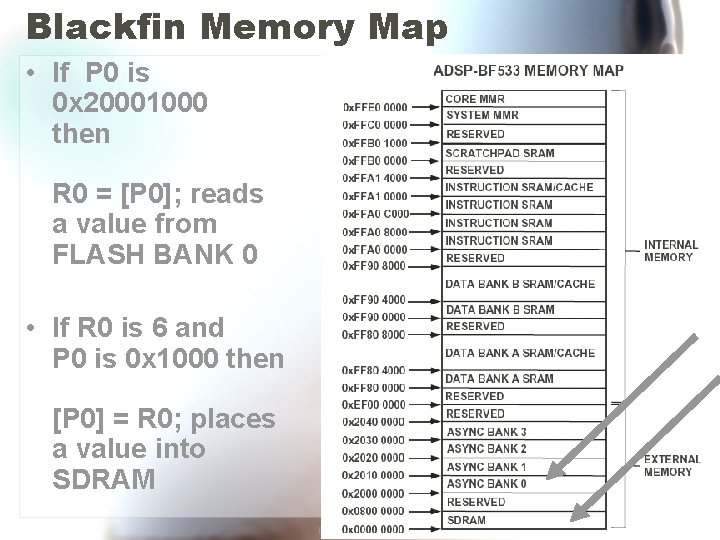

Blackfin Memory Map • If P 0 is 0 x 20001000 then R 0 = [P 0]; reads a value from FLASH BANK 0 • If R 0 is 6 and P 0 is 0 x 1000 then [P 0] = R 0; places a value into SDRAM Blackfin BF 533 I/O 5

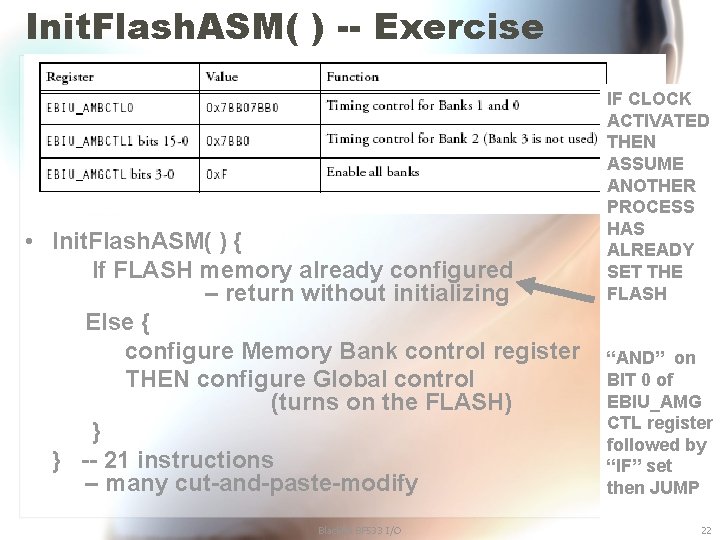

Init. Flash. ASM( ) -- REVIEW • Get the FLASH to work correctly • May be “many” processes running on the Blackfin. All these processes may want to use Init. Flash. ASM( ) • Init. Flash. ASM( ) { If FLASH memory already configured – return without initializing Else { configure Memory Bank control register THEN configure Global control (turns on the FLASH) } } Blackfin BF 533 I/O 6

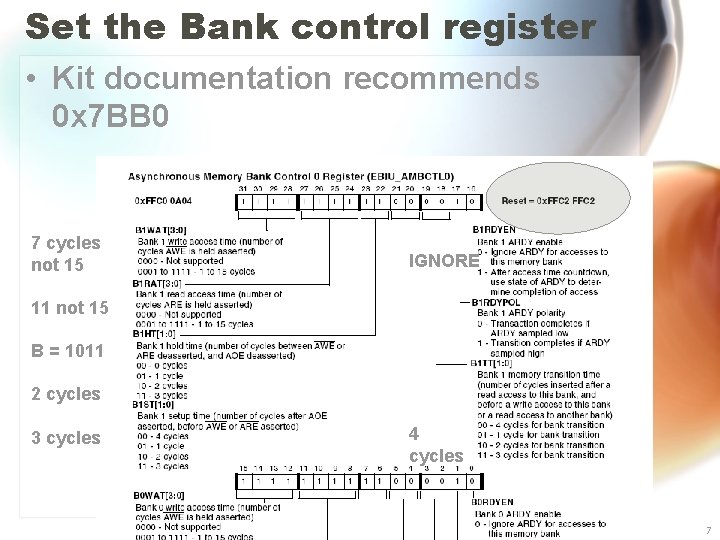

Set the Bank control register • Kit documentation recommends 0 x 7 BB 0 7 cycles not 15 IGNORE 11 not 15 B = 1011 2 cycles 4 cycles 3 cycles Blackfin BF 533 I/O 7

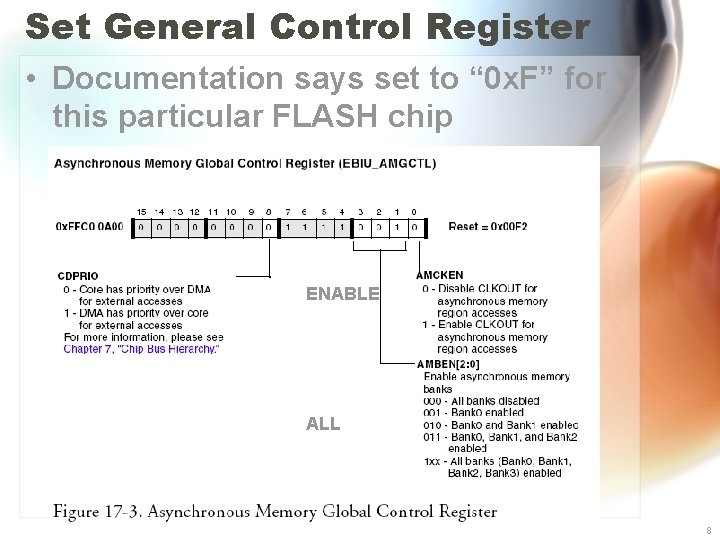

Set General Control Register • Documentation says set to “ 0 x. F” for this particular FLASH chip ENABLE ALL Blackfin BF 533 I/O 8

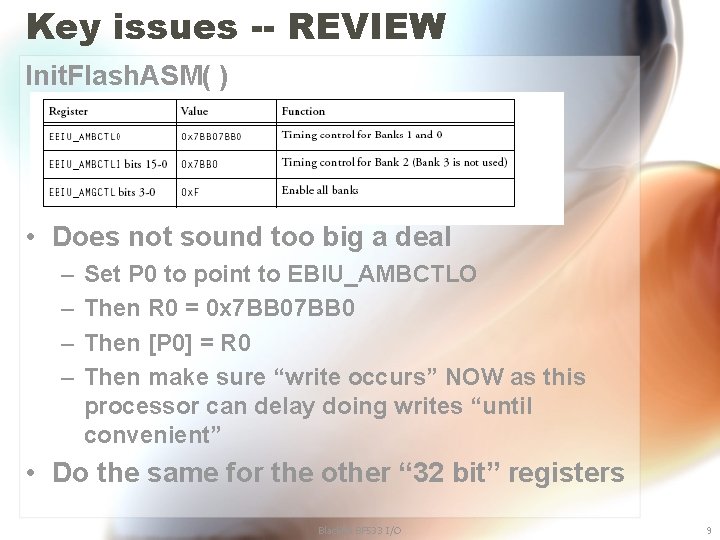

Key issues -- REVIEW Init. Flash. ASM( ) • Does not sound too big a deal – – Set P 0 to point to EBIU_AMBCTLO Then R 0 = 0 x 7 BB 0 Then [P 0] = R 0 Then make sure “write occurs” NOW as this processor can delay doing writes “until convenient” • Do the same for the other “ 32 bit” registers Blackfin BF 533 I/O 9

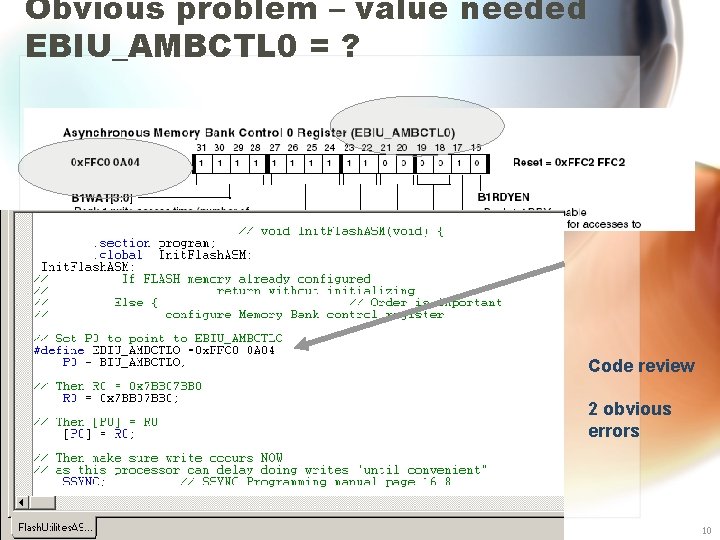

Obvious problem – value needed EBIU_AMBCTL 0 = ? Code review 2 obvious errors Blackfin BF 533 I/O 10

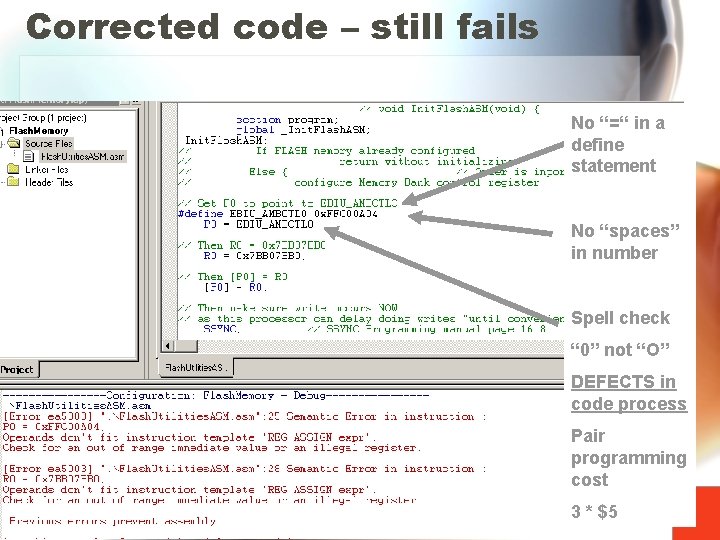

Corrected code – still fails No “=“ in a define statement No “spaces” in number Spell check “ 0” not “O” DEFECTS in code process Pair programming cost 3 * $5 Blackfin BF 533 I/O 11

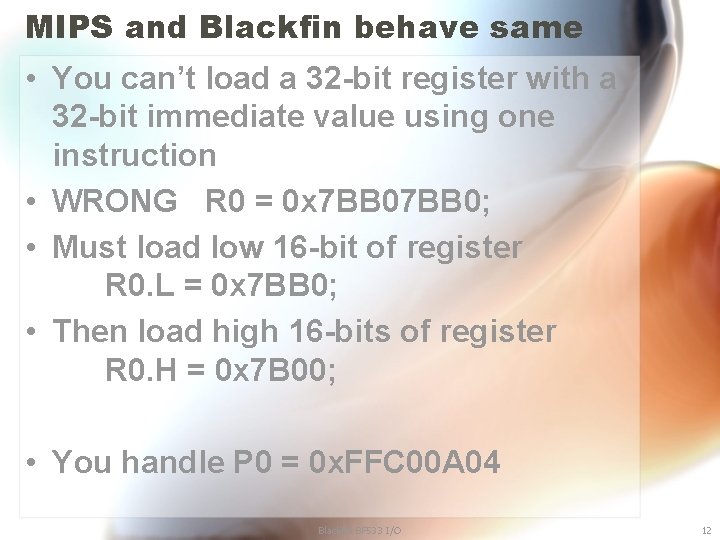

MIPS and Blackfin behave same • You can’t load a 32 -bit register with a 32 -bit immediate value using one instruction • WRONG R 0 = 0 x 7 BB 0; • Must load low 16 -bit of register R 0. L = 0 x 7 BB 0; • Then load high 16 -bits of register R 0. H = 0 x 7 B 00; • You handle P 0 = 0 x. FFC 00 A 04 Blackfin BF 533 I/O 12

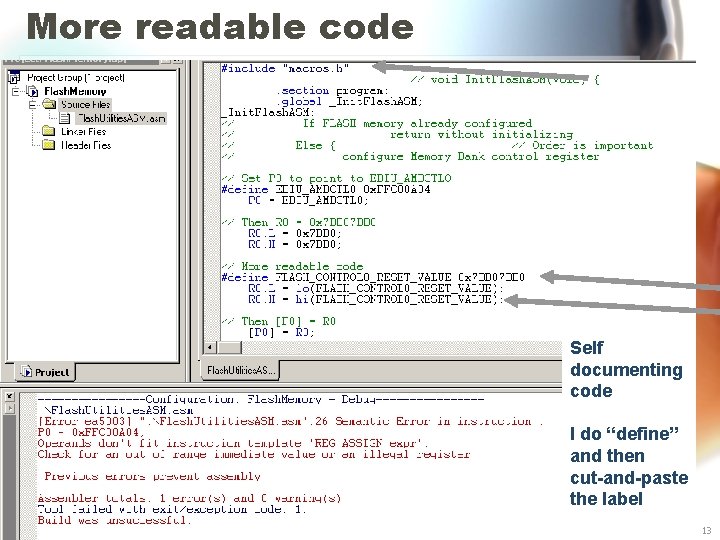

More readable code Self documenting code I do “define” and then cut-and-paste the label Blackfin BF 533 I/O 13

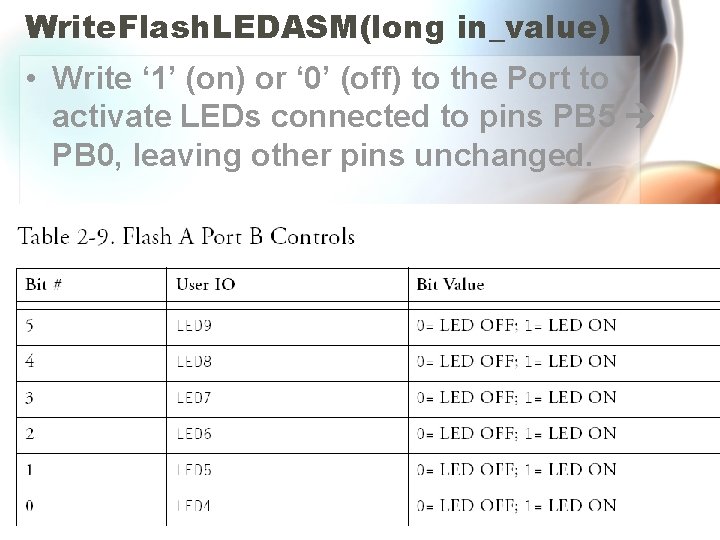

Write. Flash. LEDASM(long in_value) • Write ‘ 1’ (on) or ‘ 0’ (off) to the Port to activate LEDs connected to pins PB 5 PB 0, leaving other pins unchanged. Blackfin BF 533 I/O 14

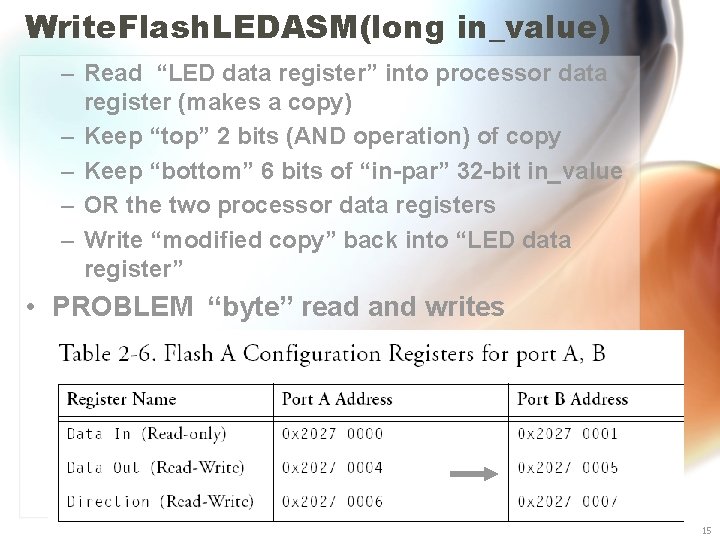

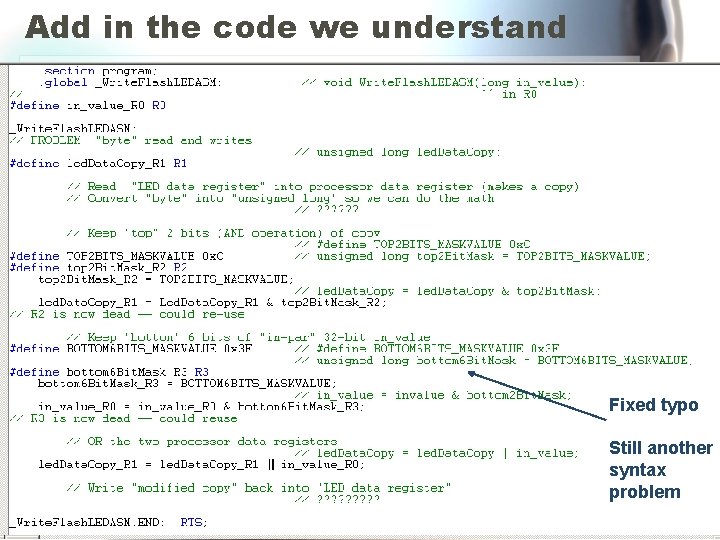

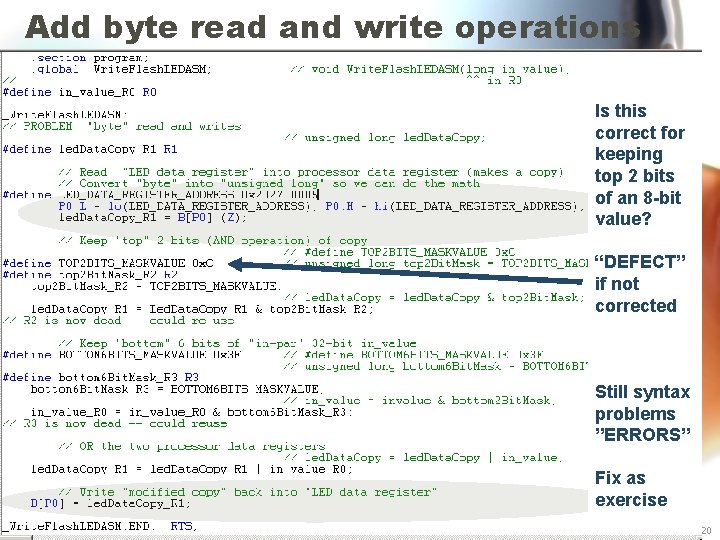

Write. Flash. LEDASM(long in_value) – Read “LED data register” into processor data register (makes a copy) – Keep “top” 2 bits (AND operation) of copy – Keep “bottom” 6 bits of “in-par” 32 -bit in_value – OR the two processor data registers – Write “modified copy” back into “LED data register” • PROBLEM “byte” read and writes Blackfin BF 533 I/O 15

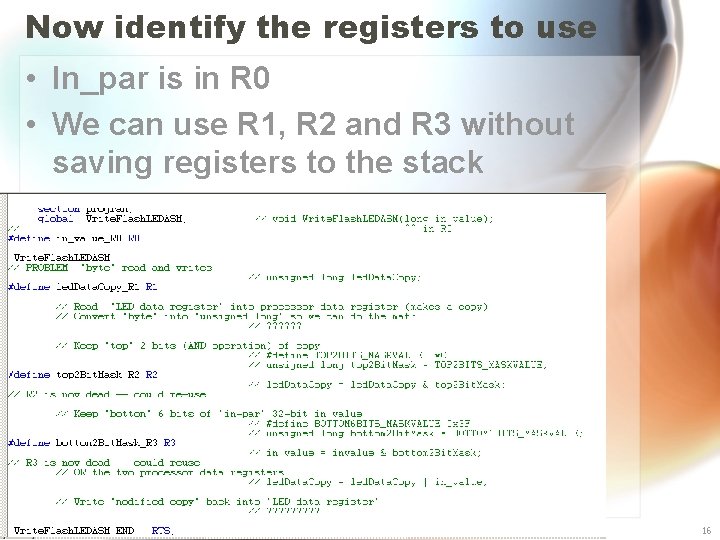

Now identify the registers to use • In_par is in R 0 • We can use R 1, R 2 and R 3 without saving registers to the stack Blackfin BF 533 I/O 16

Add in the code we understand Fixed typo Still another syntax problem Blackfin BF 533 I/O 17

![8 bit and 32 bit writes • [P 0] = R 0; 32 -bit 8 bit and 32 bit writes • [P 0] = R 0; 32 -bit](http://slidetodoc.com/presentation_image_h2/bee76a6521eb7d4e78d19781f4051ffe/image-18.jpg)

8 bit and 32 bit writes • [P 0] = R 0; 32 -bit write (4 bytes) – Places all 32 -bits of processor data register into “long word” (32 bit) address starting at memory location P 0 – If P 0 = 0 x 1000 – then place “ 32 -bit” value at memory location 0 x 1000 • B[P 0] = R 0; 8 -bit write – Places “bottom” 8 -bits of processor data register into “byte” (8 bit) address starting at memory location P 0 Blackfin BF 533 I/O 18

![8 bit and 32 bit reads • R 0 = [P 0]; 32 -bit 8 bit and 32 bit reads • R 0 = [P 0]; 32 -bit](http://slidetodoc.com/presentation_image_h2/bee76a6521eb7d4e78d19781f4051ffe/image-19.jpg)

8 bit and 32 bit reads • R 0 = [P 0]; 32 -bit read (4 bytes) – Places all 32 -bits of “long word” (32 bit) address starting at memory location P 0 into processor data register – If P 0 = 0 x 1000 – then place “ 32 -bit” value at memory location 0 x 1000 • R 0 = B[P 0] (Z); 8 -bit read – Places “byte” (8 bit) address starting at memory location P 0 into “bottom” 8 -bits of processor data register and puts “ 0” into the “top” 24 bits of register – Must convert “ 8 -bit” read operation into a “ 32” bit “store in register” operation Blackfin BF 533 I/O 19

Add byte read and write operations Is this correct for keeping top 2 bits of an 8 -bit value? “DEFECT” if not corrected Still syntax problems ”ERRORS” Fix as exercise Blackfin BF 533 I/O 20

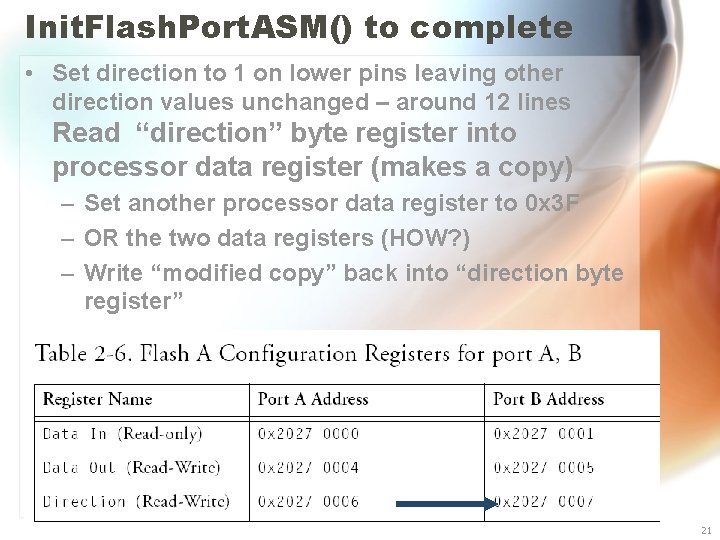

Init. Flash. Port. ASM() to complete • Set direction to 1 on lower pins leaving other direction values unchanged – around 12 lines Read “direction” byte register into processor data register (makes a copy) – Set another processor data register to 0 x 3 F – OR the two data registers (HOW? ) – Write “modified copy” back into “direction byte register” Blackfin BF 533 I/O 21

Init. Flash. ASM( ) -- Exercise • Init. Flash. ASM( ) { If FLASH memory already configured – return without initializing Else { configure Memory Bank control register THEN configure Global control (turns on the FLASH) } } -- 21 instructions – many cut-and-paste-modify Blackfin BF 533 I/O IF CLOCK ACTIVATED THEN ASSUME ANOTHER PROCESS HAS ALREADY SET THE FLASH “AND” on BIT 0 of EBIU_AMG CTL register followed by “IF” set then JUMP 22

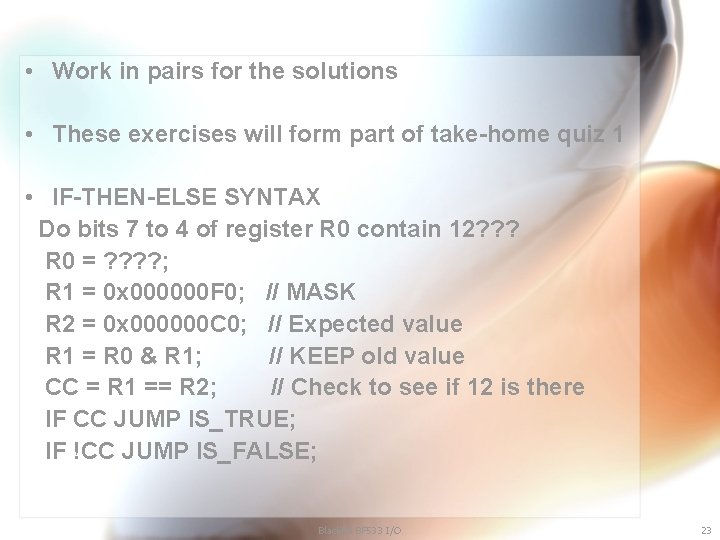

• Work in pairs for the solutions • These exercises will form part of take-home quiz 1 • IF-THEN-ELSE SYNTAX Do bits 7 to 4 of register R 0 contain 12? ? ? R 0 = ? ? ; R 1 = 0 x 000000 F 0; // MASK R 2 = 0 x 000000 C 0; // Expected value R 1 = R 0 & R 1; // KEEP old value CC = R 1 == R 2; // Check to see if 12 is there IF CC JUMP IS_TRUE; IF !CC JUMP IS_FALSE; Blackfin BF 533 I/O 23

Agenda • Processors need to send out control signals (high / low 1 / 0 true / false) – General purpose input / output GPIO on processor chip (16) – FLASH memory chip has additional I/O ports connected to Ez-Lite KIT LED’s • Making the FLASH memory I/O port control the Ez-KIT LED’s • The new Blackfin assembly language instructions needed Blackfin BF 533 I/O 27

- Slides: 24