BJT Amplifier BJT Amplifiers Overview Voltage Amplifier l

BJT Amplifier

BJT Amplifiers: Overview

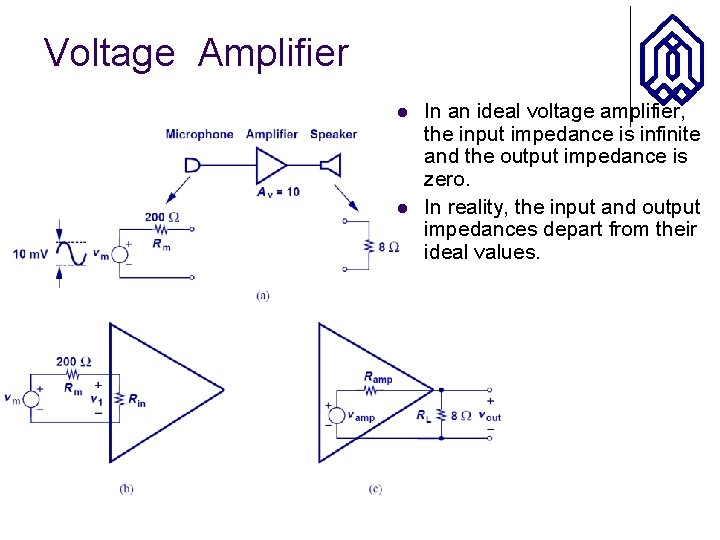

Voltage Amplifier l l In an ideal voltage amplifier, the input impedance is infinite and the output impedance is zero. In reality, the input and output impedances depart from their ideal values.

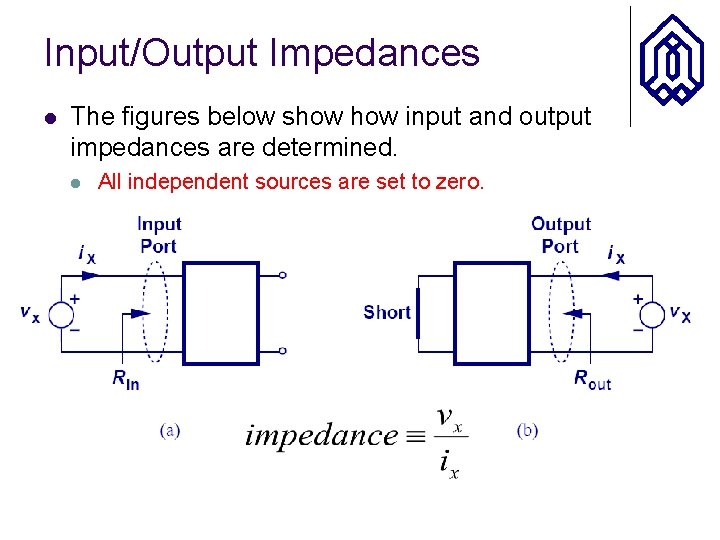

Input/Output Impedances l The figures below show input and output impedances are determined. l All independent sources are set to zero.

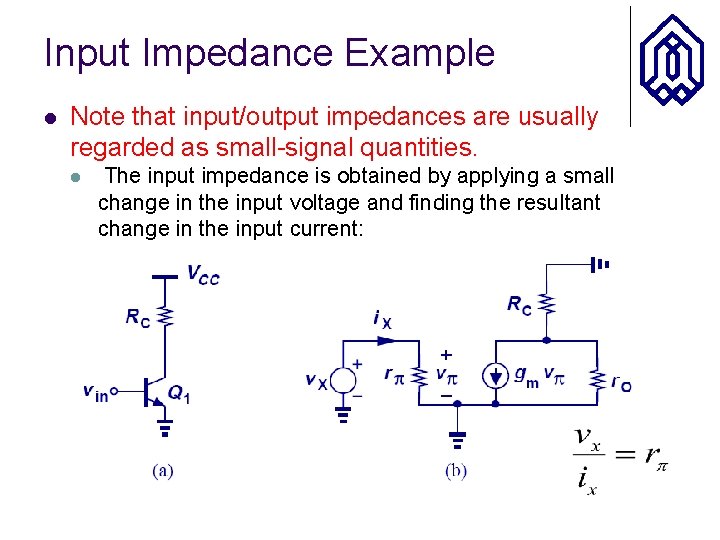

Input Impedance Example l Note that input/output impedances are usually regarded as small-signal quantities. l The input impedance is obtained by applying a small change in the input voltage and finding the resultant change in the input current:

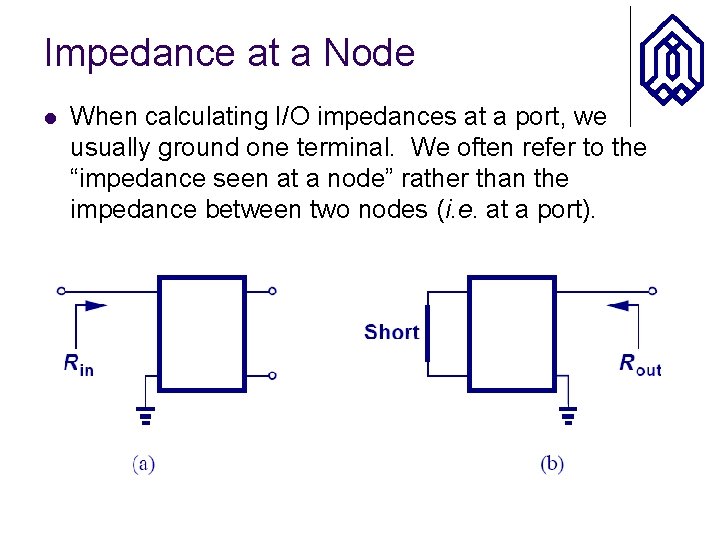

Impedance at a Node l When calculating I/O impedances at a port, we usually ground one terminal. We often refer to the “impedance seen at a node” rather than the impedance between two nodes (i. e. at a port).

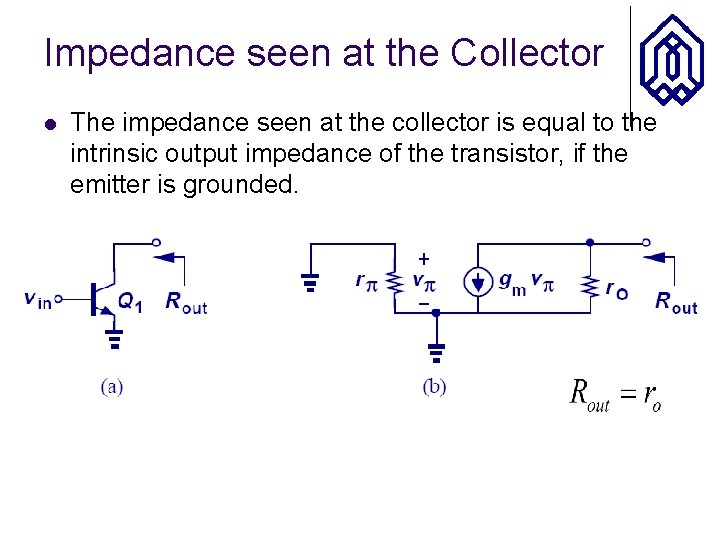

Impedance seen at the Collector l The impedance seen at the collector is equal to the intrinsic output impedance of the transistor, if the emitter is grounded.

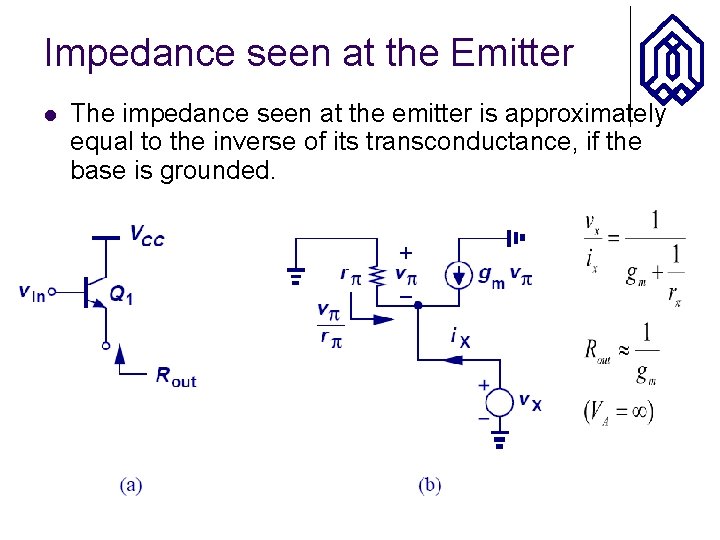

Impedance seen at the Emitter l The impedance seen at the emitter is approximately equal to the inverse of its transconductance, if the base is grounded.

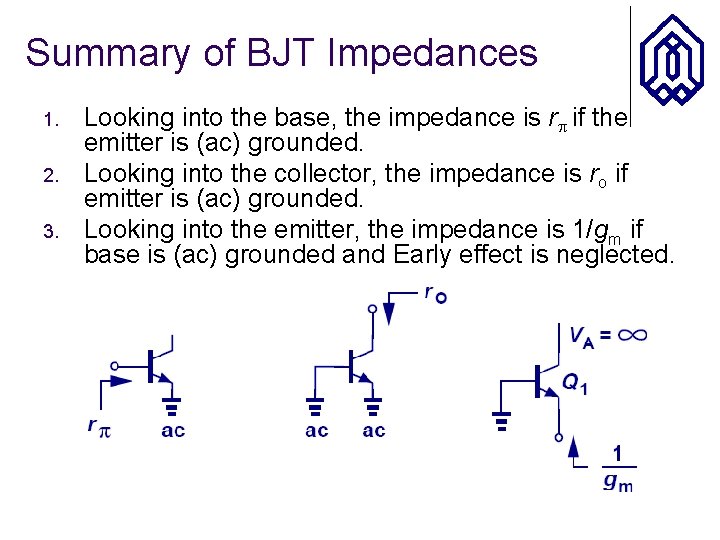

Summary of BJT Impedances 1. 2. 3. Looking into the base, the impedance is r if the emitter is (ac) grounded. Looking into the collector, the impedance is ro if emitter is (ac) grounded. Looking into the emitter, the impedance is 1/gm if base is (ac) grounded and Early effect is neglected.

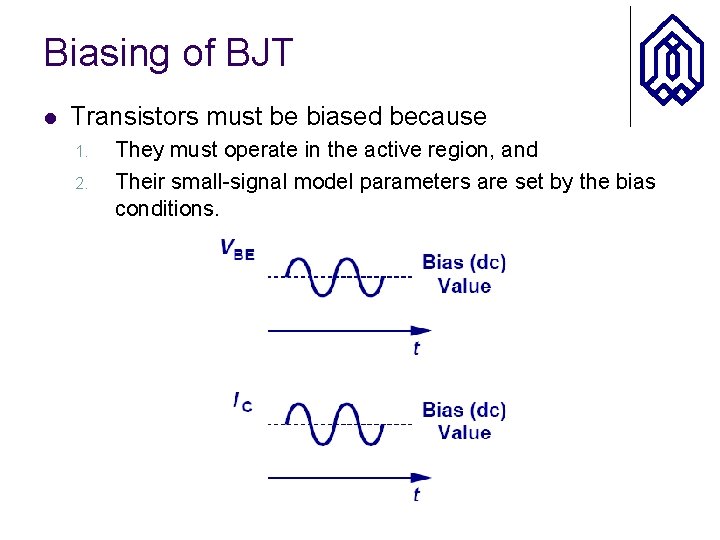

Biasing of BJT l Transistors must be biased because 1. 2. They must operate in the active region, and Their small-signal model parameters are set by the bias conditions.

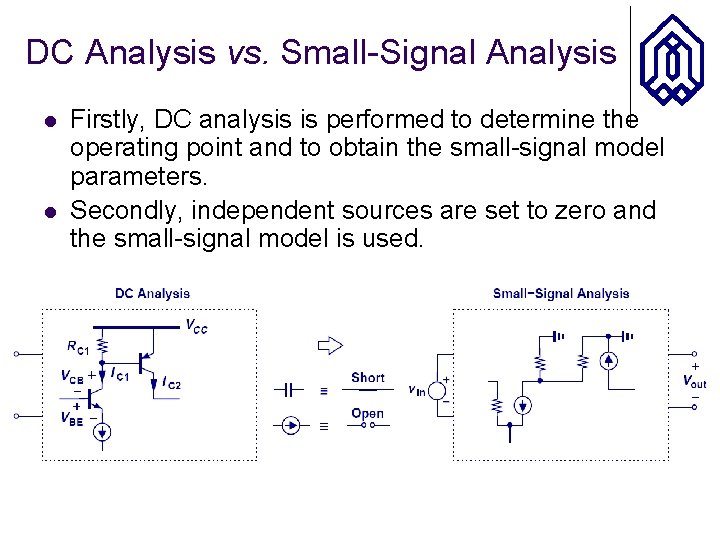

DC Analysis vs. Small-Signal Analysis l l Firstly, DC analysis is performed to determine the operating point and to obtain the small-signal model parameters. Secondly, independent sources are set to zero and the small-signal model is used.

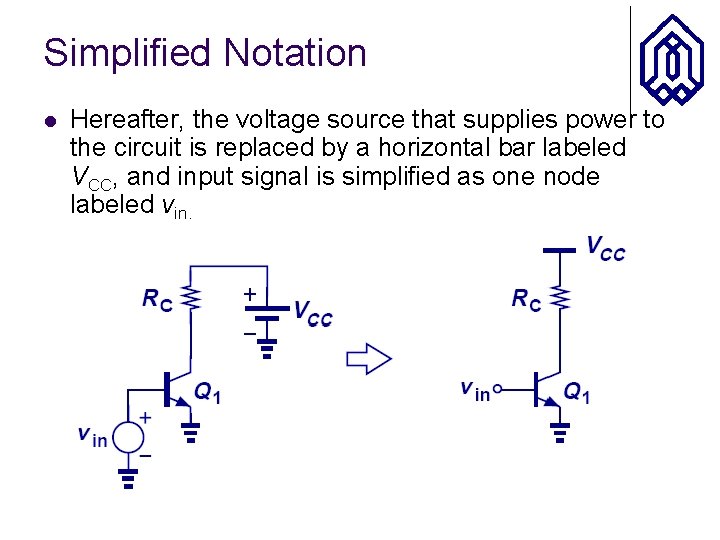

Simplified Notation l Hereafter, the voltage source that supplies power to the circuit is replaced by a horizontal bar labeled VCC, and input signal is simplified as one node labeled vin.

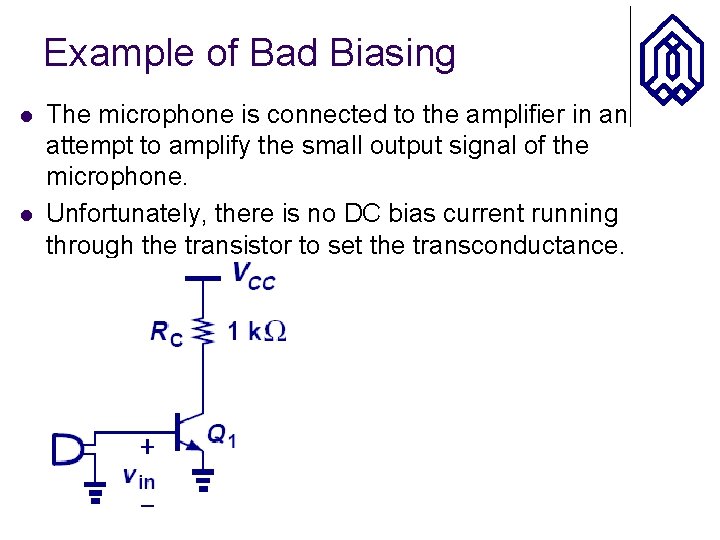

Example of Bad Biasing l l The microphone is connected to the amplifier in an attempt to amplify the small output signal of the microphone. Unfortunately, there is no DC bias current running through the transistor to set the transconductance.

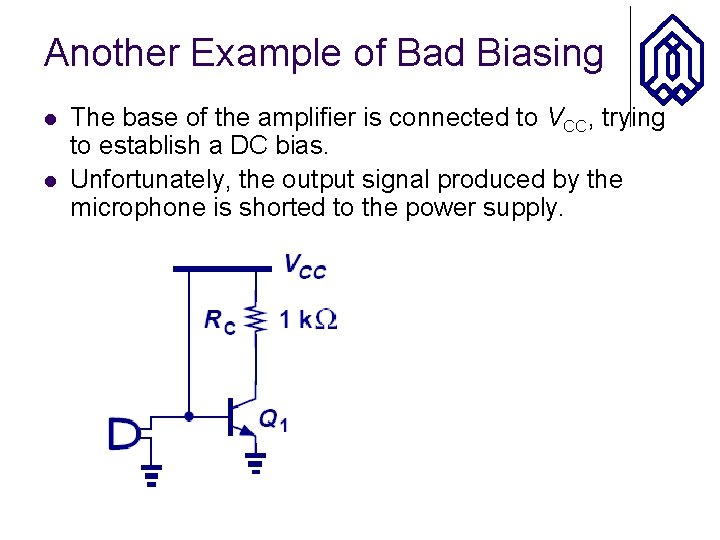

Another Example of Bad Biasing l l The base of the amplifier is connected to VCC, trying to establish a DC bias. Unfortunately, the output signal produced by the microphone is shorted to the power supply.

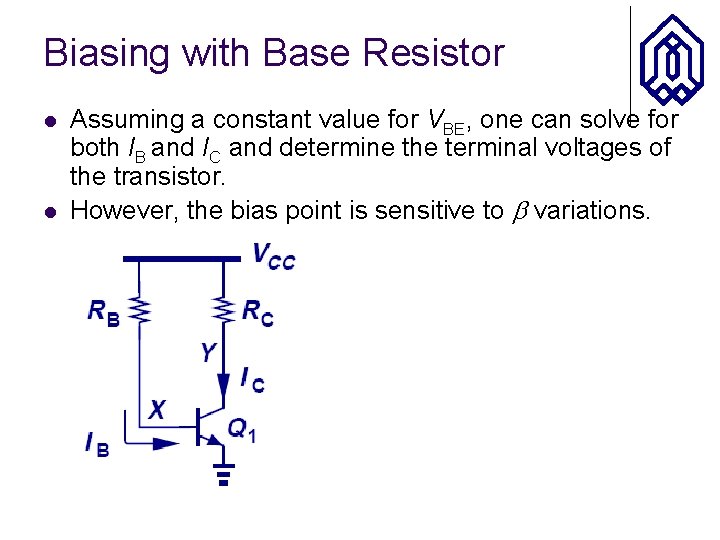

Biasing with Base Resistor l l Assuming a constant value for VBE, one can solve for both IB and IC and determine the terminal voltages of the transistor. However, the bias point is sensitive to variations.

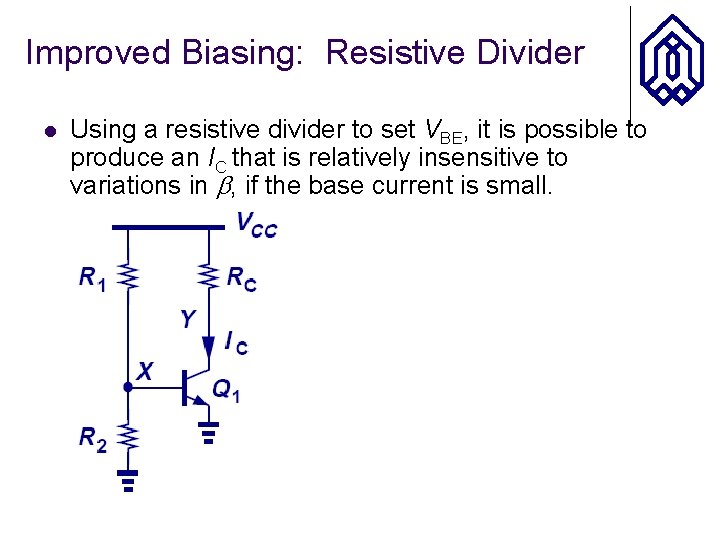

Improved Biasing: Resistive Divider l Using a resistive divider to set VBE, it is possible to produce an IC that is relatively insensitive to variations in , if the base current is small.

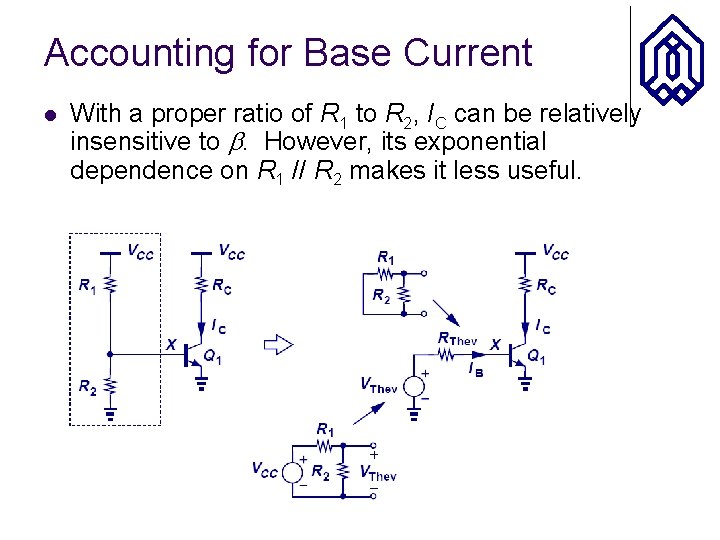

Accounting for Base Current l With a proper ratio of R 1 to R 2, IC can be relatively insensitive to . However, its exponential dependence on R 1 // R 2 makes it less useful.

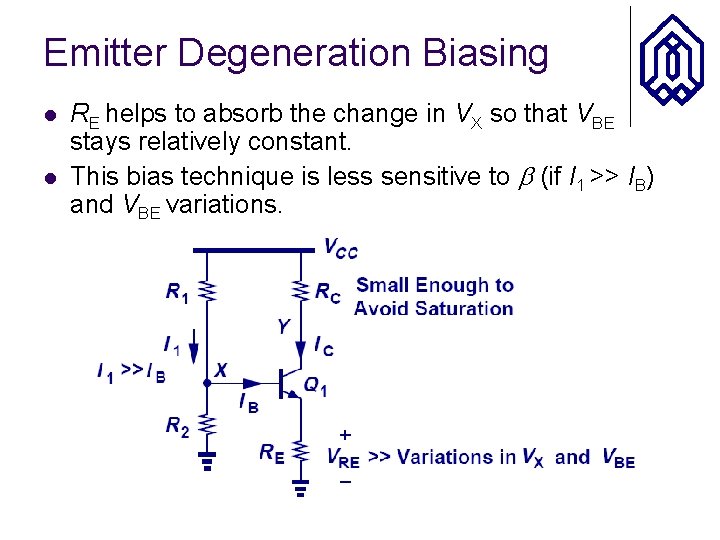

Emitter Degeneration Biasing l l RE helps to absorb the change in VX so that VBE stays relatively constant. This bias technique is less sensitive to (if I 1 >> IB) and VBE variations.

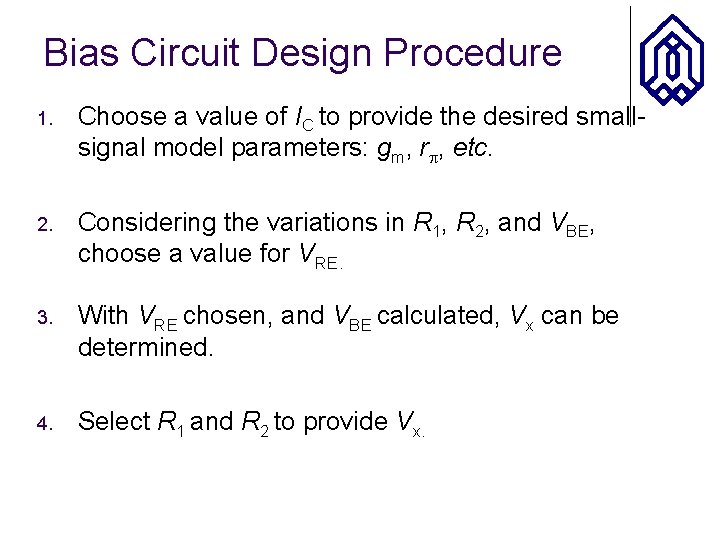

Bias Circuit Design Procedure 1. Choose a value of IC to provide the desired smallsignal model parameters: gm, r , etc. 2. Considering the variations in R 1, R 2, and VBE, choose a value for VRE. 3. With VRE chosen, and VBE calculated, Vx can be determined. 4. Select R 1 and R 2 to provide Vx.

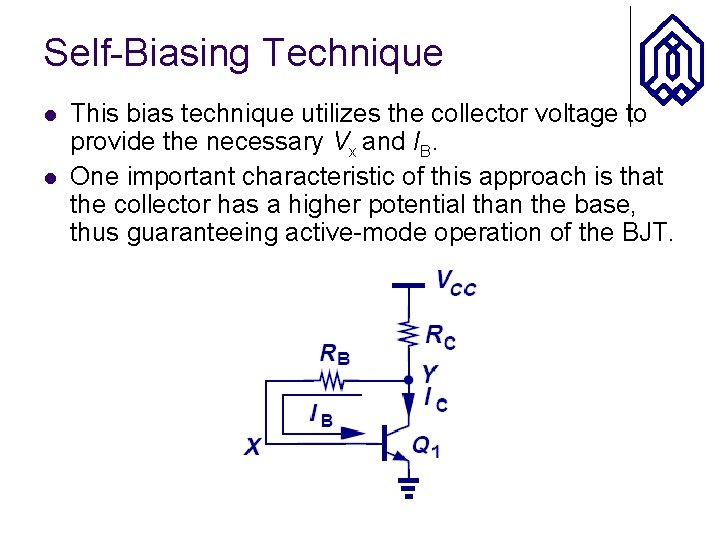

Self-Biasing Technique l l This bias technique utilizes the collector voltage to provide the necessary Vx and IB. One important characteristic of this approach is that the collector has a higher potential than the base, thus guaranteeing active-mode operation of the BJT.

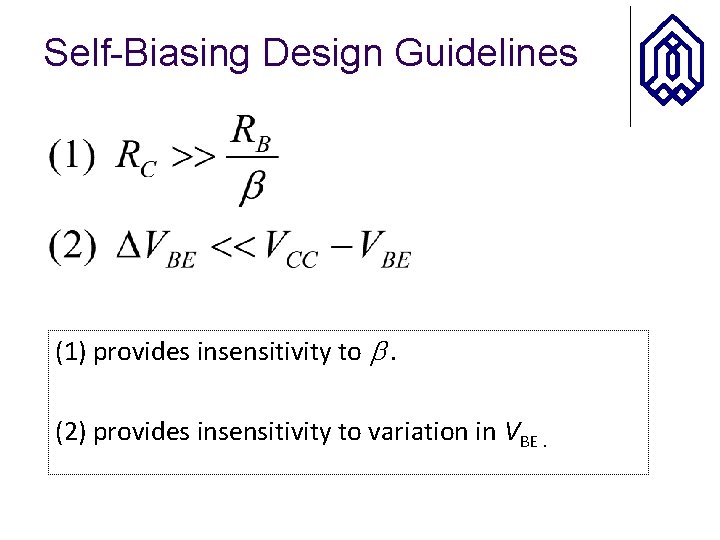

Self-Biasing Design Guidelines (1) provides insensitivity to . (2) provides insensitivity to variation in VBE.

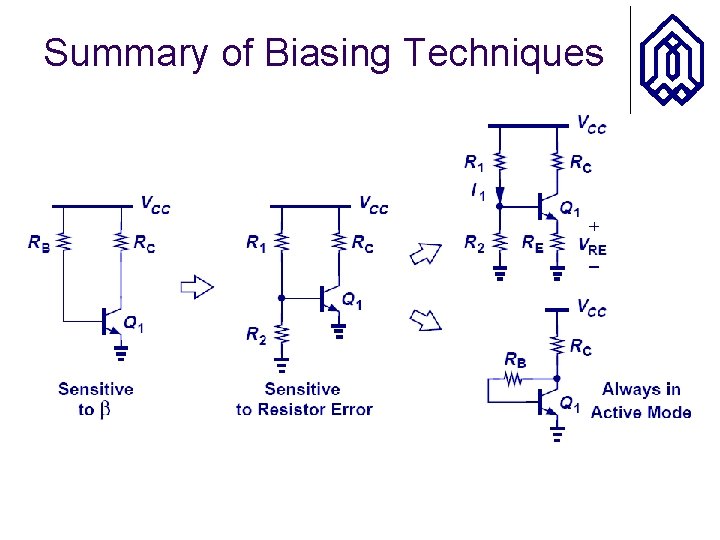

Summary of Biasing Techniques

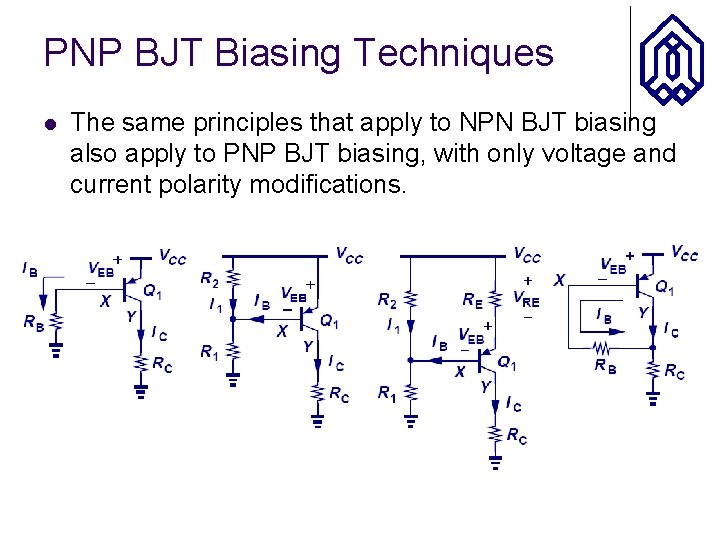

PNP BJT Biasing Techniques l The same principles that apply to NPN BJT biasing also apply to PNP BJT biasing, with only voltage and current polarity modifications.

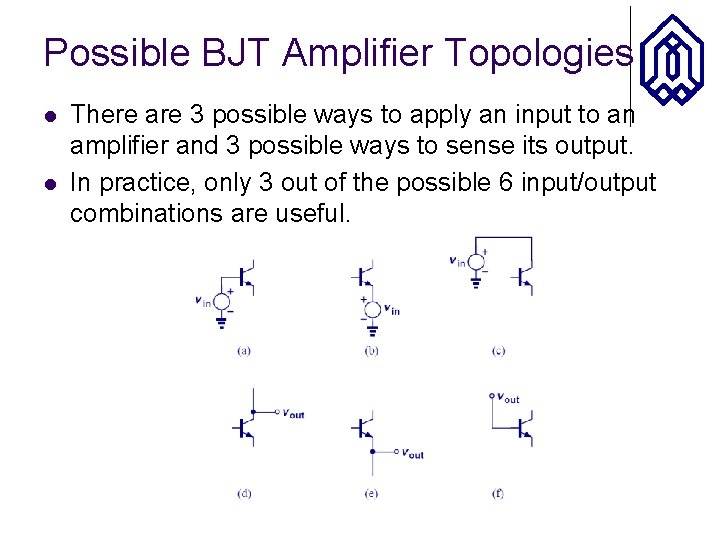

Possible BJT Amplifier Topologies l l There are 3 possible ways to apply an input to an amplifier and 3 possible ways to sense its output. In practice, only 3 out of the possible 6 input/output combinations are useful.

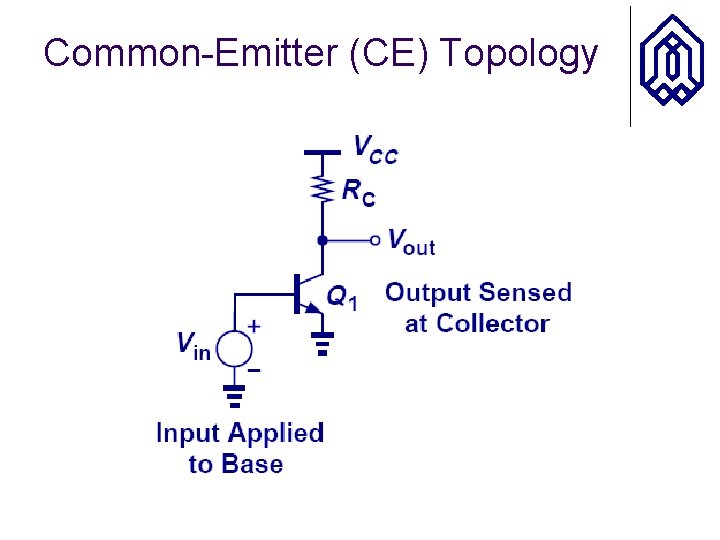

Common-Emitter (CE) Topology

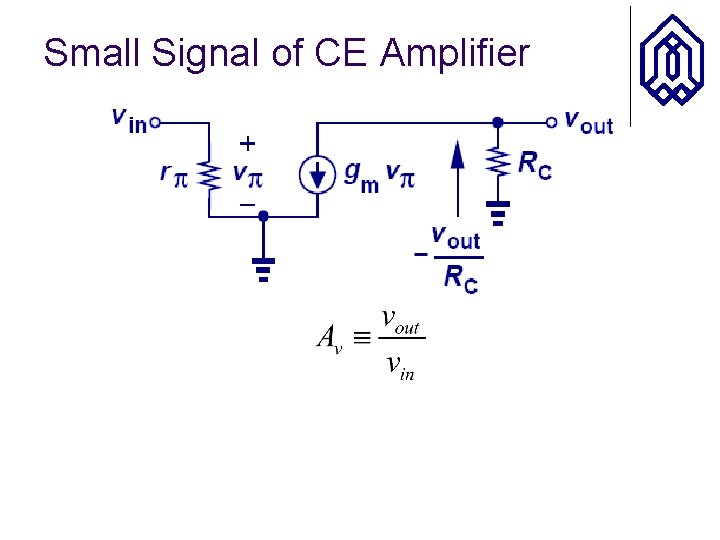

Small Signal of CE Amplifier

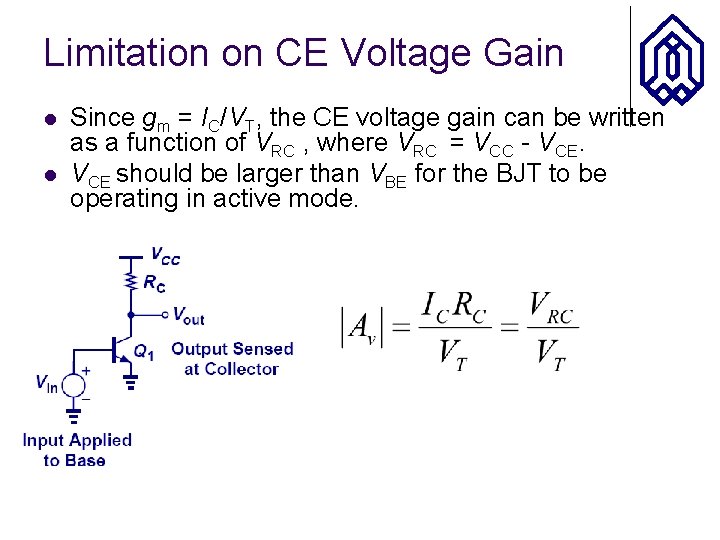

Limitation on CE Voltage Gain l l Since gm = IC/VT, the CE voltage gain can be written as a function of VRC , where VRC = VCC - VCE should be larger than VBE for the BJT to be operating in active mode.

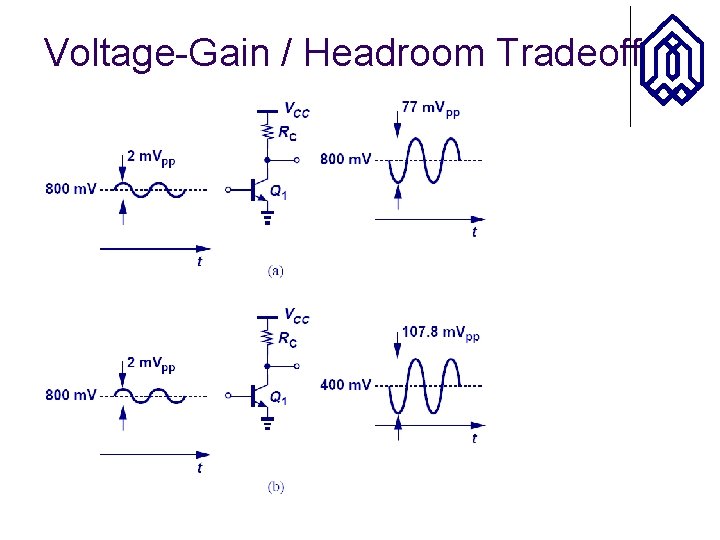

Voltage-Gain / Headroom Tradeoff

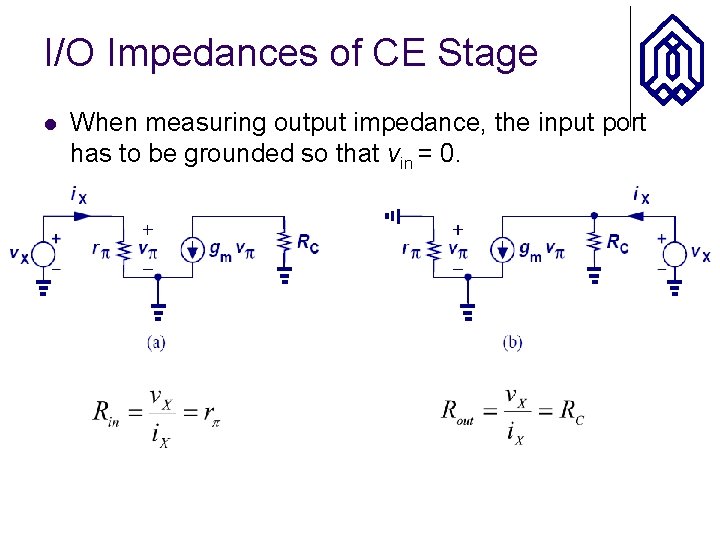

I/O Impedances of CE Stage l When measuring output impedance, the input port has to be grounded so that vin = 0.

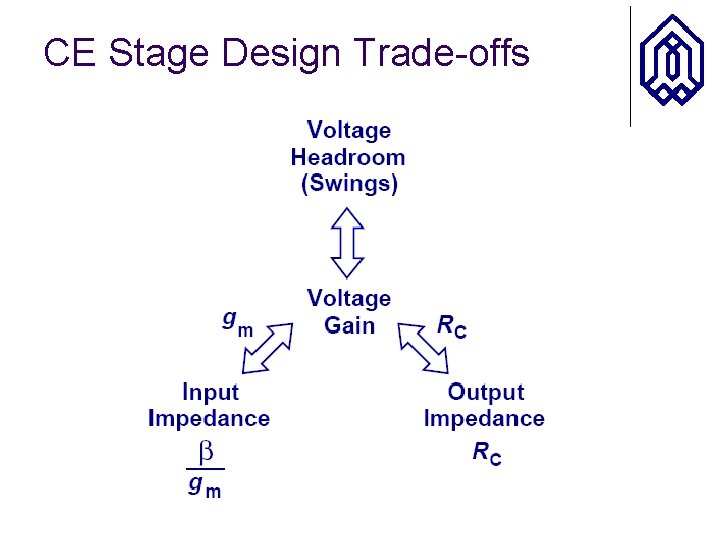

CE Stage Design Trade-offs

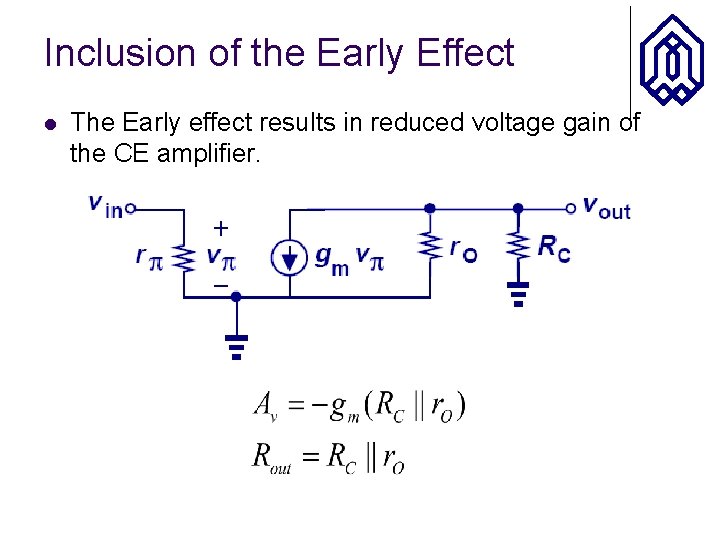

Inclusion of the Early Effect l The Early effect results in reduced voltage gain of the CE amplifier.

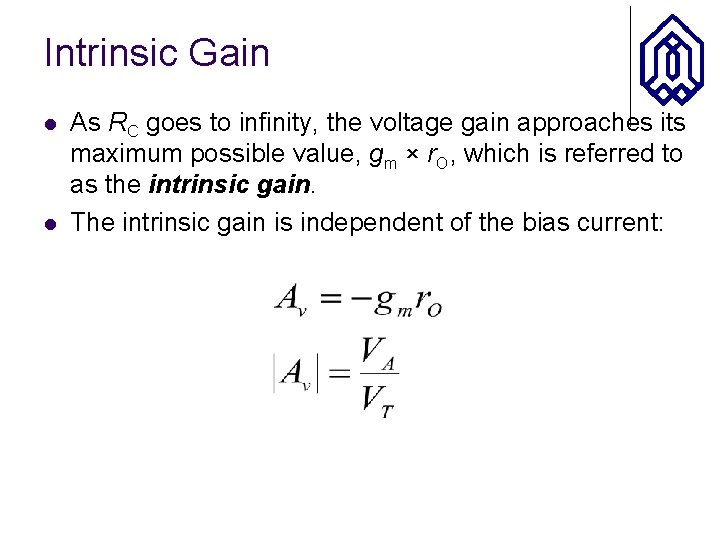

Intrinsic Gain l l As RC goes to infinity, the voltage gain approaches its maximum possible value, gm × r. O, which is referred to as the intrinsic gain. The intrinsic gain is independent of the bias current:

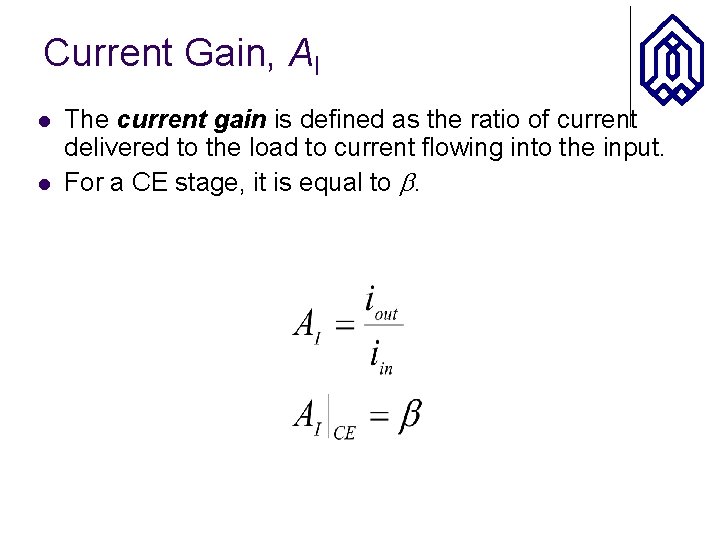

Current Gain, AI l l The current gain is defined as the ratio of current delivered to the load to current flowing into the input. For a CE stage, it is equal to .

- Slides: 33