BIST vs ATPG Introduction ATPG Automatic Test Pattern

BIST vs. ATPG

Introduction § ATPG – Automatic Test Pattern Generation § BIST – Built-In Self Test

Common scan architecture § logic test methodologies are based on a full scan infrastructure § all storage elements are connected together § Test patterns are pre-generated using a gate-level representation of the design netlist

Common scan architecture § Patterns are stored in tester memory and scanned into the circuit using parallel scan chains

Common scan architecture § Applying a test pattern consists of: 1) scanning in the pattern data 2) applying one or more functional clock cycles 3) scanning out the captured response data

Common scan architecture § The number of scan chains is limited by: § Chip I/O § Tester channels § On-chip routing congestion

Common scan architecture § BIST improves the scan infrastructure by adding: § An on-chip pattern generator § Feeds the scan chains § An on-chip result compressor § compresses the scanned out responses of all patterns into a final signature

Where similarity ends… § ATPG – uses an on-chip pattern generator as a decompressor § BIST – uses an on-chip pseudo-random pattern generator (PRPG)

Breaking the myths!!!

Myth#1: ATPG achieves better fault coverage than logic BIST

Why is that? § BIST uses random test patterns: § Lower stuck@ faults coverage § Designs will require a large number of random patterns

Solution § Designs can be modified by inserting scan-accessed test points to increase their random pattern testability

Breaking the myth § Empirical evidence shows that when 1 test point is added per 1, 000 gates (1% overhead): § stuck@ fault coverages achieved with deterministic ATPG can be obtained with a reasonable number of random patterns § (50 K to 100 K range)

Breaking the myth § Chip quality really depends on physical defect coverage § True defect coverage is proportional to the number of times each modeled fault is detected § Large number of random patterns results in significantly greater defect coverage than that achieved by the limited number of deterministic patterns

Myth#2: ATPG approaches easily scale with growing chip sizes

What is the problem? § ATPG tools typically operate on the fully flattened netlist û ever-growing CPU requirements û growing test pattern volumes û significant impact on the design cycle

What is the problem? § Cores can be dealt with separately by fully isolating them with scan cells § The resulting overhead is typically prohibitive § pattern volume reductions represent only in a one-time improvement

Solution § Hierarchical cores are made self-testable independently of other cores § Some patented techniques allow isolation of the core during test using little or no overhead

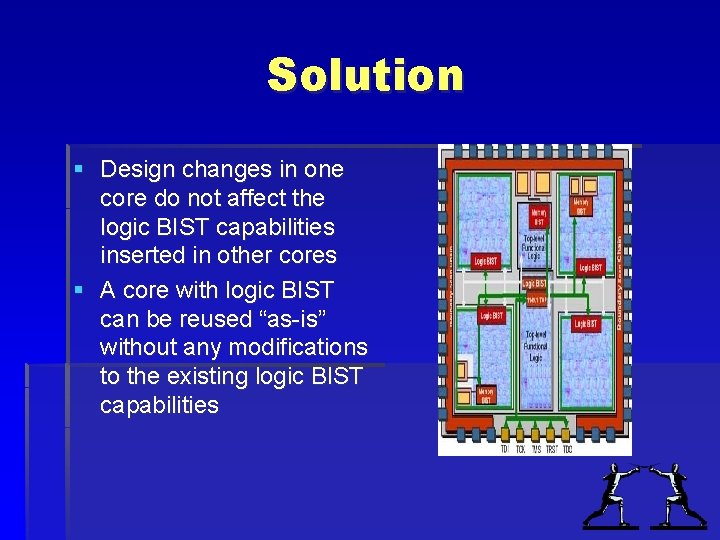

Solution § Design changes in one core do not affect the logic BIST capabilities inserted in other cores § A core with logic BIST can be reused “as-is” without any modifications to the existing logic BIST capabilities

More advantages § BIST does not require the storage of any test pattern data or require external control of clocks § it can be reused during board and system level testing. § reduces board and system manufacturing test development costs § helps time-to-market through faster hardware debug § When a chip fails functionally in the system, it can be debugged more reliably by running BIST

More advantages § BIST can also be used for dynamic burnin § Parallel execution of logic BIST on all devices on a burn-in board can be achieved using only the low-speed IEEE 1149. 1 interface for board-level access. Pre burn-in tests can even be applied using the burn-in board, eliminating a test insertion

Conclusion § ATPG continues to try to provide techniques to meet the testing challenges of complex designs § BIST capabilities originally developed to address these high-end design test has become field hardened and field proven solutions

- Slides: 22