Binary Counter with Decimal and Gray Encoding ELEC

Binary Counter with Decimal and Gray Encoding ELEC 5270 – Low Power Design of Electronic Circuits Spring 2009 Grant Lewis 1

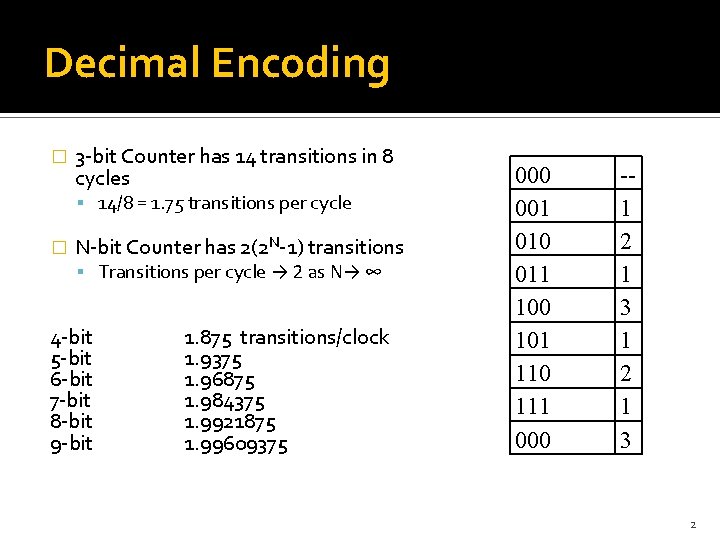

Decimal Encoding � 3 -bit Counter has 14 transitions in 8 cycles 14/8 = 1. 75 transitions per cycle � N-bit Counter has 2(2 N-1) transitions Transitions per cycle → 2 as N→ ∞ 4 -bit 5 -bit 6 -bit 7 -bit 8 -bit 9 -bit 1. 875 transitions/clock 1. 9375 1. 96875 1. 984375 1. 9921875 1. 99609375 000 001 010 011 100 101 110 111 000 -1 2 1 3 2

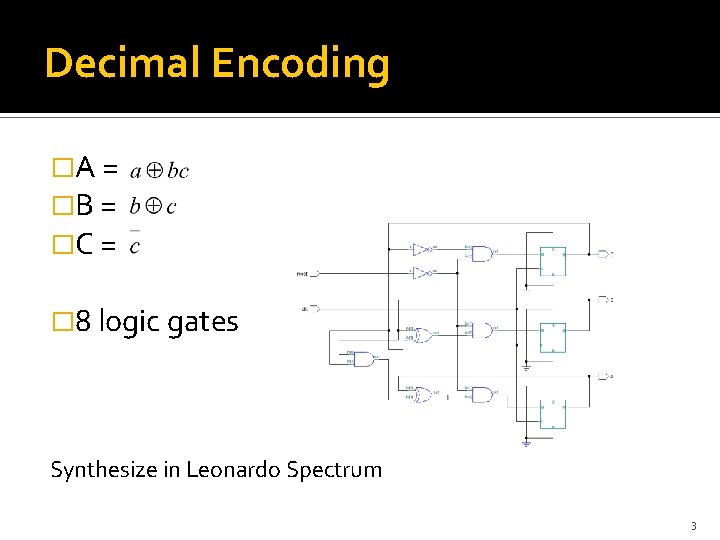

Decimal Encoding �A = �B = �C = � 8 logic gates Synthesize in Leonardo Spectrum 3

Gray Encoding � 3 -bit counter has 8 transitions in 8 cycles 8/8 = 1 transition per cycle �N-bit counter has 2 N transitions Transitions per cycle is 1 for any size counter �For large counters, ratio of transitions for Decimal to Gray → 2 000 -- 001 010 111 100 000 1 1 1 1 4

Gray Encoding � Gray Encoding can be accomplished by Binary to Gray conversion Directly Synthesizing Gray Counter � Binary to Gray conversion is accomplished with 2 XOR gates 5

Binary to Gray Conversion �With optimizations, adds one logic gate (total 9 logic gates) 6

Gray Encoding �A = �B = �C = �Adds 4 logic gates (total 12 gates) 7

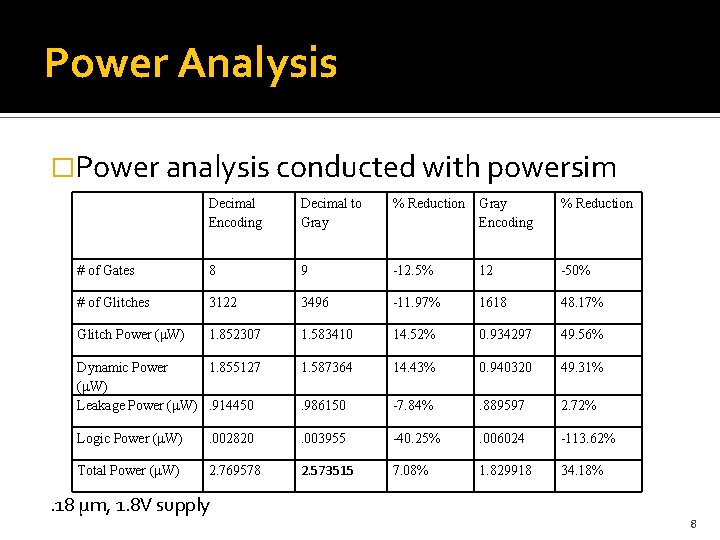

Power Analysis �Power analysis conducted with powersim Decimal Encoding Decimal to Gray % Reduction Gray Encoding % Reduction # of Gates 8 9 -12. 5% 12 -50% # of Glitches 3122 3496 -11. 97% 1618 48. 17% Glitch Power (μW) 1. 852307 1. 583410 14. 52% 0. 934297 49. 56% Dynamic Power 1. 855127 (μW) Leakage Power (μW). 914450 1. 587364 14. 43% 0. 940320 49. 31% . 986150 -7. 84% . 889597 2. 72% Logic Power (μW) . 002820 . 003955 -40. 25% . 006024 -113. 62% Total Power (μW) 2. 769578 2. 573515 7. 08% 1. 829918 34. 18% . 18 μm, 1. 8 V supply 8

Conclusions �Much of dynamic power consumption comes from glitches Can be reduced by path balancing �Directly implementing gray counter in logic removes ~1/2 of the glitches, however consumes more leakage and logic power due to increase in number of logic gates �Overall, gray counters are more power efficient 9

References �Hakenes, R. ; Manoli Y. “A Segmented Gray Code for Low-Power Microcontroller Address Buses”. EUROMICRO Conference, 1999. Proceedings. 25 th, Pages 240 – 243, Vol. 1 �Doran, R. W. “The Gray Code”. Centre for Discrete Mathematics and Theoretical Computer Science, March, 2007. �Mehta, Huzefa et al. “Some Issues in Gray Code Addressing”. Proceedings of the 6 th Great Lakes Symposium on VLSI, 1996. Pages 178 – 181. 10

- Slides: 10