BESIII Electronics and OnLine BESIII Workshop in Beijing

BESIII Electronics and On-Line BESIII Workshop in Beijing IHEP Zhao Jing-wei Sheng Hua-yi He Kang-ling October 13, 2001 Brief n Measurement Tasks n Technical Strategy n Sub-systems n Configurations and Software n On-Line System n

Brief BESIII’s sub-detectors are: n n n Vertex Chamber Main Drift Chamber TOF plus CCT Counter Electromagnetic Calorimeter MUON Identifier Electronics will consist of five sub-systems correspondingly. Total channel amount is about 50 K~77 K.

Measurement Tasks n n n To measure the time information carried by detector signal. To measure the charge values carried by detector output signals or signal amplitude. To deliver the information of fired point position (x, y) in detector cells. To provide the hit information or sum of analog signals for making trigger decision. To implement data taking and data formatting and preprocessing and sub-event packing. To transfer the packed data to On-line computer system via fast switch network.

Technical Strategy n n Short bunch crossing (8 ns) Long trigger latency (2. 4 us) pipeline must be used. High luminosity (1× 1033 cm-2 s-1). High event rate. Parallel processing on-board is needed to make dead time as small as possible.

Technical Strategy n n High beam intensity (1100 m. A× 2) Short lifetime (3 -4 hours) Bad noise environment Measures must be taken to make system immune from noise background and RF interference. Weak signal, especially for VC, EMC and MDC. low noise technique must be adopted.

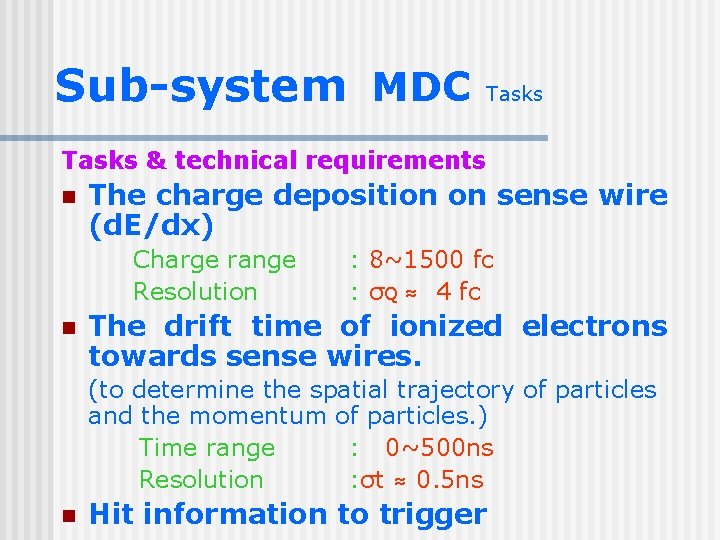

Sub-system MDC Tasks & technical requirements n The charge deposition on sense wire (d. E/dx) Charge range Resolution n : 8~1500 fc : σQ ≈ 4 fc The drift time of ionized electrons towards sense wires. (to determine the spatial trajectory of particles and the momentum of particles. ) Time range : 0~500 ns Resolution : σt ≈ 0. 5 ns n Hit information to trigger

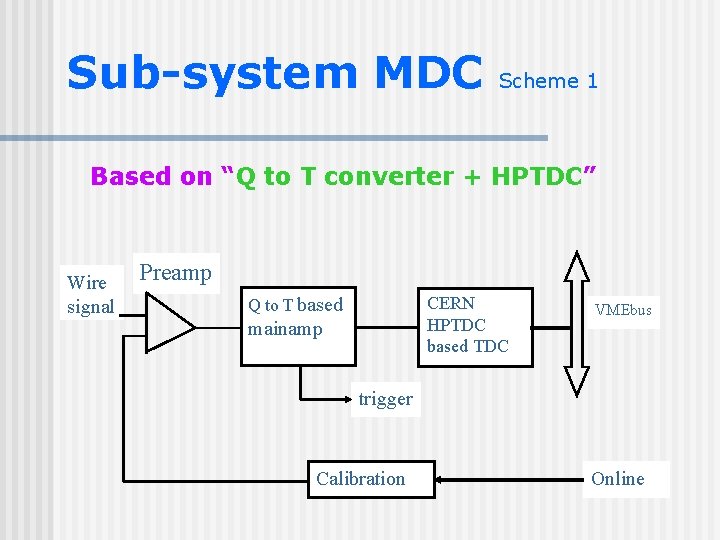

Sub-system MDC Scheme 1 Based on “Q to T converter + HPTDC” Wire signal Preamp Q to T based CERN HPTDC based TDC mainamp VMEbus trigger Calibration Online

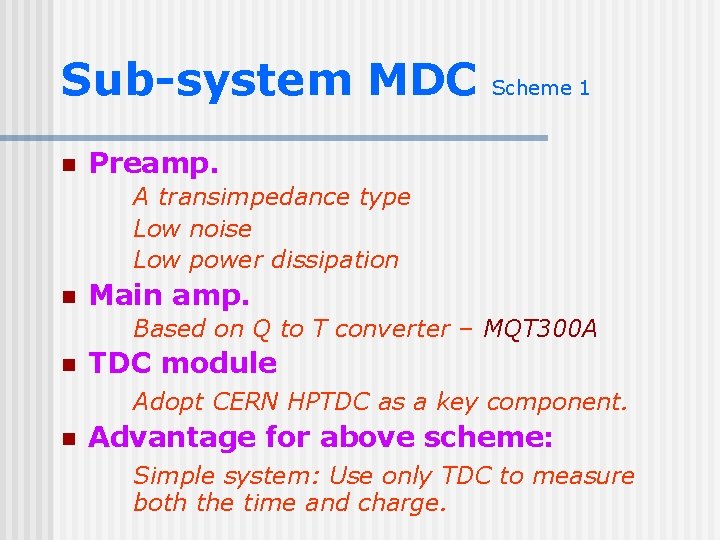

Sub-system MDC n Scheme 1 Preamp. A transimpedance type Low noise Low power dissipation n Main amp. Based on Q to T converter – MQT 300 A n TDC module Adopt CERN HPTDC as a key component. n Advantage for above scheme: Simple system: Use only TDC to measure both the time and charge.

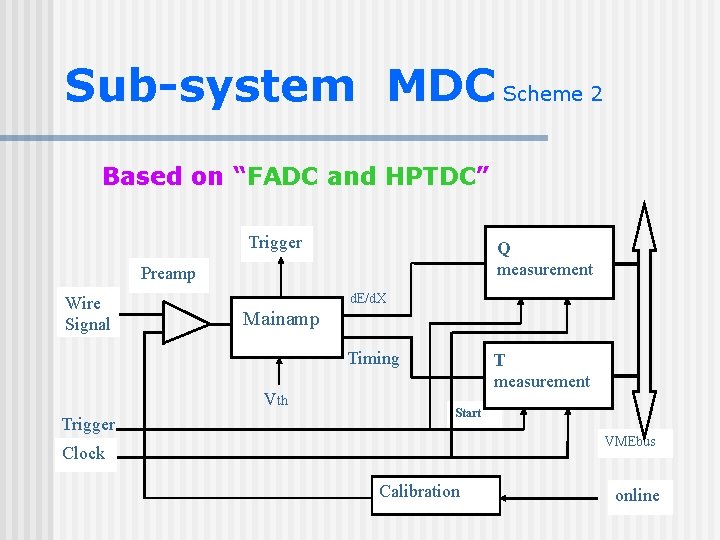

Sub-system MDC Scheme 2 Based on “FADC and HPTDC” Trigger Q measurement Preamp Wire Signal d. E/d. X Mainamp Timing Vth Trigger T measurement Start VMEbus Clock Calibration online

Sub-system MDC Scheme 2 n Charge measurement is based on FADC waveform sampling & Numerical integral. 10 bit and 40 MHz FADC is required. 9 U VME board and 32 ch. /board n Time measurement is based on CERN HPTDC chip 9 U VME board and 96 or 128 ch. /board

Sub-system VC Charge information Range = 0. 22 fc on average σQ ≤ 20% at 0. 22 fc Ch. = 300 n Hit information to trigger n

Sub-system Em. C Tasks Charge measurement Range : 0. 2 fc to 300 fc Resolution : q= 0. 1 fc

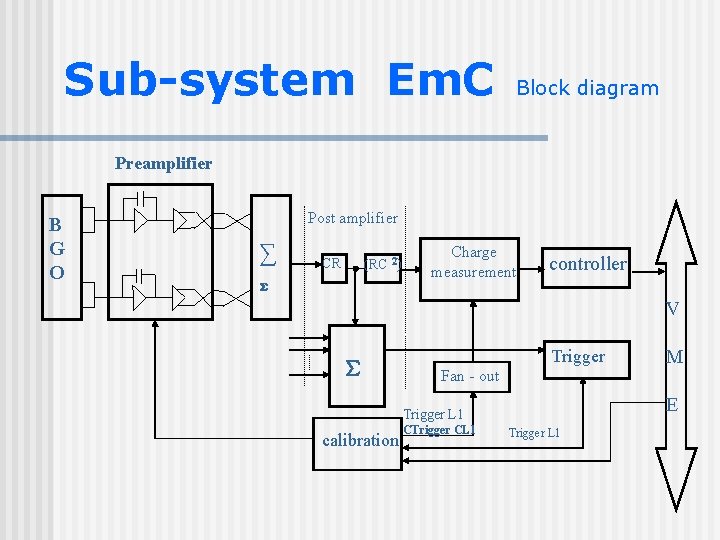

Sub-system Em. C Block diagram Preamplifier B G O Post amplifier ∑ (RC 2) CR Charge measurement controller Σ V ∑ Trigger Fan - out E Trigger L 1 calibration CTrigger CL 1 M Trigger L 1

Sub-system Em. C n n n Brief introduction 20200 BGO crystals Charge-sensitive preamplifier to receive the signal from photodiode 20 MHz FADC to digitize the waveform 15 bit dynamic range is needed. 10 bit resolution is required.

Sub-system Em. C n n n Scheme Preamplifiers are mounted on the BGO crystals. Two signals from each crystal are added together, and then feeds to post-amplifier for further amplifying and shaping. FADC samples the signal with 20 MHz. The data are pushed to the digital pipeline. The length of the pipeline equals the trigger L 1 latency. Digitized data within 1. 5 ms interval are read out by a peak finding circuit on arrival of trigger L 1. The peak value is stored in a buffer for readout by VME. Auto Range Encode Circuits are employed to expand the FADC dynamic range from 10 bits to 15 bits.

Sub-system TOF Tasks To provide the information for particle identification by measuring the flight time of the particles. n To correct the flight time by measuring the charge. n To provide hit information to trigger n

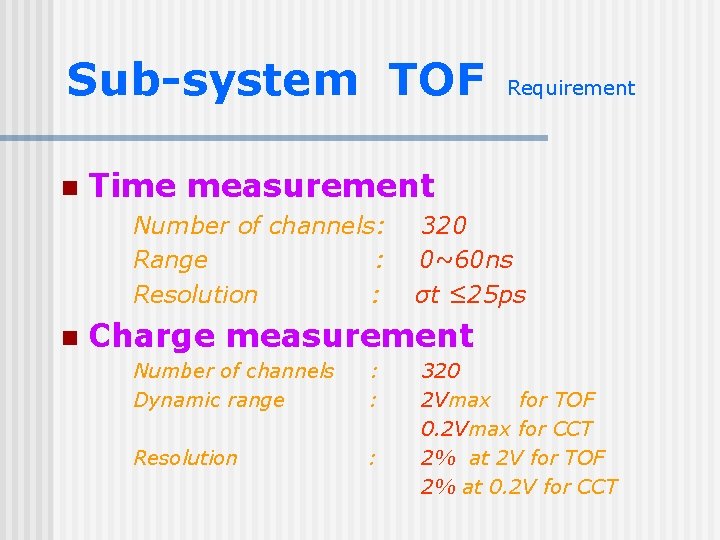

Sub-system TOF n Time measurement Number of channels: Range : Resolution : n Requirement 320 0~60 ns σt ≤ 25 ps Charge measurement Number of channels Dynamic range : : Resolution : 320 2 Vmax for TOF 0. 2 Vmax for CCT 2% at 2 V for TOF 2% at 0. 2 V for CCT

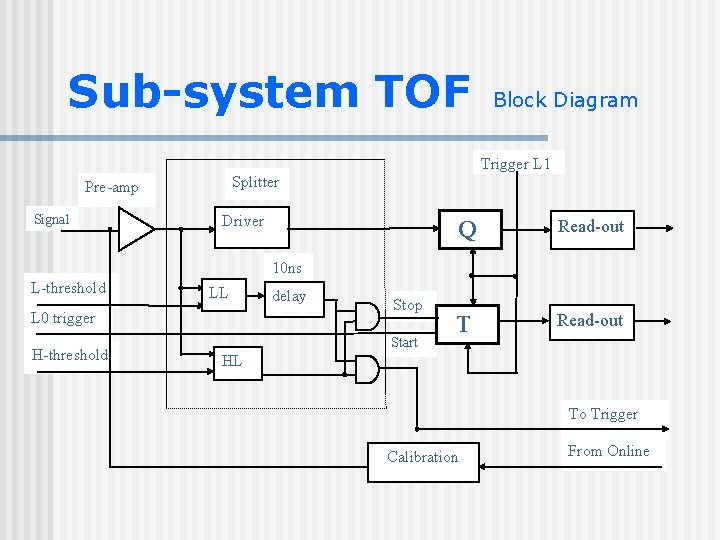

Sub-system TOF Block Diagram Trigger L 1 Splitter Pre-amp Signal Driver Q Read-out T Read-out 10 ns L-threshold LL L 0 trigger H-threshold delay Stop Start HL To Trigger Calibration From Online

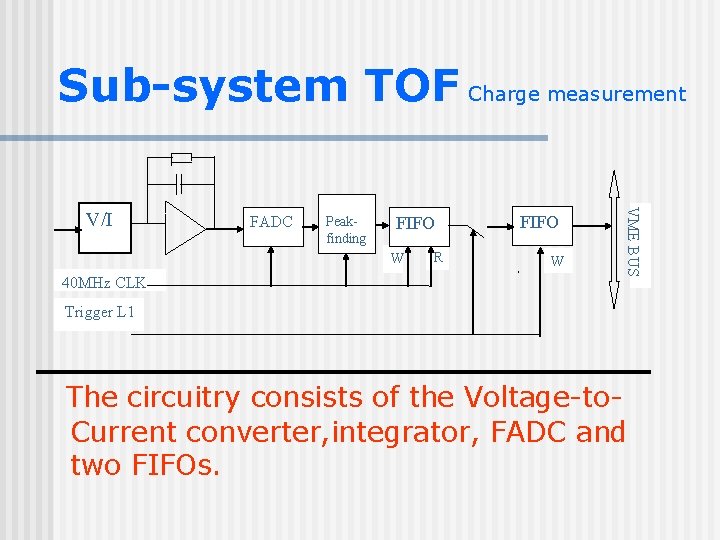

Sub-system TOF Charge measurement FADC Peakfinding FIFO W 40 MHz CLK R FIFO W VME BUS V/I Trigger L 1 The circuitry consists of the Voltage-to. Current converter, integrator, FADC and two FIFOs.

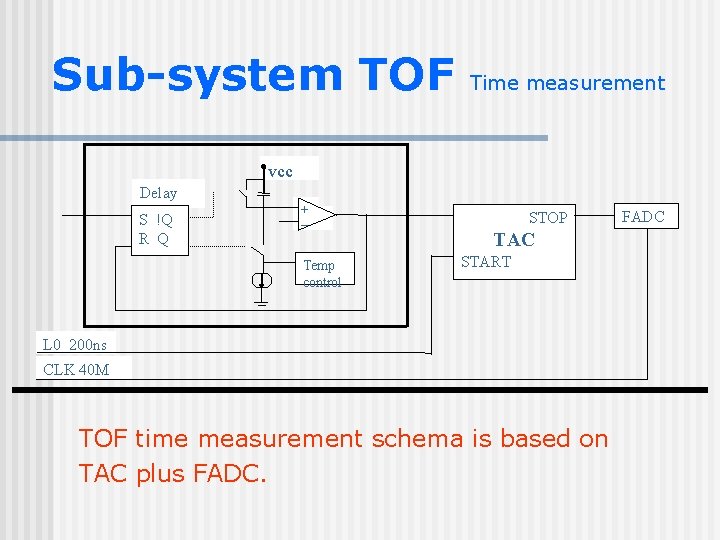

Sub-system TOF Time measurement vcc Delay S !Q R Q + _ STOP TAC Temp control START L 0 200 ns CLK 40 M TOF time measurement schema is based on TAC plus FADC

Sub-system Muon Tasks & technical requirements To deliver the information of fired point position(x, y) in detector cells. n The hit information to trigger n

Sub-system Muon n Configuration n n Modules of VME Chains in a module Data of a chain Total data of readout system 7 24 256 10 K~30 K

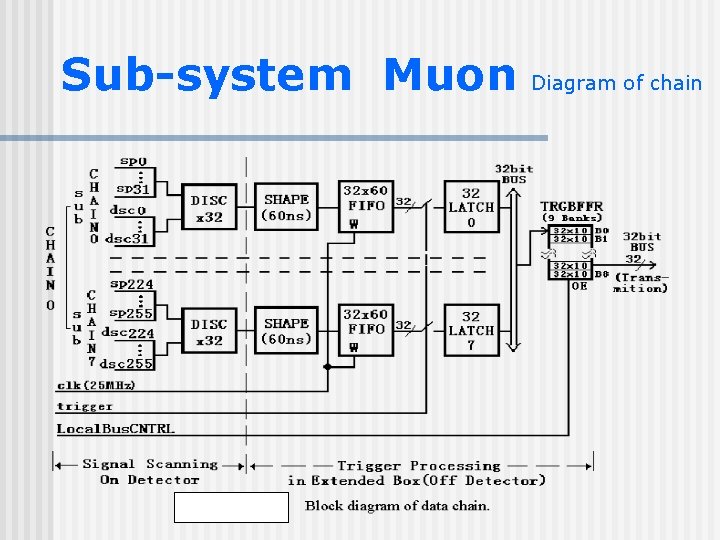

Sub-system Muon Diagram of chain

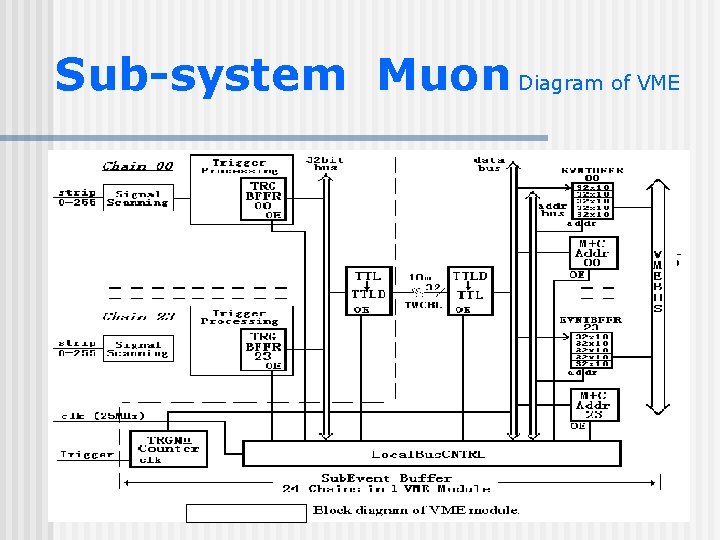

Sub-system Muon Diagram of VME

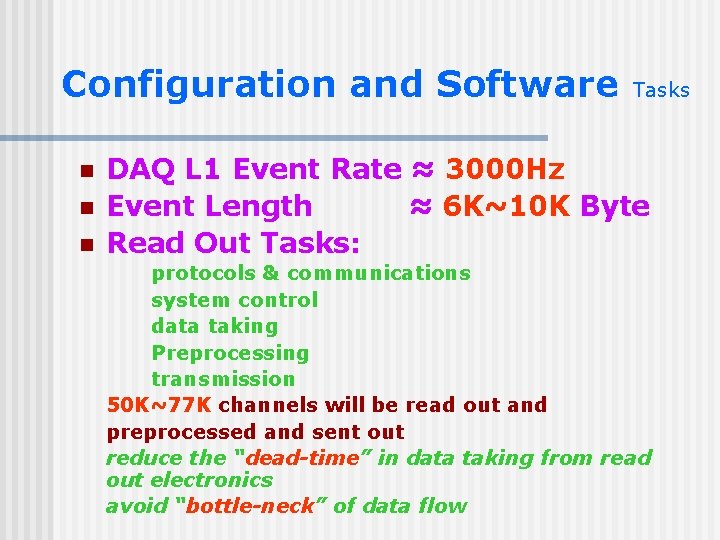

Configuration and Software n n n Tasks DAQ L 1 Event Rate ≈ 3000 Hz Event Length ≈ 6 K~10 K Byte Read Out Tasks: protocols & communications system control data taking Preprocessing transmission 50 K~77 K channels will be read out and preprocessed and sent out reduce the “dead-time” in data taking from read out electronics avoid “bottle-neck” of data flow

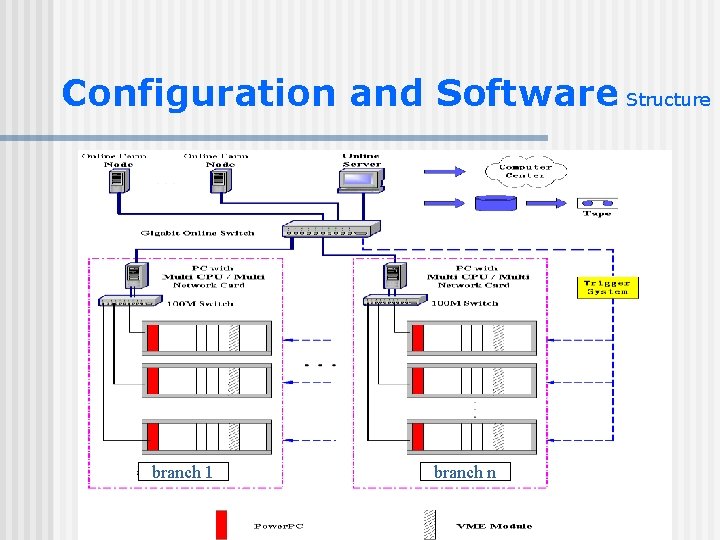

Configuration and Software Structure branch 1 branch n

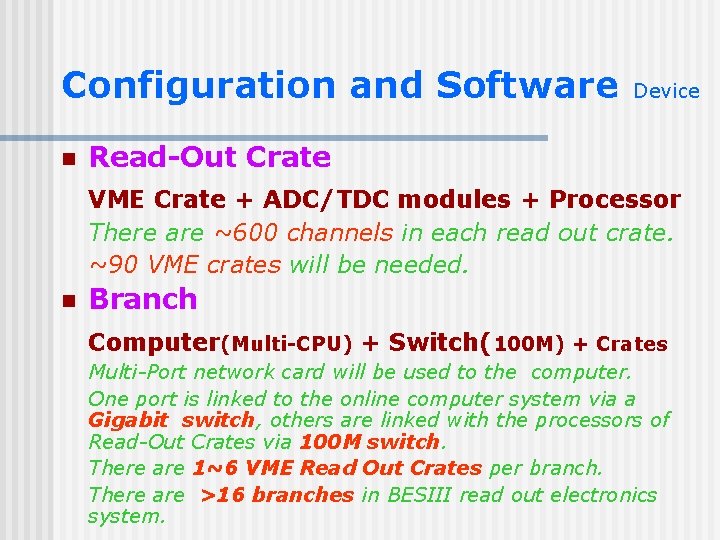

Configuration and Software n Device Read-Out Crate VME Crate + ADC/TDC modules + Processor There are ~600 channels in each read out crate. ~90 VME crates will be needed. n Branch Computer(Multi-CPU) + Switch(100 M) + Crates Multi-Port network card will be used to the computer. One port is linked to the online computer system via a Gigabit switch, others are linked with the processors of Read-Out Crates via 100 M switch. There are 1~6 VME Read Out Crates per branch. There are >16 branches in BESIII read out electronics system.

Configuration and Software Design Consideration n Adopt Commercial Product Power. PC 、100 M Switch、Computer and others n n Consider to adopt new technique and future device Performance/cost ratio The software developing environment Vx. Works and x 86 BSP、Power. PC 750 BSP

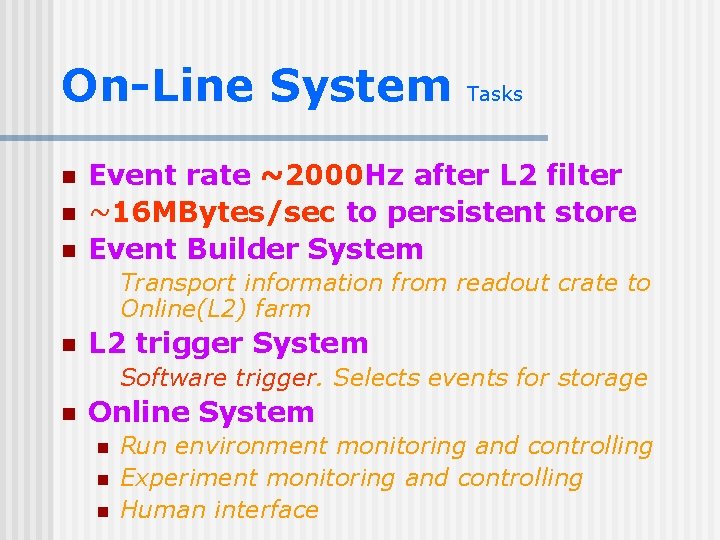

On-Line System n n n Tasks Event rate ~2000 Hz after L 2 filter ~16 MBytes/sec to persistent store Event Builder System Transport information from readout crate to Online(L 2) farm n L 2 trigger System Software trigger. Selects events for storage n Online System n n n Run environment monitoring and controlling Experiment monitoring and controlling Human interface

On-Line System n Tasks Data Storage mass storage and transmission via fast network n Slow control system HV control and monitoring n Environmental monitoring n Dead time & Luminosity monitoring n n Tests

On-Line System n n n High performance computer Graphics User Interface to experiment Functional requirement n n n n Requirements Configuration and constants of system Execute command to FEE and Farm nodes Error message reports for FEE and Farm nodes Calibration Support Diagnostic Tools Data Monitoring Support Database and network support

Thanks!

- Slides: 32