Belle II SVD Silicon On Insulator Belle II

Sign up to view full document!

SIGN UP

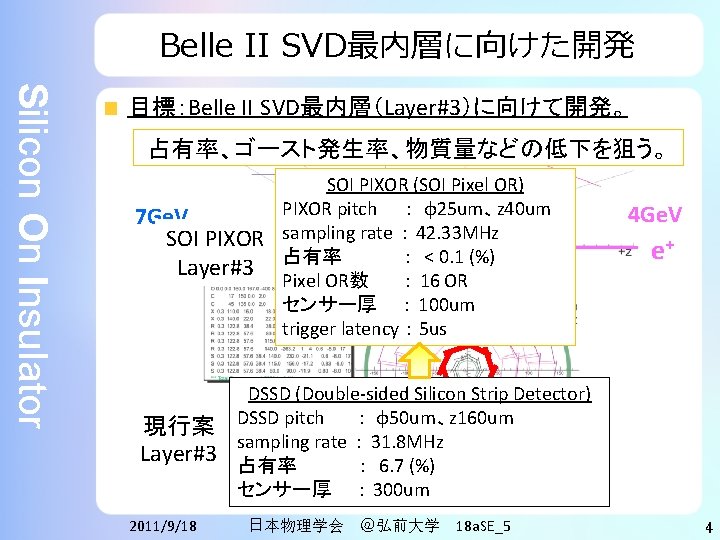

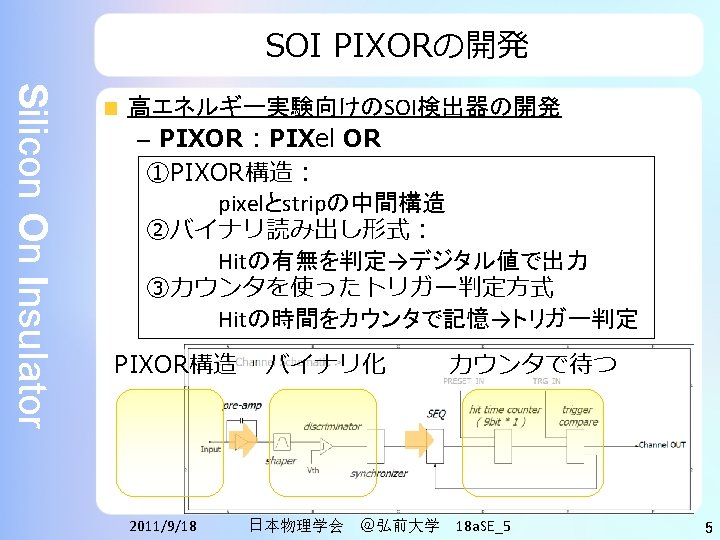

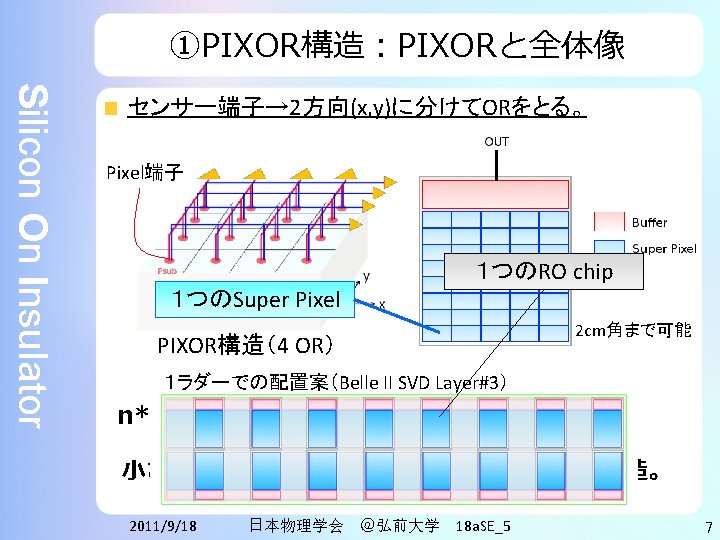

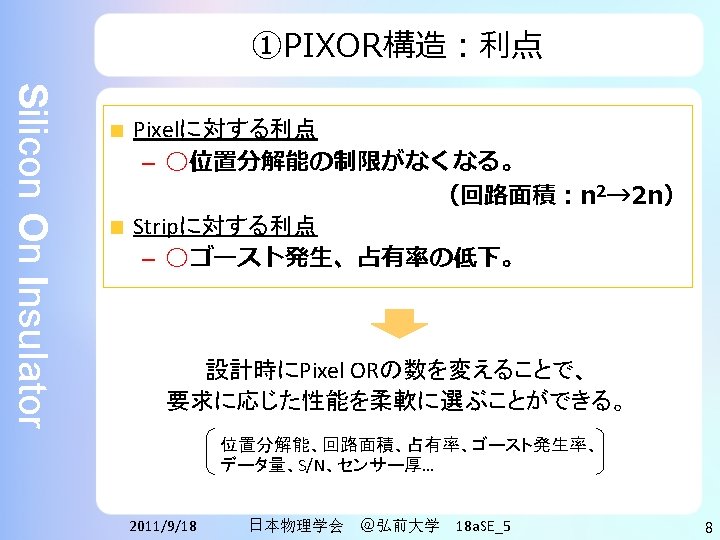

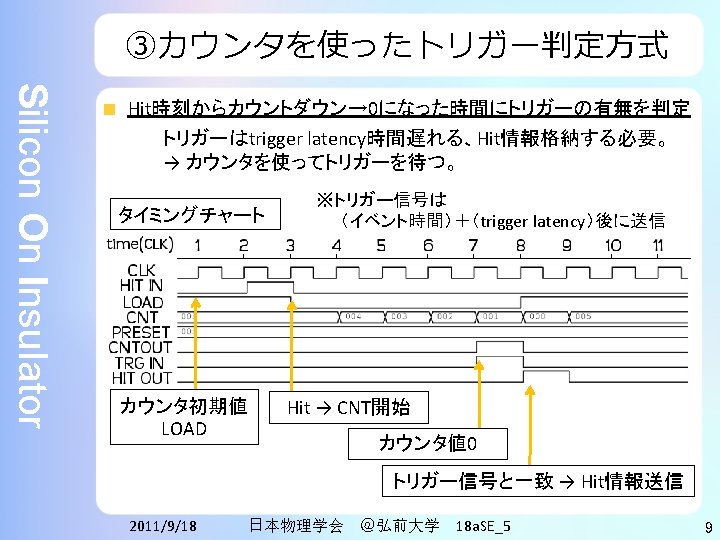

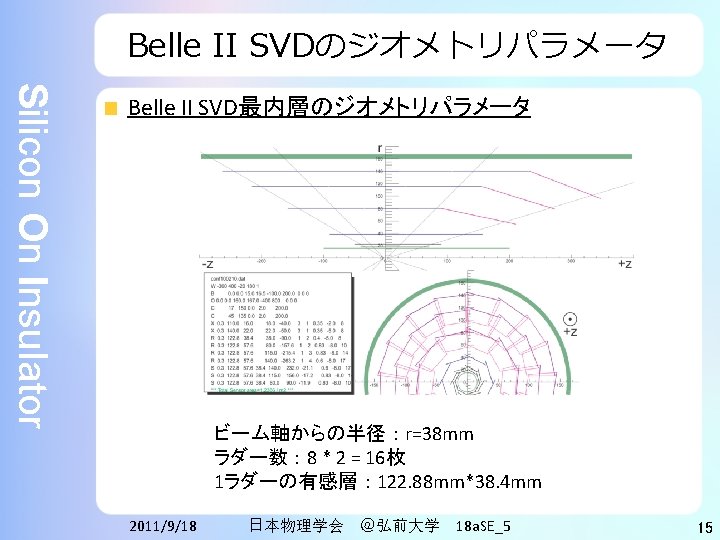

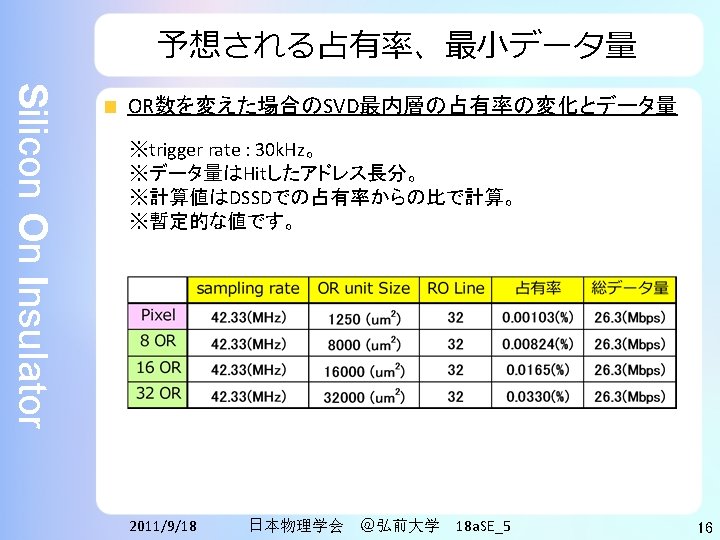

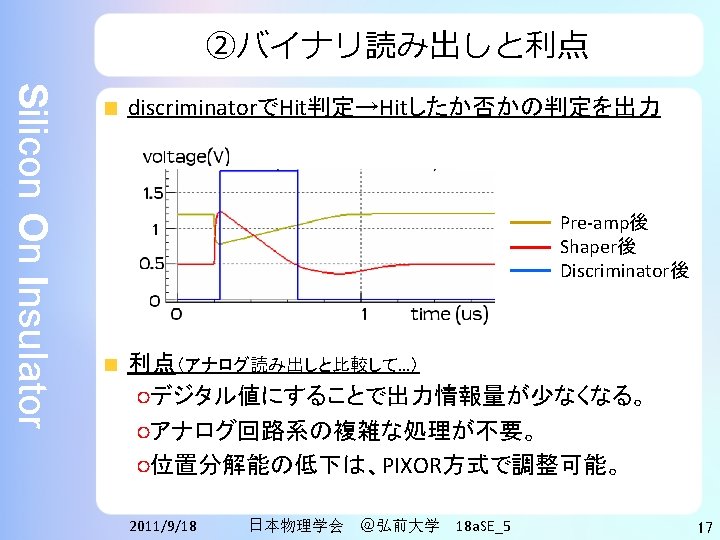

Belle II SVD最内層に向けた開発 Silicon On Insulator 目標:Belle II SVD最内層(Layer#3)に向けて開発。 占有率、ゴースト発生率、物質量などの低下を狙う。 7 Ge. V - PIXOR e. SOI Layer#3 現行案 Layer#3 2011/9/18 SOI PIXOR (SOI Pixel OR) PIXOR pitch : φ25 um、z 40 um sampling rate : 42. 33 MHz 占有率 : < 0. 1 (%) Pixel OR数 : 16 OR センサー厚 : 100 um trigger latency : 5 us 4 Ge. V e+ DSSD (Double-sided Silicon Strip Detector) DSSD pitch : φ50 um、z 160 um sampling rate : 31. 8 MHz 占有率 : 6. 7 (%) センサー厚 : 300 um 日本物理学会 @弘前大学 18 a. SE_5 4

- Slides: 20