Beam Test Results on Deep NWell MAPS Matrix

Beam Test Results on Deep NWell MAPS Matrix S. Bettarini University & INFN, Pisa on behalf of the SLIM 5 Collaboration and the SVT-Super. B group Super. B meeting – Orsay 15 -18 Feb. 2009 1

Outline • Deep NWell Monolithic Active Pixel Sensor design concept • Caracterization of apsel 4 D • Test-beam setup • Alignment procedure /Track fit • Results on DUT= MAPS : – Efficiency vs. threshold – Efficiency inside the pixel cell – (Intrinsic) Resolution • Improvements on the design of the cell • Conclusions 2

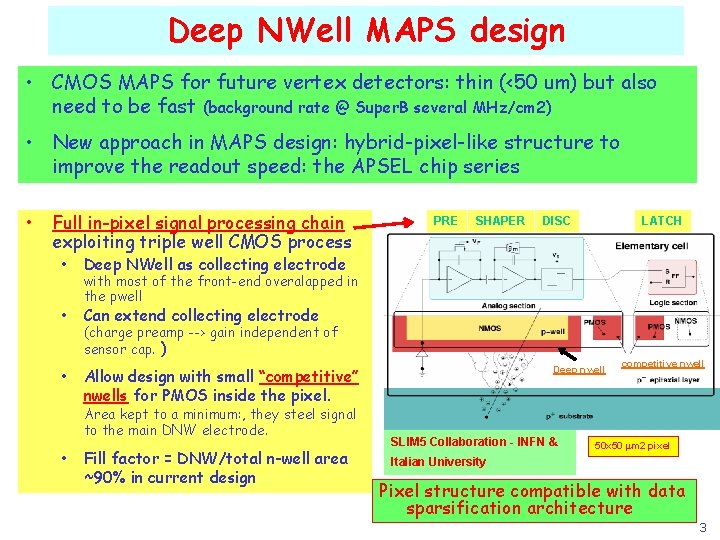

Deep NWell MAPS design • CMOS MAPS for future vertex detectors: thin (<50 um) but also need to be fast (background rate @ Super. B several MHz/cm 2) • New approach in MAPS design: hybrid-pixel-like structure to improve the readout speed: the APSEL chip series • Full in-pixel signal processing chain exploiting triple well CMOS process PRE SHAPER DISC LATCH • Deep NWell as collecting electrode with most of the front-end overalapped in the pwell • Can extend collecting electrode (charge preamp --> gain independent of sensor cap. ) • Allow design with small “competitive” nwells for PMOS inside the pixel. Area kept to a minimum: , they steel signal to the main DNW electrode. • Fill factor = DNW/total n-well area ~90% in current design Deep nwell SLIM 5 Collaboration - INFN & competitive nwell 50 x 50 mm 2 pixel Italian University Pixel structure compatible with data sparsification architecture 3

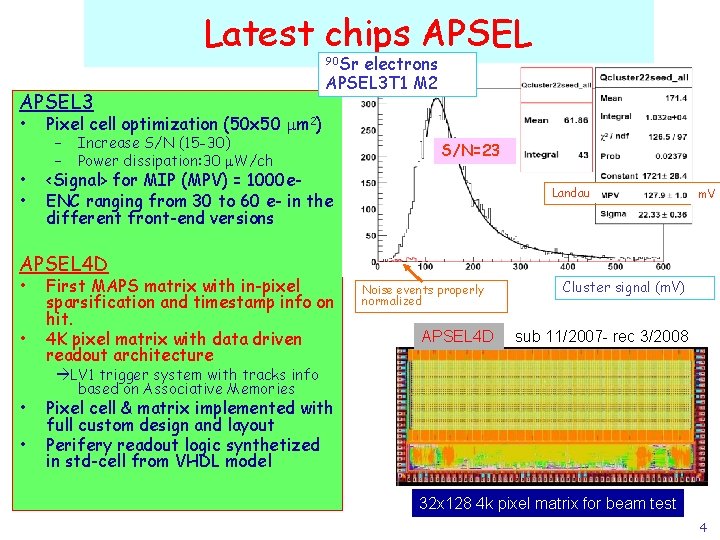

Latest chips APSEL 90 Sr APSEL 3 • • • electrons APSEL 3 T 1 M 2 Pixel cell optimization (50 x 50 mm 2) – – Increase S/N (15 -30) Power dissipation: 30 m. W/ch S/N=23 <Signal> for MIP (MPV) = 1000 e. ENC ranging from 30 to 60 e- in the different front-end versions Landau APSEL 4 D • • First MAPS matrix with in-pixel sparsification and timestamp info on hit. 4 K pixel matrix with data driven readout architecture Noise events properly normalized APSEL 4 D m. V Cluster signal (m. V) sub 11/2007 - rec 3/2008 LV 1 trigger system with tracks info based on Associative Memories Pixel cell & matrix implemented with full custom design and layout Perifery readout logic synthetized in std-cell from VHDL model 32 x 128 4 k pixel matrix for beam test 4

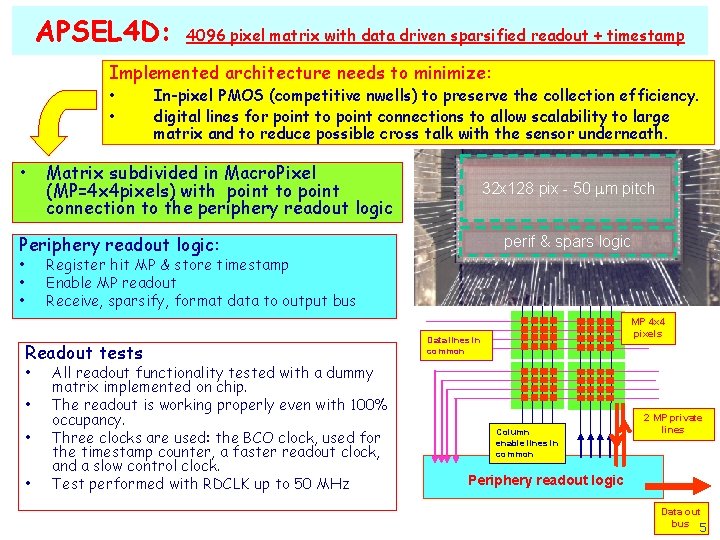

APSEL 4 D: 4096 pixel matrix with data driven sparsified readout + timestamp Implemented architecture needs to minimize: • • • In-pixel PMOS (competitive nwells) to preserve the collection efficiency. digital lines for point to point connections to allow scalability to large matrix and to reduce possible cross talk with the sensor underneath. Matrix subdivided in Macro. Pixel (MP=4 x 4 pixels) with point to point connection to the periphery readout logic 32 x 128 pix - 50 mm pitch Periphery readout logic: • • • perif & spars logic Register hit MP & store timestamp Enable MP readout Receive, sparsify, format data to output bus Readout tests • • All readout functionality tested with a dummy matrix implemented on chip. The readout is working properly even with 100% occupancy. Three clocks are used: the BCO clock, used for the timestamp counter, a faster readout clock, and a slow control clock. Test performed with RDCLK up to 50 MHz MP 4 x 4 pixels Data lines in common Column enable lines in common 2 MP private lines Periphery readout logic Data out bus 5

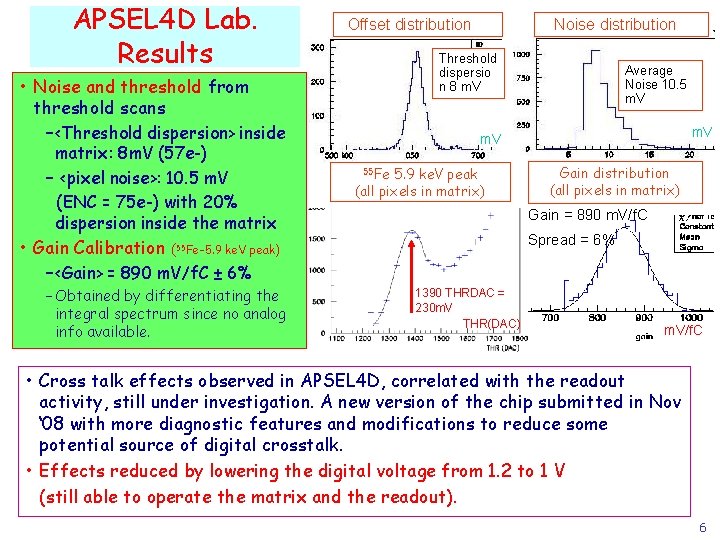

APSEL 4 D Lab. Results Offset distribution Threshold dispersio n 8 m. V • Noise and threshold from threshold scans – <Threshold dispersion> inside matrix: 8 m. V (57 e-) – <pixel noise>: 10. 5 m. V (ENC = 75 e-) with 20% dispersion inside the matrix • Gain Calibration (55 Fe-5. 9 ke. V peak) – <Gain> = 890 m. V/f. C ± 6% – Obtained by differentiating the integral spectrum since no analog info available. Noise distribution Average Noise 10. 5 m. V 55 Fe 5. 9 ke. V peak (all pixels in matrix) Gain distribution (all pixels in matrix) Gain = 890 m. V/f. C Spread = 6% 1390 THRDAC = 230 m. V THR(DAC) m. V/f. C • Cross talk effects observed in APSEL 4 D, correlated with the readout activity, still under investigation. A new version of the chip submitted in Nov ‘ 08 with more diagnostic features and modifications to reduce some potential source of digital crosstalk. • Effects reduced by lowering the digital voltage from 1. 2 to 1 V (still able to operate the matrix and the readout). 6

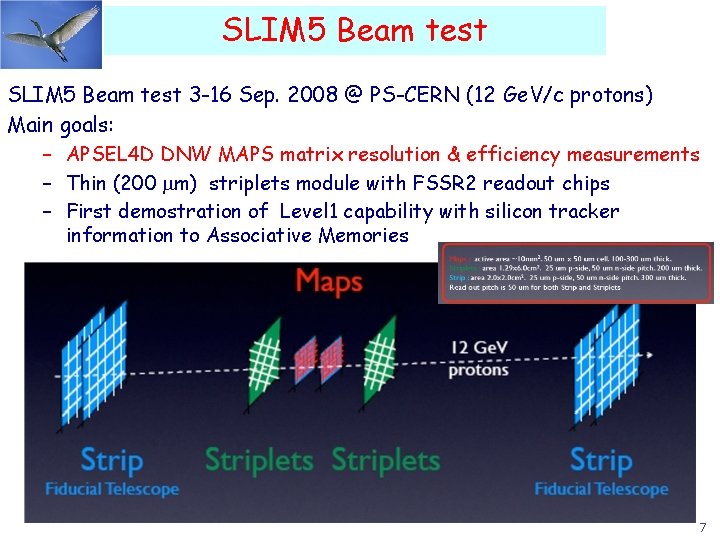

SLIM 5 Beam test 3 -16 Sep. 2008 @ PS-CERN (12 Ge. V/c protons) Main goals: – APSEL 4 D DNW MAPS matrix resolution & efficiency measurements – Thin (200 mm) striplets module with FSSR 2 readout chips – First demostration of Level 1 capability with silicon tracker information to Associative Memories 7

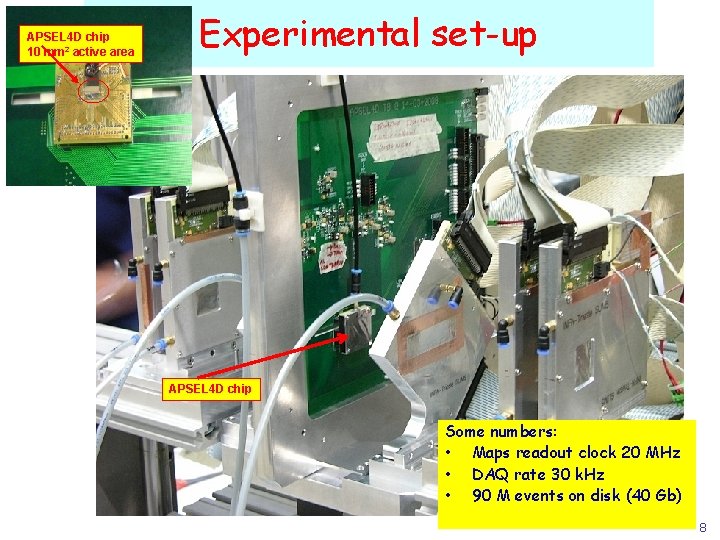

APSEL 4 D chip 10 mm 2 active area Experimental set-up APSEL 4 D chip Some numbers: • Maps readout clock 20 MHz • DAQ rate 30 k. Hz • 90 M events on disk (40 Gb) 8

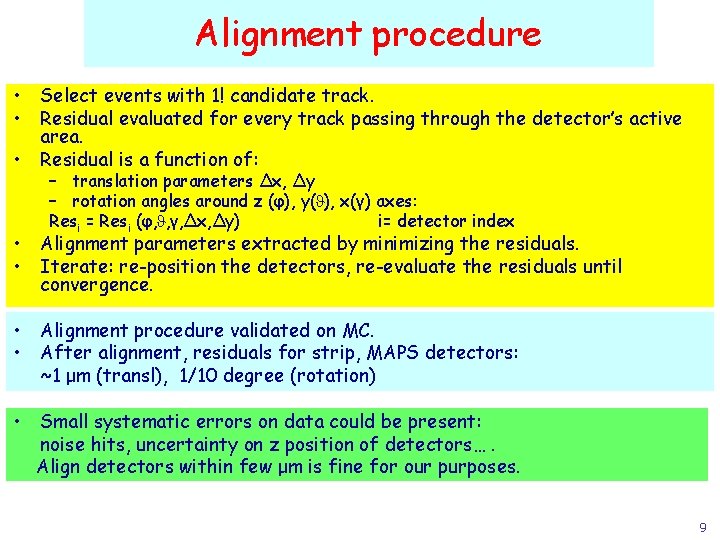

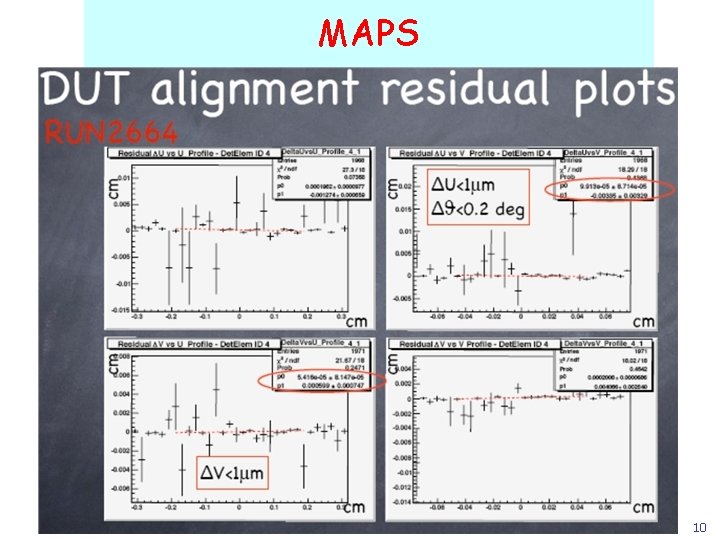

Alignment procedure • Select events with 1! candidate track. • Residual evaluated for every track passing through the detector’s active area. • Residual is a function of: – translation parameters Δx, Δy – rotation angles around z (φ), y(ϑ), x(γ) axes: Resi = Resi (φ, ϑ, γ, Δx, Δy) i= detector index • Alignment parameters extracted by minimizing the residuals. • Iterate: re-position the detectors, re-evaluate the residuals until convergence. • Alignment procedure validated on MC. • After alignment, residuals for strip, MAPS detectors: ~1 μm (transl), 1/10 degree (rotation) • Small systematic errors on data could be present: noise hits, uncertainty on z position of detectors…. Align detectors within few μm is fine for our purposes. 9

MAPS 10

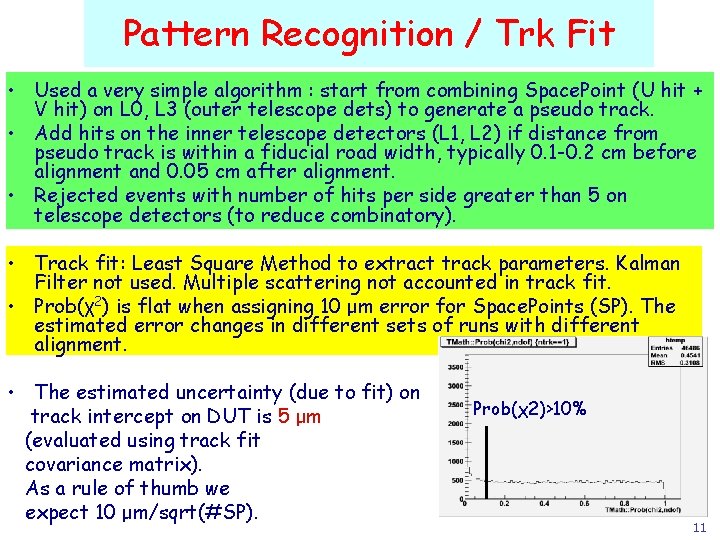

Pattern Recognition / Trk Fit • Used a very simple algorithm : start from combining Space. Point (U hit + V hit) on L 0, L 3 (outer telescope dets) to generate a pseudo track. • Add hits on the inner telescope detectors (L 1, L 2) if distance from pseudo track is within a fiducial road width, typically 0. 1 -0. 2 cm before alignment and 0. 05 cm after alignment. • Rejected events with number of hits per side greater than 5 on telescope detectors (to reduce combinatory). • Track fit: Least Square Method to extract track parameters. Kalman Filter not used. Multiple scattering not accounted in track fit. • Prob(χ2) is flat when assigning 10 μm error for Space. Points (SP). The estimated error changes in different sets of runs with different alignment. • The estimated uncertainty (due to fit) on track intercept on DUT is 5 μm (evaluated using track fit covariance matrix). As a rule of thumb we expect 10 μm/sqrt(#SP). Prob(χ2)>10% 11

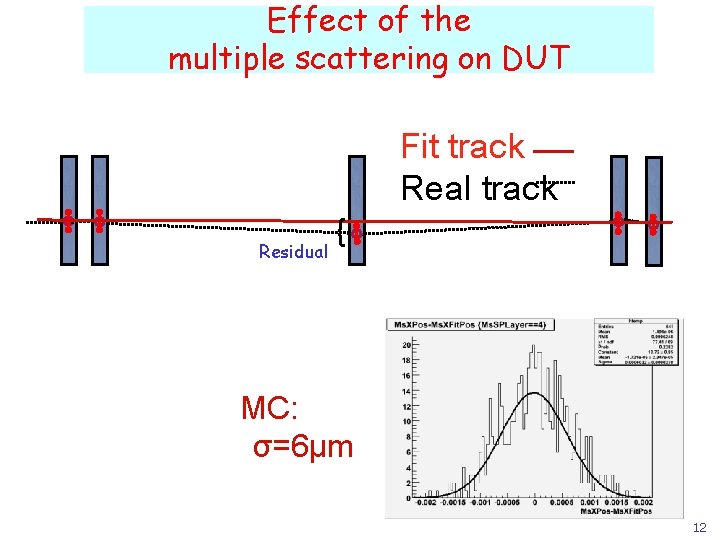

Effect of the multiple scattering on DUT Fit track Real track Residual { MC: σ=6μm 12

MAPS efficiency • Number of tracks intersecting DUT • Number of clusters associated to tracks evaluated by the Residual plots: – Res = Space. Pointmeas- Space. Pointtrk – Fit: Gaussian(signal) + line(noise) – Clusters associated to tracks = Gaussian’s area • Efficiency = #clusters/#tracks 13

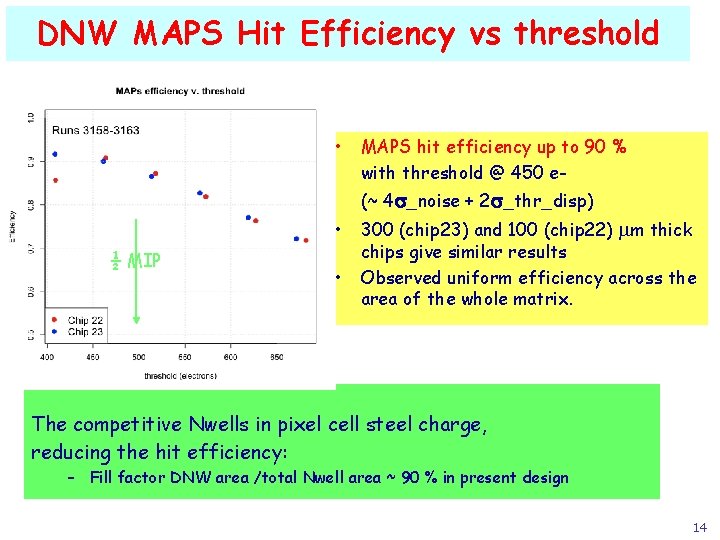

DNW MAPS Hit Efficiency vs threshold • MAPS hit efficiency up to 90 % with threshold @ 450 e(~ 4 s_noise + 2 s_thr_disp) • ½ MIP • 300 (chip 23) and 100 (chip 22) mm thick chips give similar results Observed uniform efficiency across the area of the whole matrix. The competitive Nwells in pixel cell steel charge, reducing the hit efficiency: – Fill factor DNW area /total Nwell area ~ 90 % in present design 14

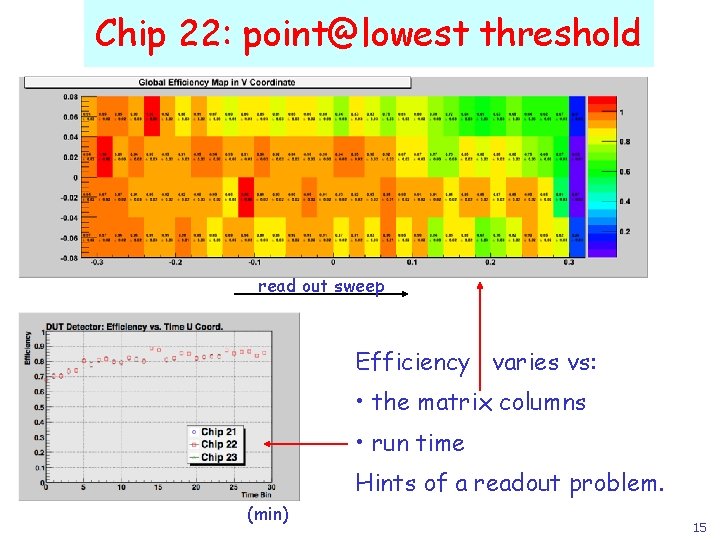

Chip 22: point@lowest threshold read out sweep Efficiency varies vs: • the matrix columns • run time Hints of a readout problem. (min) 15

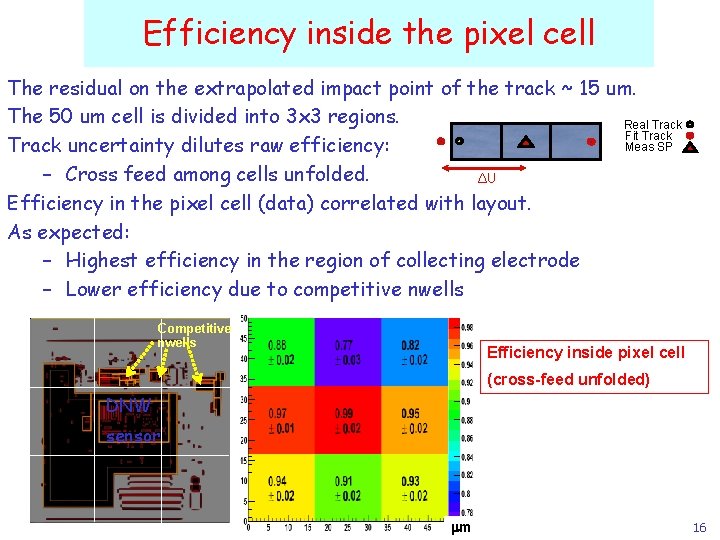

Efficiency inside the pixel cell The residual on the extrapolated impact point of the track ~ 15 um. The 50 um cell is divided into 3 x 3 regions. Real Track Fit Track Meas SP Track uncertainty dilutes raw efficiency: – Cross feed among cells unfolded. ΔU Efficiency in the pixel cell (data) correlated with layout. As expected: – Highest efficiency in the region of collecting electrode – Lower efficiency due to competitive nwells Competitive nwells Efficiency inside pixel cell (cross-feed unfolded) DNW sensor mm 16

Mij is evaluated by a toy MC (input: residual). 17

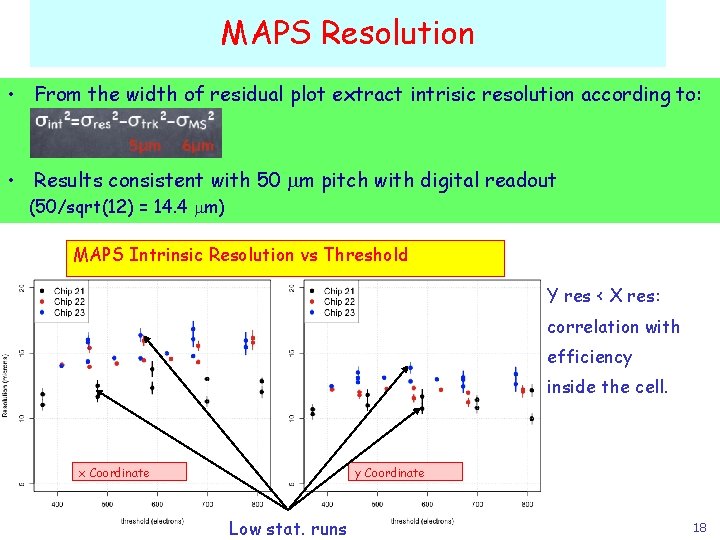

MAPS Resolution • From the width of residual plot extract intrisic resolution according to: • Results consistent with 50 mm pitch with digital readout (50/sqrt(12) = 14. 4 mm) MAPS Intrinsic Resolution vs Threshold Y res < X res: correlation with efficiency inside the cell. x Coordinate y Coordinate Low stat. runs 18

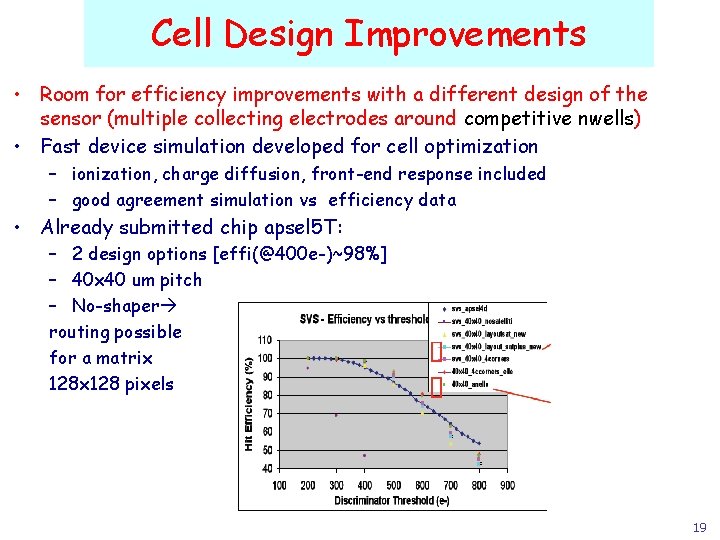

Cell Design Improvements • Room for efficiency improvements with a different design of the sensor (multiple collecting electrodes around competitive nwells) • Fast device simulation developed for cell optimization – ionization, charge diffusion, front-end response included – good agreement simulation vs efficiency data • Already submitted chip apsel 5 T: – 2 design options [effi(@400 e-)~98%] – 40 x 40 um pitch – No-shaper routing possible for a matrix 128 pixels 19

Conclusions • A first MAPS matrix with in-pixel sparsification and timestamp information for hits fully characterized and tested with beams with very encouraging results: – Threshold dispersion across matrix ~ 60 e– Pixel Noise ENC = 75 e– Hit efficiency up to 92% (sensor design not optimized yet!) with good uniformity across the matrix. – Intrisinc resolution ~ 14 mm compatible with 50 mm pitch and digital readout. • Already submitted a new chip with improved cell design. Ready to be tested with beam next summer. 20

SLIM 5 -Silicon detectors with Low Interactions with Material G. Batignani 1, 2, S. Bettarini 1, 2, F. Bosi 1, 2, G. Calderini 1, 2, , R. Cenci 1, 2, A. Cervelli 1, 2, F. Crescioli 1, 2, M. Dell’Orso 1, 2, F. Forti 1, 2, P. Giannetti 1, 2 , M. A. Giorgi 1, 2, A. Lusiani 2, 3, G. Marchiori 1, 2, M. Massa 1, 2, F. Morsani 1, 2, N. Neri 1, 2, E. Paoloni 1, 2, M. Piendibene 1, 2, G. Rizzo 1, 2 , L. Sartori 1, 2, J. Walsh 2 C. Andreoli 4, 5, E. Pozzati 4, 5, L. Ratti 4, 5, V. Speziali 4, 5, M. Manghisoni 5, 6, V. Re 5, 6, G. Traversi 5, 6, L. Gaioni 4, 5 M. Bomben 7, L. Bosisio 7, P. Cristaudo 7, G. Giacomini 7, L. Lanceri 7, I. Rachevskaia 7, L. Vitale 7, M. Bruschi 8, R. Di Sipio 8, B. Giacobbe 8, A. Gabrielli 8, F. Giorgi 8, C. Sbarra 8, N. Semprini 8, R. Spighi 8, S. Valentinetti 8, M. Villa 8, A. Zoccoli 8, D. Gamba 9, G. Giraudo 9, P. Mereu 9, G. F. Dalla Betta 10 , G. Soncini 10 , G. Fontana 10 , L. Pancheri 10 , G. Verzellesi 11 1 Università degli Studi di Pisa, 2 INFN Pisa, 3 Scuola Normale Superiore di Pisa, 4 Università degli Studi di Pavia, 5 INFN Pavia, 6 Università degli Studi di Bergamo, 7 INFN Trieste and Università degli Studi di Trieste 8 INFN Bologna and Università degli Studi di Bologna 9 INFN Torino and Università degli Studi di Torino 10 Università degli Studi di Trento and INFN Padova 11 Università degli Studi di Modena e Reggio Emilia and INFN Padova 21

- Slides: 21