Beam Secondary Shower Acquisition System Dynamic range coverage

Beam Secondary Shower Acquisition System: Dynamic range coverage and initial designs Student Meeting Jose Luis Sirvent Ph. D. Student 12/08/2013

1. Previously on Jose’s Ph. D… • 4 Studies carried out for the moment (With 3 reports available): – p. CVD Signal estimations from Wire Scanners • • http: //issues. cern. ch/browse/BIWS-419 Dynamic range first approximations for SPS – – • Dynamic range first approximations for LHC – – • SPS max Charge per bunch (All BWS)_Totem: 120 p. C SPS max Charge per bucnh (Prototype Location 51740)_Nominal: 60 p. C LHC max Charge per bunch E=2 e-6 m B=123 m @ 7 Te. V (Beam_Sigma=181 um)_Nominal: 226 p. C LHC max Charge per bunch E=2 e-6 m B=123 m @ 450 Ge. V (Beam_Sigma=716 um)_Nominal: 32 p. C Proposal of Dynamic range: 2 f. C (~MIP) to 400 p. C (~2*Qmax) – Impact of Long Cables (250 m of CK 50) in the p. CVD Signal (Report) • • • http: //issues. cern. ch/browse/BIWS-422 250 m Cable Bandwidth: ~ 10 MHz (To avoid 25 ns pulse overlapping needed > 40 MHz) Amplitude loss of 5 d. B Observed offset due pulse overlapping 5% Settling time ~ 66 ns (first 3 bunches) – BWS Scan Simulation Though Long CK 50 Cables (Report) • • • http: //issues. cern. ch/browse/BIWS-424 p. CVD Signal generation from BWS and Beam characteristics (Script) Matlab processing and simulation of cable as an approximate filter (Script) Sigma measurement not affected by cable Very low temporal resolution at bunch level (too long decays) Not constant offset. This is good, bad…? – CK 50 Cable Measurements in the SPS for BWS Prototype location (Report) New! • • • http: //issues. cern. ch/browse/BIWS-437 Pspice Model and analytical expressions validated! Extraction of a reliable Matlab model for CK 50 and other coaxial cables, also validated with real data. Noise study of 176 m of CK 50, frequency, temporal and amplitude distribution. Pulse distortion study

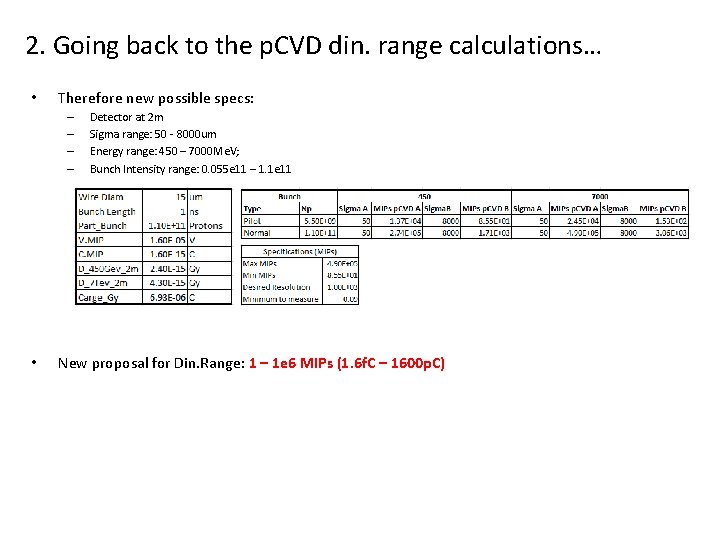

2. Going back to the p. CVD din. range calculations… – p. CVD Signal estimations from Wire Scanners • • • http: //issues. cern. ch/browse/BIWS-419 Dynamic range first approximations for SPS – SPS max Charge per bunch (All BWS)_Totem: 120 p. C ( ~7. 5 e 4 MIP) – SPS max Charge per bucnh (Prototype Location 51740)_Nominal: 60 p. C ( ~3. 7 e 4 MIP) Dynamic range first approximations for LHC – LHC max Charge per bunch E=2 e-6 m B=123 m @ 7 Te. V (Beam_Sigma=181 um)_Nominal: 226 p. C (1. 5 e 5 MIP) – LHC max Charge per bunch E=2 e-6 m B=123 m @ 450 Ge. V (Beam_Sigma=716 um)_Nominal: 32 p. C (2 e 4 MIP) 1 st Proposal of Dynamic range: 1. 6 f. C (~MIP) to 400 p. C (2. 5 e 5 MIPS) (Study from Accelerator Specs and Existing BWS locacions) – We can also simplify estimations by using some “User-Based experience” (Thanks Ana!): PSB: • “The min in PSB is ~1 mm, the max, I do not know for sure but up to now I've found ~7 mm”: Sigma 1 -7 mm PS: • “The smallest sizes measured are in the order of 1 mm too. But the largest I think is around 12 mm! (TOF inj) ”: Sigma 112 mm SPS: • “ I don't think there is a measurement under 0. 2 mm”: Sigma 0. 2 -4 mm LJHC: • “Current sizes should be a good estimation: Sigma 0. 1 – 1. 5 mm • B 1 -> By=287. 81 m, Bx=165. 48 m, Dy=0. 1032, Dx=-0. 0857 m B 2 -> By=404. 55 m, Bx=123. 51 m, Dy=-0. 2180, Dx=0. 1168 m

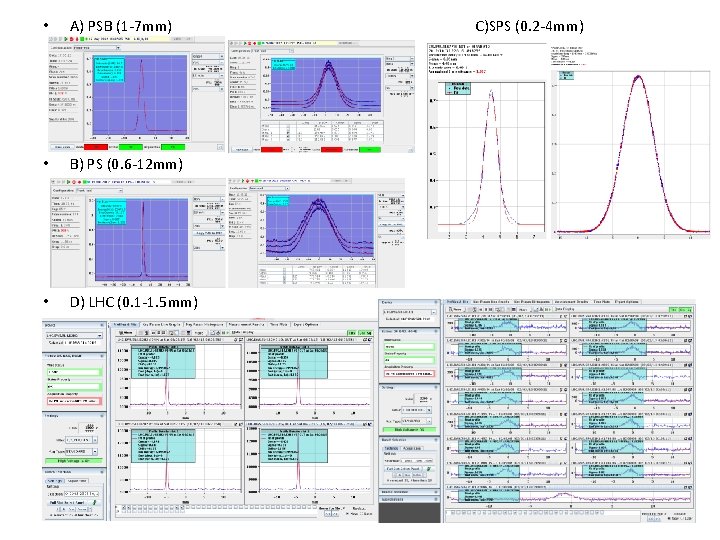

• A) PSB (1 -7 mm) • B) PS (0. 6 -12 mm) • D) LHC (0. 1 -1. 5 mm) C)SPS (0. 2 -4 mm)

2. Going back to the p. CVD din. range calculations… • Therefore new possible specs: – – • Detector at 2 m Sigma range: 50 - 8000 um Energy range: 450 – 7000 Me. V; Bunch Intensity range: 0. 055 e 11 – 1. 1 e 11 New proposal for Din. Range: 1 – 1 e 6 MIPs (1. 6 f. C – 1600 p. C)

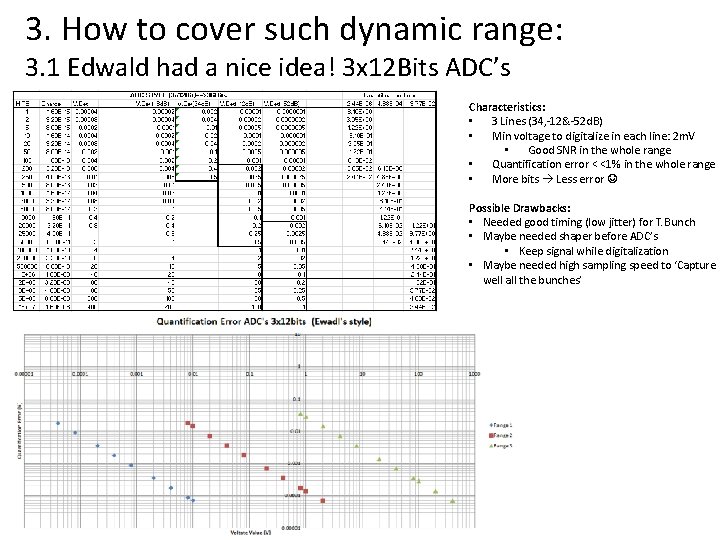

3. How to cover such dynamic range: 3. 1 Edwald had a nice idea! 3 x 12 Bits ADC’s Characteristics: • 3 Lines (34, -12&-52 d. B) • Min voltage to digitalize in each line: 2 m. V • Good SNR in the whole range • Quantification error < <1% in the whole range • More bits Less error Possible Drawbacks: • Needed good timing (low jitter) for T. Bunch • Maybe needed shaper before ADC’s • Keep signal while digitalization • Maybe needed high sampling speed to ‘Capture well all the bunches’

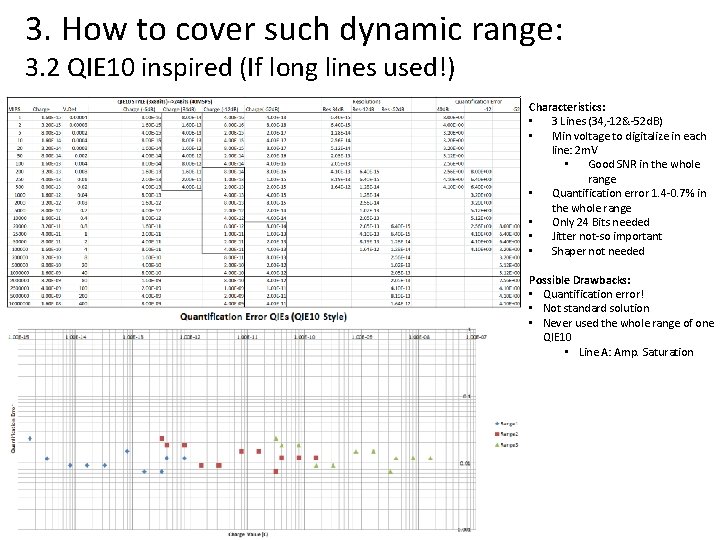

3. How to cover such dynamic range: 3. 2 QIE 10 inspired (If long lines used!) Characteristics: • 3 Lines (34, -12&-52 d. B) • Min voltage to digitalize in each line: 2 m. V • Good SNR in the whole range • Quantification error 1. 4 -0. 7% in the whole range • Only 24 Bits needed • Jitter not-so important • Shaper not needed Possible Drawbacks: • Quantification error! • Not standard solution • Never used the whole range of one QIE 10 • Line A: Amp. Saturation

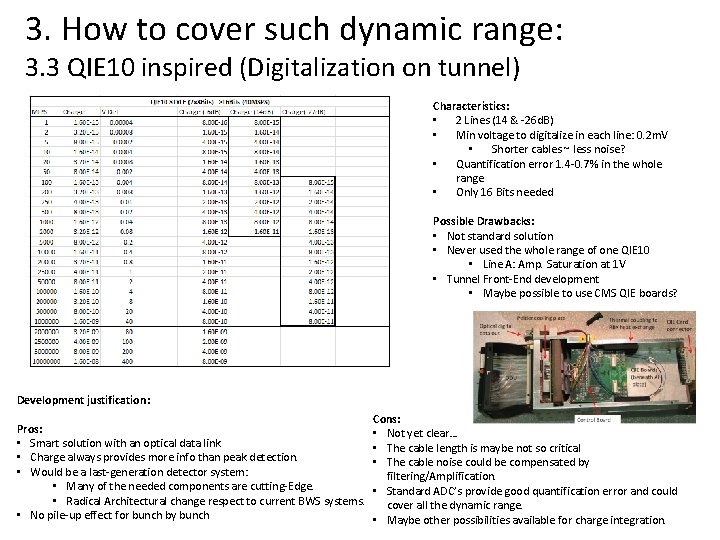

3. How to cover such dynamic range: 3. 3 QIE 10 inspired (Digitalization on tunnel) Characteristics: • 2 Lines (14 & -26 d. B) • Min voltage to digitalize in each line: 0. 2 m. V • Shorter cables ~ less noise? • Quantification error 1. 4 -0. 7% in the whole range • Only 16 Bits needed Possible Drawbacks: • Not standard solution • Never used the whole range of one QIE 10 • Line A: Amp. Saturation at 1 V • Tunnel Front-End development • Maybe possible to use CMS QIE boards? Development justification: Pros: • Smart solution with an optical data link • Charge always provides more info than peak detection. • Would be a last-generation detector system: • Many of the needed components are cutting-Edge. • Radical Architectural change respect to current BWS systems. • No pile-up effect for bunch by bunch Cons: • Not yet clear… • The cable length is maybe not so critical • The cable noise could be compensated by filtering/Amplification. • Standard ADC’s provide good quantification error and could cover all the dynamic range. • Maybe other possibilities available for charge integration.

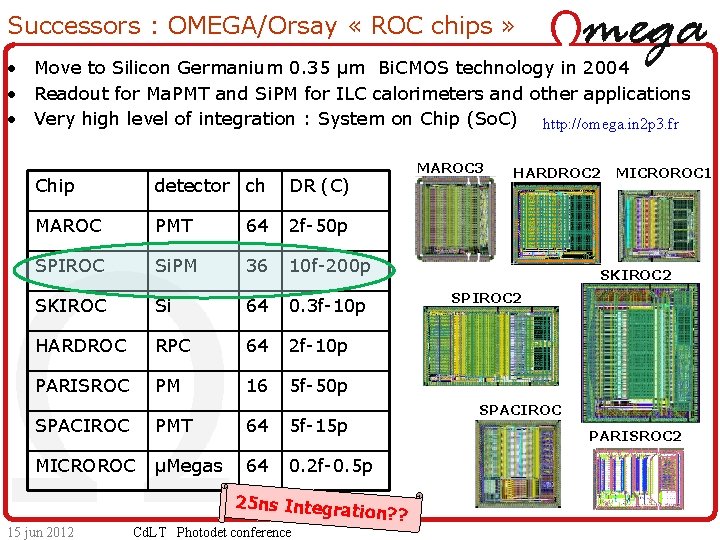

Successors : OMEGA/Orsay « ROC chips » • Move to Silicon Germanium 0. 35 µm Bi. CMOS technology in 2004 • Readout for Ma. PMT and Si. PM for ILC calorimeters and other applications • Very high level of integration : System on Chip (So. C) http: //omega. in 2 p 3. fr MAROC 3 Chip detector ch DR (C) MAROC PMT 64 2 f-50 p SPIROC Si. PM 36 10 f-200 p SKIROC Si 64 0. 3 f-10 p HARDROC RPC 64 2 f-10 p PARISROC PM 16 5 f-50 p PMT 64 5 f-15 p MICROROC µMegas 64 0. 2 f-0. 5 p SKIROC 2 SPIROC 2 PARISROC 2 25 ns Integra tion? ? Cd. LT Photodet conference MICROROC 1 SPACIROC 15 jun 2012 HARDROC 2

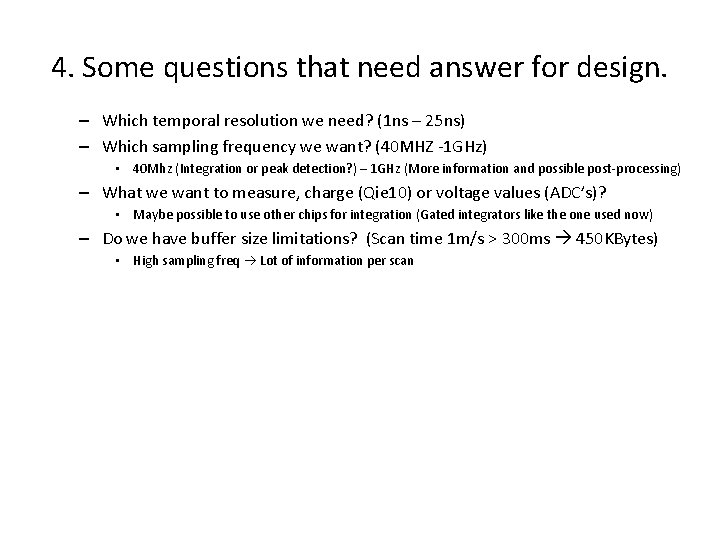

4. Some questions that need answer for design. – Which temporal resolution we need? (1 ns – 25 ns) – Which sampling frequency we want? (40 MHZ -1 GHz) • 40 Mhz (Integration or peak detection? ) – 1 GHz (More information and possible post-processing) – What we want to measure, charge (Qie 10) or voltage values (ADC’s)? • Maybe possible to use other chips for integration (Gated integrators like the one used now) – Do we have buffer size limitations? (Scan time 1 m/s > 300 ms 450 KBytes) • High sampling freq Lot of information per scan

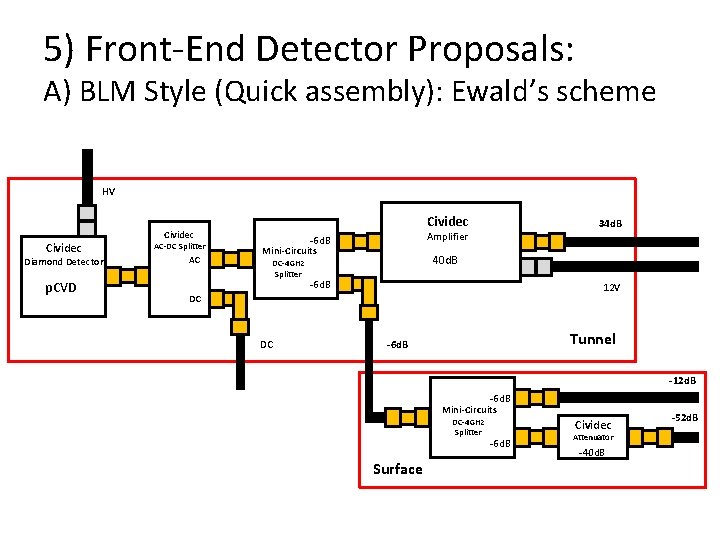

5) Front-End Detector Proposals: A) BLM Style (Quick assembly): Ewald’s scheme HV Cividec Diamond Detector p. CVD Cividec AC-DC Splitter AC Cividec -6 d. B Mini-Circuits DC-4 GHz Splitter 34 d. B Amplifier 40 d. B -6 d. B 12 V DC DC Tunnel -6 d. B -12 d. B -6 d. B Mini-Circuits DC-4 GHz Splitter Surface Cividec -6 d. B Attenuator -40 d. B -52 d. B

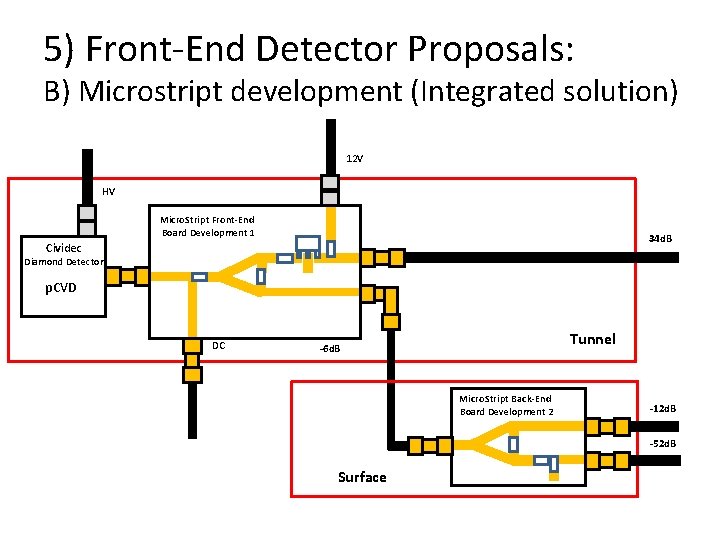

5) Front-End Detector Proposals: B) Microstript development (Integrated solution) 12 V HV Micro. Stript Front-End Board Development 1 34 d. B Cividec Diamond Detector p. CVD DC Tunnel -6 d. B Micro. Stript Back-End Board Development 2 -6 d. B -12 d. B -52 d. B Surface

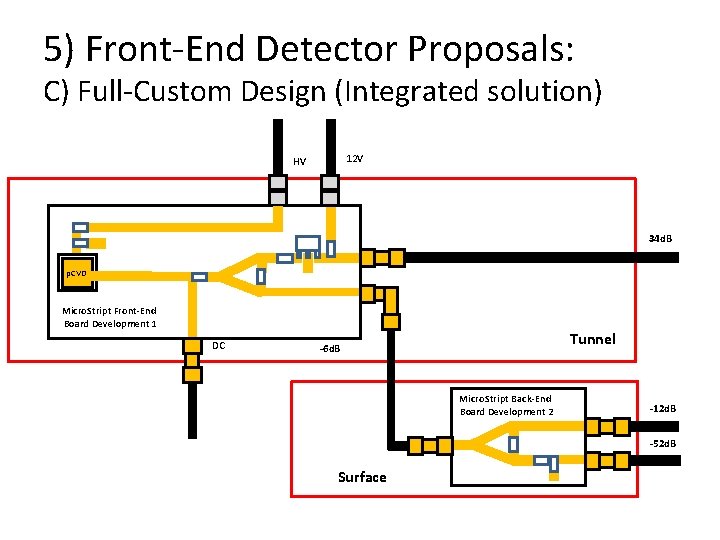

5) Front-End Detector Proposals: C) Full-Custom Design (Integrated solution) 12 V HV 34 d. B p. CVD Micro. Stript Front-End Board Development 1 DC Tunnel -6 d. B Micro. Stript Back-End Board Development 2 -6 d. B -12 d. B -52 d. B Surface

6) Development of a GUI • Reasons: – Complete Wire Scan simulation from Beam, cable, amplification and acquisition properties. – Evaluation of Digitalization Schemes (ADC VS QIE) – Study of impact of the long cable in sigma determination. – Extraction of Bb. B profiles. Quantification of error. – Study of coverage of Din. Range with different lines. – Include noise sources (not yet done)

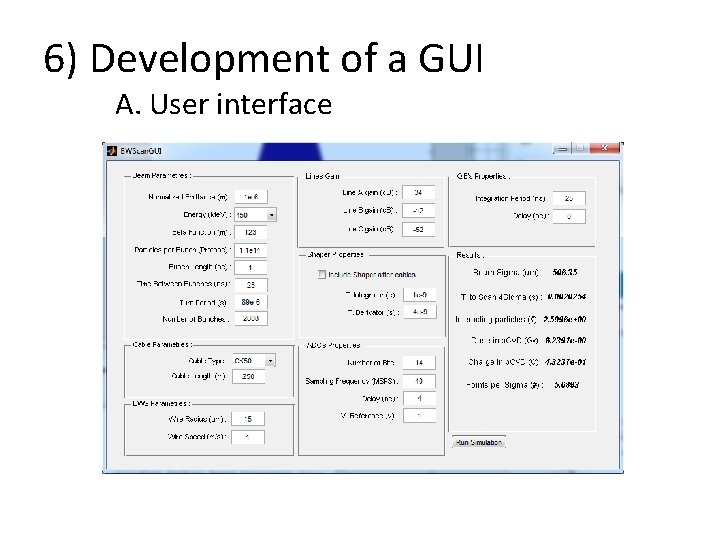

6) Development of a GUI A. User interface

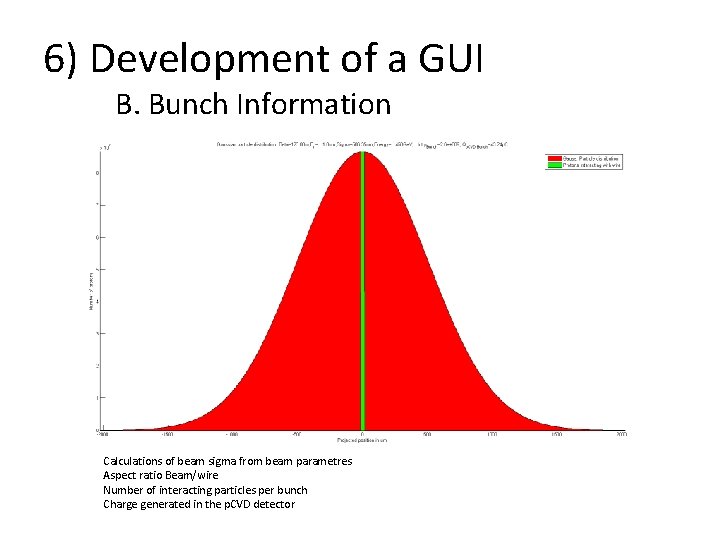

6) Development of a GUI B. Bunch Information Calculations of beam sigma from beam parametres Aspect ratio Beam/wire Number of interacting particles per bunch Charge generated in the p. CVD detector

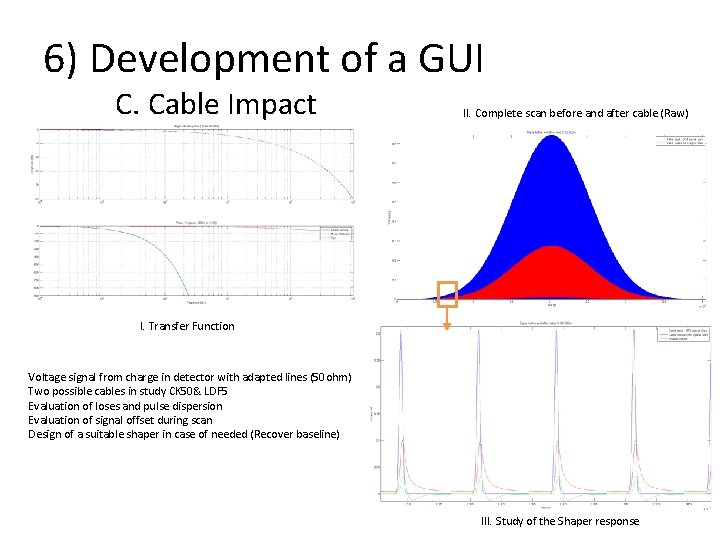

6) Development of a GUI C. Cable Impact II. Complete scan before and after cable (Raw) I. Transfer Function Voltage signal from charge in detector with adapted lines (50 ohm) Two possible cables in study CK 50& LDF 5 Evaluation of loses and pulse dispersion Evaluation of signal offset during scan Design of a suitable shaper in case of needed (Recover baseline) III. Study of the Shaper response

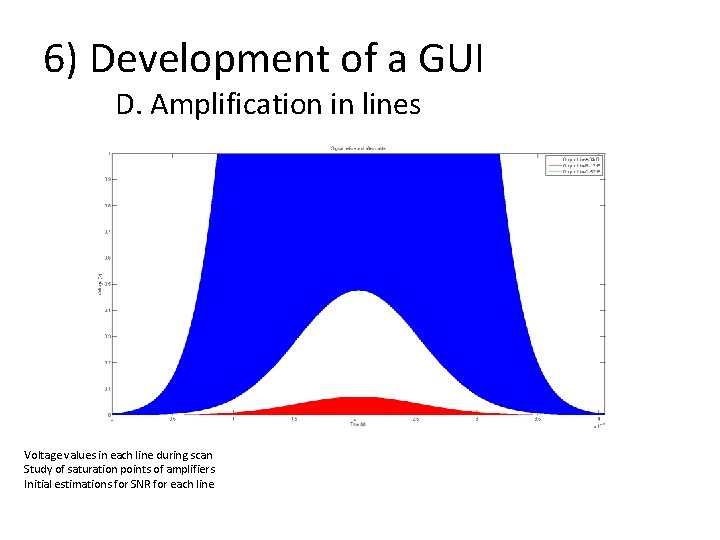

6) Development of a GUI D. Amplification in lines Voltage values in each line during scan Study of saturation points of amplifiers Initial estimations for SNR for each line

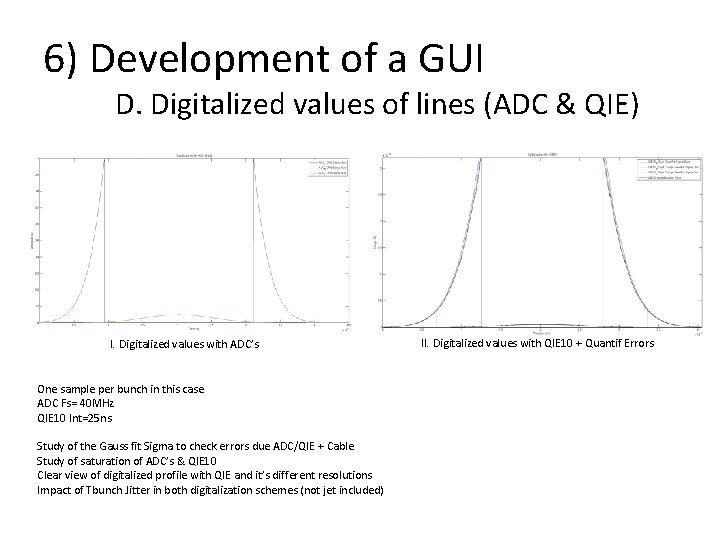

6) Development of a GUI D. Digitalized values of lines (ADC & QIE) I. Digitalized values with ADC’s One sample per bunch in this case ADC Fs= 40 MHz QIE 10 Int=25 ns Study of the Gauss fit Sigma to check errors due ADC/QIE + Cable Study of saturation of ADC’s & QIE 10 Clear view of digitalized profile with QIE and it’s different resolutions Impact of Tbunch Jitter in both digitalization schemes (not jet included) II. Digitalized values with QIE 10 + Quantif Errors

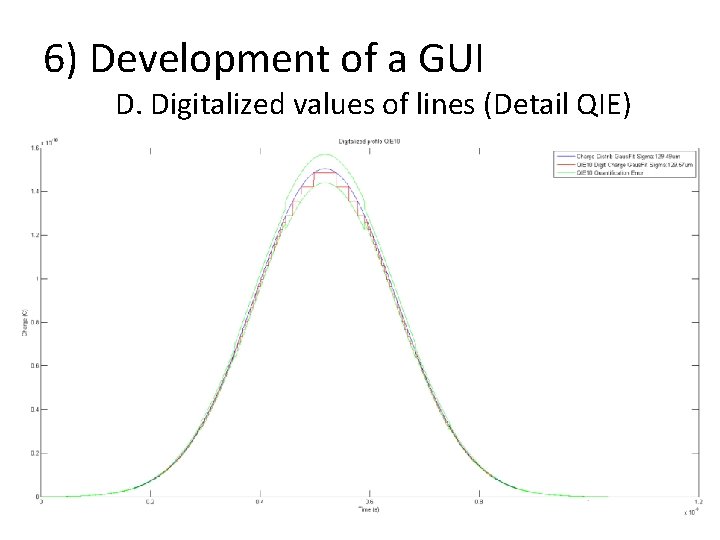

6) Development of a GUI D. Digitalized values of lines (Detail QIE)

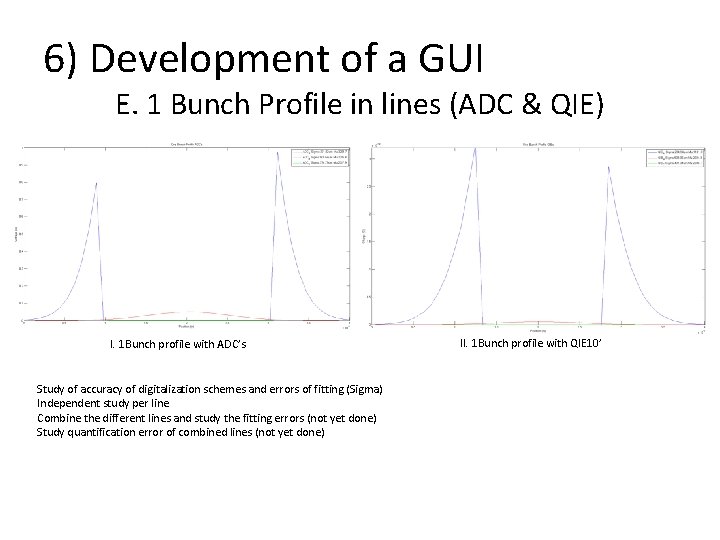

6) Development of a GUI E. 1 Bunch Profile in lines (ADC & QIE) I. 1 Bunch profile with ADC’s Study of accuracy of digitalization schemes and errors of fitting (Sigma) Independent study per line Combine the different lines and study the fitting errors (not yet done) Study quantification error of combined lines (not yet done) II. 1 Bunch profile with QIE 10’

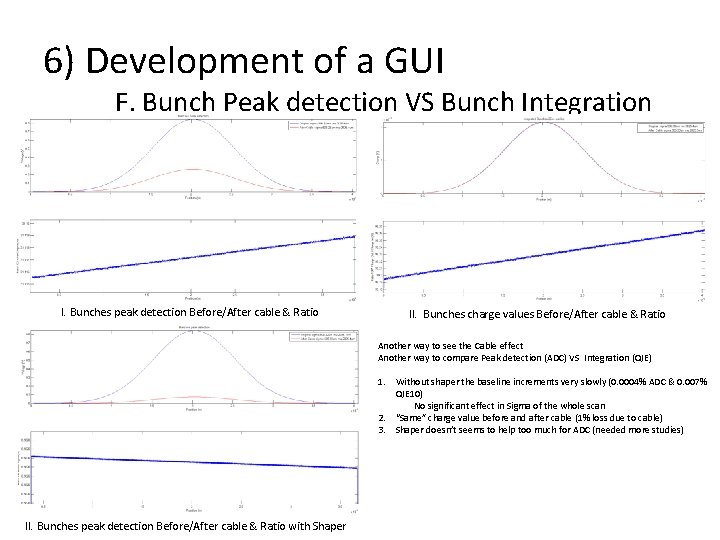

6) Development of a GUI F. Bunch Peak detection VS Bunch Integration I. Bunches peak detection Before/After cable & Ratio II. Bunches charge values Before/After cable & Ratio Another way to see the Cable effect Another way to compare Peak detection (ADC) VS Integration (QIE) 1. Without shaper the baseline increments very slowly (0. 0004% ADC & 0. 007% QIE 10) No significant effect in Sigma of the whole scan 2. “Same” charge value before and after cable (1% loss due to cable) 3. Shaper doesn’t seems to help too much for ADC (needed more studies) II. Bunches peak detection Before/After cable & Ratio with Shaper

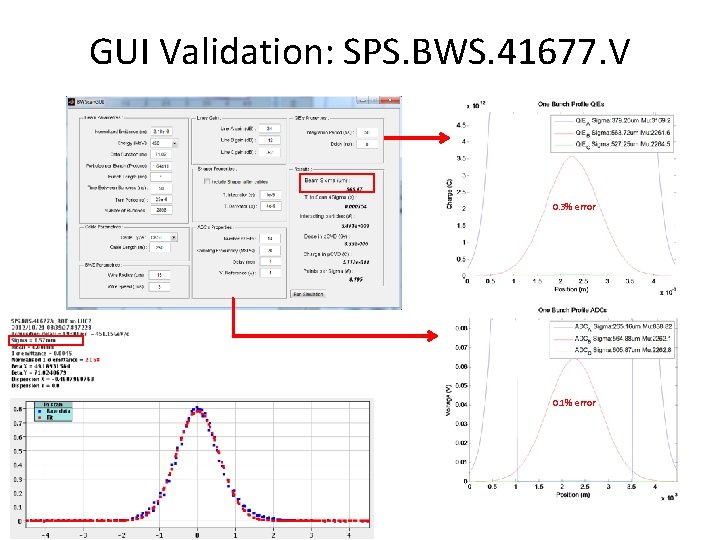

GUI Validation: SPS. BWS. 41677. V 0. 3% error 0. 1% error

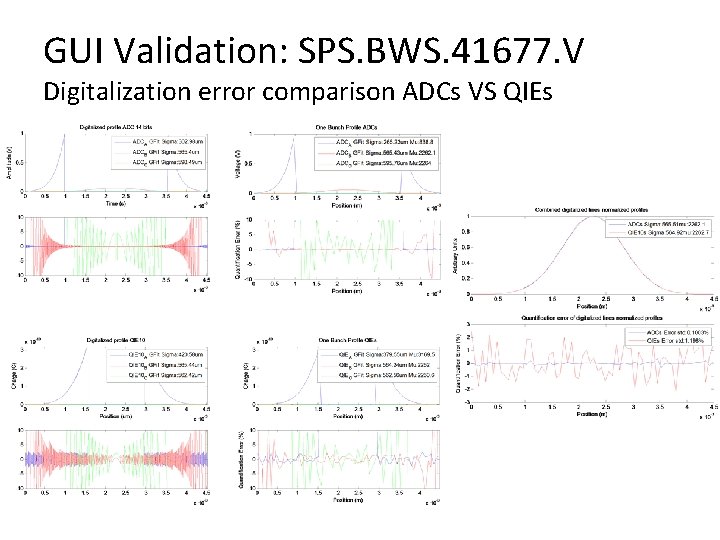

GUI Validation: SPS. BWS. 41677. V Digitalization error comparison ADCs VS QIEs

GUI Validation: SPS. BWS. 41677. V 50 ns Spacing 20 MHz ADC

GUI Validation: SPS. BWS. 41677. V 50 ns Spacing 50 ns int QIE

- Slides: 26