Basics of IC design Miroslav Havrnek 3 rd

Basics of IC design Miroslav Havránek 3 rd June 2013, TALENT Summer School, CERN

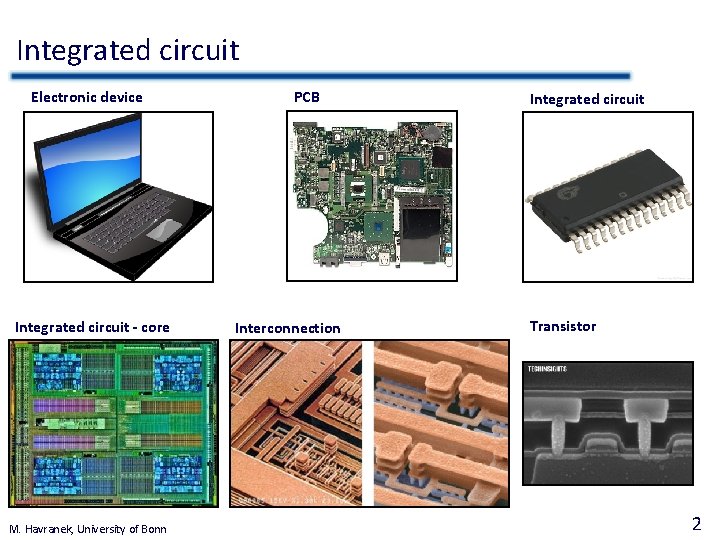

Integrated circuit Electronic device Integrated circuit - core M. Havranek, University of Bonn PCB Interconnection Integrated circuit Transistor 2

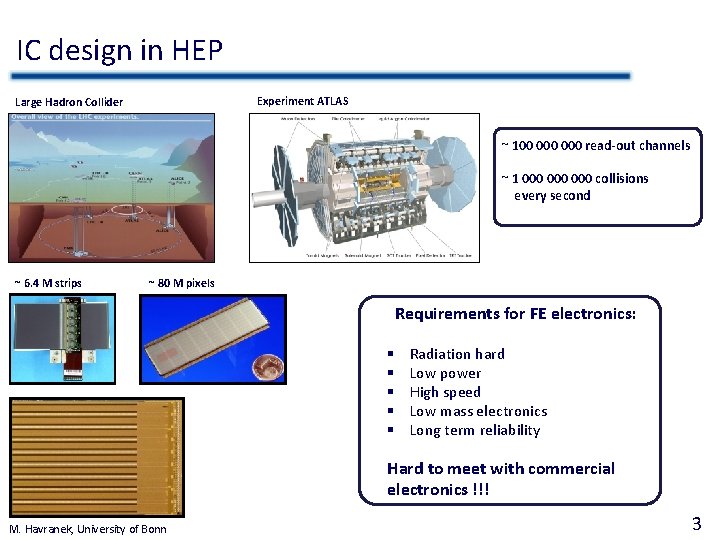

IC design in HEP Experiment ATLAS Large Hadron Collider ~ 100 000 read-out channels ~ 1 000 000 collisions every second ~ 6. 4 M strips ~ 80 M pixels Requirements for FE electronics: § § § Radiation hard Low power High speed Low mass electronics Long term reliability Hard to meet with commercial electronics !!! M. Havranek, University of Bonn 3

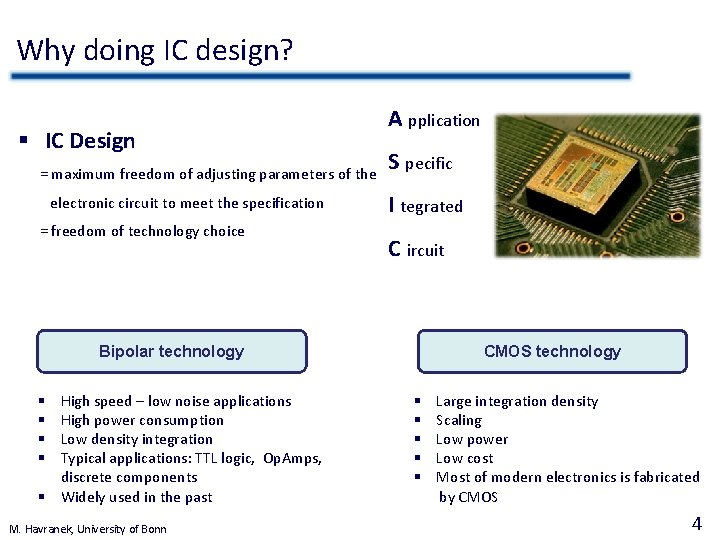

Why doing IC design? § IC Design = maximum freedom of adjusting parameters of the electronic circuit to meet the specification = freedom of technology choice A pplication S pecific I tegrated C ircuit Bipolar technology High speed – low noise applications High power consumption Low density integration Typical applications: TTL logic, Op. Amps, discrete components § Widely used in the past § § M. Havranek, University of Bonn CMOS technology § § § Large integration density Scaling Low power Low cost Most of modern electronics is fabricated by CMOS 4

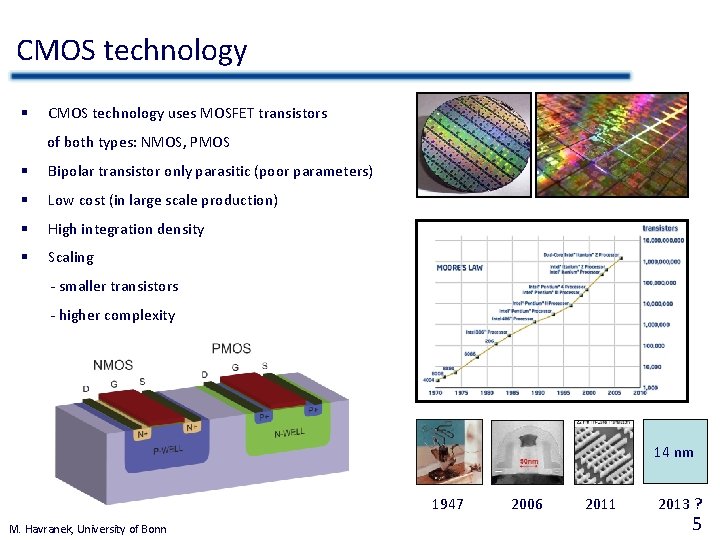

CMOS technology § CMOS technology uses MOSFET transistors of both types: NMOS, PMOS § Bipolar transistor only parasitic (poor parameters) § Low cost (in large scale production) § High integration density § Scaling - smaller transistors - higher complexity - higher power density 14 nm 1947 M. Havranek, University of Bonn 2006 2011 2013 ? 5

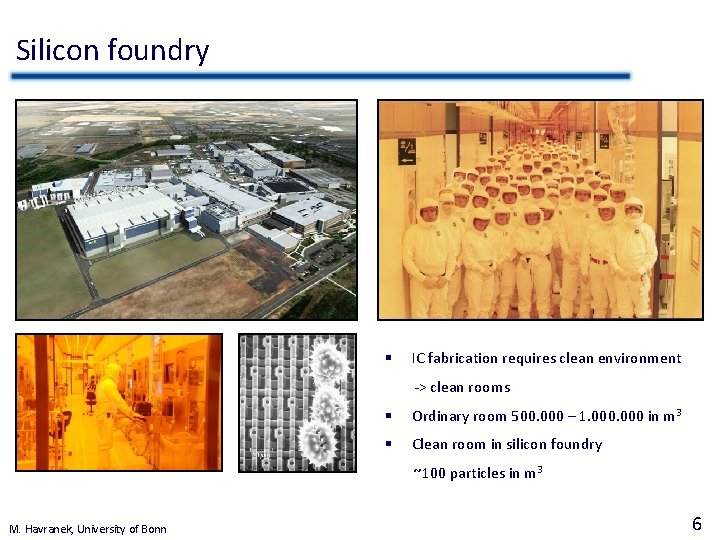

Silicon foundry § IC fabrication requires clean environment -> clean rooms § Ordinary room 500. 000 – 1. 000 in m 3 § Clean room in silicon foundry ~100 particles in m 3 M. Havranek, University of Bonn 6

Electronic components in CMOS technology § Active components - MOSFET transistors - parasitic bipolar transistors (poor parameters) CMOS technology is optimized for fabrication of NMOS and PMOS transistors, passive components have limited performance (precision, linearity) § Passive components - resistors - capacitors - inductors (used in RF application) - diodes Hard to integrate large capacitors (> 10 p. F) and large resistors (> 50 kΩ) M. Havranek, University of Bonn 7

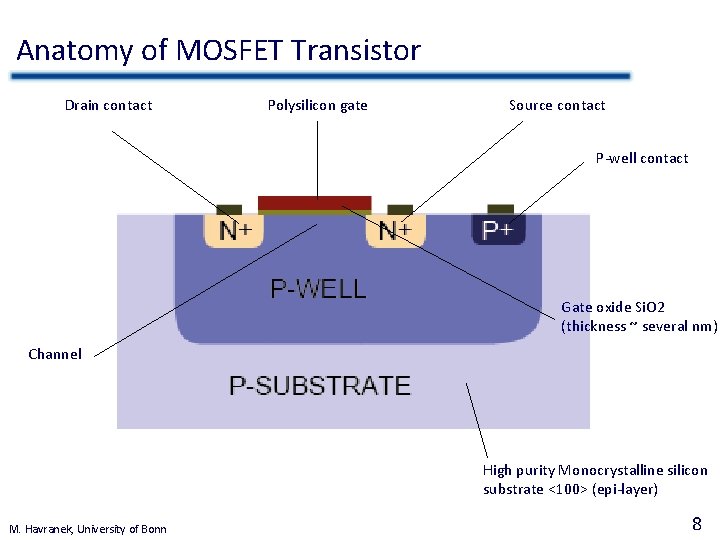

Anatomy of MOSFET Transistor Drain contact Polysilicon gate Source contact P-well contact Gate oxide Si. O 2 (thickness ~ several nm) Channel High purity Monocrystalline silicon substrate <100> (epi-layer) M. Havranek, University of Bonn 8

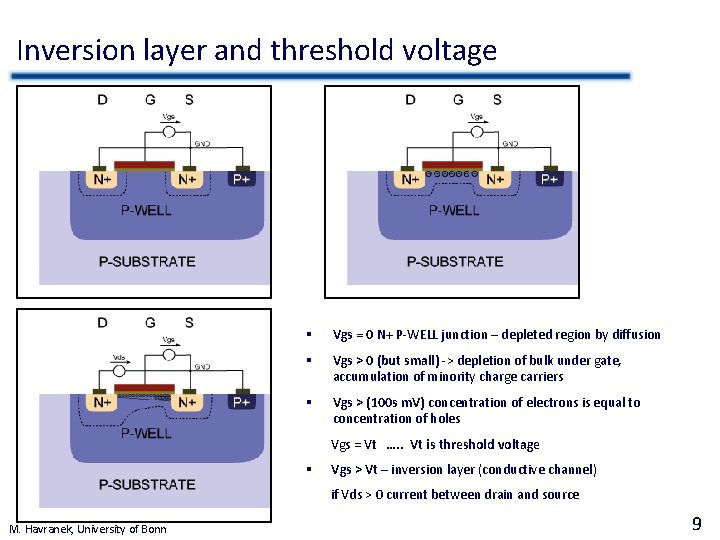

Inversion layer and threshold voltage § Vgs = 0 N+ P-WELL junction – depleted region by diffusion § Vgs > 0 (but small) -> depletion of bulk under gate, accumulation of minority charge carriers § Vgs > (100 s m. V) concentration of electrons is equal to concentration of holes Vgs = Vt …. . Vt is threshold voltage § Vgs > Vt – inversion layer (conductive channel) if Vds > 0 current between drain and source M. Havranek, University of Bonn 9

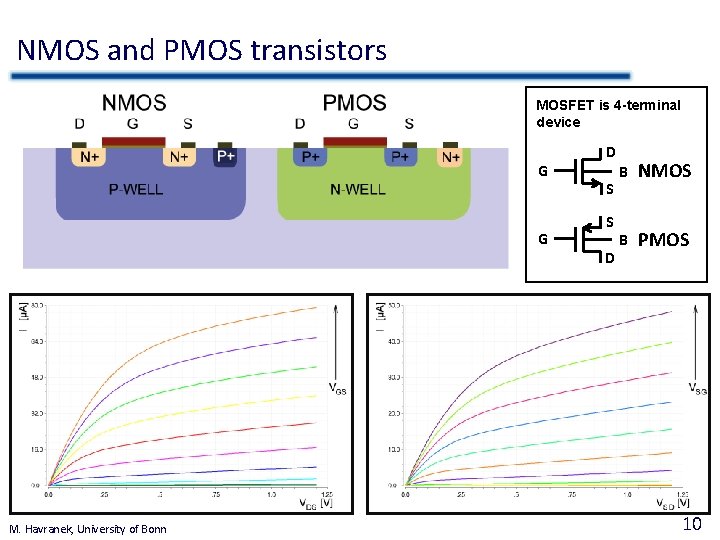

NMOS and PMOS transistors MOSFET is 4 -terminal device G G M. Havranek, University of Bonn D S S D B NMOS B PMOS 10

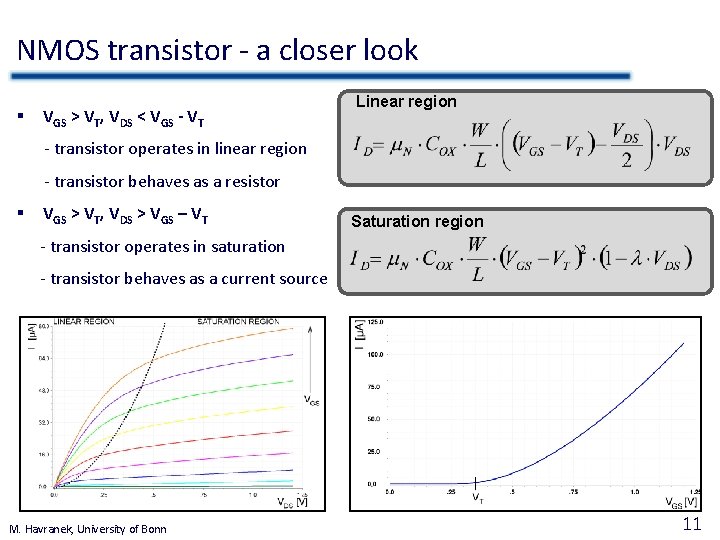

NMOS transistor - a closer look § VGS > VT, VDS < VGS - VT Linear region - transistor operates in linear region - transistor behaves as a resistor § VGS > VT, VDS > VGS – VT Saturation region - transistor operates in saturation - transistor behaves as a current source M. Havranek, University of Bonn 11

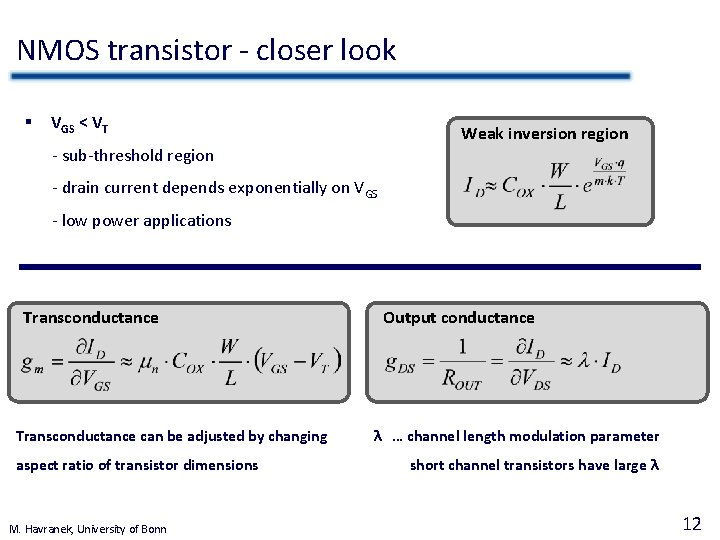

NMOS transistor - closer look § VGS < VT Weak inversion region - sub-threshold region - drain current depends exponentially on VGS - low power applications Transconductance can be adjusted by changing aspect ratio of transistor dimensions M. Havranek, University of Bonn Output conductance λ … channel length modulation parameter short channel transistors have large λ 12

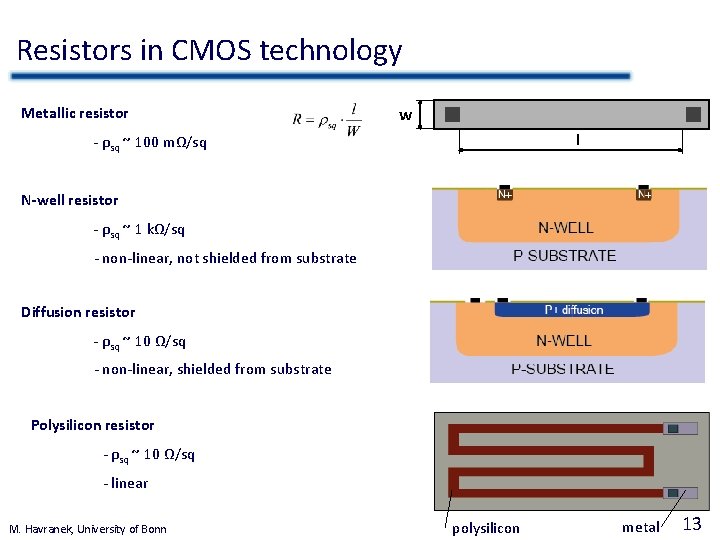

Resistors in CMOS technology Metallic resistor w l - ρsq ~ 100 mΩ/sq N-well resistor - ρsq ~ 1 kΩ/sq - non-linear, not shielded from substrate Diffusion resistor - ρsq ~ 10 Ω/sq - non-linear, shielded from substrate Polysilicon resistor - ρsq ~ 10 Ω/sq - linear M. Havranek, University of Bonn polysilicon metal 13

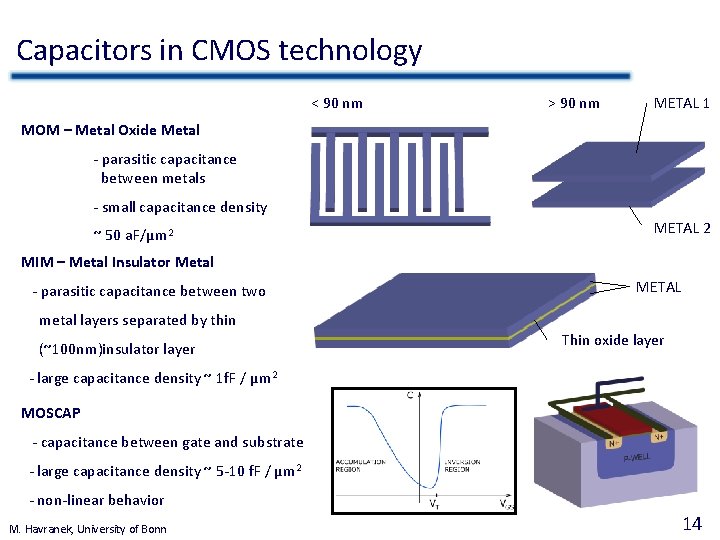

Capacitors in CMOS technology < 90 nm > 90 nm METAL 1 MOM – Metal Oxide Metal - parasitic capacitance between metals - small capacitance density ~ 50 a. F/µm 2 METAL 2 MIM – Metal Insulator Metal - parasitic capacitance between two METAL metal layers separated by thin (~100 nm)insulator layer Thin oxide layer - large capacitance density ~ 1 f. F / µm 2 MOSCAP - capacitance between gate and substrate - large capacitance density ~ 5 -10 f. F / µm 2 - non-linear behavior M. Havranek, University of Bonn 14

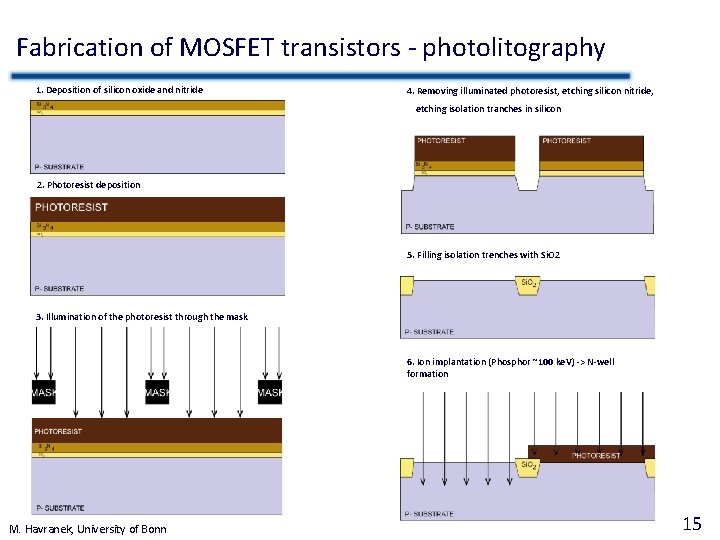

Fabrication of MOSFET transistors - photolitography 1. Deposition of silicon oxide and nitride 4. Removing illuminated photoresist, etching silicon nitride, etching isolation tranches in silicon 2. Photoresist deposition 5. Filling isolation trenches with Si. O 2 3. Illumination of the photoresist through the mask 6. Ion implantation (Phosphor ~100 ke. V) -> N-well formation M. Havranek, University of Bonn 15

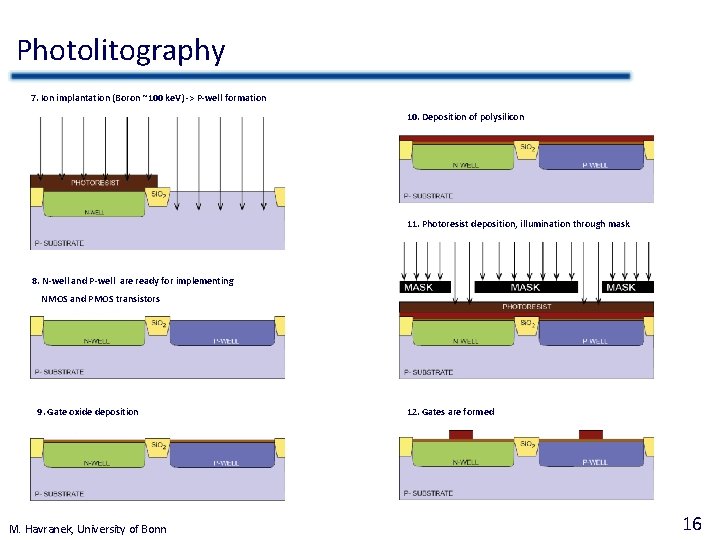

Photolitography 7. Ion implantation (Boron ~100 ke. V) -> P-well formation 10. Deposition of polysilicon 11. Photoresist deposition, illumination through mask 8. N-well and P-well are ready for implementing NMOS and PMOS transistors 9. Gate oxide deposition M. Havranek, University of Bonn 12. Gates are formed 16

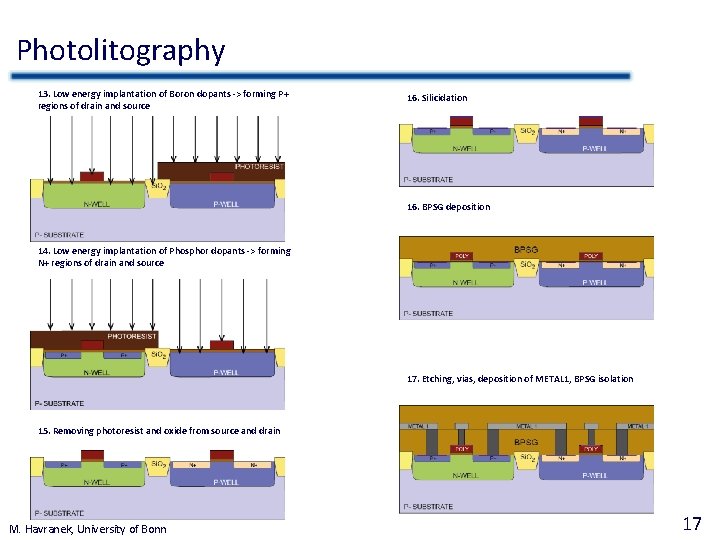

Photolitography 13. Low energy implantation of Boron dopants -> forming P+ regions of drain and source 16. Silicidation 16. BPSG deposition 14. Low energy implantation of Phosphor dopants -> forming N+ regions of drain and source 17. Etching, vias, deposition of METAL 1, BPSG isolation 15. Removing photoresist and oxide from source and drain M. Havranek, University of Bonn 17

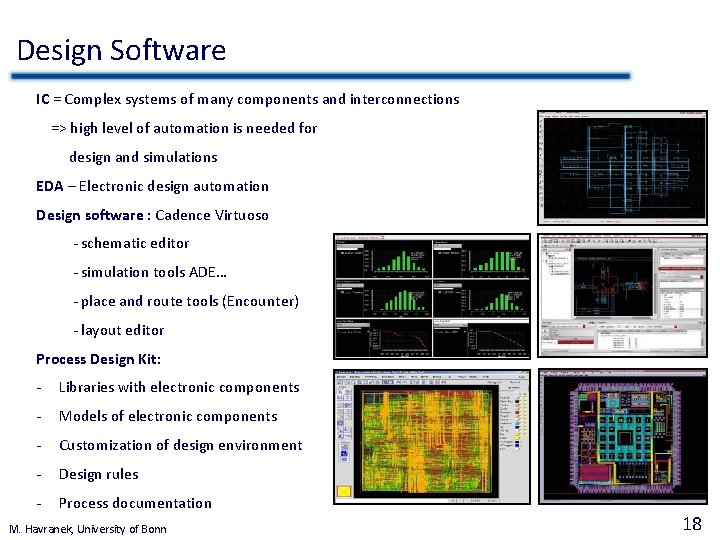

Design Software IC = Complex systems of many components and interconnections => high level of automation is needed for design and simulations EDA – Electronic design automation Design software : Cadence Virtuoso - schematic editor - simulation tools ADE… - place and route tools (Encounter) - layout editor Process Design Kit: - Libraries with electronic components - Models of electronic components - Customization of design environment - Design rules - Process documentation M. Havranek, University of Bonn 18

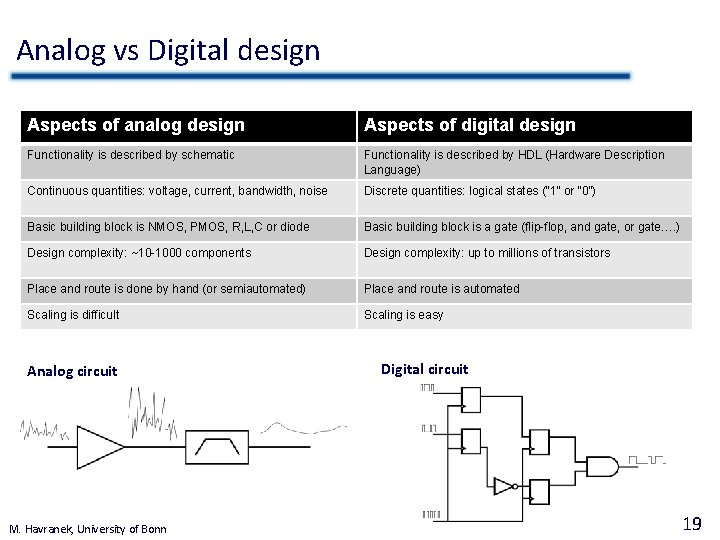

Analog vs Digital design Aspects of analog design Aspects of digital design Functionality is described by schematic Functionality is described by HDL (Hardware Description Language) Continuous quantities: voltage, current, bandwidth, noise Discrete quantities: logical states (“ 1” or “ 0”) Basic building block is NMOS, PMOS, R, L, C or diode Basic building block is a gate (flip-flop, and gate, or gate…. ) Design complexity: ~10 -1000 components Design complexity: up to millions of transistors Place and route is done by hand (or semiautomated) Place and route is automated Scaling is difficult Scaling is easy Analog circuit M. Havranek, University of Bonn Digital circuit 19

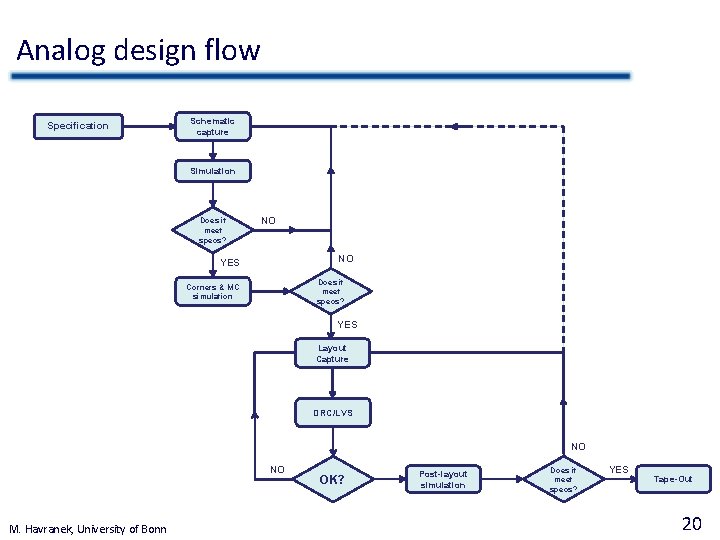

Analog design flow Specification Schematic capture Simulation Does it meet specs? NO NO YES Does it meet specs? Corners & MC simulation YES Layout Capture DRC/LVS NO NO M. Havranek, University of Bonn OK? Post-layout simulation Does it meet specs? YES Tape-Out 20

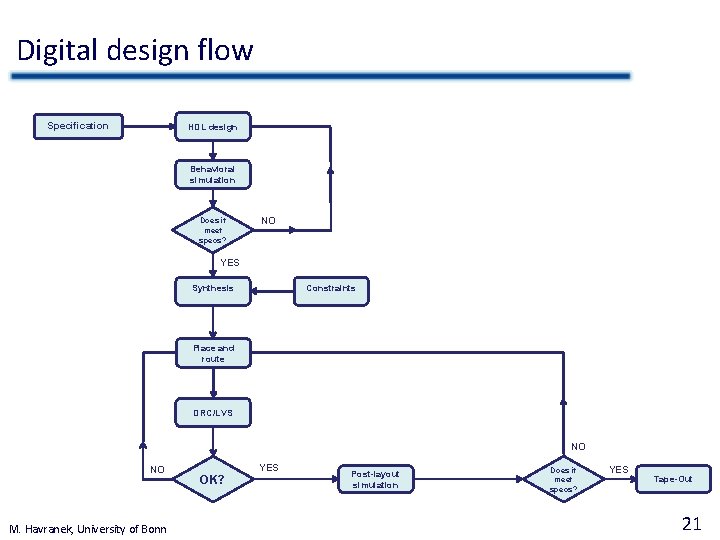

Digital design flow Specification HDL design Behavioral simulation Does it meet specs? NO YES Synthesis Constraints Place and route DRC/LVS NO NO M. Havranek, University of Bonn OK? YES Post-layout simulation Does it meet specs? YES Tape-Out 21

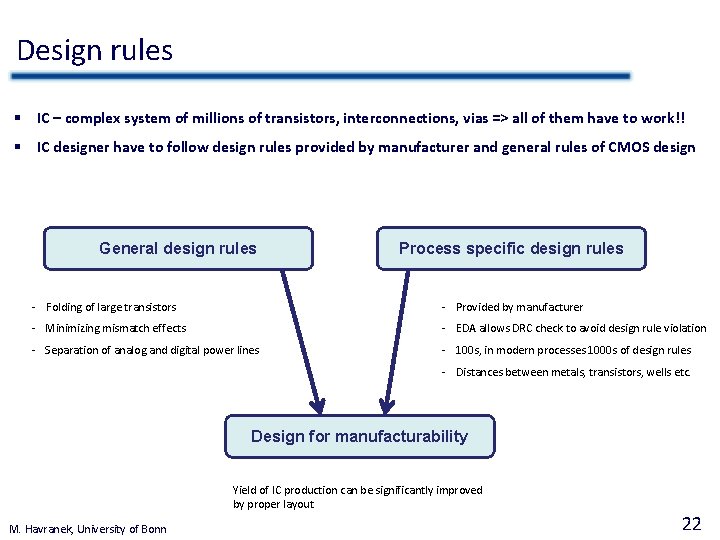

Design rules § IC – complex system of millions of transistors, interconnections, vias => all of them have to work!! § IC designer have to follow design rules provided by manufacturer and general rules of CMOS design General design rules Process specific design rules - Folding of large transistors - Provided by manufacturer - Minimizing mismatch effects - EDA allows DRC check to avoid design rule violation - Separation of analog and digital power lines - 100 s, in modern processes 1000 s of design rules - Distances between metals, transistors, wells etc. Design for manufacturability Yield of IC production can be significantly improved by proper layout M. Havranek, University of Bonn 22

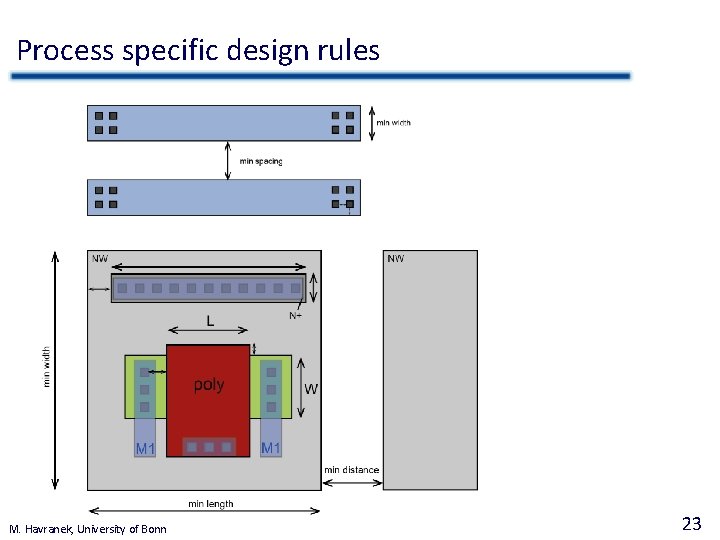

Process specific design rules M. Havranek, University of Bonn 23

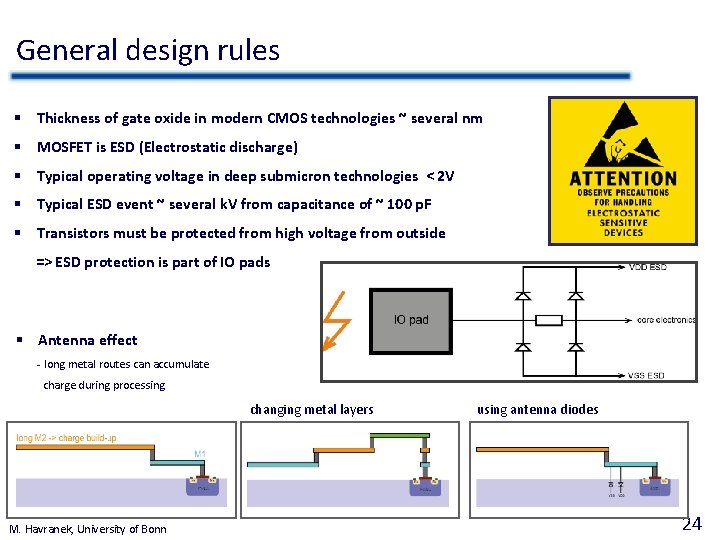

General design rules § Thickness of gate oxide in modern CMOS technologies ~ several nm § MOSFET is ESD (Electrostatic discharge) § Typical operating voltage in deep submicron technologies < 2 V § Typical ESD event ~ several k. V from capacitance of ~ 100 p. F § Transistors must be protected from high voltage from outside => ESD protection is part of IO pads § Antenna effect - long metal routes can accumulate charge during processing changing metal layers M. Havranek, University of Bonn using antenna diodes 24

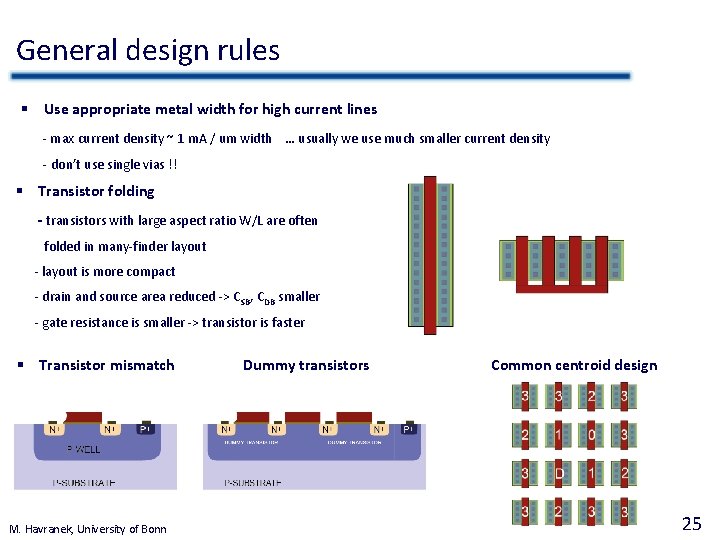

General design rules § Use appropriate metal width for high current lines - max current density ~ 1 m. A / um width … usually we use much smaller current density - don’t use single vias !! § Transistor folding - transistors with large aspect ratio W/L are often folded in many-finder layout - layout is more compact - drain and source area reduced -> CSB, CDB smaller - gate resistance is smaller -> transistor is faster § Transistor mismatch M. Havranek, University of Bonn Dummy transistors Common centroid design 25

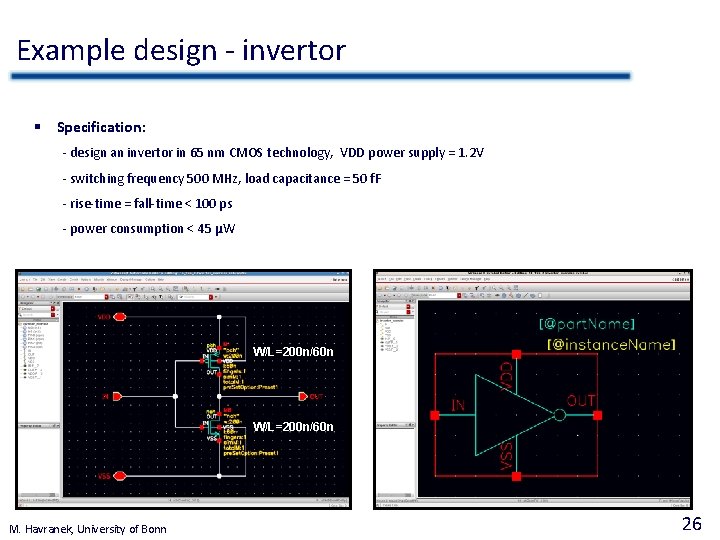

Example design - invertor § Specification: - design an invertor in 65 nm CMOS technology, VDD power supply = 1. 2 V - switching frequency 500 MHz, load capacitance = 50 f. F - rise-time = fall-time < 100 ps - power consumption < 45 µW W/L=200 n/60 nl M. Havranek, University of Bonn 26

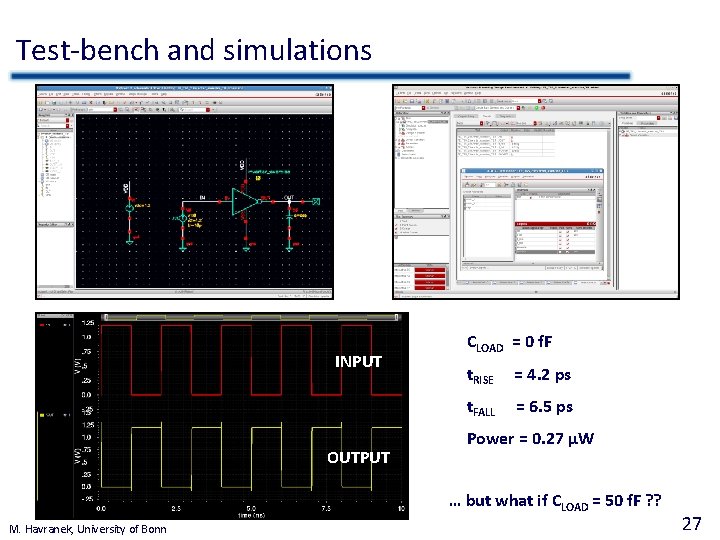

Test-bench and simulations INPUT OUTPUT CLOAD = 0 f. F t. RISE = 4. 2 ps t. FALL = 6. 5 ps Power = 0. 27 µW … but what if CLOAD = 50 f. F ? ? M. Havranek, University of Bonn 27

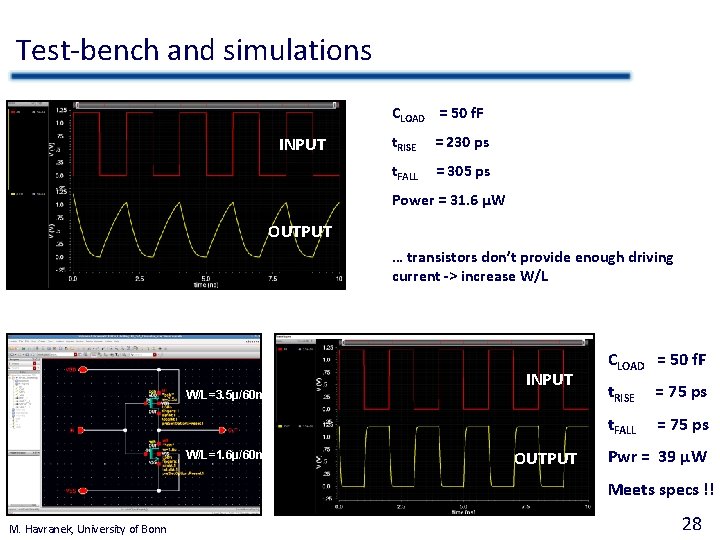

Test-bench and simulations CLOAD = 50 f. F INPUT t. RISE = 230 ps t. FALL = 305 ps Power = 31. 6 µW OUTPUT … transistors don’t provide enough driving current -> increase W/L=3. 5µ/60 n W/L=1. 6µ/60 n INPUT OUTPUT CLOAD = 50 f. F t. RISE = 75 ps t. FALL = 75 ps Pwr = 39 µW Meets specs !! M. Havranek, University of Bonn 28

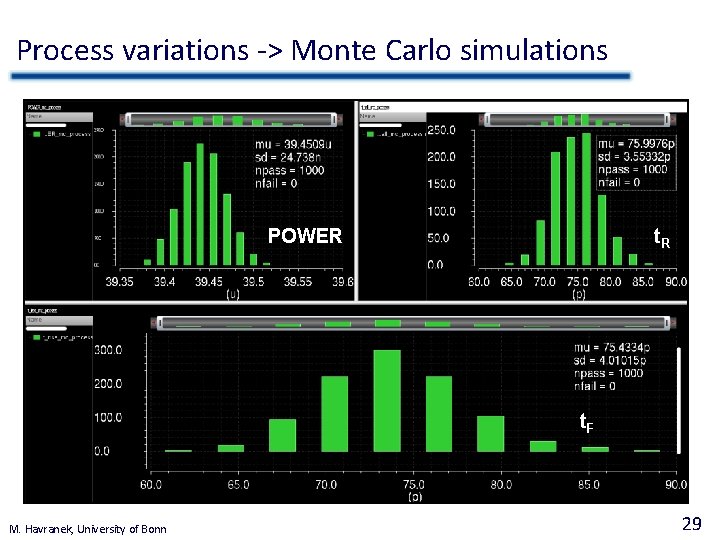

Process variations -> Monte Carlo simulations POWER t. F M. Havranek, University of Bonn 29

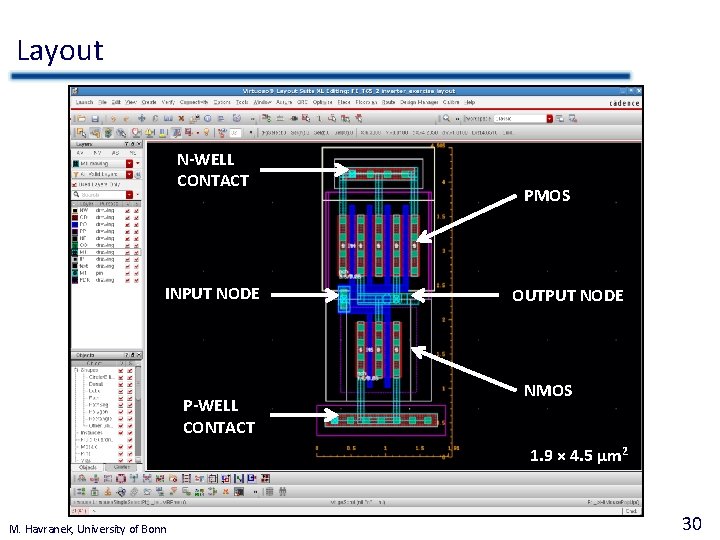

Layout N-WELL CONTACT INPUT NODE P-WELL CONTACT PMOS OUTPUT NODE NMOS 1. 9 × 4. 5 µm 2 M. Havranek, University of Bonn 30

Thank you for your attention 3 rd June 2013, TALENT Summer School, CERN

- Slides: 31