Basic Overview of VHDL Slides Available at www

Basic Overview of VHDL Slides Available at: www. pages. drexel. edu/~mjm 46 Matthew Murach

What is VHDL? VHDL is hardware descriptive language that is used to design and implement hardware devices. n VHDL is used in prototyping devices and in the development of hardware simulators. n Most of the concepts of VHDL design were covered in ECEC 200 logic circuits. n

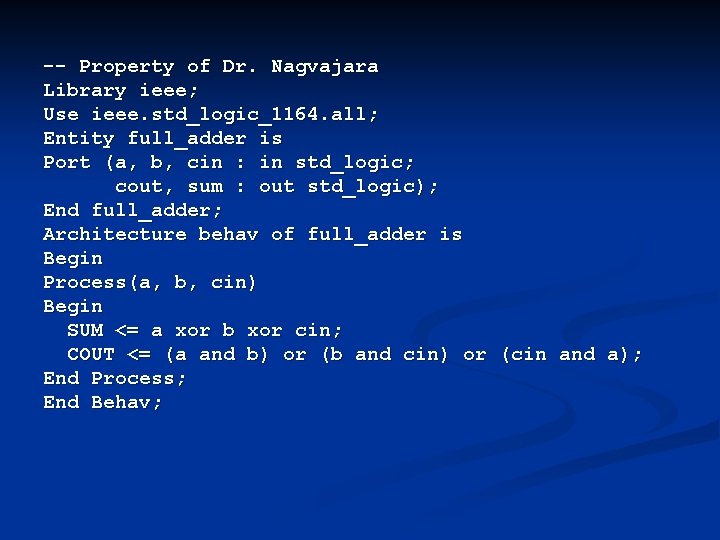

First Program – lecture notes -- Property of Dr. Nagvajara Library ieee; Use ieee. std_logic_1164. all; Entity full_adder is Port (a, b, cin : in std_logic; cout, sum : out std_logic); End full_adder; Architecture behav of full_adder is Begin Process(a, b, cin) Begin SUM <= a xor b xor cin; COUT <= (a and b) or (b and cin) or (cin and a); End Process; End Behav;

Fundamentals of VHDL Comments in VHDL use double hyphens just like the // in C++ n For example -- This is a comment n All Lines in VHDL similar to C++ terminate with the semicolon n An important note is that VHDL is NOT case sensitive i. e. IF and if are both keywords. n

Header of the VHDL Code Headers for the VHDL files are very analogous to headers in C++. A simple syntax for this header file is as follows Library ieee; -- Use IEEE defined libraries Use ieee. std_logic_1164. all; --Defines std logic type Use work. p 1_pack. all; -- User Defined library n

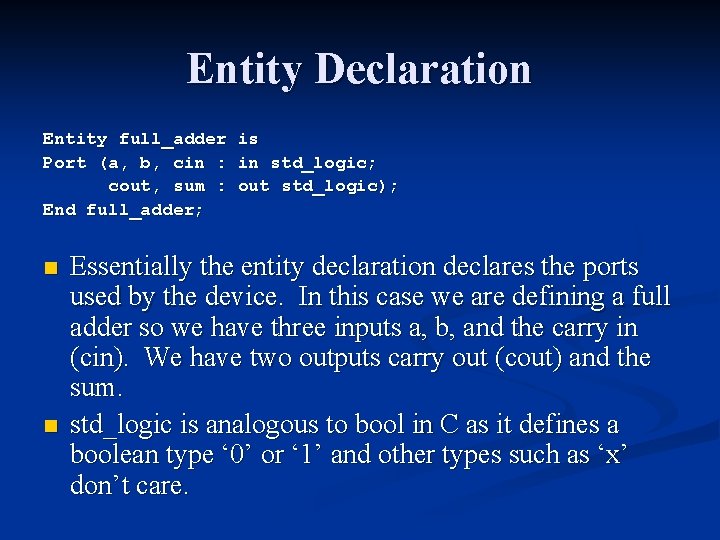

Entity Declaration Entity full_adder Port (a, b, cin : cout, sum : End full_adder; n n is in std_logic; out std_logic); Essentially the entity declaration declares the ports used by the device. In this case we are defining a full adder so we have three inputs a, b, and the carry in (cin). We have two outputs carry out (cout) and the sum. std_logic is analogous to bool in C as it defines a boolean type ‘ 0’ or ‘ 1’ and other types such as ‘x’ don’t care.

Architecture Section Architecture arch_name of entity_name is -- Signal declarations here Begin Process(sensitivity_list) -- Variable declarations here Begin -- do something here End Process; End arch_name; n n This section defines how the hardware behaves and operates Note that signal declarations should be made before beginning processes and variables are declared in the process.

Architecture Section The sensitivity list includes all signals in which this device should operate namely when a change in the signal(s) occurs. n The process given in the example operates on a change in either a, b, cin n Normally you should use a clock to drive the process section process(ck) – Trigger process on ck n

Signals and Variables Note that in VHDL there are two types of assignment signals and variables. n A variable is analogous to C++’s definition. n i. e. A : = temp; -- A now equals temp’s value n A Signal is analogous to real wiring. n i. e A <= temp; – A equals temp AFTER delay n Use of signals over variables is STRONGLY encouraged. n

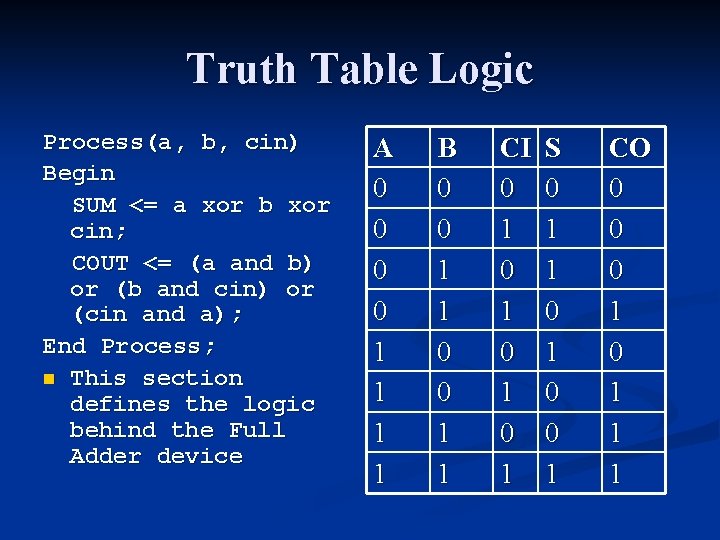

Truth Table Logic Process(a, b, cin) Begin SUM <= a xor b xor cin; COUT <= (a and b) or (b and cin) or (cin and a); End Process; n This section defines the logic behind the Full Adder device A 0 0 1 1 B 0 0 1 1 CI 0 1 0 1 S 0 1 1 0 0 1 CO 0 0 0 1 1 1

-- Property of Dr. Nagvajara Library ieee; Use ieee. std_logic_1164. all; Entity full_adder is Port (a, b, cin : in std_logic; cout, sum : out std_logic); End full_adder; Architecture behav of full_adder is Begin Process(a, b, cin) Begin SUM <= a xor b xor cin; COUT <= (a and b) or (b and cin) or (cin and a); End Process; End Behav;

- Slides: 11