Basic MIPS Implementation Control 1 Heres an updated

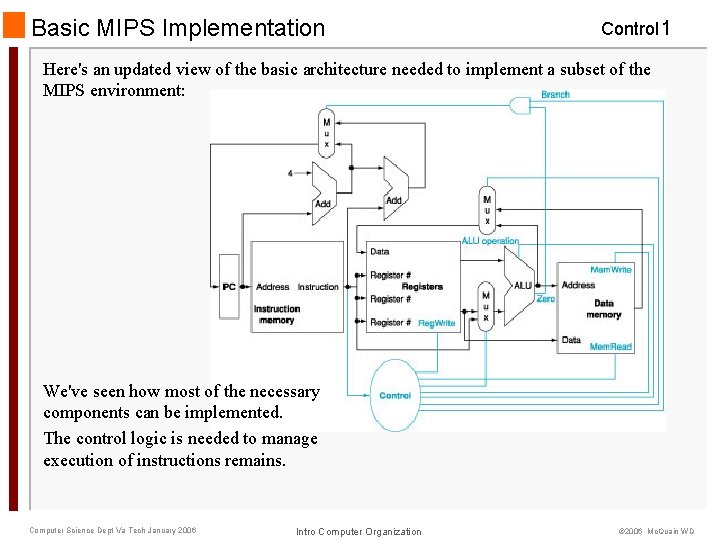

Basic MIPS Implementation Control 1 Here's an updated view of the basic architecture needed to implement a subset of the MIPS environment: We've seen how most of the necessary components can be implemented. The control logic is needed to manage execution of instructions remains. Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

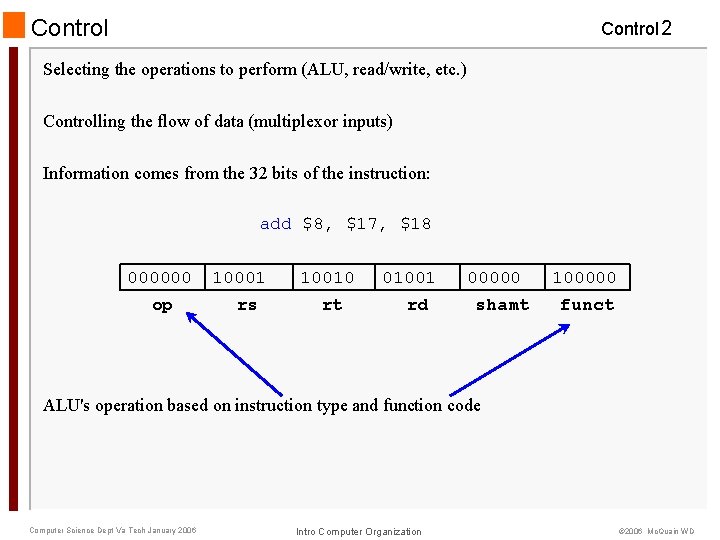

Control 2 Selecting the operations to perform (ALU, read/write, etc. ) Controlling the flow of data (multiplexor inputs) Information comes from the 32 bits of the instruction: add $8, $17, $18 000000 op 10001 rs 10010 rt 01001 rd 00000 shamt 100000 funct ALU's operation based on instruction type and function code Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

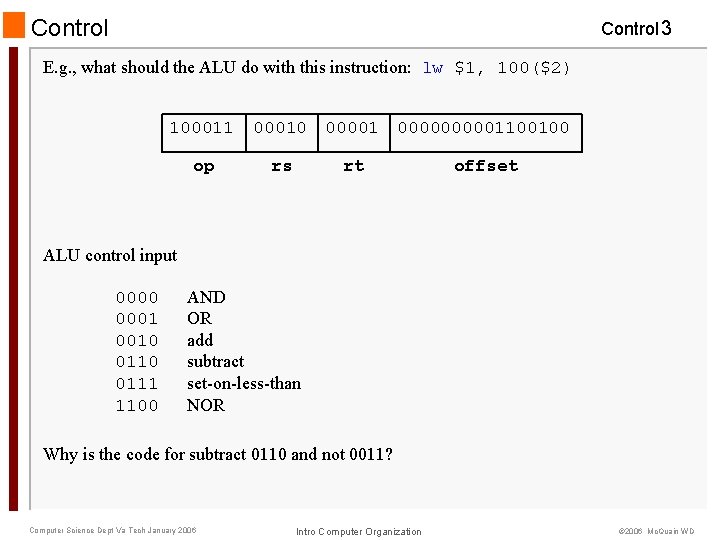

Control 3 E. g. , what should the ALU do with this instruction: lw $1, 100($2) 100011 op 00010 00001 rs 000001100100 rt offset ALU control input 0000 0001 0010 0111 1100 AND OR add subtract set-on-less-than NOR Why is the code for subtract 0110 and not 0011? Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

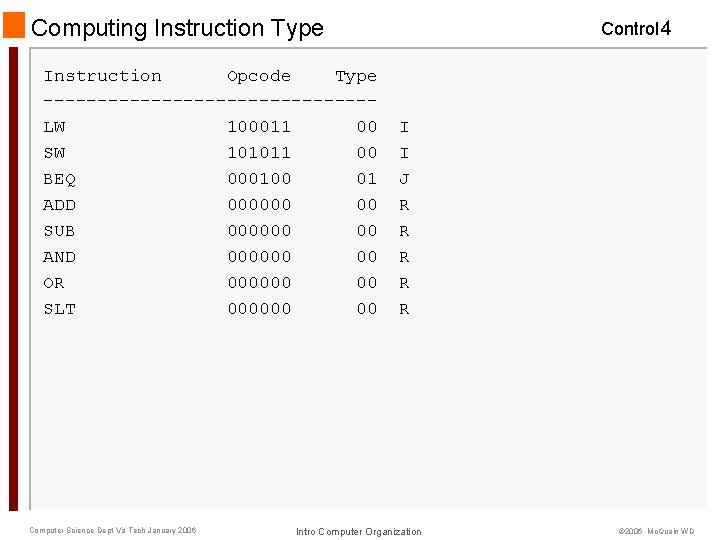

Computing Instruction Type Instruction Opcode Type ---------------LW 100011 00 SW 101011 00 BEQ 000100 01 ADD 000000 00 SUB 000000 00 AND 000000 00 OR 000000 00 SLT 000000 00 Computer Science Dept Va Tech January 2006 Control 4 I I J R R R Intro Computer Organization © 2006 Mc. Quain WD

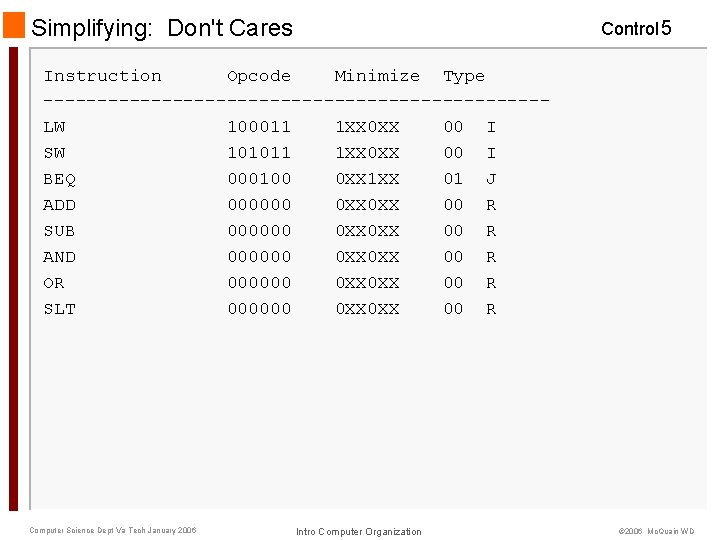

Simplifying: Don't Cares Control 5 Instruction Opcode Minimize Type -----------------------LW 100011 1 XX 00 I SW 101011 1 XX 00 I BEQ 000100 0 XX 1 XX 01 J ADD 000000 0 XX 00 R SUB 000000 0 XX 00 R AND 000000 0 XX 00 R OR 000000 0 XX 00 R SLT 000000 0 XX 00 R Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

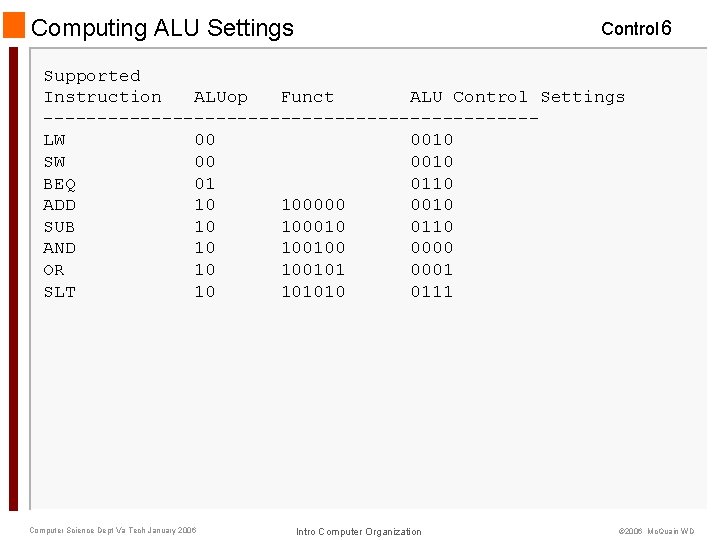

Computing ALU Settings Control 6 Supported Instruction ALUop Funct ALU Control Settings -----------------------LW 00 0010 SW 00 0010 BEQ 01 0110 ADD 10 100000 0010 SUB 10 100010 0110 AND 10 100100 0000 OR 10 100101 0001 SLT 10 101010 0111 Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

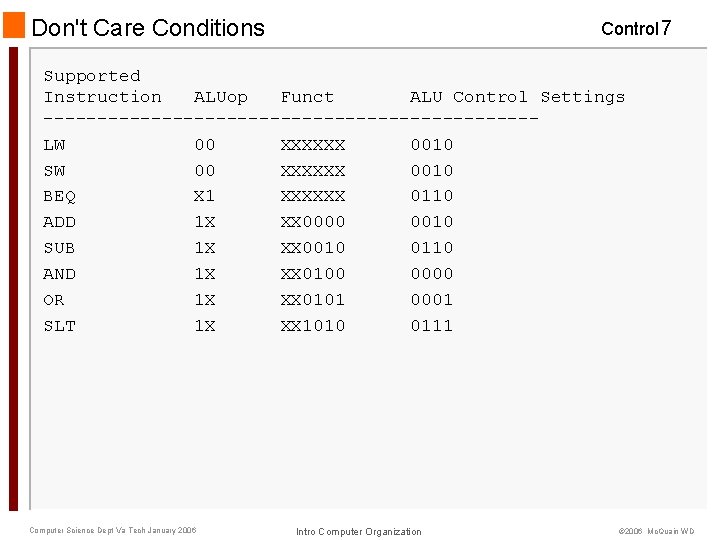

Don't Care Conditions Control 7 Supported Instruction ALUop Funct ALU Control Settings -----------------------LW 00 XXXXXX 0010 SW 00 XXXXXX 0010 BEQ X 1 XXXXXX 0110 ADD 1 X XX 0000 0010 SUB 1 X XX 0010 0110 AND 1 X XX 0100 0000 OR 1 X XX 0101 0001 SLT 1 X XX 1010 0111 Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

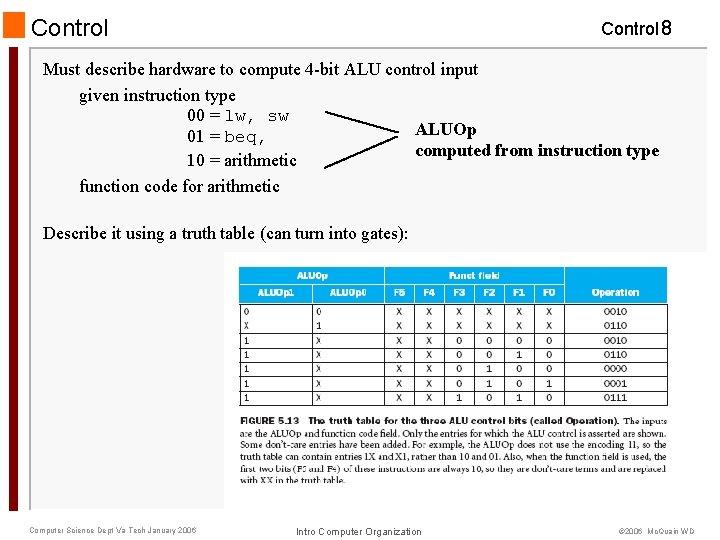

Control 8 Must describe hardware to compute 4 -bit ALU control input given instruction type 00 = lw, sw ALUOp 01 = beq, computed from instruction type 10 = arithmetic function code for arithmetic Describe it using a truth table (can turn into gates): Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

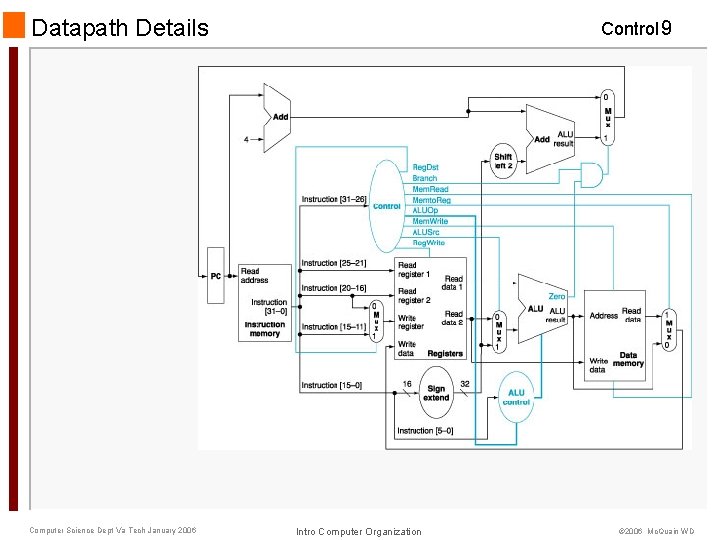

Datapath Details Computer Science Dept Va Tech January 2006 Control 9 Intro Computer Organization © 2006 Mc. Quain WD

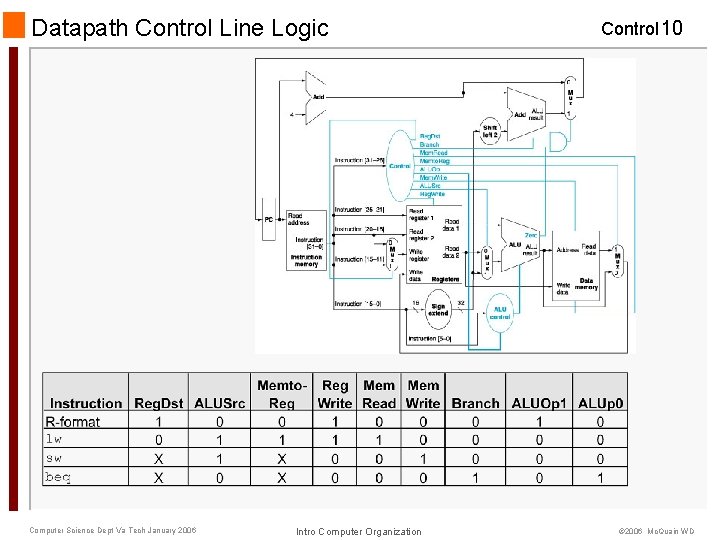

Datapath Control Line Logic Computer Science Dept Va Tech January 2006 Intro Computer Organization Control 10 © 2006 Mc. Quain WD

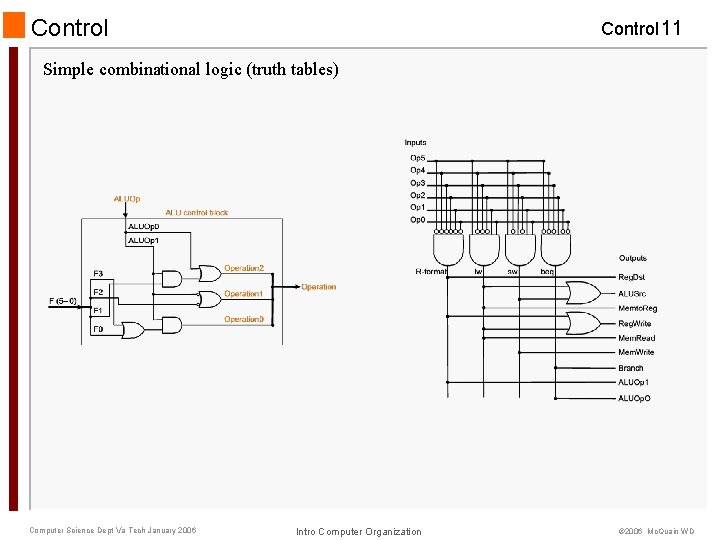

Control 11 Simple combinational logic (truth tables) Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

![Breaking down an instruction Control 12 ISA definition of arithmetic: Reg[Memory[PC][15: 11]] <= Reg[Memory[PC][25: Breaking down an instruction Control 12 ISA definition of arithmetic: Reg[Memory[PC][15: 11]] <= Reg[Memory[PC][25:](http://slidetodoc.com/presentation_image_h2/153800ef9bf384b61cb2909cbfd07e80/image-12.jpg)

Breaking down an instruction Control 12 ISA definition of arithmetic: Reg[Memory[PC][15: 11]] <= Reg[Memory[PC][25: 21]] op Reg[Memory[PC][20: 16]] Could break down to: IR <= Memory[PC] A <= Reg[IR[25: 21]] B <= Reg[IR[20: 16]] ALUOut <= A op B Reg[IR[20: 16]] <= ALUOut We forgot an important part of the definition of arithmetic! PC <= PC + 4 Computer Science Dept Va Tech January 2006 Intro Computer Organization © 2006 Mc. Quain WD

- Slides: 12