Basic Gates Verilog Discussion D 5 2 Examples

Basic Gates Verilog Discussion D 5. 2 Examples 1 - 3

Basic Gates - Verilog • Example 1 – 2 -Input Gates: Logic Equations • Example 2 – Multiple-Input Gates • Example 3 – 4 -Input Gates: for Loop

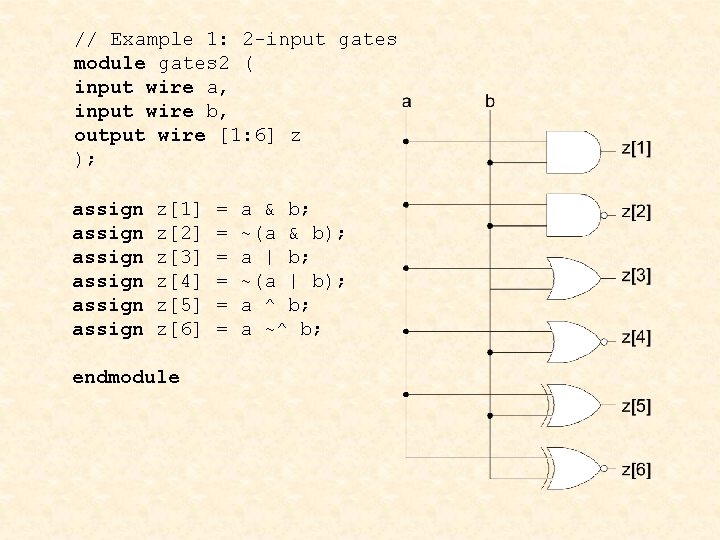

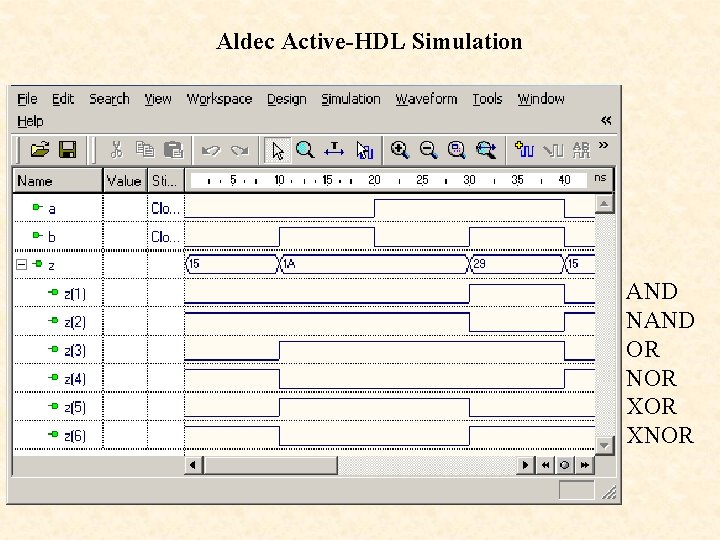

// Example 1: 2 -input gates module gates 2 ( input wire a, input wire b, output wire [1: 6] z ); assign assign z[1] z[2] z[3] z[4] z[5] z[6] endmodule = = = a & b; ~(a & b); a | b; ~(a | b); a ^ b; a ~^ b;

Aldec Active-HDL Simulation AND NAND OR NOR XNOR

Basic Gates - Verilog • Example 1 – 2 -Input Gates: Logic Equations • Example 2 – Multiple-Input Gates • Example 3 – 4 -Input Gates: for Loop

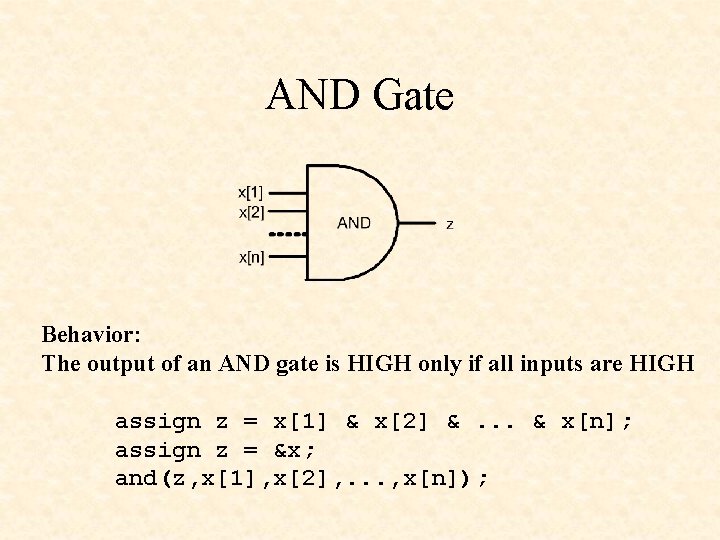

AND Gate Behavior: The output of an AND gate is HIGH only if all inputs are HIGH assign z = x[1] & x[2] &. . . & x[n]; assign z = &x; and(z, x[1], x[2], . . . , x[n]);

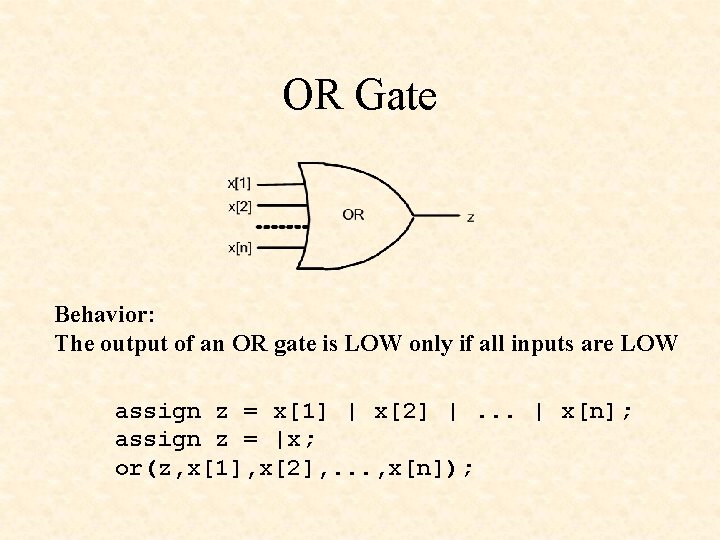

OR Gate Behavior: The output of an OR gate is LOW only if all inputs are LOW assign z = x[1] | x[2] |. . . | x[n]; assign z = |x; or(z, x[1], x[2], . . . , x[n]);

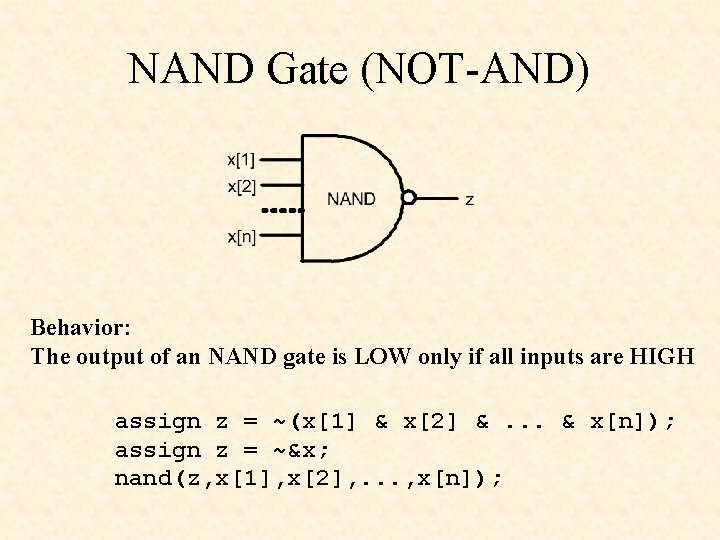

NAND Gate (NOT-AND) Behavior: The output of an NAND gate is LOW only if all inputs are HIGH assign z = ~(x[1] & x[2] &. . . & x[n]); assign z = ~&x; nand(z, x[1], x[2], . . . , x[n]);

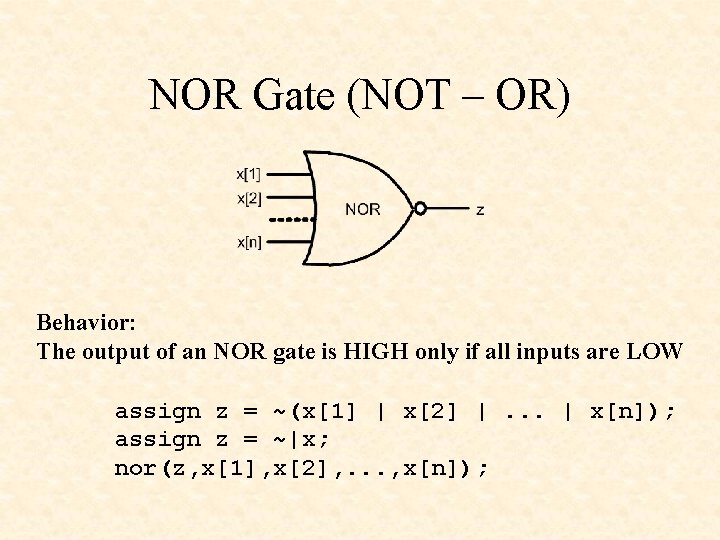

NOR Gate (NOT – OR) Behavior: The output of an NOR gate is HIGH only if all inputs are LOW assign z = ~(x[1] | x[2] |. . . | x[n]); assign z = ~|x; nor(z, x[1], x[2], . . . , x[n]);

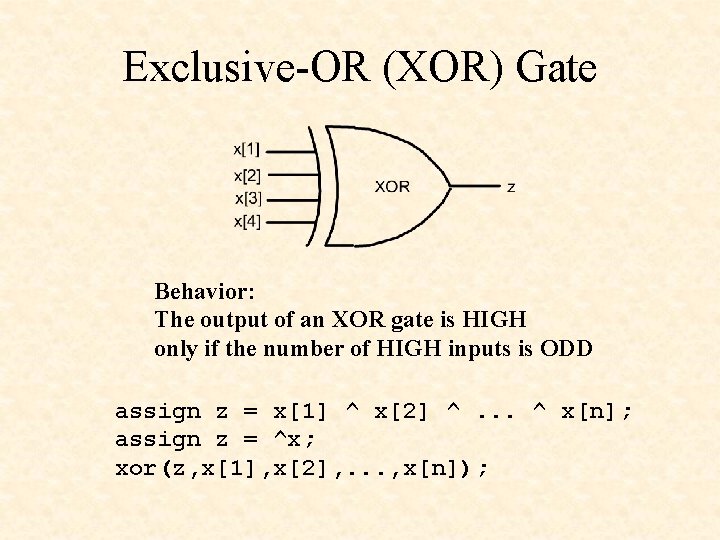

Exclusive-OR (XOR) Gate Behavior: The output of an XOR gate is HIGH only if the number of HIGH inputs is ODD assign z = x[1] ^ x[2] ^. . . ^ x[n]; assign z = ^x; xor(z, x[1], x[2], . . . , x[n]);

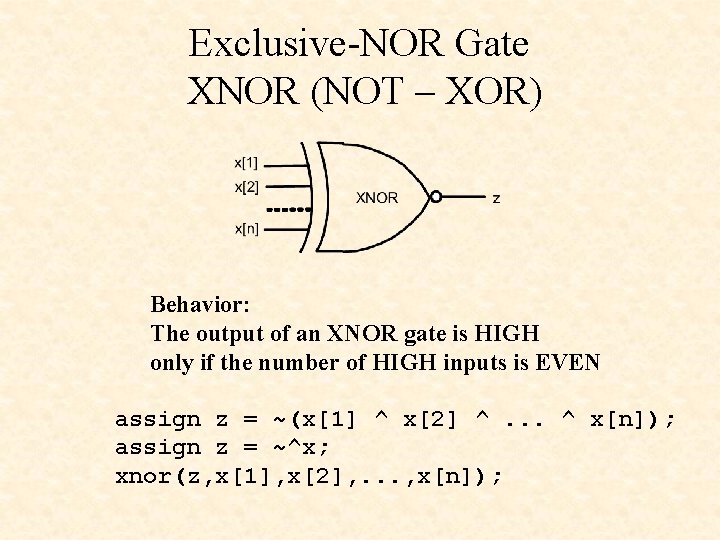

Exclusive-NOR Gate XNOR (NOT – XOR) Behavior: The output of an XNOR gate is HIGH only if the number of HIGH inputs is EVEN assign z = ~(x[1] ^ x[2] ^. . . ^ x[n]); assign z = ~^x; xnor(z, x[1], x[2], . . . , x[n]);

![// Example 2: 4 -input gates module gates 4 ( input wire [4: 1] // Example 2: 4 -input gates module gates 4 ( input wire [4: 1]](http://slidetodoc.com/presentation_image_h2/8709d444ef038709f5ecf751f0446569/image-12.jpg)

// Example 2: 4 -input gates module gates 4 ( input wire [4: 1] x , output wire [6: 1] z , output wire [6: 1] y ); and(z[6], x[1], x[2], x[3], x[4]); nand(z[5], x[1], x[2], x[3], x[4]); or(z[4], x[1], x[2], x[3], x[4]); nor(z[3], x[1], x[2], x[3], x[4]); xor(z[2], x[1], x[2], x[3], x[4]); xnor(z[1], x[2], x[3], x[4]); assign assign y[6] y[5] y[4] y[3] y[2] y[1] endmodule = = = &x; ~&x; |x; ~|x; ^x; ~^x; Instantiation Statements Reduction Operators

![and(z[6], x[1], . . . nand(z[5], x[1], . . . or(z[4], x[1], . . and(z[6], x[1], . . . nand(z[5], x[1], . . . or(z[4], x[1], . .](http://slidetodoc.com/presentation_image_h2/8709d444ef038709f5ecf751f0446569/image-13.jpg)

and(z[6], x[1], . . . nand(z[5], x[1], . . . or(z[4], x[1], . . . nor(z[3], x[1], . . . xor(z[2], x[1], . . . xnor(z[1], x[1], . . . assign assign y[6] y[5] y[4] y[3] y[2] y[1] = = = &x; ~&x; |x; ~|x; ^x; ~^x;

Basic Gates - Verilog • Example 1 – 2 -Input Gates: Logic Equations • Example 2 – Multiple-Input Gates • Example 3 – 4 -Input Gates: for Loop

![4 -Input AND Gate 3 -Level Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z 4 -Input AND Gate 3 -Level Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z](http://slidetodoc.com/presentation_image_h2/8709d444ef038709f5ecf751f0446569/image-15.jpg)

4 -Input AND Gate 3 -Level Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z & x[i]; 2 -Level

![// Example 3: Verilog for loop module and 4 ( input wire [4: 1] // Example 3: Verilog for loop module and 4 ( input wire [4: 1]](http://slidetodoc.com/presentation_image_h2/8709d444ef038709f5ecf751f0446569/image-16.jpg)

// Example 3: Verilog for loop module and 4 ( input wire [4: 1] x , output reg z ); integer i; Sensitivity list // 4 -input AND gate * always @(x) begin z = x[1]; for(i=2; i<=4; i=i+1) z = z & x[i]; endmodule

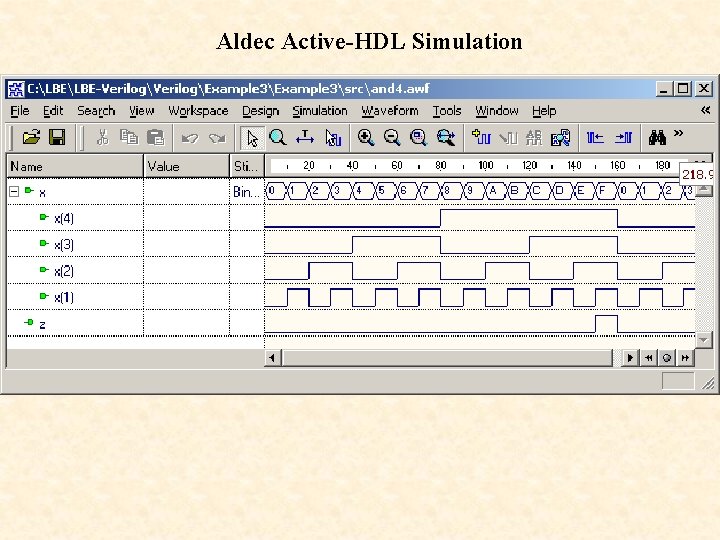

Aldec Active-HDL Simulation

![4 -Input OR Gate Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z 4 -Input OR Gate Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z](http://slidetodoc.com/presentation_image_h2/8709d444ef038709f5ecf751f0446569/image-18.jpg)

4 -Input OR Gate Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z | x[i];

![4 -Input XOR Gate Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z 4 -Input XOR Gate Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z](http://slidetodoc.com/presentation_image_h2/8709d444ef038709f5ecf751f0446569/image-19.jpg)

4 -Input XOR Gate Behavior: z = x[1]; for(i=2; i<=4; i=i+1) z = z ^ x[i]; Note: z = 1 if the number of 1 inputs in ODD

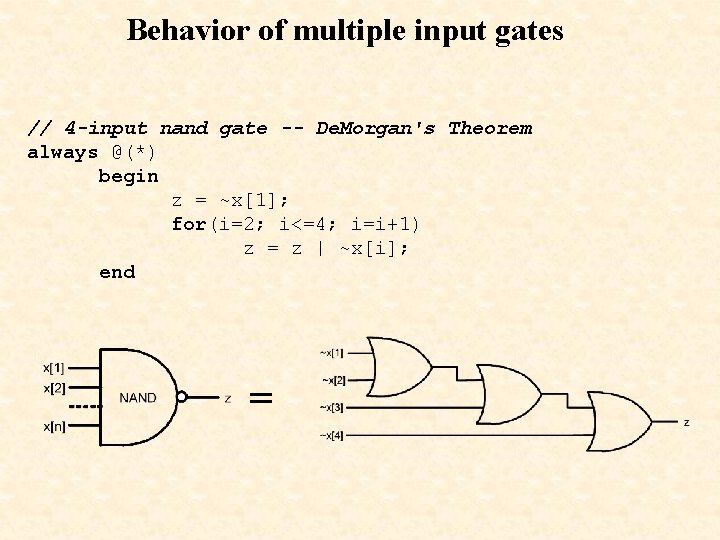

Behavior of multiple input gates // 4 -input nand gate -- De. Morgan's Theorem always @(*) begin z = ~x[1]; for(i=2; i<=4; i=i+1) z = z | ~x[i]; end =

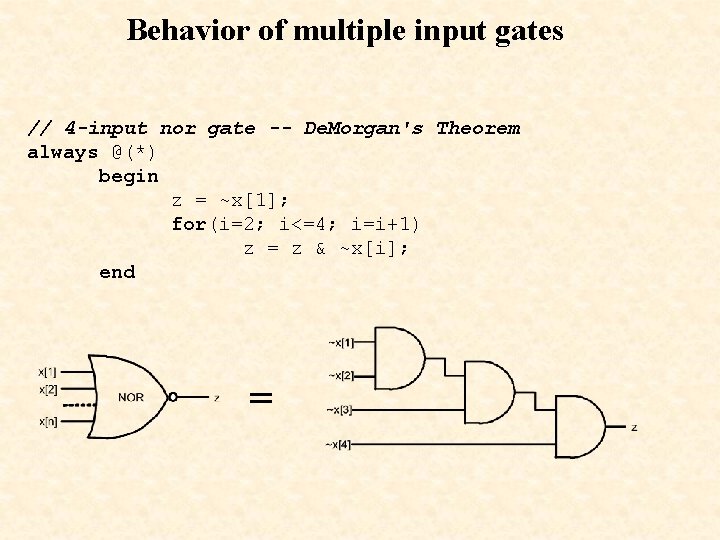

Behavior of multiple input gates // 4 -input nor gate -- De. Morgan's Theorem always @(*) begin z = ~x[1]; for(i=2; i<=4; i=i+1) z = z & ~x[i]; end =

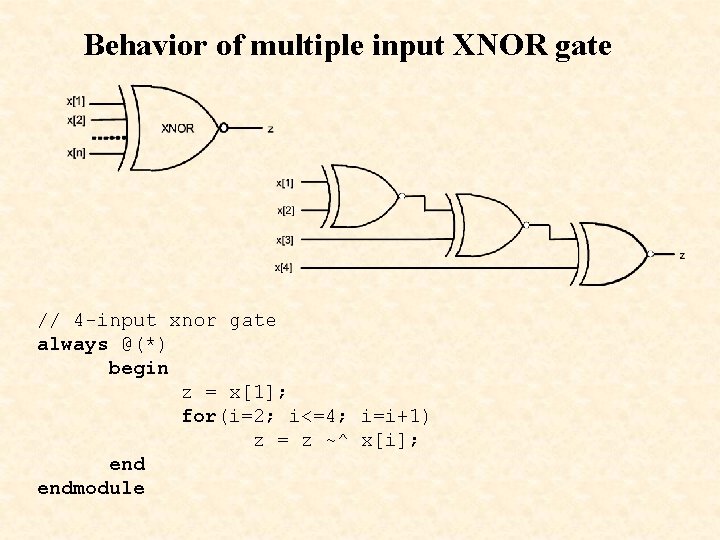

Behavior of multiple input XNOR gate // 4 -input xnor gate always @(*) begin z = x[1]; for(i=2; i<=4; i=i+1) z = z ~^ x[i]; endmodule

- Slides: 22