Background Basics of semiconductor physics Basics of elementary

Background Ø Basics of semiconductor physics Ø Basics of elementary linear circuit analysis Ø Fundamental concepts will however be reviewed A. Rivetti – INFN Sezione di Torino

Lecture I: • Semicondunctor properties review • MOS transistor physics A. Rivetti – INFN Sezione di Torino

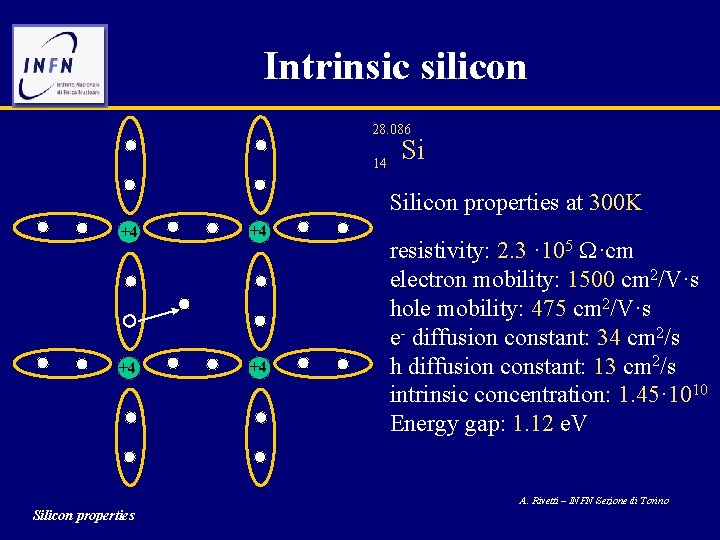

Intrinsic silicon 28. 086 14 Si Silicon properties at 300 K +4 +4 resistivity: 2. 3 · 105 W·cm electron mobility: 1500 cm 2/V·s hole mobility: 475 cm 2/V·s e- diffusion constant: 34 cm 2/s h diffusion constant: 13 cm 2/s intrinsic concentration: 1. 45· 1010 Energy gap: 1. 12 e. V A. Rivetti – INFN Sezione di Torino Silicon properties

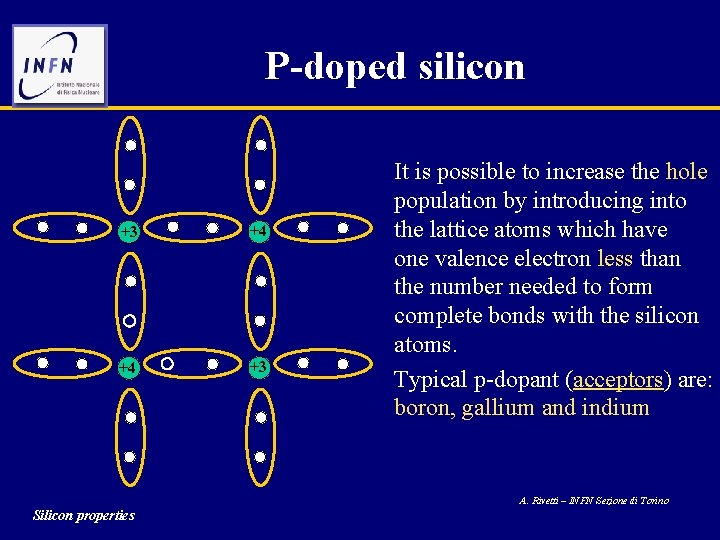

P-doped silicon +3 +4 +4 +3 It is possible to increase the hole population by introducing into the lattice atoms which have one valence electron less than the number needed to form complete bonds with the silicon atoms. Typical p-dopant (acceptors) are: boron, gallium and indium A. Rivetti – INFN Sezione di Torino Silicon properties

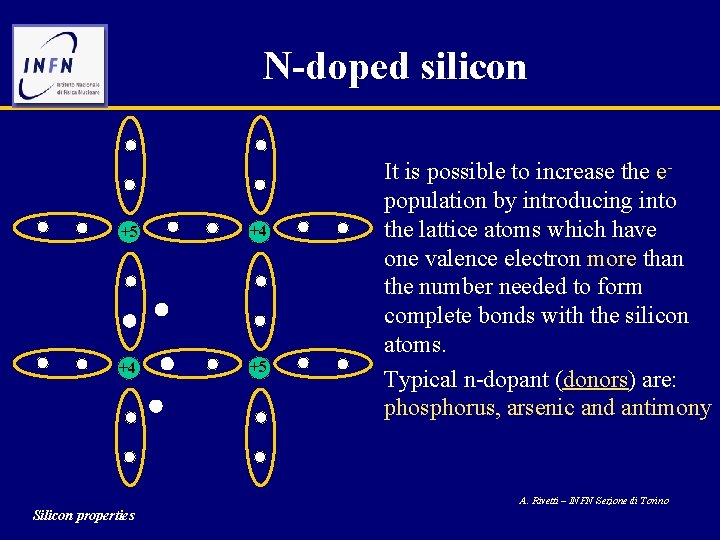

N-doped silicon +5 +4 +4 +5 It is possible to increase the epopulation by introducing into the lattice atoms which have one valence electron more than the number needed to form complete bonds with the silicon atoms. Typical n-dopant (donors) are: phosphorus, arsenic and antimony A. Rivetti – INFN Sezione di Torino Silicon properties

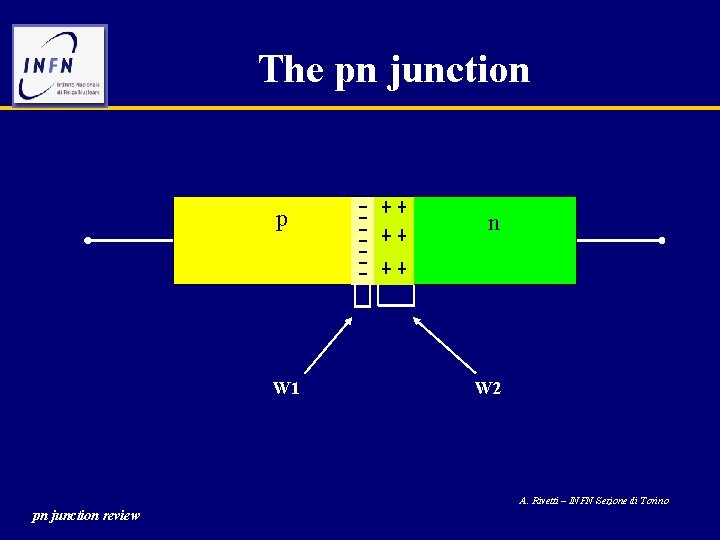

The pn junction p n W 1 W 2 A. Rivetti – INFN Sezione di Torino pn junction review

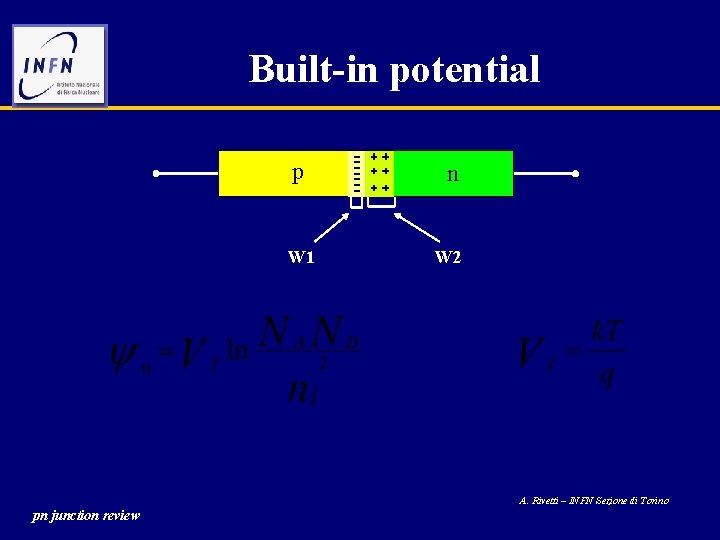

Built-in potential p n W 1 W 2 A. Rivetti – INFN Sezione di Torino pn junction review

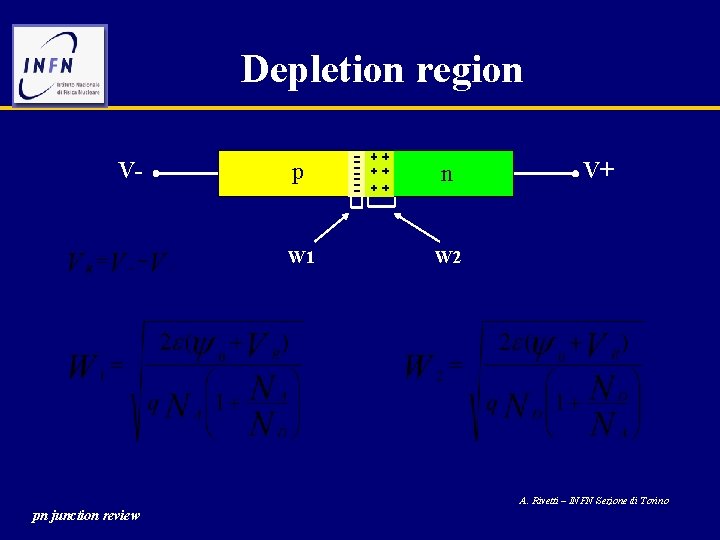

Depletion region V- p n W 1 W 2 V+ A. Rivetti – INFN Sezione di Torino pn junction review

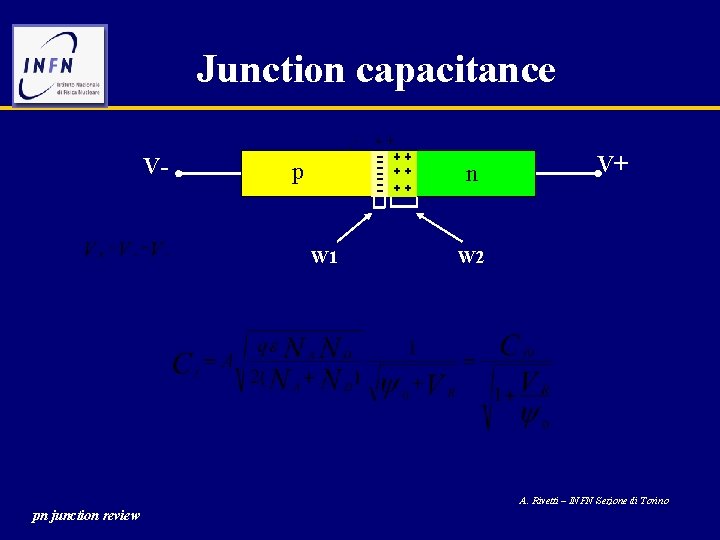

Junction capacitance V- ----- p W 1 - - + + n V+ W 2 A. Rivetti – INFN Sezione di Torino pn junction review

Lecture I: • Semicondunctor properties review • MOS transistor physics A. Rivetti – INFN Sezione di Torino

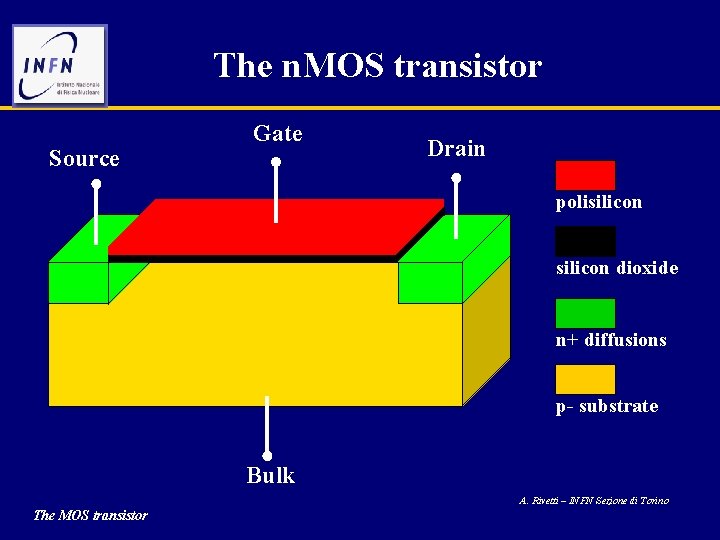

The n. MOS transistor Source Gate Drain polisilicon dioxide n+ diffusions p- substrate Bulk A. Rivetti – INFN Sezione di Torino The MOS transistor

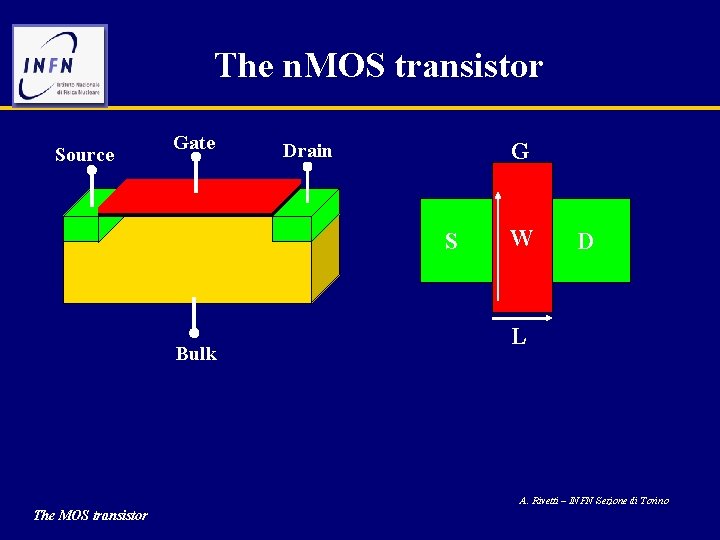

The n. MOS transistor Source Gate G Drain S Bulk W D L A. Rivetti – INFN Sezione di Torino The MOS transistor

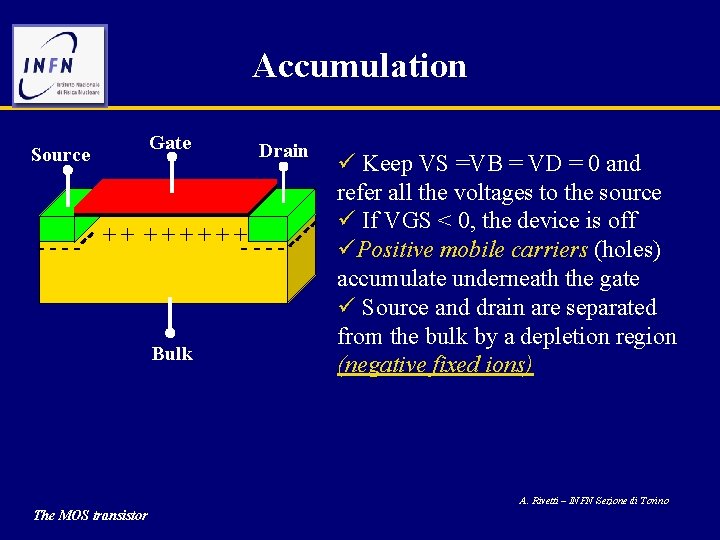

Accumulation Source Gate Drain - - + + + +- - Bulk ü Keep VS =VB = VD = 0 and refer all the voltages to the source ü If VGS < 0, the device is off üPositive mobile carriers (holes) accumulate underneath the gate ü Source and drain are separated from the bulk by a depletion region (negative fixed ions) A. Rivetti – INFN Sezione di Torino The MOS transistor

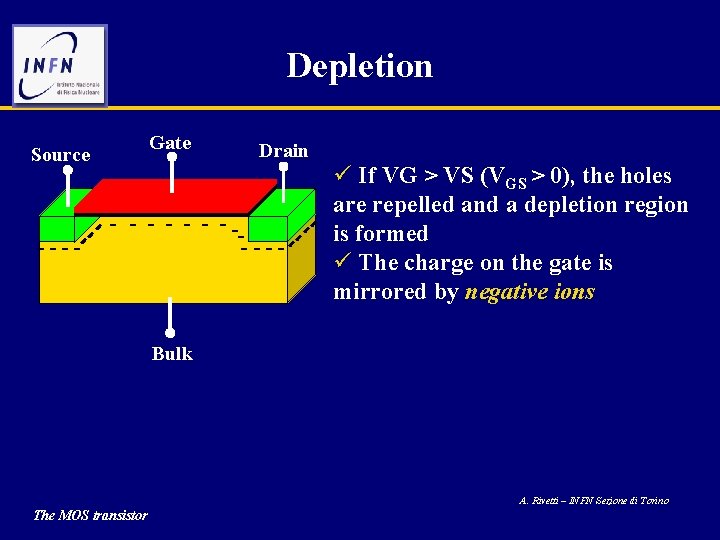

Depletion Gate Source ---- Drain - - - --- - ü If VG > VS (VGS > 0), the holes are repelled and a depletion region is formed ü The charge on the gate is mirrored by negative ions Bulk A. Rivetti – INFN Sezione di Torino The MOS transistor

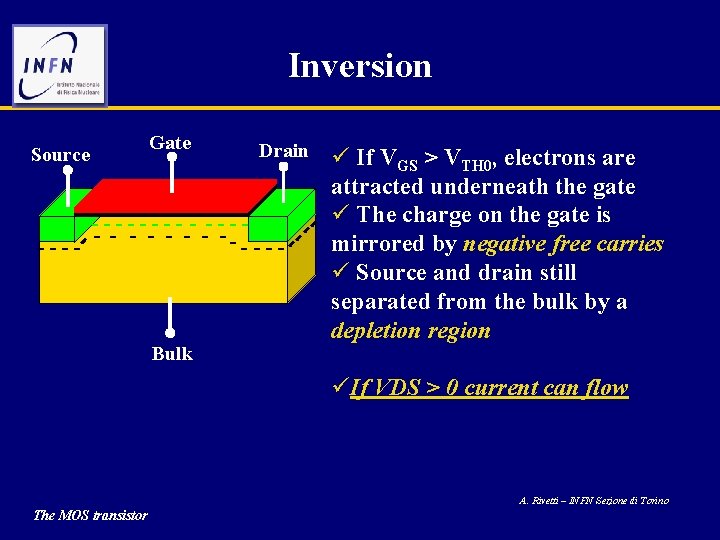

Inversion Source Gate Drain ---- - - - - - --- - Bulk ü If VGS > VTH 0, electrons are attracted underneath the gate ü The charge on the gate is mirrored by negative free carries ü Source and drain still separated from the bulk by a depletion region üIf VDS > 0 current can flow A. Rivetti – INFN Sezione di Torino The MOS transistor

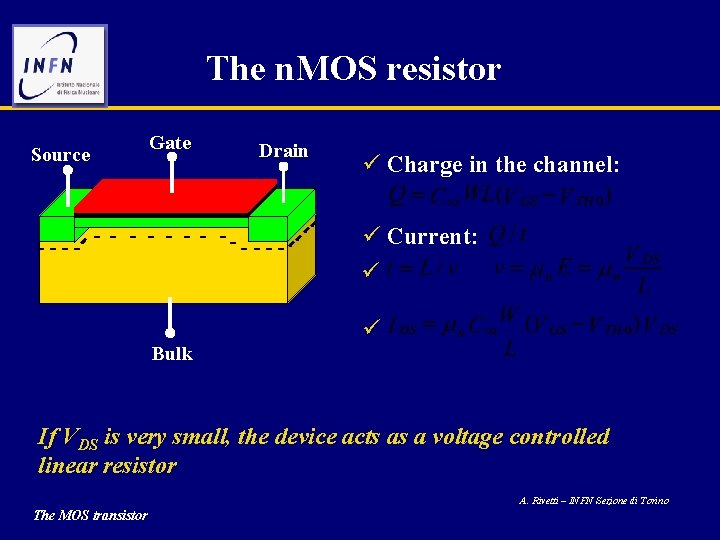

The n. MOS resistor Source Gate Drain - - --- - ü Charge in the channel: ü Current: ü ü Bulk If VDS is very small, the device acts as a voltage controlled linear resistor A. Rivetti – INFN Sezione di Torino The MOS transistor

NMOS I-V characteristic For the moment, Vsourse is kept at zero Vdrain Vgate Vsource A. Rivetti – INFN Sezione di Torino The MOS transistor

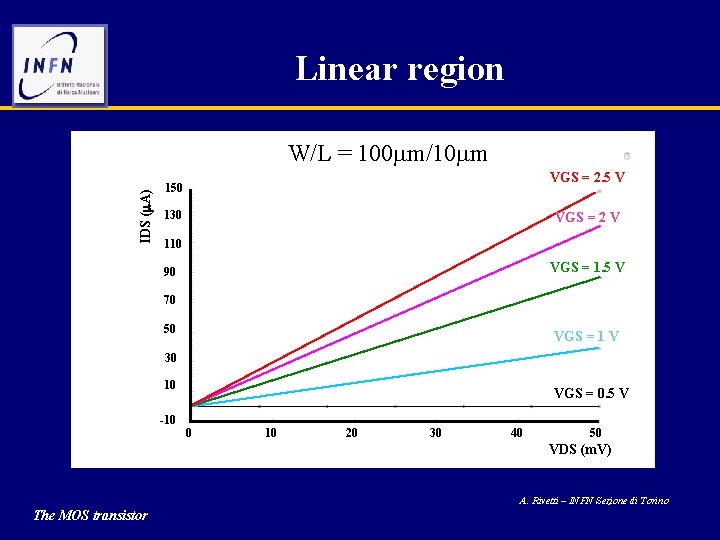

Linear region IDS (m. A) W/L = 100 mm/10 mm VGS = 2. 5 V 150 130 VGS = 2 V 110 VGS = 1. 5 V 90 70 50 VGS = 1 V 30 10 -10 VGS = 0. 5 V 0 10 20 30 40 50 VDS (m. V) A. Rivetti – INFN Sezione di Torino The MOS transistor

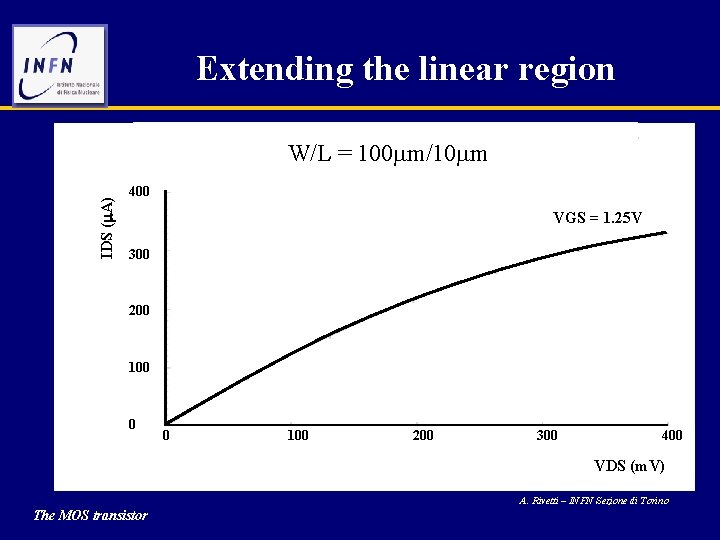

Extending the linear region IDS (m. A) W/L = 100 mm/10 mm 400 VGS = 1. 25 V 300 200 100 0 0 100 200 300 400 VDS (m. V) A. Rivetti – INFN Sezione di Torino The MOS transistor

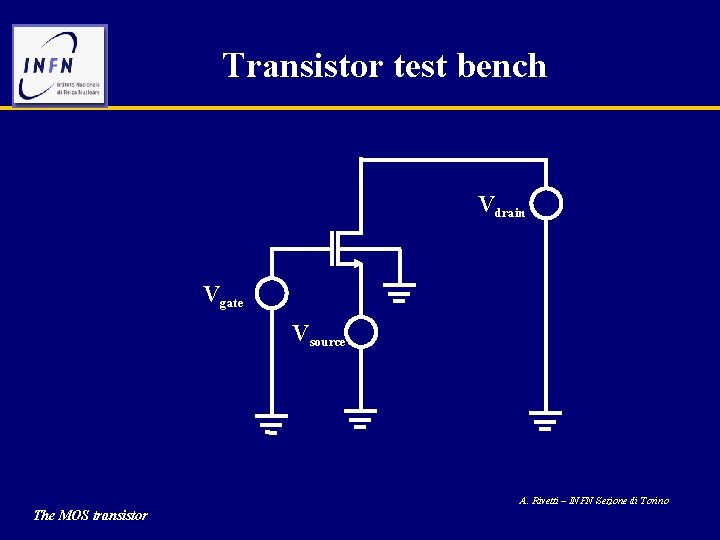

Transistor test bench Vdrain Vgate Vsource A. Rivetti – INFN Sezione di Torino The MOS transistor

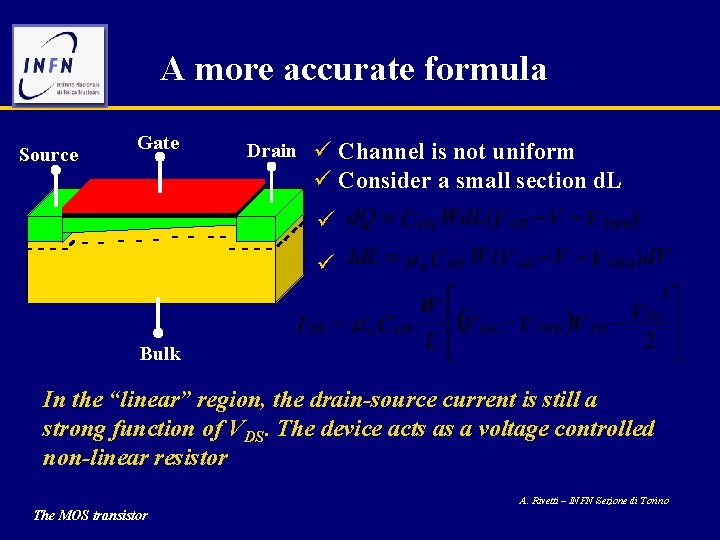

A more accurate formula Source Gate Drain - - - -- - ü Channel is not uniform ü Consider a small section d. L ü ü Bulk In the “linear” region, the drain-source current is still a strong function of VDS. The device acts as a voltage controlled non-linear resistor A. Rivetti – INFN Sezione di Torino The MOS transistor

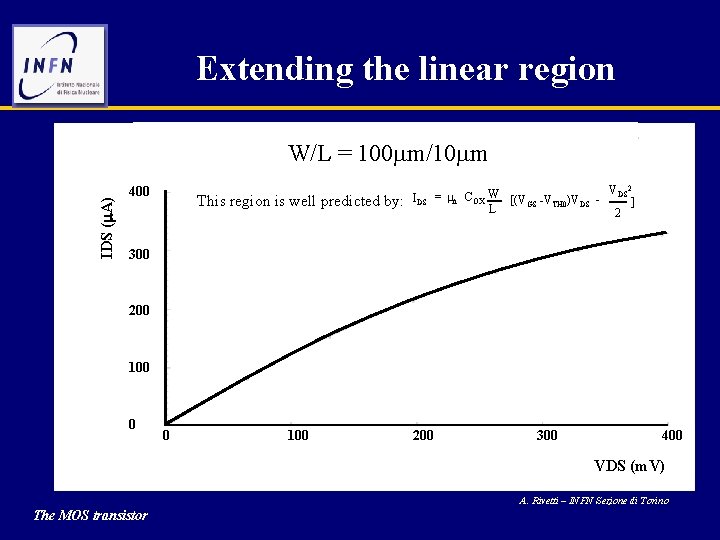

Extending the linear region IDS (m. A) W/L = 100 mm/10 mm 400 This region is well predicted by: IDS = mn COX W [(VGS -VTH 0)VDS L VDS 2 2 ] 300 200 100 0 0 100 200 300 400 VDS (m. V) A. Rivetti – INFN Sezione di Torino The MOS transistor

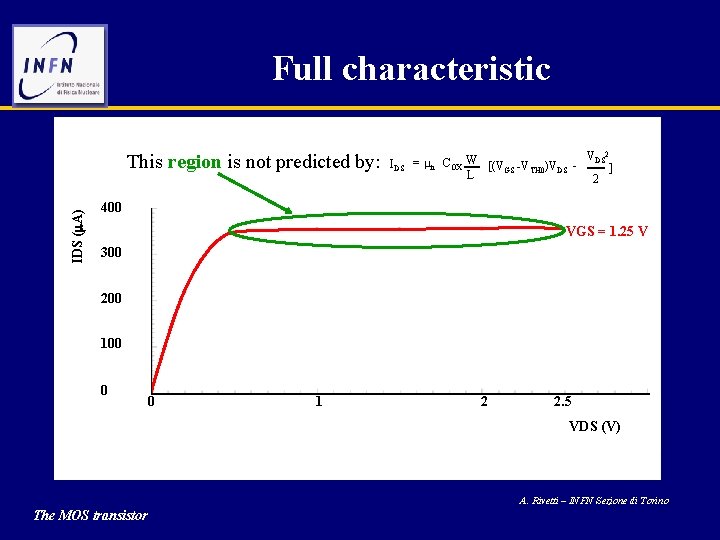

Full characteristic IDS (m. A) This region is not predicted by: IDS = mn COX W [(VGS -VTH 0)VDS L VDS 2 2 ] 400 VGS = 1. 25 V 300 200 100 0 0 1 2 2. 5 VDS (V) A. Rivetti – INFN Sezione di Torino The MOS transistor

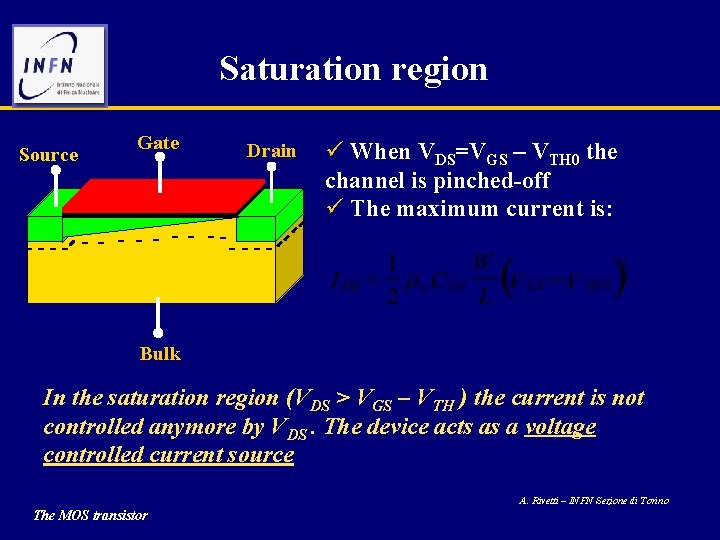

Saturation region Source Gate Drain - - - -- - ü When VDS=VGS – VTH 0 the channel is pinched-off ü The maximum current is: Bulk In the saturation region (VDS > VGS – VTH ) the current is not controlled anymore by VDS. The device acts as a voltage controlled current source A. Rivetti – INFN Sezione di Torino The MOS transistor

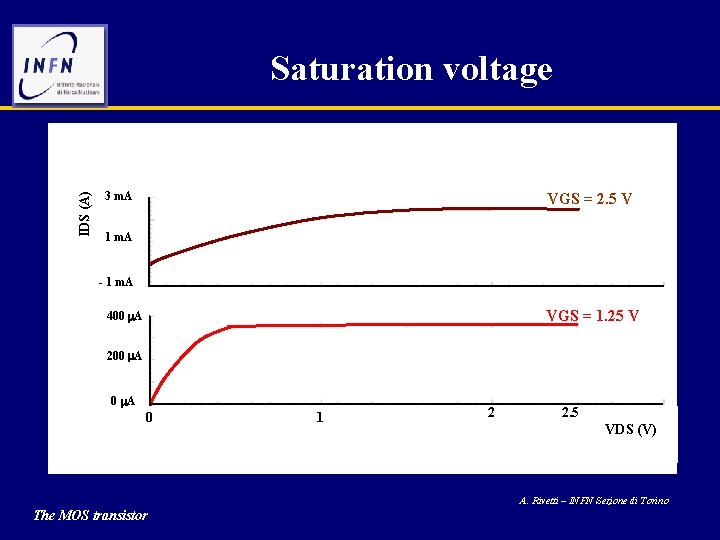

IDS (A) Saturation voltage 3 m. A VGS = 2. 5 V 1 m. A - 1 m. A VGS = 1. 25 V 400 m. A 200 m. A 0 1 2 2. 5 VDS (V) A. Rivetti – INFN Sezione di Torino The MOS transistor

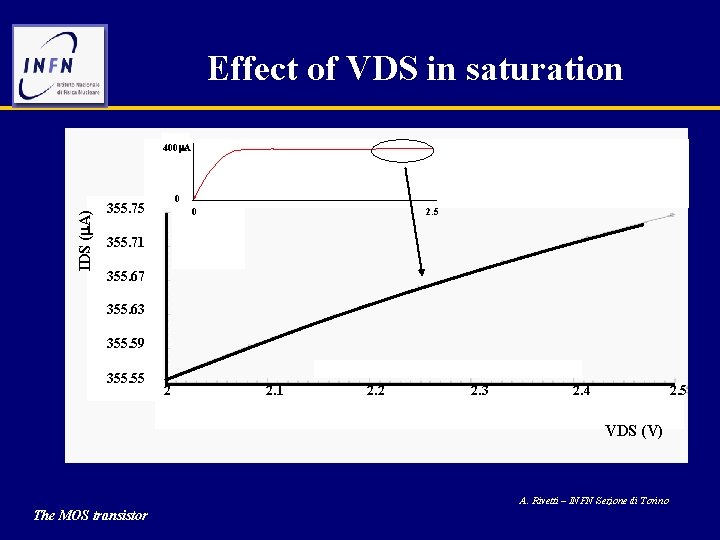

Effect of VDS in saturation IDS (m. A) 400 m. A 0 355. 75 0 2. 5 355. 71 355. 67 355. 63 355. 59 355. 55 2 2. 1 2. 2 2. 3 2. 4 2. 5 VDS (V) A. Rivetti – INFN Sezione di Torino The MOS transistor

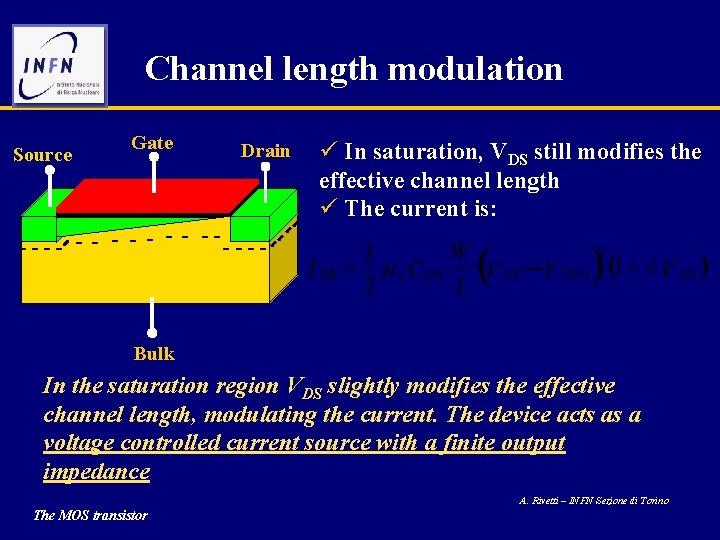

Channel length modulation Source Gate Drain - - - -- - ü In saturation, VDS still modifies the effective channel length ü The current is: Bulk In the saturation region VDS slightly modifies the effective channel length, modulating the current. The device acts as a voltage controlled current source with a finite output impedance A. Rivetti – INFN Sezione di Torino The MOS transistor

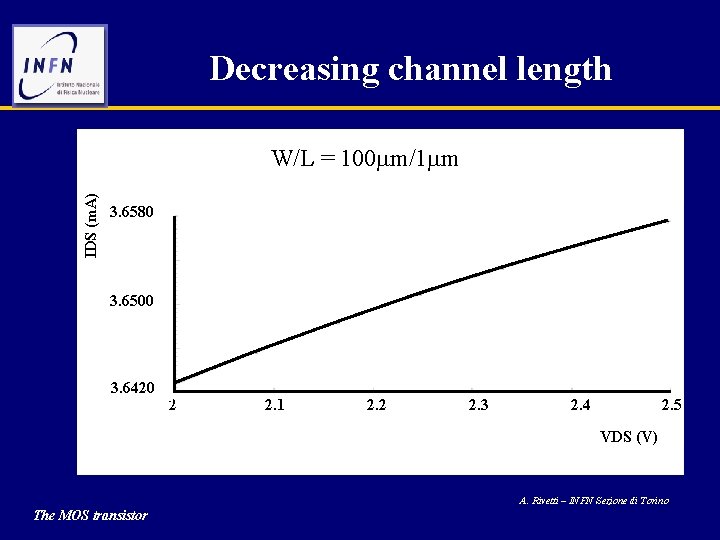

Decreasing channel length IDS (m. A) W/L = 100 mm/1 mm 3. 6580 3. 6500 3. 6420 2 2. 1 2. 2 2. 3 2. 4 2. 5 VDS (V) A. Rivetti – INFN Sezione di Torino The MOS transistor

Effect of VGS IDS (m. A) W/L = 100 mm/1 mm 30 20 10 0 -10 0 1 2 2. 5 VDS (V) A. Rivetti – INFN Sezione di Torino The MOS transistor

The threshold voltage VTH = f. MS + 2 f. F + QB COX - QOX COX A. Rivetti – INFN Sezione di Torino The MOS transistor

The body effect What happens to the current if we raise Vsource and Vgate simultaneously, keeping VGS and VDS constant? Vdrain Vgate Vsource A. Rivetti – INFN Sezione di Torino The MOS transistor

The body effect A. Rivetti – INFN Sezione di Torino The MOS transistor

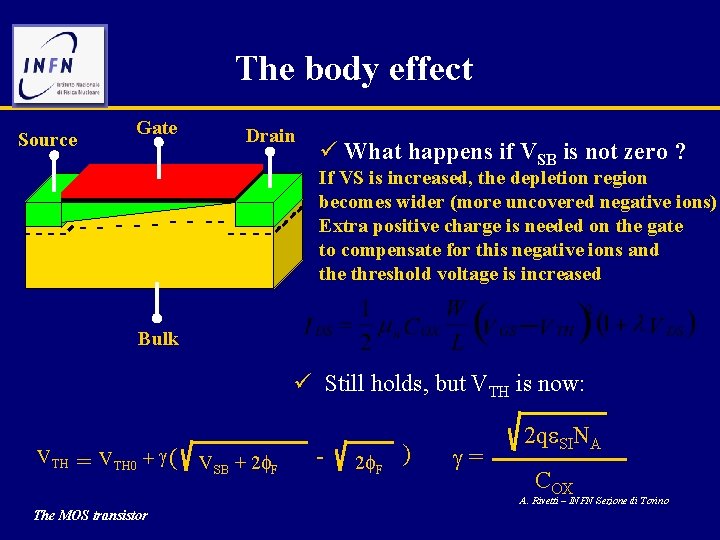

The body effect Source Gate Drain - - - -- - ü What happens if VSB is not zero ? If VS is increased, the depletion region becomes wider (more uncovered negative ions) Extra positive charge is needed on the gate to compensate for this negative ions and the threshold voltage is increased Bulk ü Still holds, but VTH is now: VTH = VTH 0 + g ( VSB + 2 f. F - 2 f. F ) g= 2 qe. SINA COX A. Rivetti – INFN Sezione di Torino The MOS transistor

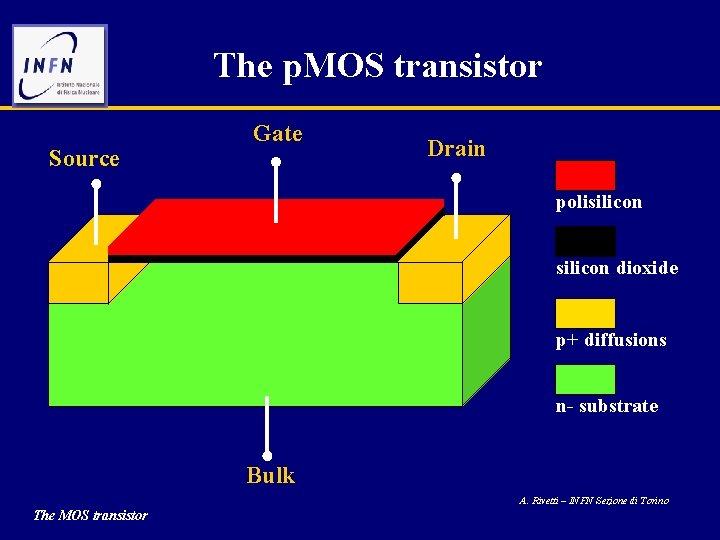

The p. MOS transistor Source Gate Drain polisilicon dioxide p+ diffusions n- substrate Bulk A. Rivetti – INFN Sezione di Torino The MOS transistor

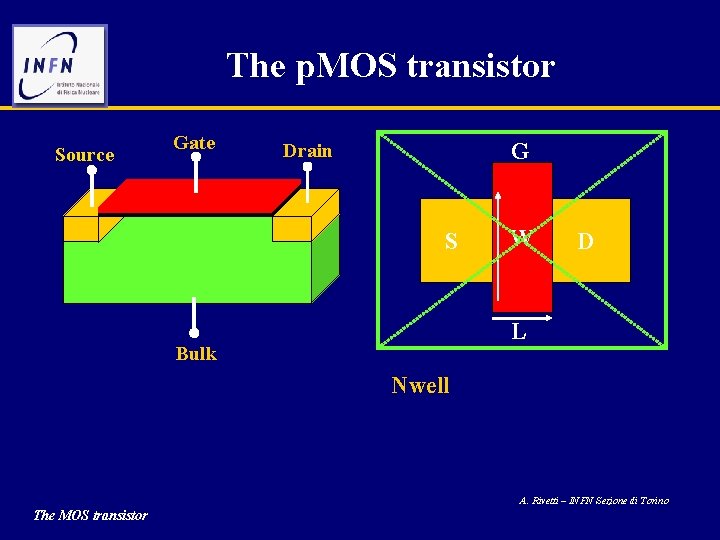

The p. MOS transistor Source Gate G Drain S W D L Bulk Nwell A. Rivetti – INFN Sezione di Torino The MOS transistor

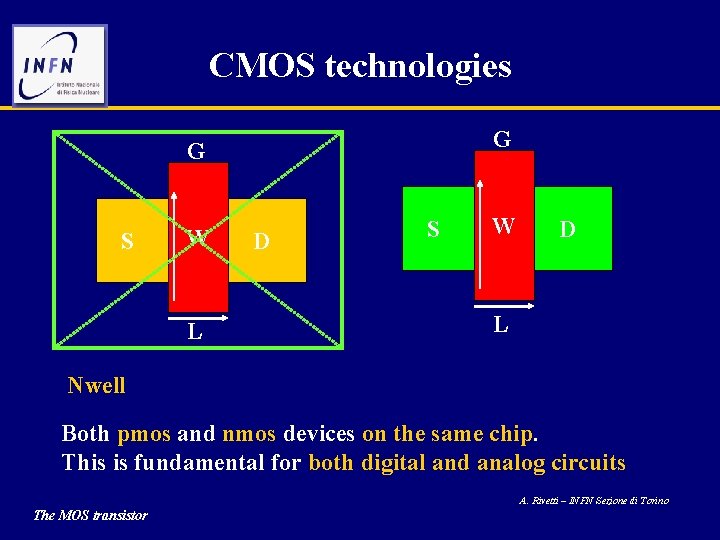

CMOS technologies G G S W L D S W D L Nwell Both pmos and nmos devices on the same chip. This is fundamental for both digital and analog circuits A. Rivetti – INFN Sezione di Torino The MOS transistor

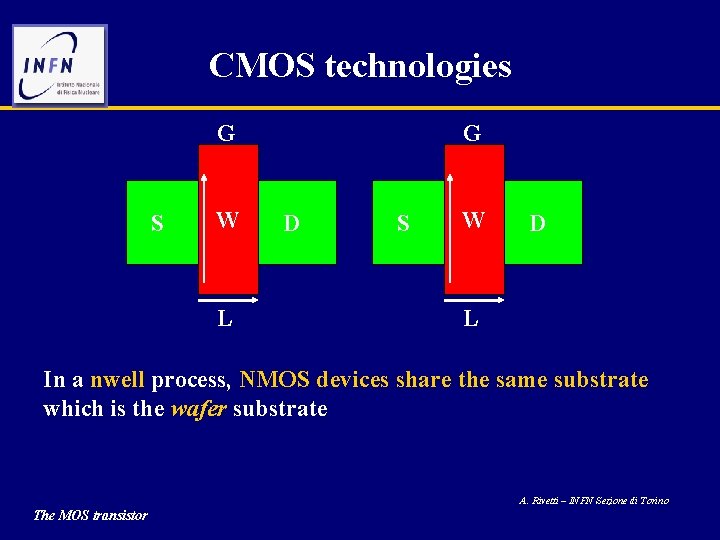

CMOS technologies G S W L G D S W D L In a nwell process, NMOS devices share the same substrate which is the wafer substrate A. Rivetti – INFN Sezione di Torino The MOS transistor

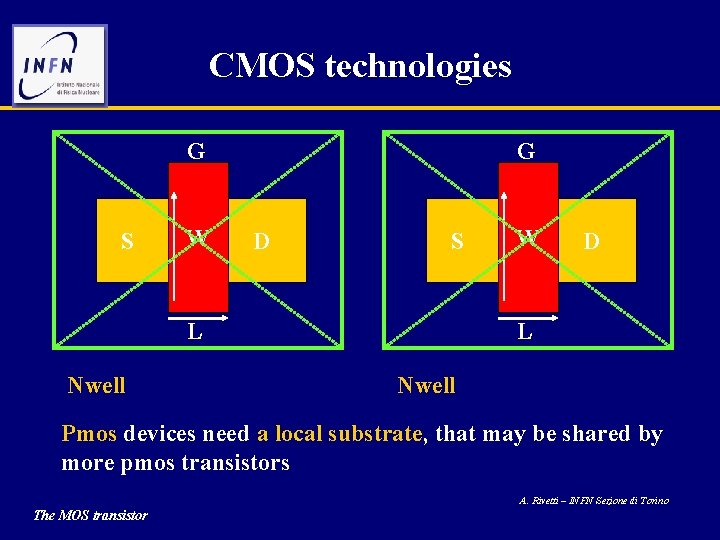

CMOS technologies G S W G D S L Nwell W D L Nwell Pmos devices need a local substrate, that may be shared by more pmos transistors A. Rivetti – INFN Sezione di Torino The MOS transistor

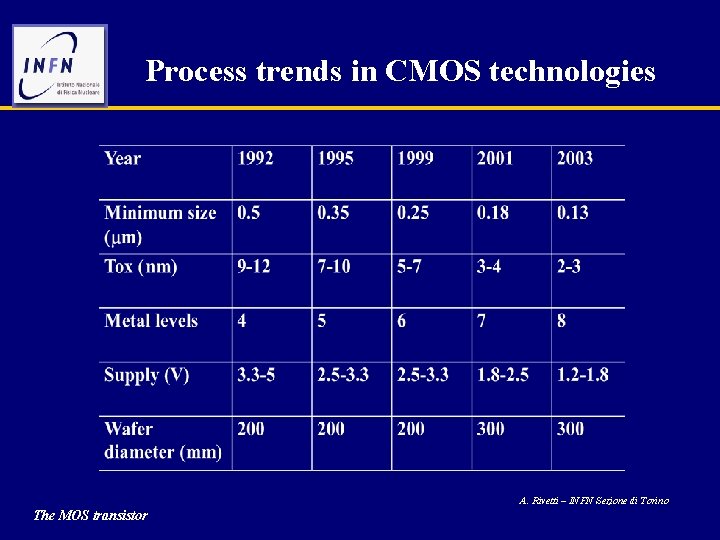

Process trends in CMOS technologies A. Rivetti – INFN Sezione di Torino The MOS transistor

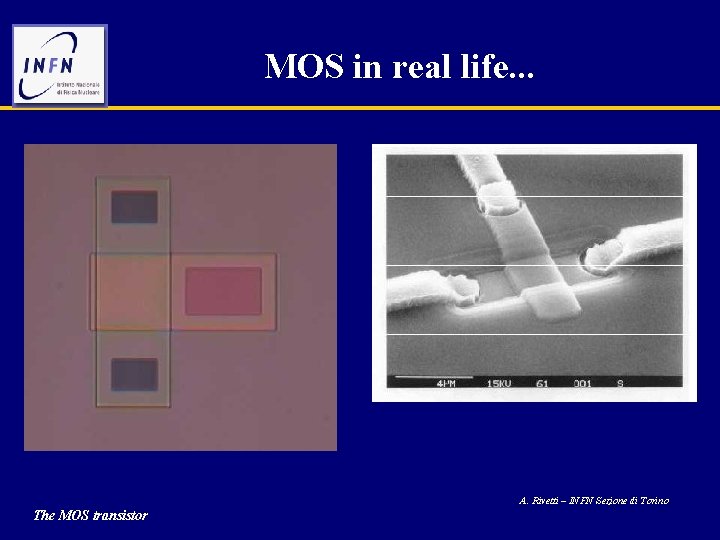

MOS in real life. . . A. Rivetti – INFN Sezione di Torino The MOS transistor

Metal interconnections A. Rivetti – INFN Sezione di Torino The MOS transistor

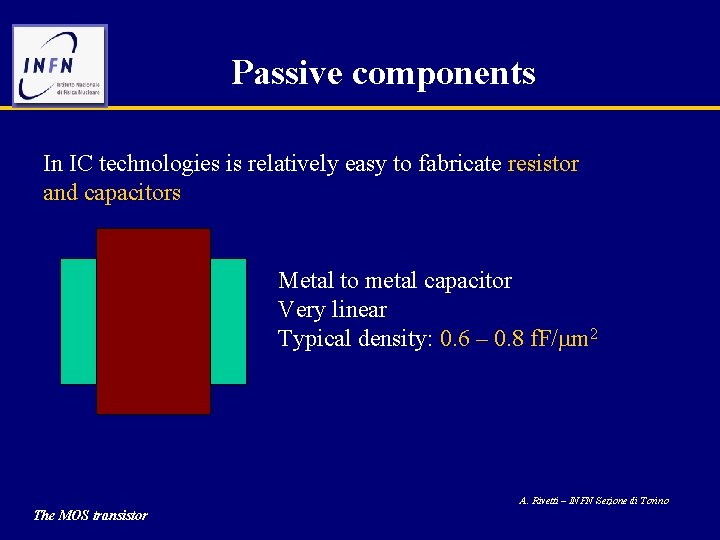

Passive components In IC technologies is relatively easy to fabricate resistor and capacitors Metal to metal capacitor Very linear Typical density: 0. 6 – 0. 8 f. F/mm 2 A. Rivetti – INFN Sezione di Torino The MOS transistor

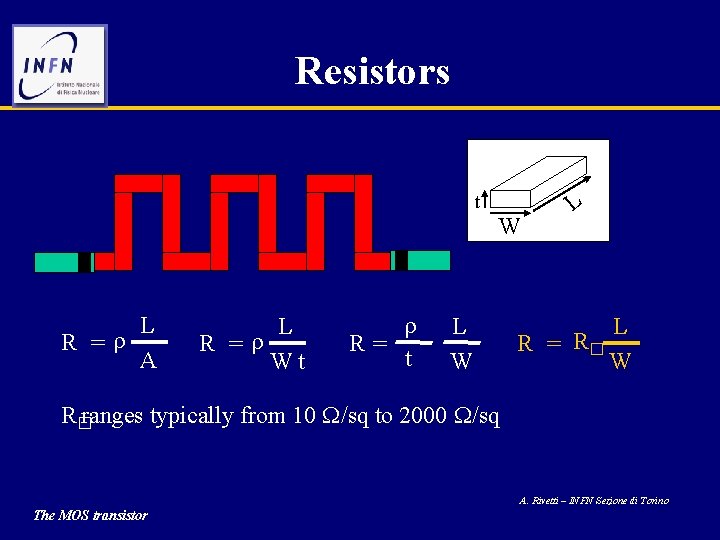

Resistors t W R =r L A L R =r Wt r R= t L W L L R = R� W R�ranges typically from 10 W/sq to 2000 W/sq A. Rivetti – INFN Sezione di Torino The MOS transistor

- Slides: 43