Baby MIND Synchronization at JPARC Georgi Mitev 20102021

Baby MIND Synchronization at J-PARC Georgi Mitev 20/10/2021 1

Baby MIND 20/10/2021 2

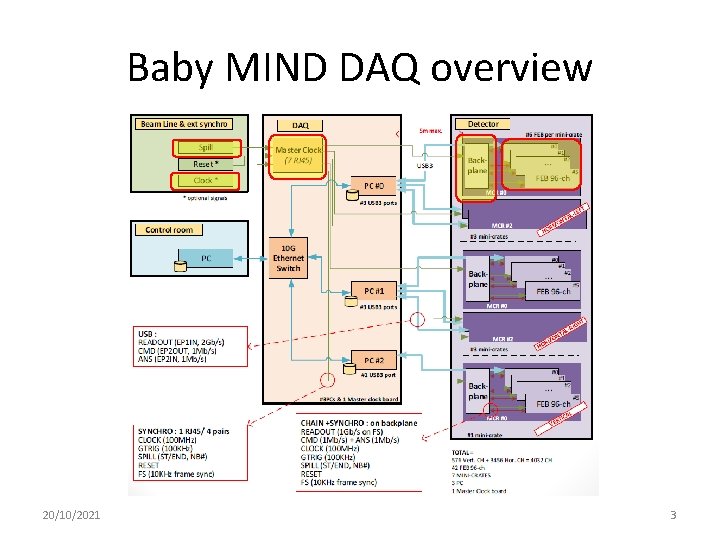

Baby MIND DAQ overview 20/10/2021 3

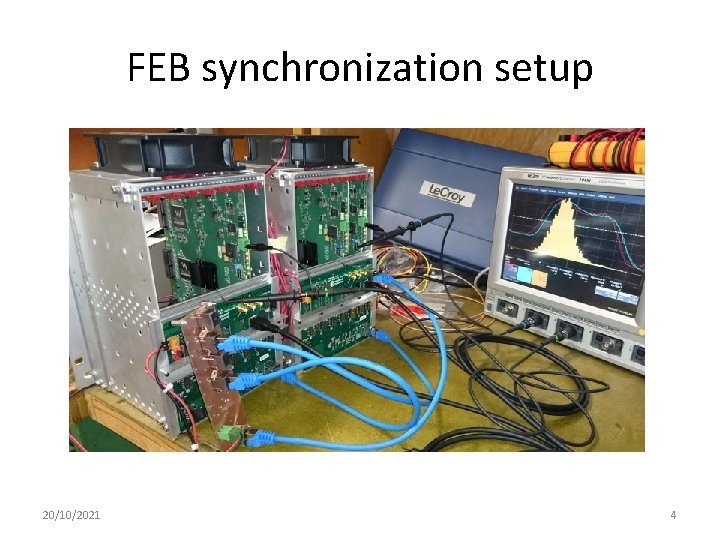

FEB synchronization setup 20/10/2021 4

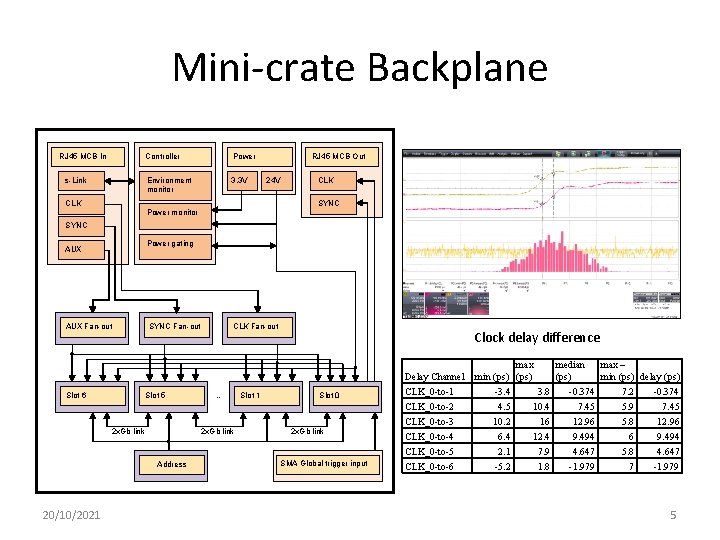

Mini-crate Backplane RJ 45 MCB In s-Link Controller Power Environment monitor 3. 3 V RJ 45 MCB Out 24 V CLK SYNC Power monitor SYNC Power gating AUX Fan-out Slot 6 SYNC Fan-out Slot 5 2 x. Gb link … 2 x. Gb link Address 20/10/2021 CLK Fan-out Slot 1 Clock delay difference Slot 0 2 x. Gb link SMA Global trigger input Delay Channel CLK_0 -to-1 CLK_0 -to-2 CLK_0 -to-3 CLK_0 -to-4 CLK_0 -to-5 CLK_0 -to-6 max median max – min (ps) min (ps) delay (ps) -3. 4 3. 8 -0. 374 7. 2 -0. 374 4. 5 10. 4 7. 45 5. 9 7. 45 10. 2 16 12. 96 5. 8 12. 96 6. 4 12. 4 9. 494 6 9. 494 2. 1 7. 9 4. 647 5. 8 4. 647 -5. 2 1. 8 -1. 979 7 -1. 979 5

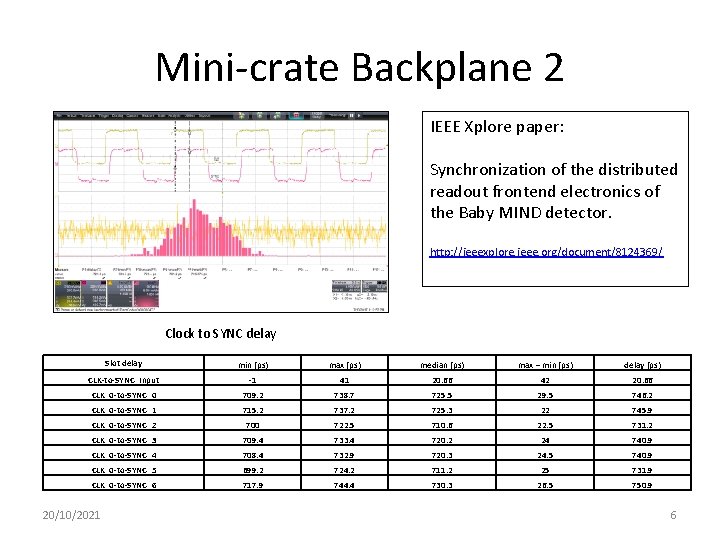

Mini-crate Backplane 2 IEEE Xplore paper: Synchronization of the distributed readout frontend electronics of the Baby MIND detector. http: //ieeexplore. ieee. org/document/8124369/ Clock to SYNC delay Slot delay min (ps) max (ps) median (ps) max – min (ps) delay (ps) CLK-to-SYNC_Input -1 41 20. 66 42 20. 66 CLK_0 -to-SYNC_0 709. 2 738. 7 725. 5 29. 5 746. 2 CLK_0 -to-SYNC_1 715. 2 737. 2 725. 3 22 745. 9 CLK_0 -to-SYNC_2 700 722. 5 710. 6 22. 5 731. 2 CLK_0 -to-SYNC_3 709. 4 733. 4 720. 2 24 740. 9 CLK_0 -to-SYNC_4 708. 4 732. 9 720. 3 24. 5 740. 9 CLK_0 -to-SYNC_5 699. 2 724. 2 711. 2 25 731. 9 CLK_0 -to-SYNC_6 717. 9 744. 4 730. 3 26. 5 750. 9 20/10/2021 6

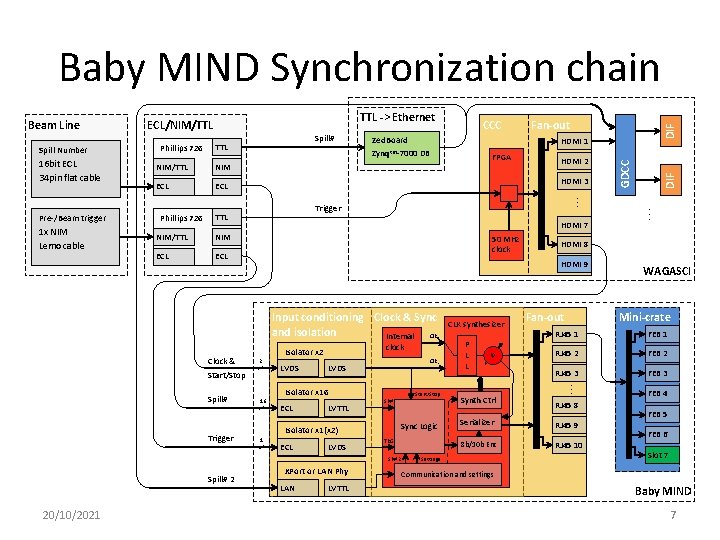

Baby MIND Synchronization chain 1 x NIM Lemo cable NIM ECL Phillips 726 NIM ECL FPGA Trigger HDMI 7 50 MHz clock 0 Trigger clock Isolator x 2 2 Start/Stop Spill# 16 LVDS Clk 1 LVDS Isolator x 16 ECL LVTTL Start/Stop SP# Sync Logic Isolator x 1(x 2) 1 ECL LVDS TRG SP# 2 Spill# 2 20/10/2021 XPort or LAN Phy LAN LVTTL DIF HDMI 8 HDMI 9 Input conditioning Clock & Sync and isolation Clk Internal Clock & HDMI 2 HDMI 3 TTL NIM/TTL HDMI 1 CLK synthesizer P L L φ Synth Ctrl Fan-out WAGASCI Mini-crate RJ 45 1 FEB 1 RJ 45 2 FEB 2 RJ 45 3 FEB 4 RJ 45 8 Serializer RJ 45 9 8 b/10 b Enc RJ 45 10 Settings DIF NIM/TTL Fan-out . . . Pre-/Beam trigger TTL CCC Zed. Board Zynqtm-7000 DB GDCC 16 bit ECL 34 pin flat cable Phillips 726 Spill# . . . Spill Number TTL -> Ethernet ECL/NIM/TTL . . . Beam Line FEB 5 FEB 6 Slot 7 Communication and settings Baby MIND 7

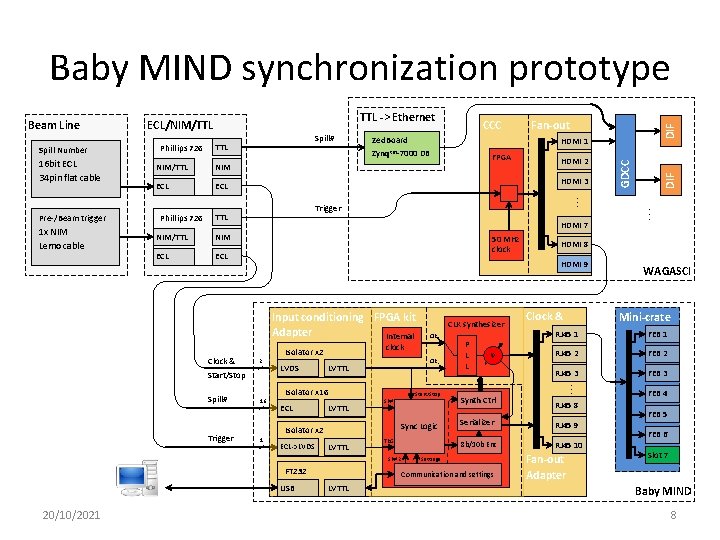

Baby MIND synchronization prototype 1 x NIM Lemo cable NIM ECL Phillips 726 NIM ECL HDMI 7 50 MHz clock Trigger Isolator x 2 2 16 LVDS LVTTL Start/Stop SP# Sync Logic Isolator x 2 1 ECL->LVDS LVTTL FT 232 USB Clk 0 Clk 1 LVTTL Isolator x 16 ECL CLK synthesizer clock TRG SP# 2 20/10/2021 P L L φ Synth Ctrl Clock & Mini-crate FEB 1 RJ 45 2 FEB 2 RJ 45 3 FEB 4 RJ 45 8 RJ 45 9 8 b/10 b Enc RJ 45 10 Settings WAGASCI RJ 45 1 Serializer Communication and settings LVTTL DIF HDMI 8 HDMI 9 Start/Stop Spill# HDMI 2 Trigger Input conditioning FPGA kit Adapter Internal Clock & FPGA HDMI 3 TTL NIM/TTL HDMI 1 DIF NIM/TTL Fan-out . . . Pre-/Beam trigger TTL CCC Zed. Board Zynqtm-7000 DB GDCC 16 bit ECL 34 pin flat cable Phillips 726 Spill# . . . Spill Number TTL -> Ethernet ECL/NIM/TTL . . . Beam Line Fan-out Adapter FEB 5 FEB 6 Slot 7 Baby MIND 8

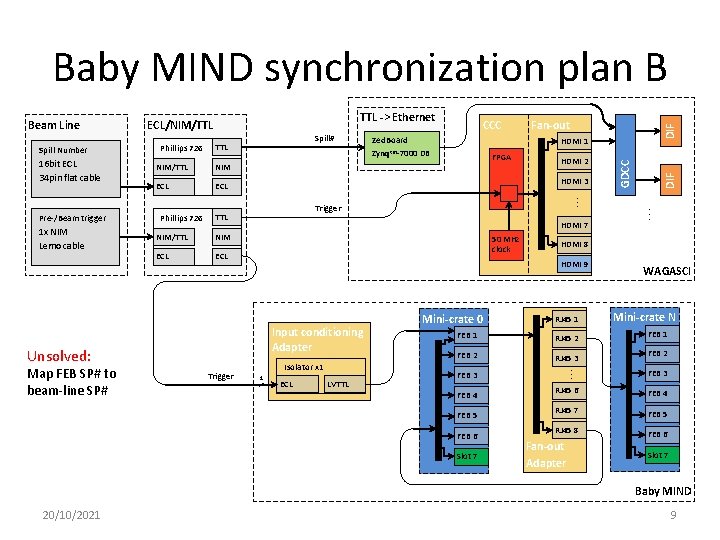

Baby MIND synchronization plan B 1 x NIM Lemo cable NIM ECL Phillips 726 NIM ECL HDMI 7 50 MHz clock Isolator x 1 1 ECL LVTTL DIF HDMI 8 HDMI 9 Input conditioning Adapter Trigger HDMI 2 Trigger Unsolved: Map FEB SP# to beam-line SP# FPGA HDMI 3 TTL NIM/TTL HDMI 1 Mini-crate 0 RJ 45 1 FEB 1 RJ 45 2 FEB 2 RJ 45 3 FEB 4 FEB 5 FEB 6 Slot 7 DIF NIM/TTL Fan-out . . . Pre-/Beam trigger TTL CCC Zed. Board Zynqtm-7000 DB GDCC 16 bit ECL 34 pin flat cable Phillips 726 Spill# . . . Spill Number TTL -> Ethernet ECL/NIM/TTL WAGASCI Mini-crate N FEB 1 FEB 2 . . . Beam Line FEB 3 RJ 45 6 FEB 4 RJ 45 7 FEB 5 RJ 45 8 Fan-out Adapter FEB 6 Slot 7 Baby MIND 20/10/2021 9

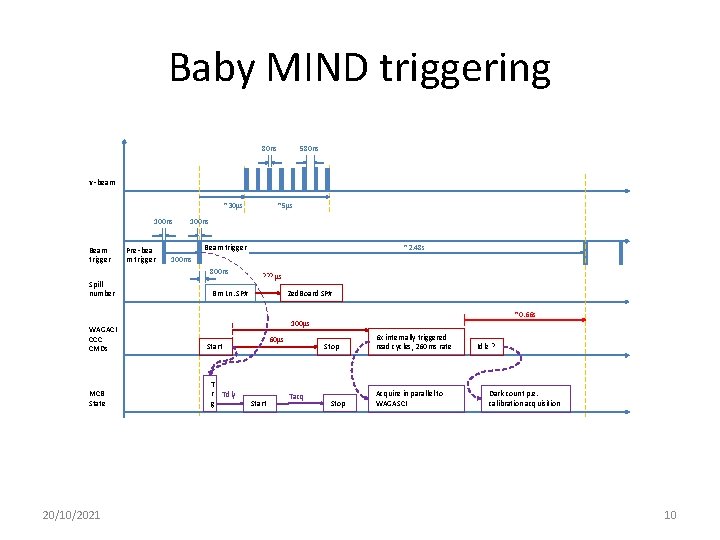

Baby MIND triggering 580 ns ν‑beam ~30μs 100 ns Beam trigger Pre‑bea m trigger 100 ns Beam trigger WAGACI CCC CMDs MCB State 20/10/2021 ~2. 48 s 100 ms 800 ns Spill number ~5μs ? ? ? μs Bm Ln. SP# Zed. Board SP# ~0. 66 s 100μs 60μs Start T r Tdly g Start Stop Tacq Stop 6 x internally triggered read cycles, 260 ms rate Acquire in parallel to WAGASCI Idle ? Dark count p. e. calibration acquisition 10

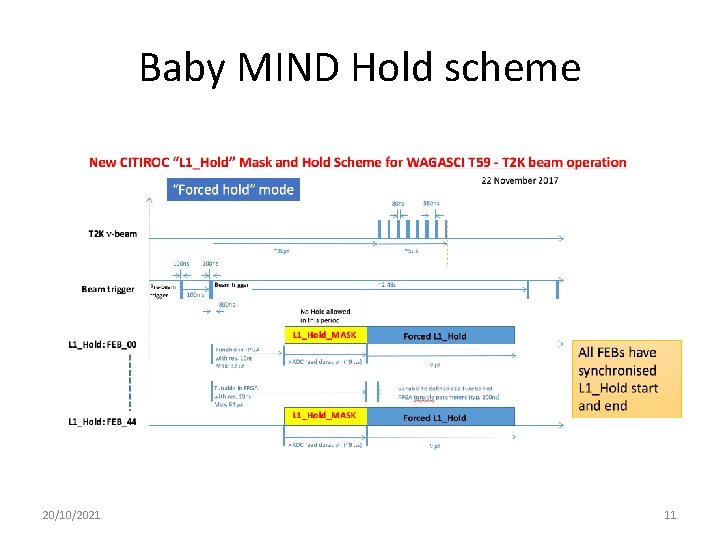

Baby MIND Hold scheme 20/10/2021 11

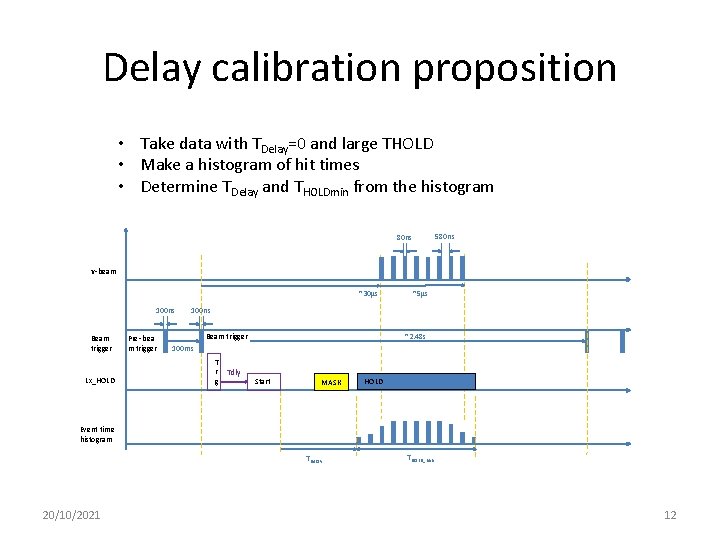

Delay calibration proposition • Take data with TDelay=0 and large THOLD • Make a histogram of hit times • Determine TDelay and THOLDmin from the histogram 580 ns ν‑beam ~30μs 100 ns Beam trigger Lx_HOLD Pre‑bea m trigger ~5μs 100 ns Beam trigger ~2. 48 s 100 ms T r Tdly g Start MASK HOLD Event time histogram TDelay 20/10/2021 THOLD_min 12

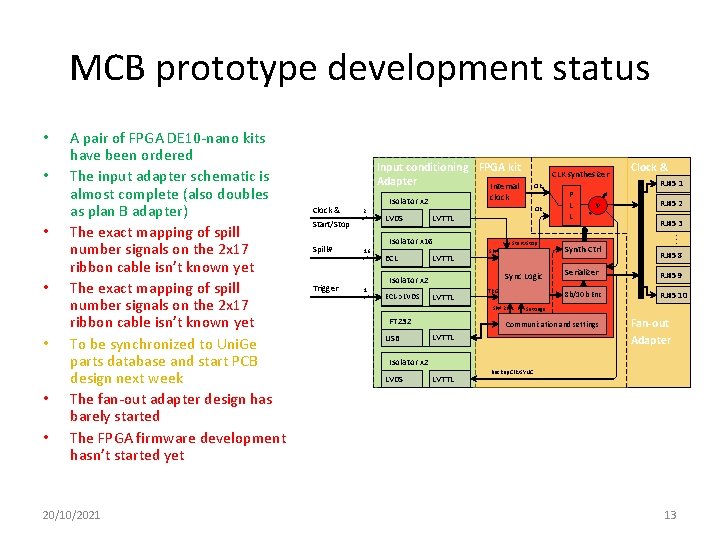

MCB prototype development status • • • A pair of FPGA DE 10 -nano kits have been ordered The input adapter schematic is almost complete (also doubles as plan B adapter) The exact mapping of spill number signals on the 2 x 17 ribbon cable isn’t known yet To be synchronized to Uni. Ge parts database and start PCB design next week The fan-out adapter design has barely started The FPGA firmware development hasn’t started yet 20/10/2021 Input conditioning FPGA kit Adapter Internal Clock & Start/Stop Spill# Trigger 16 LVDS Clk 1 LVTTL Isolator x 16 ECL LVTTL Start/Stop SP# Sync Logic Isolator x 2 1 ECL->LVDS LVTTL TRG SP# 2 FT 232 USB Clk 0 clock Isolator x 2 2 CLK synthesizer P L L φ Synth Ctrl Clock & RJ 45 1 RJ 45 2 RJ 45 3. . . • RJ 45 8 Serializer RJ 45 9 8 b/10 b Enc RJ 45 10 Settings Communication and settings LVTTL Fan-out Adapter Isolator x 2 LVDS LVTTL Backup Clk/SYNC 13

MCB installation and connectivity • Initial proposition to install the MCB inside the 6 U VME crate alongside GDCC/CCC was found hard to achieve. New solution is needed. • Powered from an outlet adapter • SYNC outputs - 8 CAT 6 cables to the Baby-MIND mini-crates • Computer control – USB or LAN connection via onboard USB/LAN serial converter • Clock signal input – LVDS on HDMI from CCC • Synchronization signals – ECL on ribbon cables from the pair of Philips scientific 726 modules • Cable lengths and installation paths TBD 20/10/2021 14

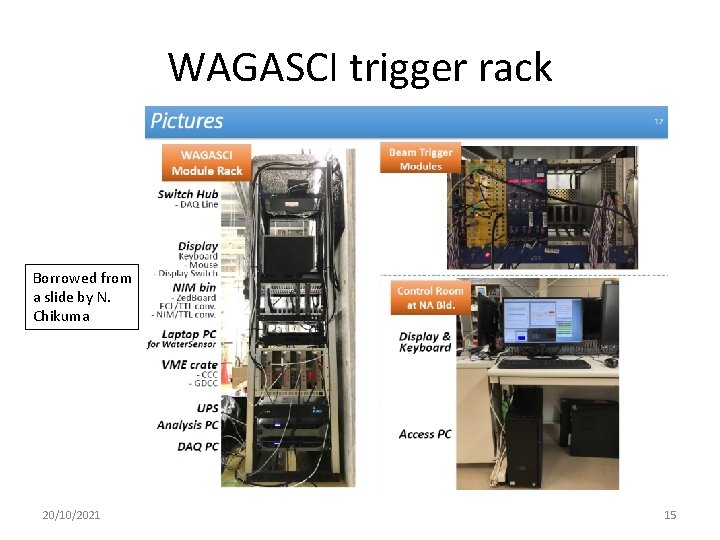

WAGASCI trigger rack Borrowed from a slide by N. Chikuma 20/10/2021 15

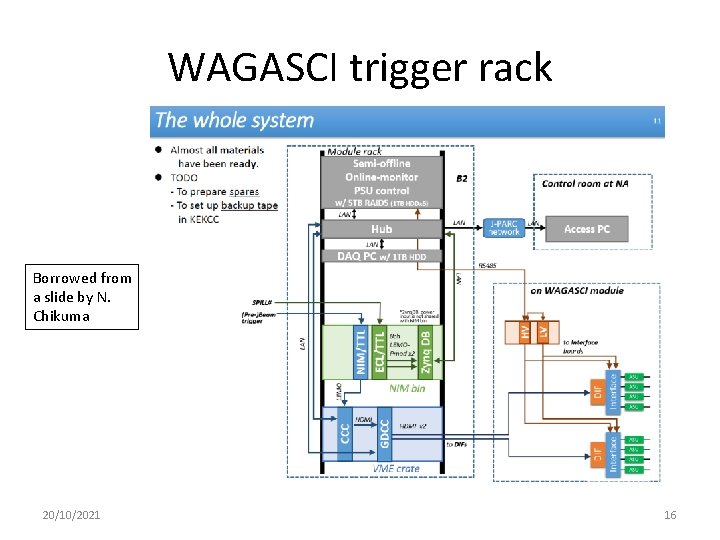

WAGASCI trigger rack Borrowed from a slide by N. Chikuma 20/10/2021 16

• Backup Slides 20/10/2021 17

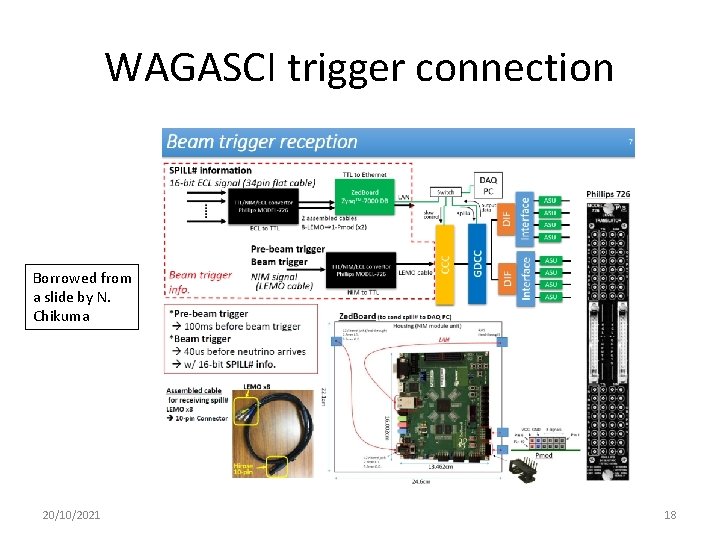

WAGASCI trigger connection Borrowed from a slide by N. Chikuma 20/10/2021 18

- Slides: 18