Bab 13 Rangkaian Logika Digital CMOS Pendahuluan n

Bab 13 Rangkaian Logika Digital CMOS

Pendahuluan n n Perkembangan teknologi digital saat ini didukung oleh teknologi CMOS Keuntungan teknologi CMOS – Daya rendah – Tidak mengalami degenerasi – Scaling lebih mudah

Rangkaian Logika Inverter n Simbol

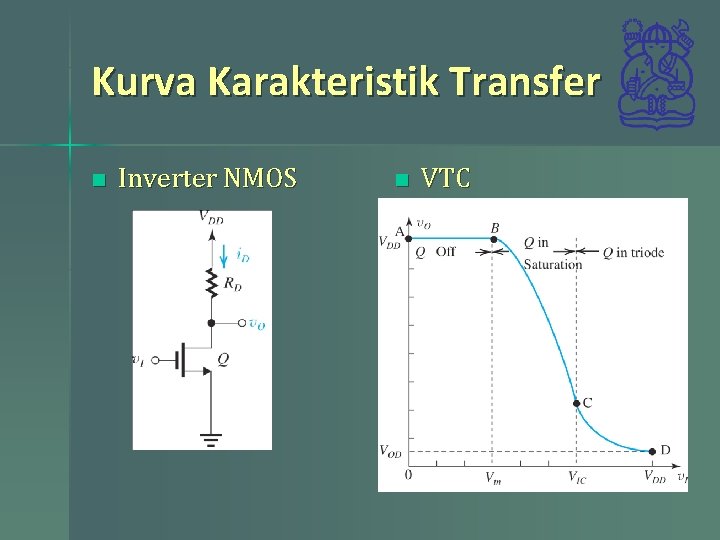

Kurva Karakteristik Transfer n Inverter NMOS n VTC

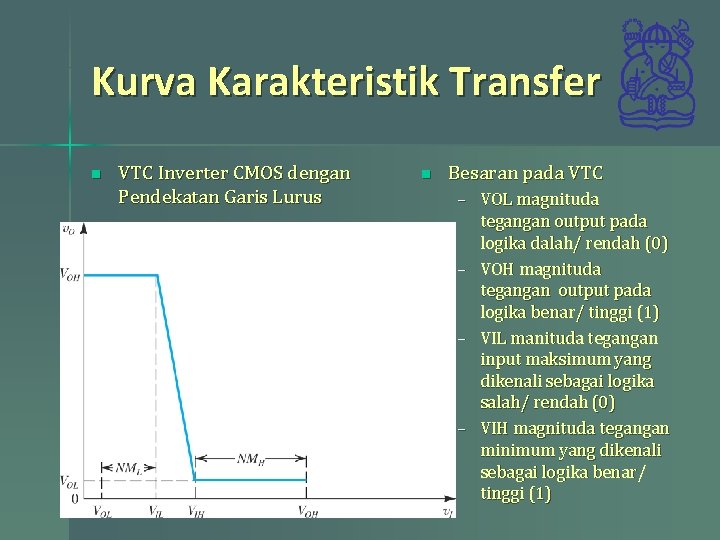

Kurva Karakteristik Transfer n VTC Inverter CMOS dengan Pendekatan Garis Lurus n Besaran pada VTC – VOL magnituda tegangan output pada logika dalah/ rendah (0) – VOH magnituda tegangan output pada logika benar/ tinggi (1) – VIL manituda tegangan input maksimum yang dikenali sebagai logika salah/ rendah (0) – VIH magnituda tegangan minimum yang dikenali sebagai logika benar/ tinggi (1)

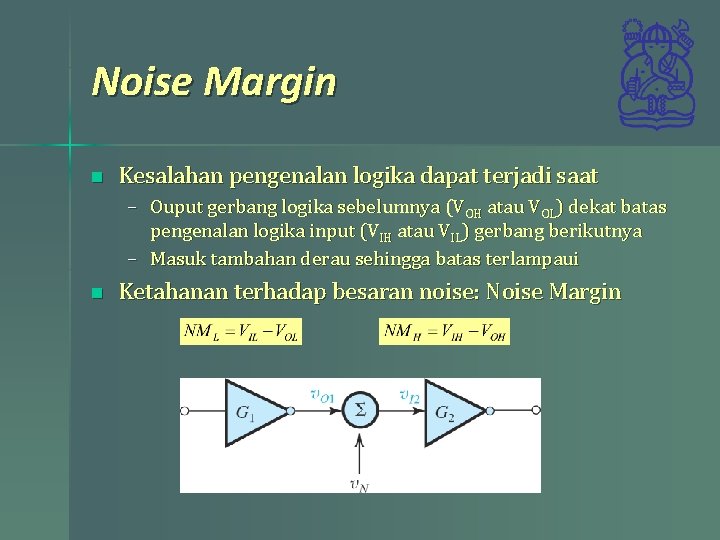

Noise Margin n Kesalahan pengenalan logika dapat terjadi saat – Ouput gerbang logika sebelumnya (VOH atau VOL) dekat batas pengenalan logika input (VIH atau VIL) gerbang berikutnya – Masuk tambahan derau sehingga batas terlampaui n Ketahanan terhadap besaran noise: Noise Margin

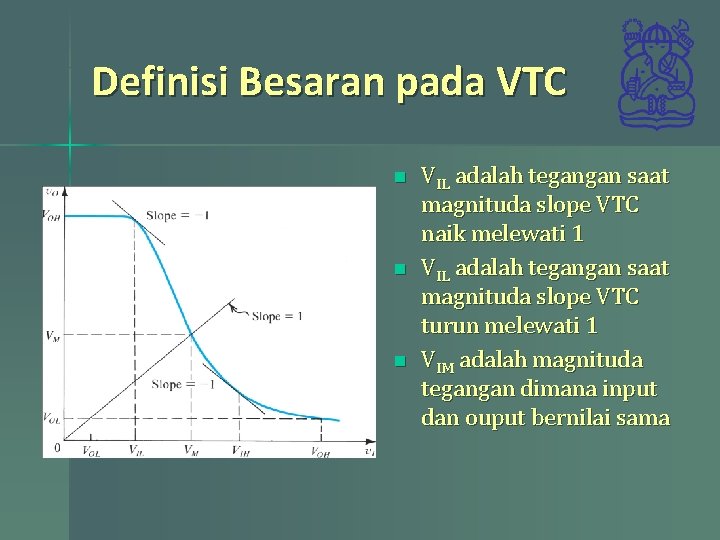

Definisi Besaran pada VTC n n n VIL adalah tegangan saat magnituda slope VTC naik melewati 1 VIL adalah tegangan saat magnituda slope VTC turun melewati 1 VIM adalah magnituda tegangan dimana input dan ouput bernilai sama

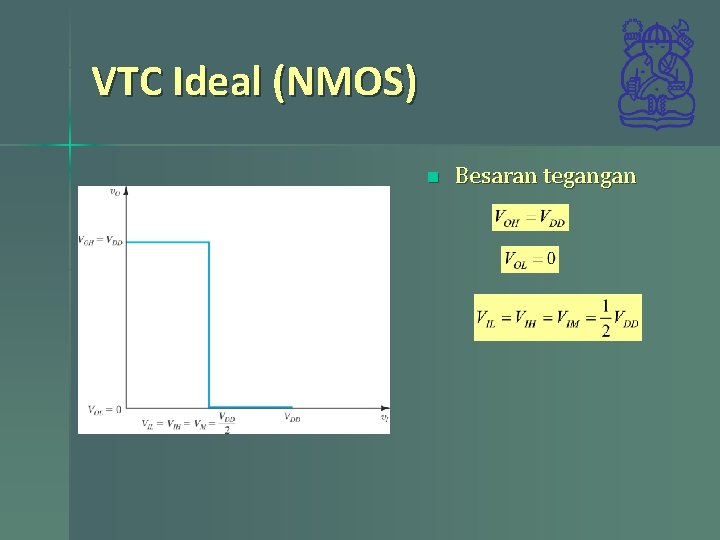

VTC Ideal (NMOS) n Besaran tegangan

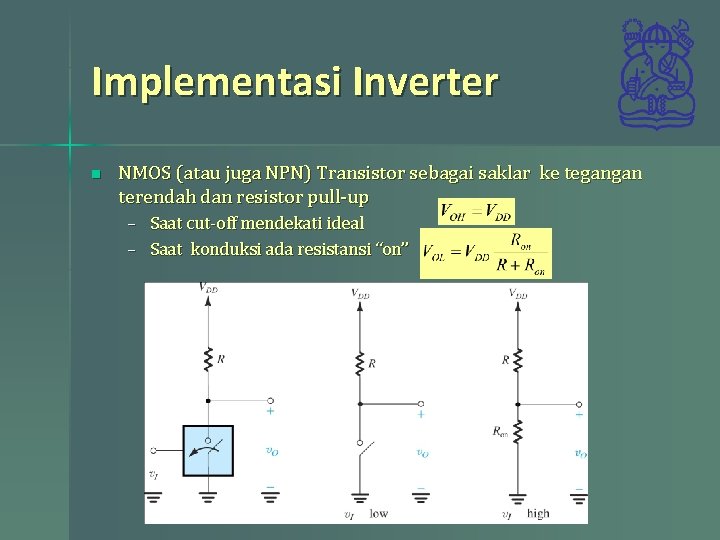

Implementasi Inverter n NMOS (atau juga NPN) Transistor sebagai saklar ke tegangan terendah dan resistor pull-up – Saat cut-off mendekati ideal – Saat konduksi ada resistansi “on”

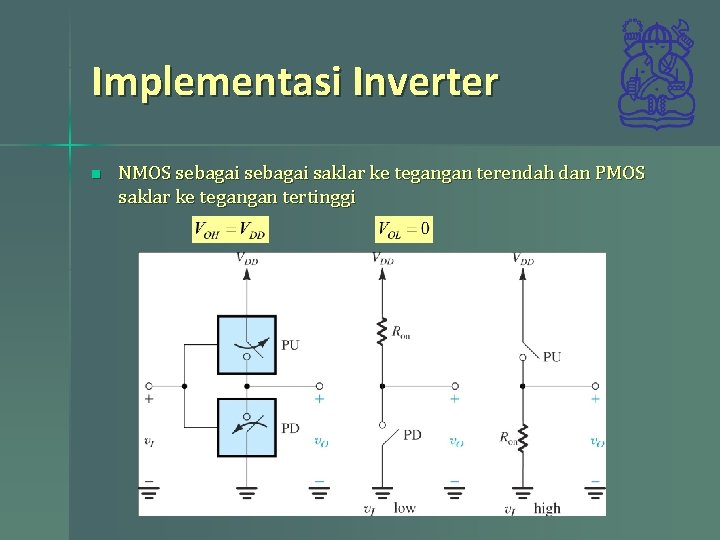

Implementasi Inverter n NMOS sebagai saklar ke tegangan terendah dan PMOS saklar ke tegangan tertinggi

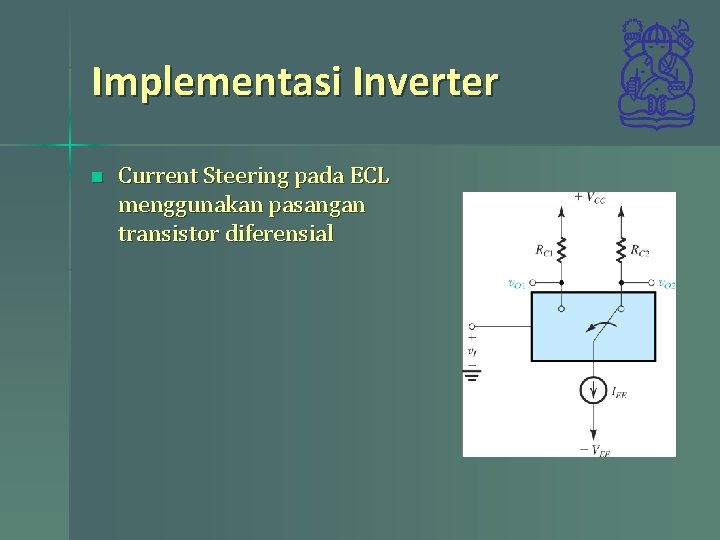

Implementasi Inverter n Current Steering pada ECL menggunakan pasangan transistor diferensial

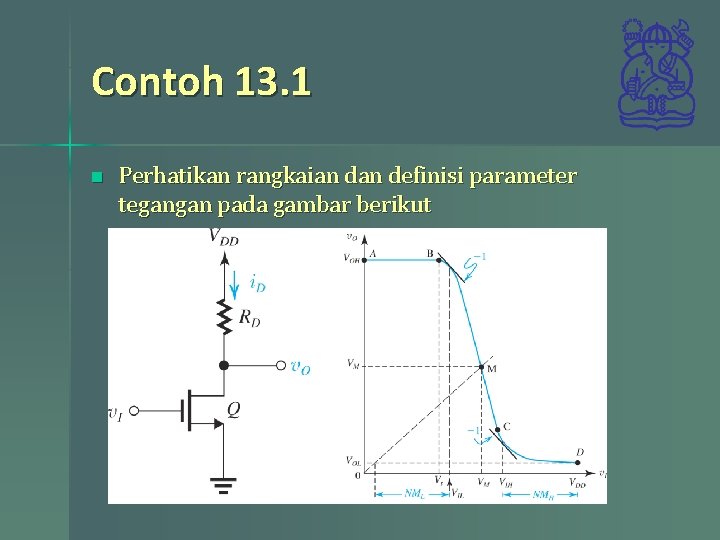

Contoh 13. 1 a) b) c) d) Turunkan persamaan VOH, VOL, VIH dan VIM (abaikan l), nyatakan dalam besaran VDD, Vt. dan kn. RD ≡ 1/Vx. Tunjukkan bahwa Vx adalah parameter perancangan inverter dan cari nilai Vx sehingga VIM=VDD/2. Carilah nilai numerik parameter di atas untuk VDD=1, 8 V dan Vt=0, 5 V dengan. Vx pada (b). Untuk kn’=300 u. A/V 2 dan W/L=1, 5, carilah nilai RD dan gunakan untuk menentukan disipasi rata-rata inverter dengan mengasumsikan logika nol dan satu masing-masing setengah perioda

Contoh 13. 1 n Perhatikan rangkaian definisi parameter tegangan pada gambar berikut

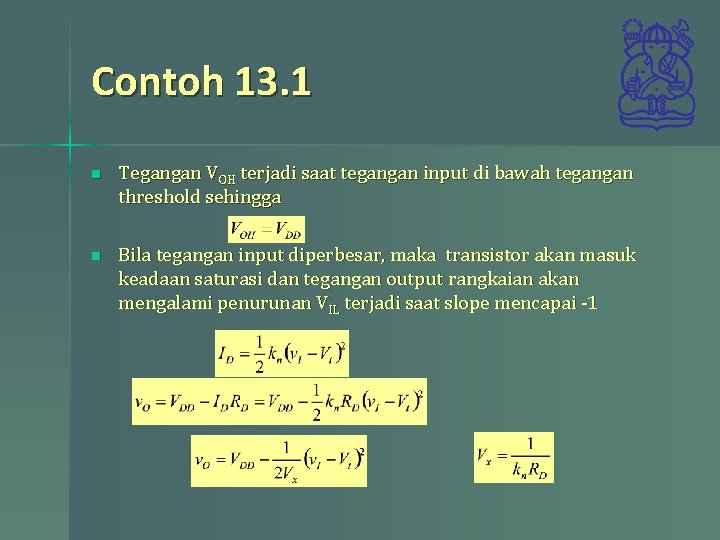

Contoh 13. 1 n Tegangan VOH terjadi saat tegangan input di bawah tegangan threshold sehingga n Bila tegangan input diperbesar, maka transistor akan masuk keadaan saturasi dan tegangan output rangkaian akan mengalami penurunan VIL terjadi saat slope mencapai -1

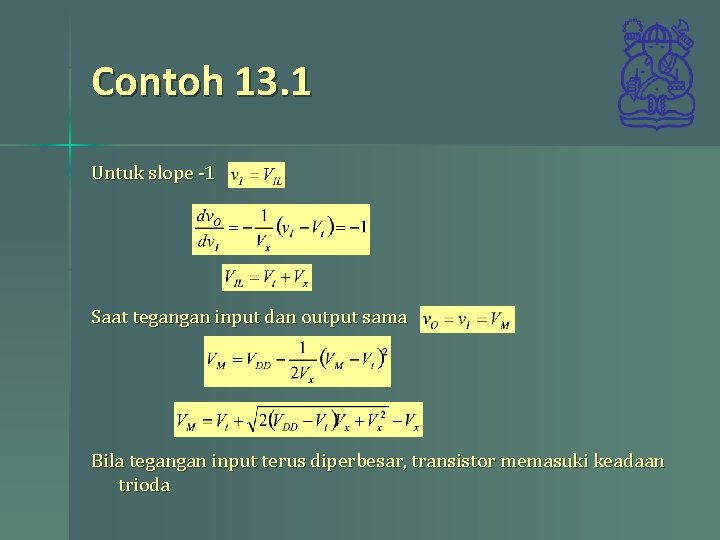

Contoh 13. 1 Untuk slope -1 Saat tegangan input dan output sama Bila tegangan input terus diperbesar, transistor memasuki keadaan trioda

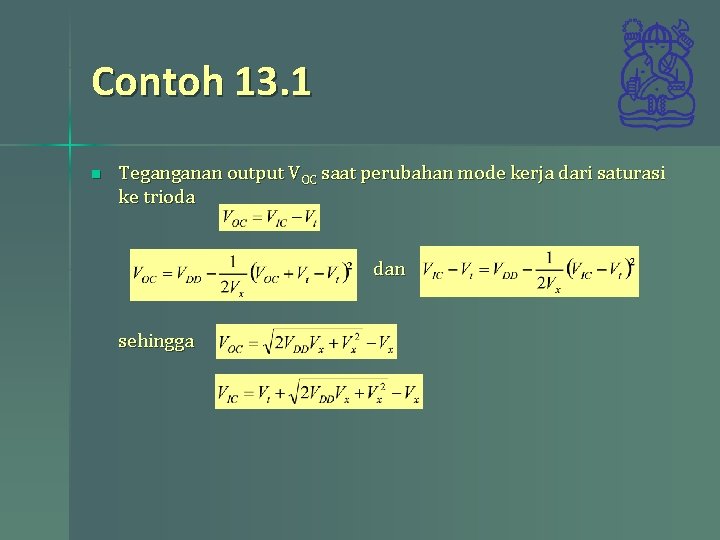

Contoh 13. 1 n Teganganan output VOC saat perubahan mode kerja dari saturasi ke trioda dan sehingga

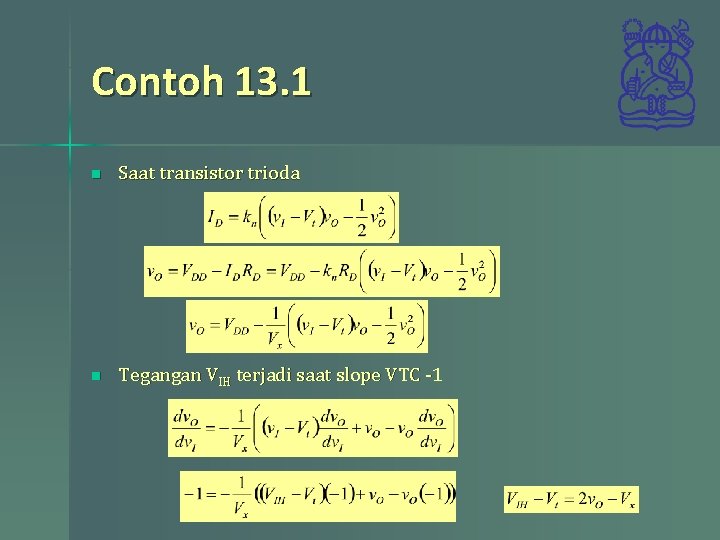

Contoh 13. 1 n Saat transistor trioda n Tegangan VIH terjadi saat slope VTC -1

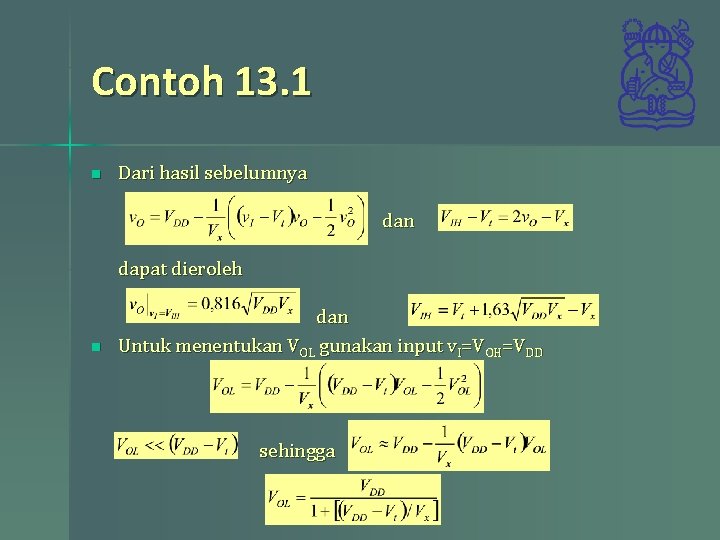

Contoh 13. 1 n Dari hasil sebelumnya dan dapat dieroleh n dan Untuk menentukan VOL gunakan input v. I=VOH=VDD sehingga

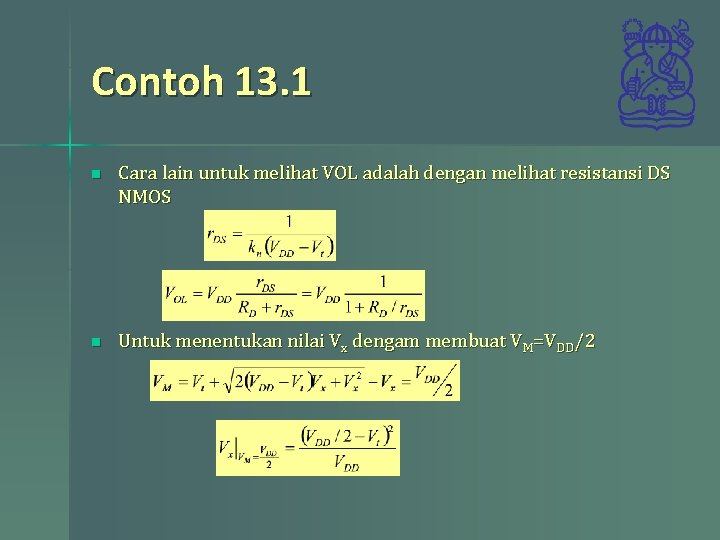

Contoh 13. 1 n Cara lain untuk melihat VOL adalah dengan melihat resistansi DS NMOS n Untuk menentukan nilai Vx dengam membuat VM=VDD/2

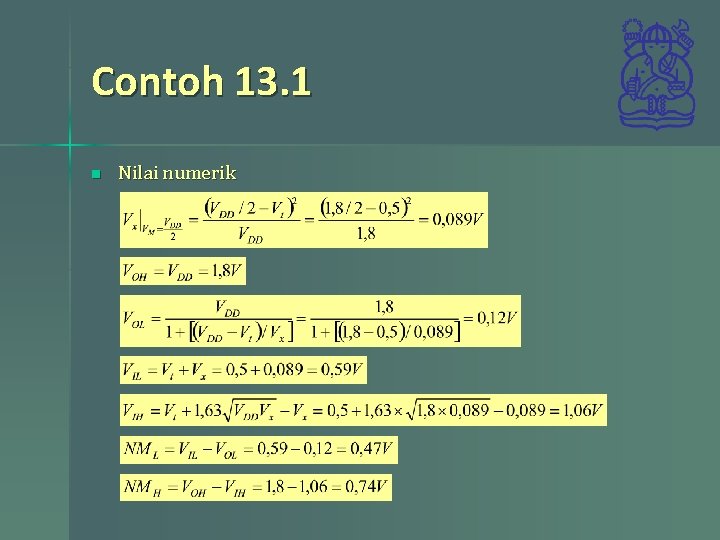

Contoh 13. 1 n Nilai numerik

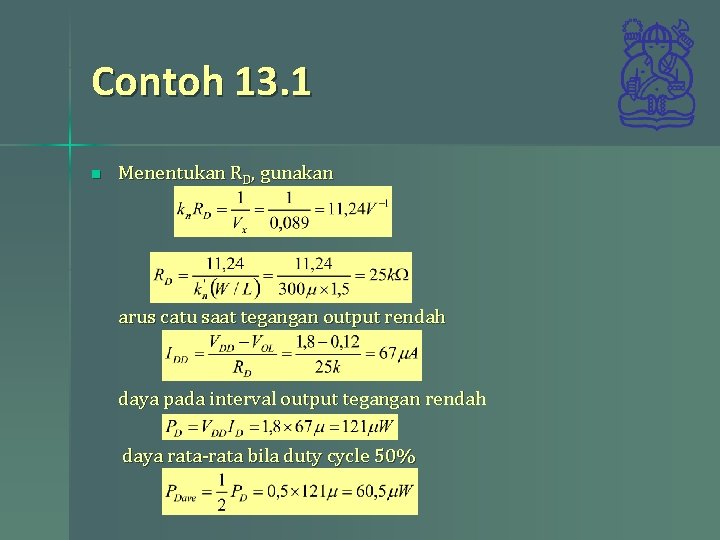

Contoh 13. 1 n Menentukan RD, gunakan arus catu saat tegangan output rendah daya pada interval output tegangan rendah daya rata-rata bila duty cycle 50%

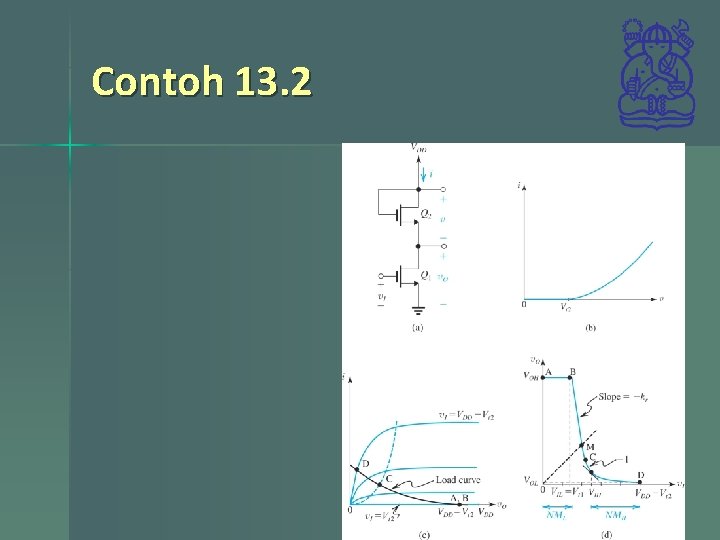

Contoh 13. 2

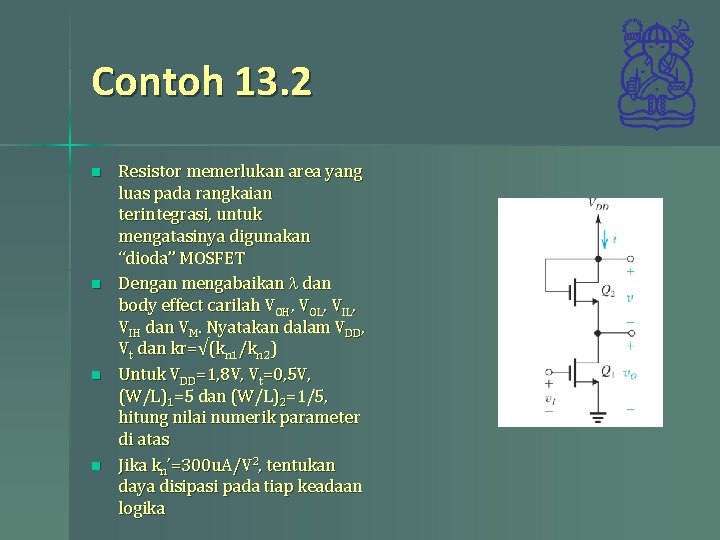

Contoh 13. 2 n n Resistor memerlukan area yang luas pada rangkaian terintegrasi, untuk mengatasinya digunakan “dioda” MOSFET Dengan mengabaikan l dan body effect carilah VOH, VOL, VIH dan VM. Nyatakan dalam VDD, Vt dan kr=√(kn 1/kn 2) Untuk VDD=1, 8 V, Vt=0, 5 V, (W/L)1=5 dan (W/L)2=1/5, hitung nilai numerik parameter di atas Jika kn’=300 u. A/V 2, tentukan daya disipasi pada tiap keadaan logika

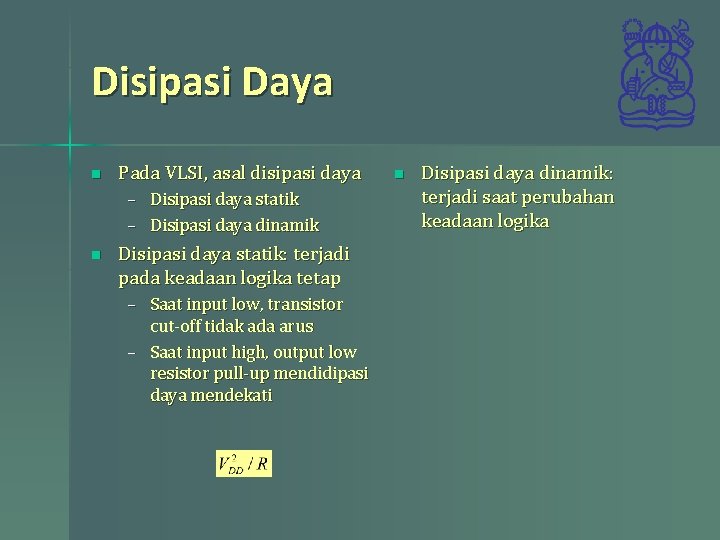

Disipasi Daya n Pada VLSI, asal disipasi daya – Disipasi daya statik – Disipasi daya dinamik n Disipasi daya statik: terjadi pada keadaan logika tetap – Saat input low, transistor cut-off tidak ada arus – Saat input high, output low resistor pull-up mendidipasi daya mendekati n Disipasi daya dinamik: terjadi saat perubahan keadaan logika

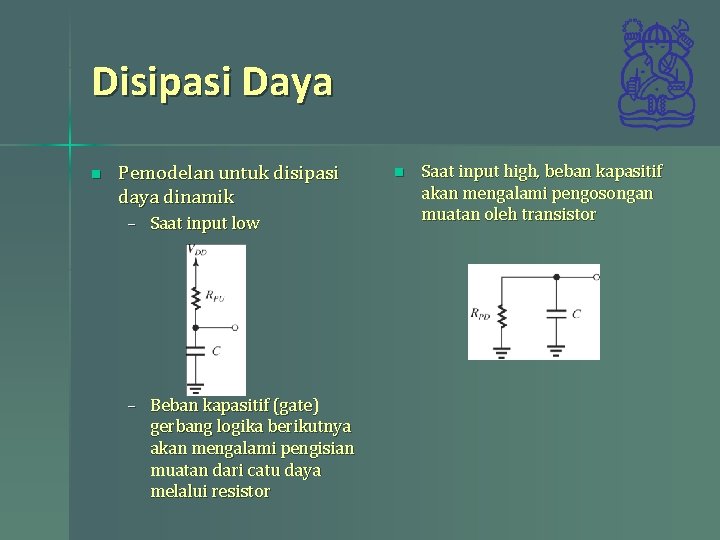

Disipasi Daya n Pemodelan untuk disipasi daya dinamik – Saat input low – Beban kapasitif (gate) gerbang logika berikutnya akan mengalami pengisian muatan dari catu daya melalui resistor n Saat input high, beban kapasitif akan mengalami pengosongan muatan oleh transistor

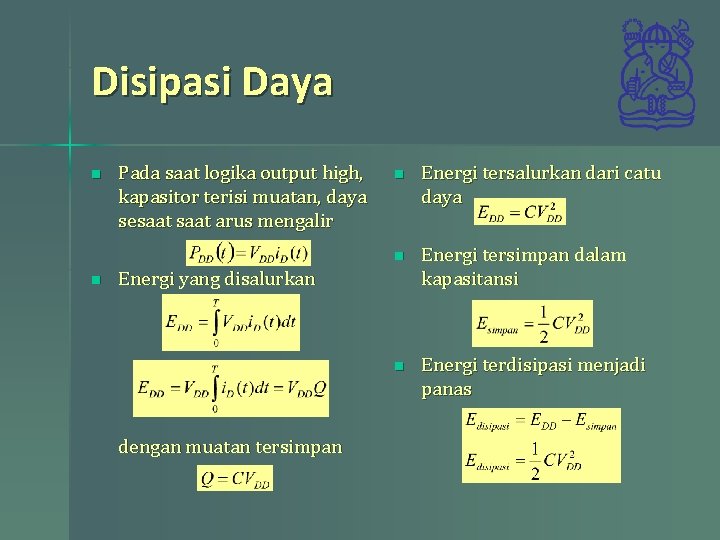

Disipasi Daya n n Pada saat logika output high, kapasitor terisi muatan, daya sesaat arus mengalir n Energi tersalurkan dari catu daya n Energi tersimpan dalam kapasitansi n Energi terdisipasi menjadi panas Energi yang disalurkan dengan muatan tersimpan

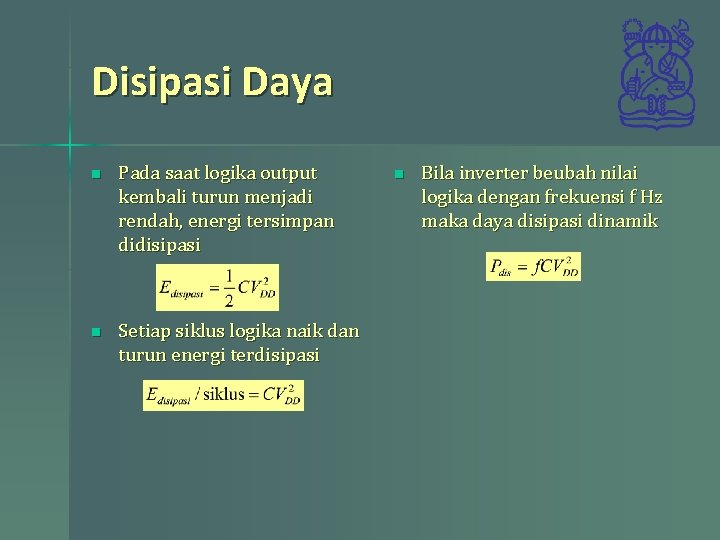

Disipasi Daya n Pada saat logika output kembali turun menjadi rendah, energi tersimpan didisipasi n Setiap siklus logika naik dan turun energi terdisipasi n Bila inverter beubah nilai logika dengan frekuensi f Hz maka daya disipasi dinamik

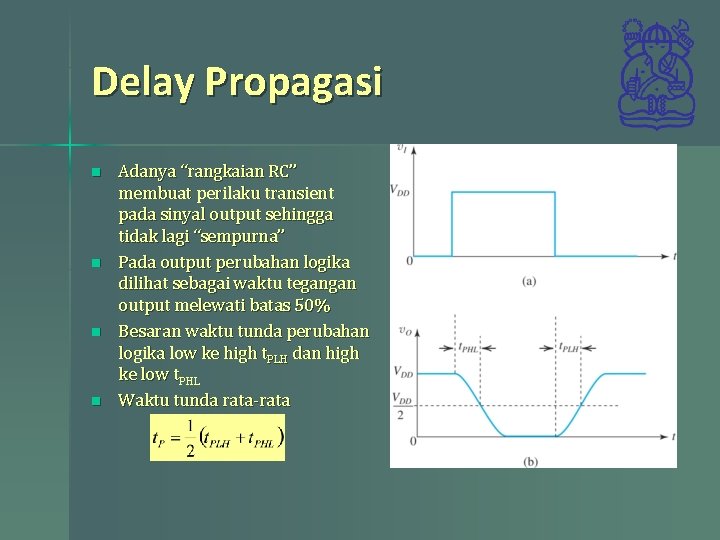

Delay Propagasi n n Adanya “rangkaian RC” membuat perilaku transient pada sinyal output sehingga tidak lagi “sempurna” Pada output perubahan logika dilihat sebagai waktu tegangan output melewati batas 50% Besaran waktu tunda perubahan logika low ke high t. PLH dan high ke low t. PHL Waktu tunda rata-rata

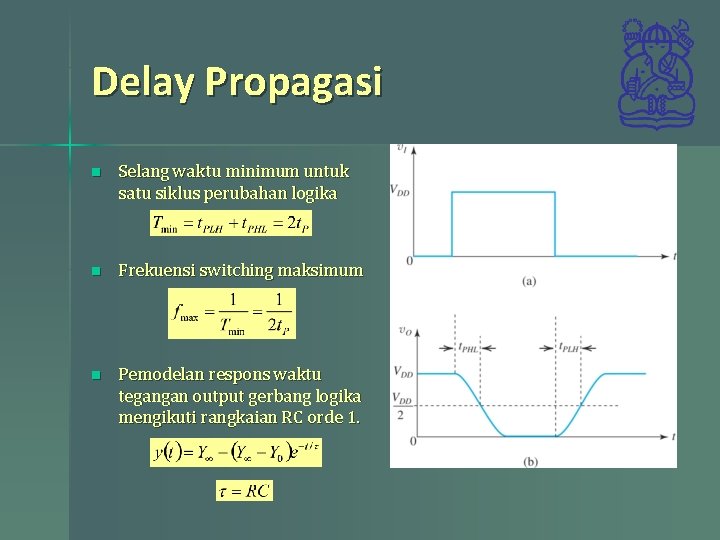

Delay Propagasi n Selang waktu minimum untuk satu siklus perubahan logika n Frekuensi switching maksimum n Pemodelan respons waktu tegangan output gerbang logika mengikuti rangkaian RC orde 1.

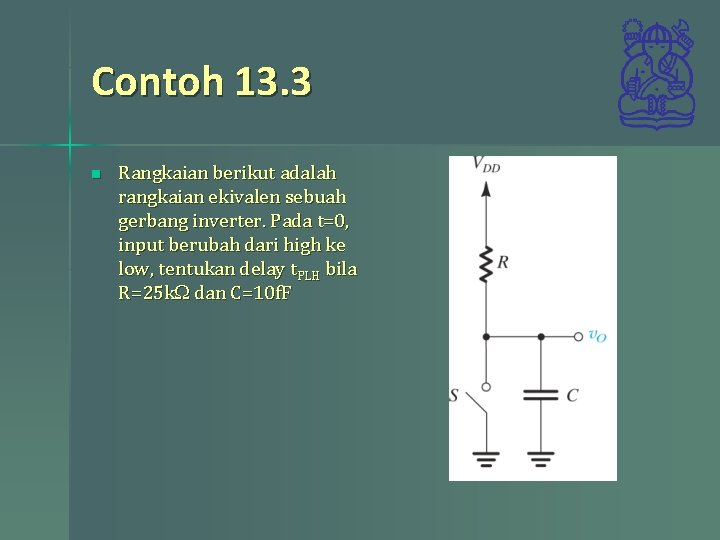

Contoh 13. 3 n Rangkaian berikut adalah rangkaian ekivalen sebuah gerbang inverter. Pada t=0, input berubah dari high ke low, tentukan delay t. PLH bila R=25 k. W dan C=10 f. F

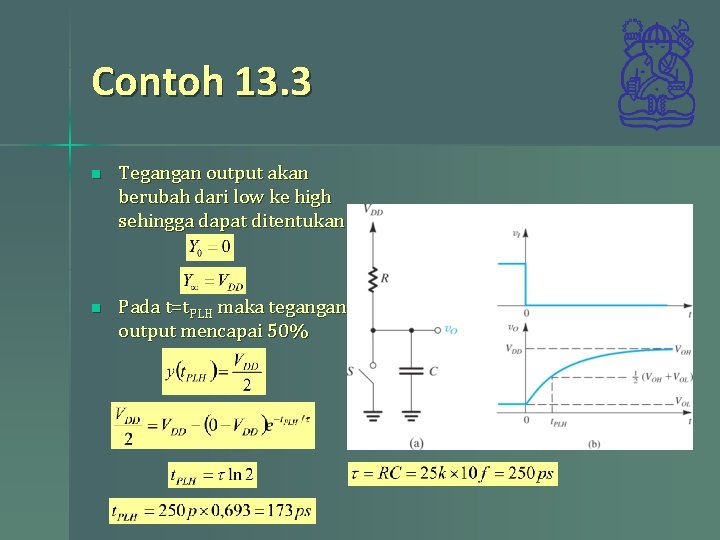

Contoh 13. 3 n Tegangan output akan berubah dari low ke high sehingga dapat ditentukan n Pada t=t. PLH maka tegangan output mencapai 50%

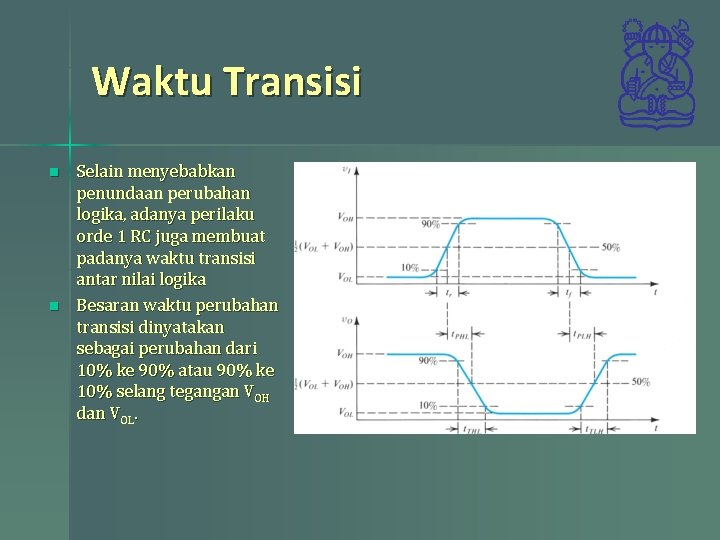

Waktu Transisi n n Selain menyebabkan penundaan perubahan logika, adanya perilaku orde 1 RC juga membuat padanya waktu transisi antar nilai logika Besaran waktu perubahan transisi dinyatakan sebagai perubahan dari 10% ke 90% atau 90% ke 10% selang tegangan VOH dan VOL.

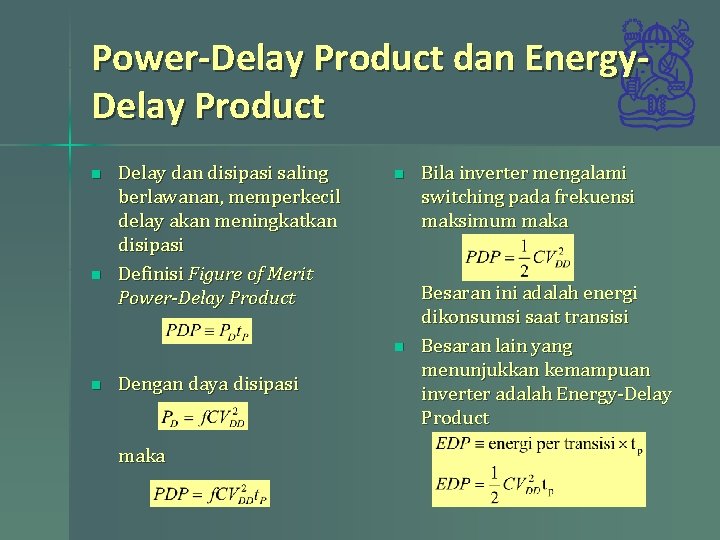

Power-Delay Product dan Energy. Delay Product n n Delay dan disipasi saling berlawanan, memperkecil delay akan meningkatkan disipasi Definisi Figure of Merit Power-Delay Product n n n Dengan daya disipasi maka Bila inverter mengalami switching pada frekuensi maksimum maka Besaran ini adalah energi dikonsumsi saat transisi Besaran lain yang menunjukkan kemampuan inverter adalah Energy-Delay Product

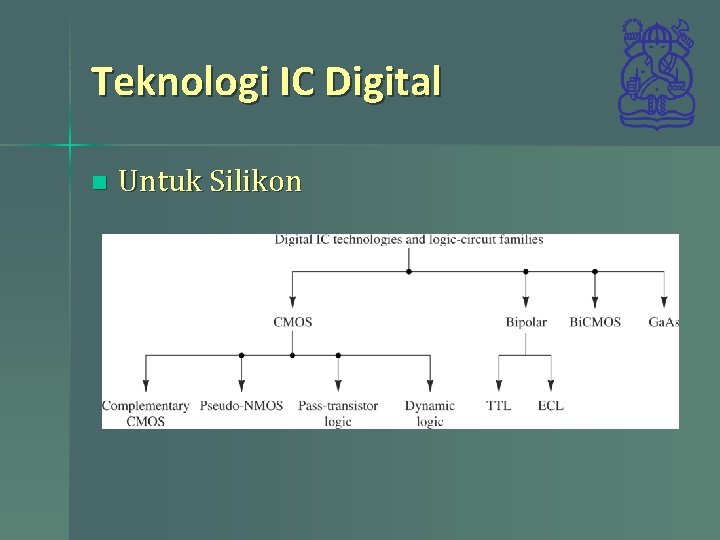

Teknologi IC Digital n Untuk Silikon

- Slides: 34