Bab 13 Rangkaian Logika Digital CMOS Inverter CMOS

Bab 13 Rangkaian Logika Digital CMOS

Inverter CMOS n CMOS – Complementary Metal Oxide Semiconductor memanfaatkan pasangan NMOS sebagai saklar pulldown dan PMOS sebagai saklar pull-up

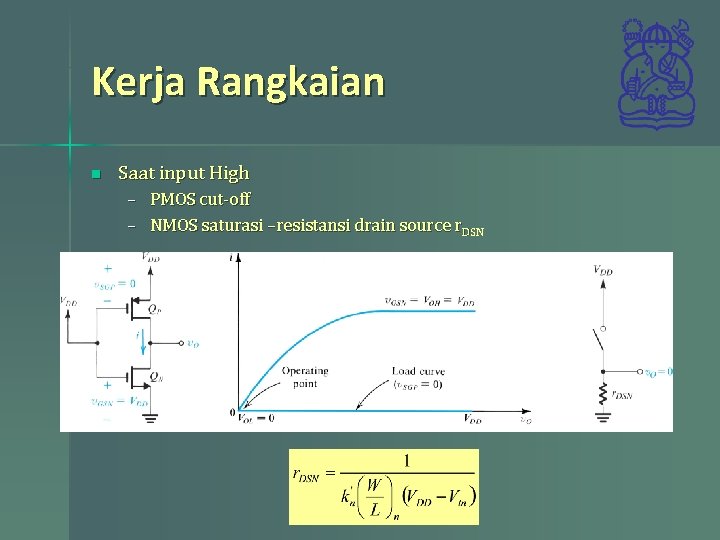

Kerja Rangkaian n Saat input High – PMOS cut-off – NMOS saturasi –resistansi drain source r. DSN

Kerja Rangkaian n Saat input Low – NMOS cut-off – PMOS saturasi –resistansi drain source r. DSP

Kerja Rangkaian n n Output selalu 0 atau VDD Daya disipasi statik nol Alur resistansi oleh transistor kecil – tahan noise dan interferensi PMOS dan NMOS memberikan kemampuan driving yang tinggi ke GND atau VDD Resistansi input gerbang logika tak hingga

VTC Inverter CMOS n Persamaan arus

VTC Inverter CMOS n CMOS dibuat simetri n Menentukan VIH: NMOS trioda, PMOS saturasi diferensiasinya

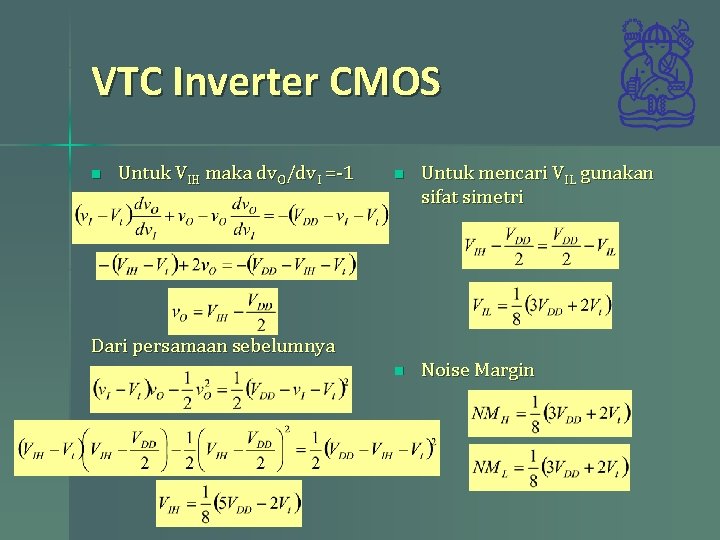

VTC Inverter CMOS n Untuk VIH maka dv. O/dv. I =-1 n Untuk mencari VIL gunakan sifat simetri n Noise Margin Dari persamaan sebelumnya

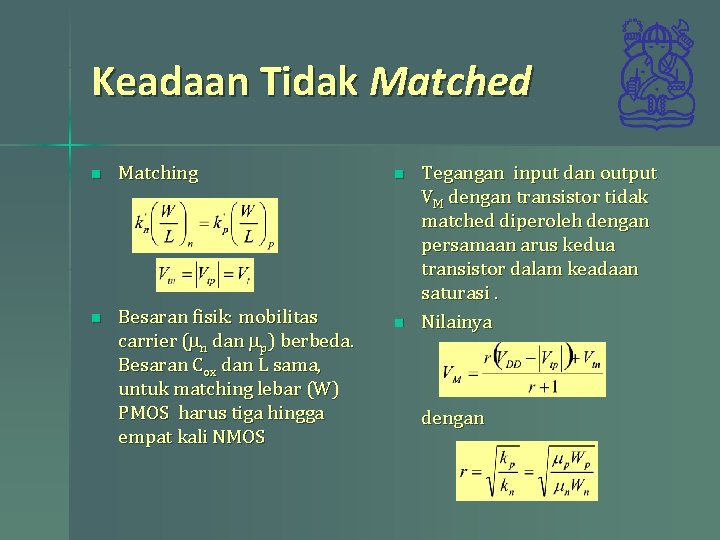

Keadaan Tidak Matched n Matching n Besaran fisik: mobilitas carrier (mn dan mp) berbeda. Besaran Cox dan L sama, untuk matching lebar (W) PMOS harus tiga hingga empat kali NMOS n n Tegangan input dan output VM dengan transistor tidak matched diperoleh dengan persamaan arus kedua transistor dalam keadaan saturasi. Nilainya dengan

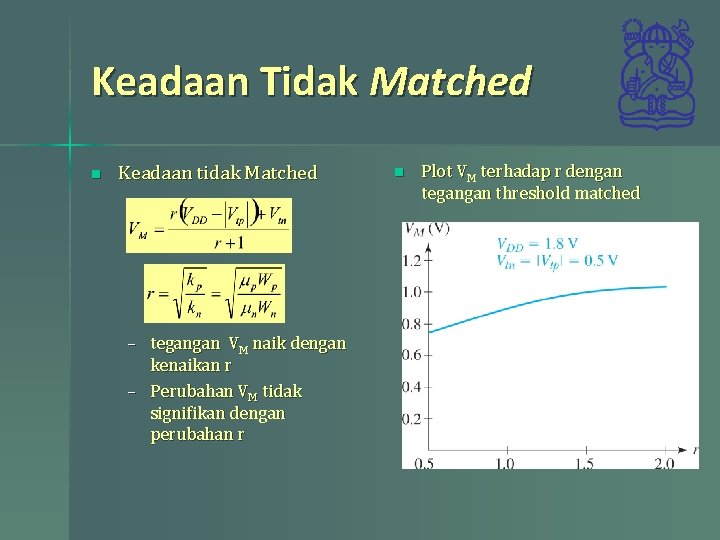

Keadaan Tidak Matched n Keadaan tidak Matched – tegangan VM naik dengan kenaikan r – Perubahan VM tidak signifikan dengan perubahan r n Plot VM terhadap r dengan tegangan threshold matched

- Slides: 10