Bab 13 Rangkaian Logika Digital CMOS Gerbang Logika

Bab 13 Rangkaian Logika Digital CMOS

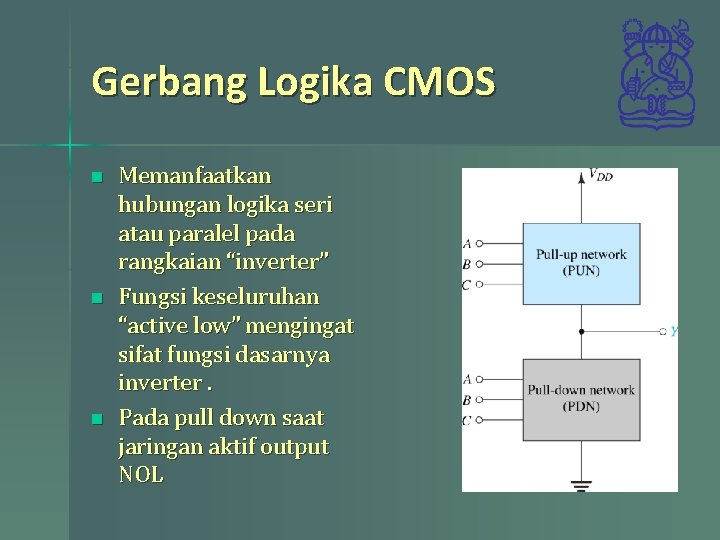

Gerbang Logika CMOS n n n Memanfaatkan hubungan logika seri atau paralel pada rangkaian “inverter” Fungsi keseluruhan “active low” mengingat sifat fungsi dasarnya inverter. Pada pull down saat jaringan aktif output NOL

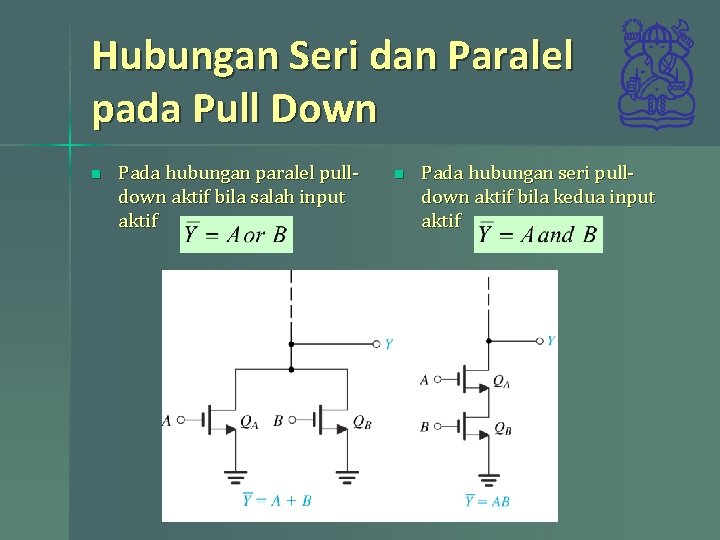

Hubungan Seri dan Paralel pada Pull Down n Pada hubungan paralel pulldown aktif bila salah input aktif n Pada hubungan seri pulldown aktif bila kedua input aktif

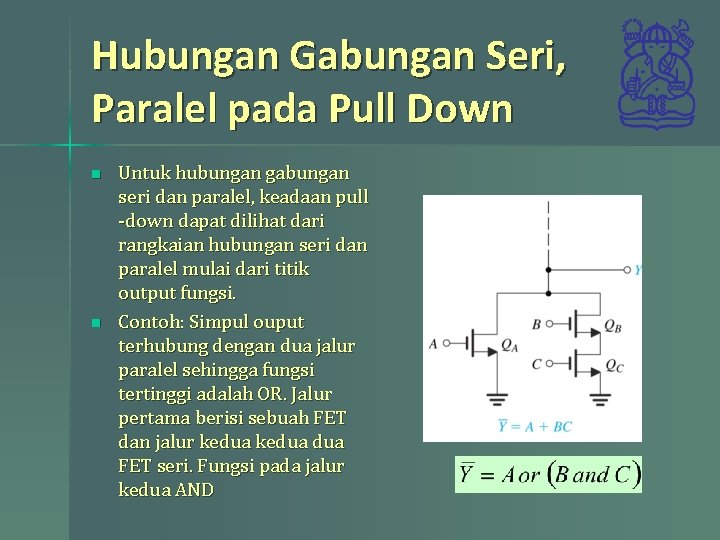

Hubungan Gabungan Seri, Paralel pada Pull Down n n Untuk hubungan gabungan seri dan paralel, keadaan pull -down dapat dilihat dari rangkaian hubungan seri dan paralel mulai dari titik output fungsi. Contoh: Simpul ouput terhubung dengan dua jalur paralel sehingga fungsi tertinggi adalah OR. Jalur pertama berisi sebuah FET dan jalur kedua dua FET seri. Fungsi pada jalur kedua AND

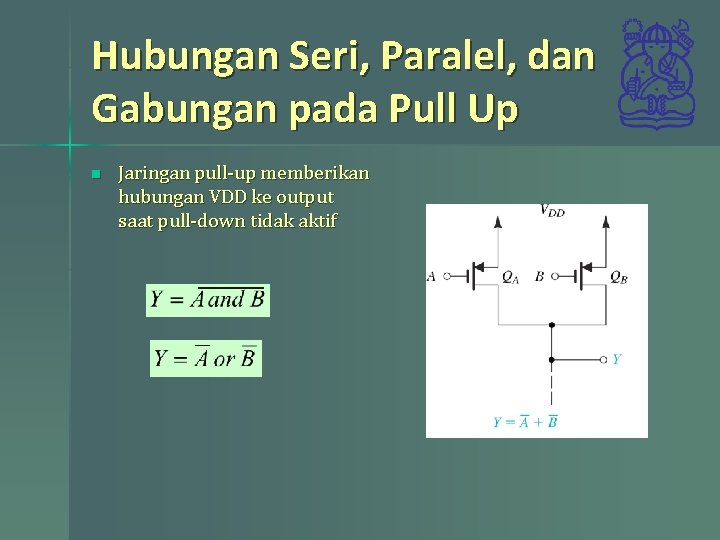

Hubungan Seri, Paralel, dan Gabungan pada Pull Up n Jaringan pull-up memberikan hubungan VDD ke output saat pull-down tidak aktif

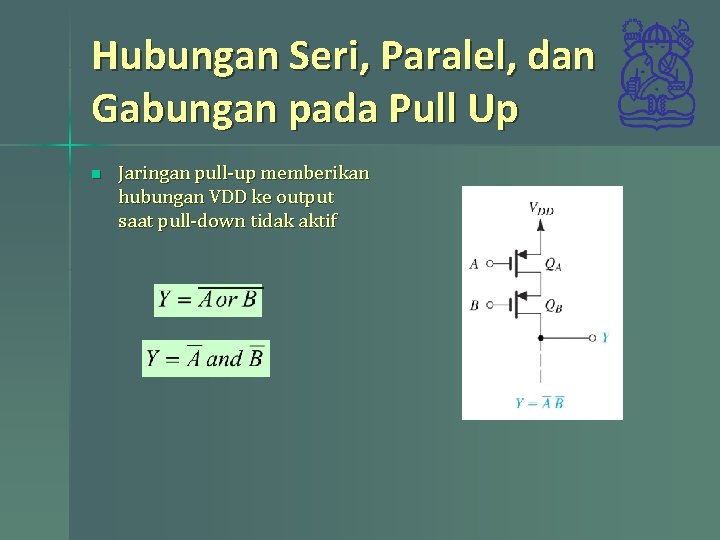

Hubungan Seri, Paralel, dan Gabungan pada Pull Up n Jaringan pull-up memberikan hubungan VDD ke output saat pull-down tidak aktif

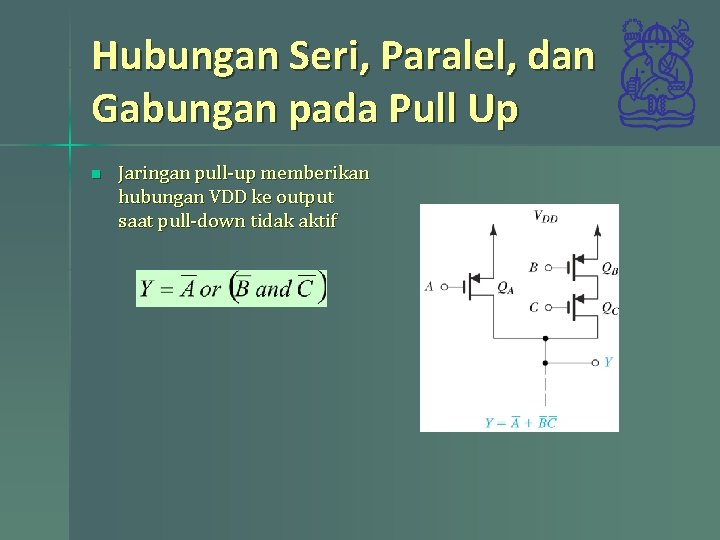

Hubungan Seri, Paralel, dan Gabungan pada Pull Up n Jaringan pull-up memberikan hubungan VDD ke output saat pull-down tidak aktif

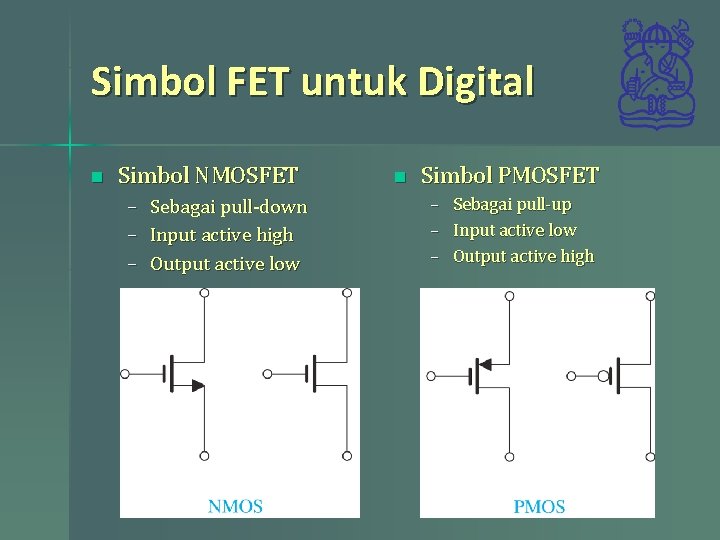

Simbol FET untuk Digital n Simbol NMOSFET – Sebagai pull-down – Input active high – Output active low n Simbol PMOSFET – Sebagai pull-up – Input active low – Output active high

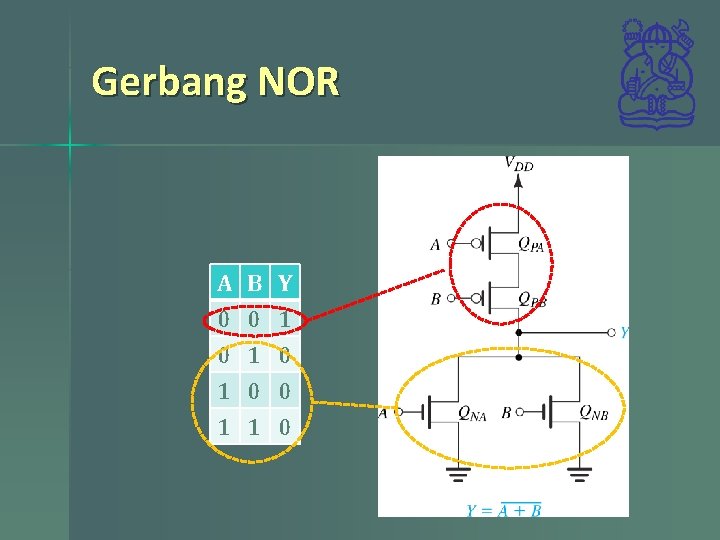

Gerbang NOR A 0 0 1 B 0 1 0 Y 1 0 0 1 1 0

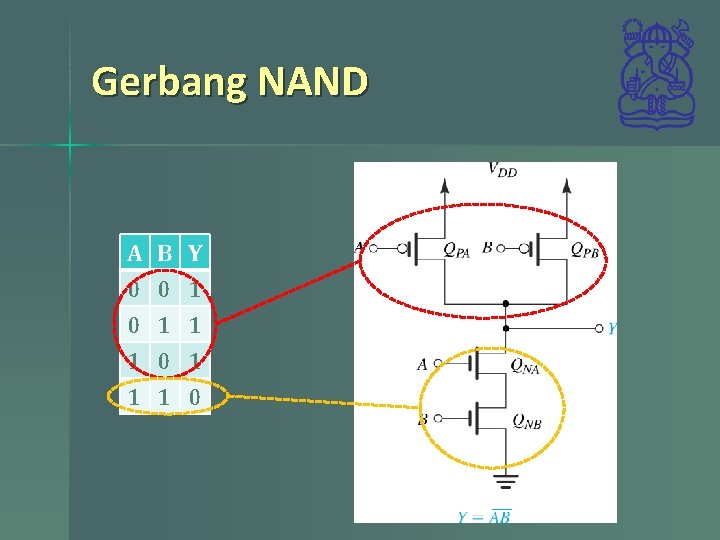

Gerbang NAND A 0 0 1 B 0 1 0 Y 1 1 1 0

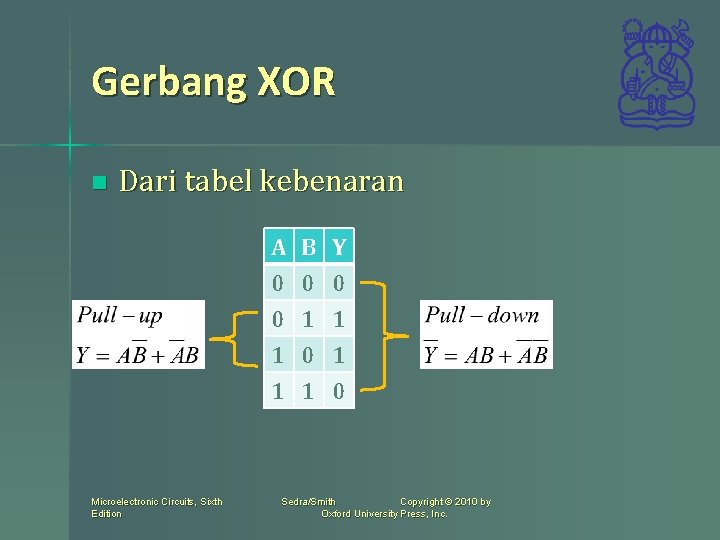

Gerbang XOR n Dari tabel kebenaran A 0 0 1 B 0 1 0 Y 0 1 1 0 Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc.

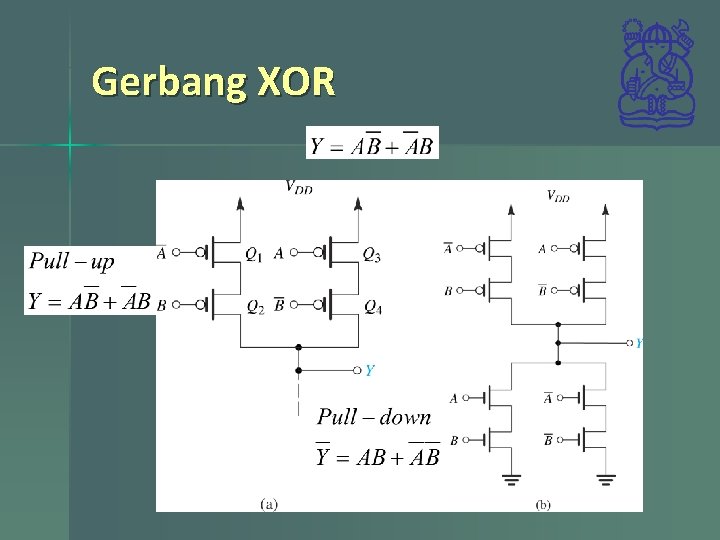

Gerbang XOR

Hubungan Pull-Up dan Pull. Down n Hubungan pull-up dan pull-down saling komplementasi Hubungan seri di Pull-down diikuti hubungan paralel di Pull-Up Sebaliknya hubungan paralel di pull-down diikuti hungungan seri di Pull-Up

Perancangan Rangkaian n 1. 2. 3. 4. 5. Bentuk Umum Y=f(input) Bentuk fungsi akhir Negasi (invert)-kan dua kali (fungsi masih sama) Lakukan de Morgan pada negasi dalam fungsi Susun rangkaian Pull Down sesuai bentuk active-low hasil 3 – hubungan AND seri dan OR paralel Susun rangkaian Pull Up sebagai komplemen rangkaian Pull Down – PD seri PU paralel dan PD paralel PUseri Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc.

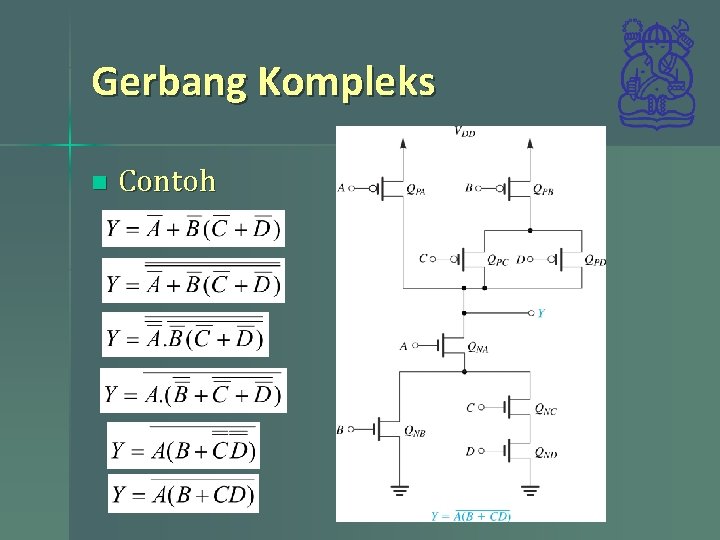

Gerbang Kompleks n Contoh

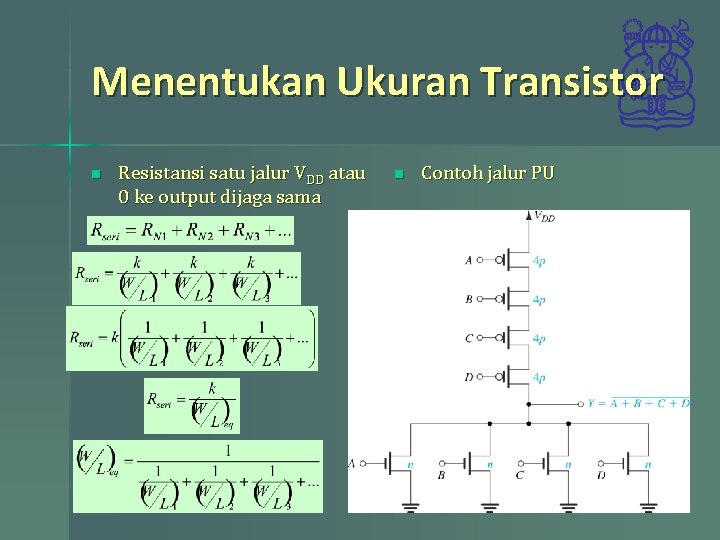

Menentukan Ukuran Transistor n Resistansi satu jalur VDD atau 0 ke output dijaga sama n Contoh jalur PU

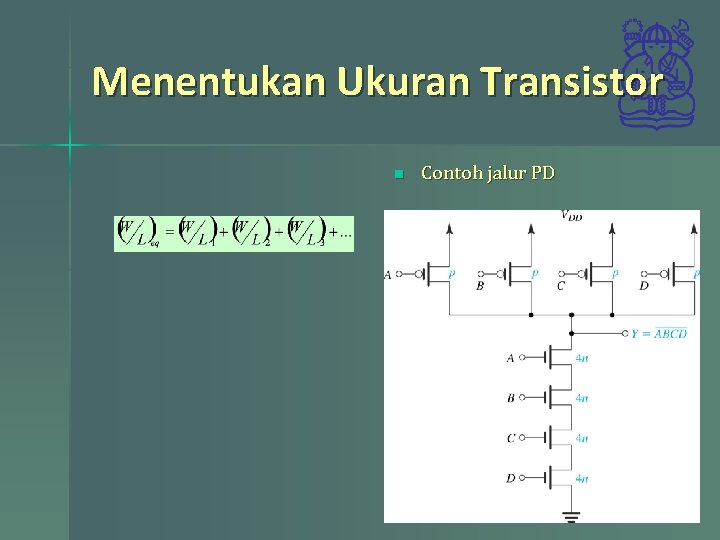

Menentukan Ukuran Transistor n Contoh jalur PD

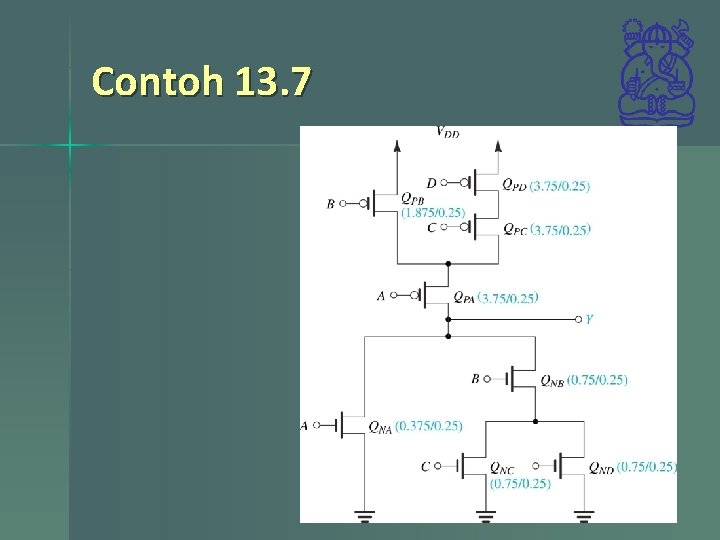

Contoh 13. 7

Fan-in dan Fan-out Fan-in n Fan-out: jumlah maksimum beban sehingga gerbang logika masih berfungsi n Pada CMOS penambahan beban hanya akan berpengaruh pada delay n

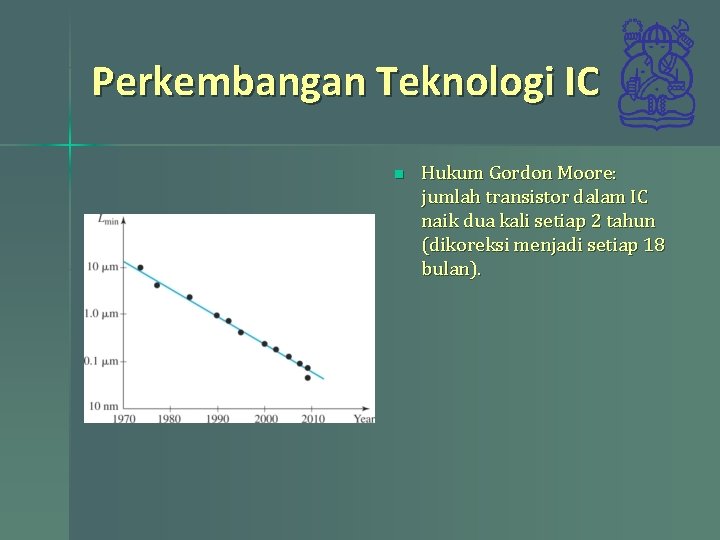

Perkembangan Teknologi IC n Hukum Gordon Moore: jumlah transistor dalam IC naik dua kali setiap 2 tahun (dikoreksi menjadi setiap 18 bulan).

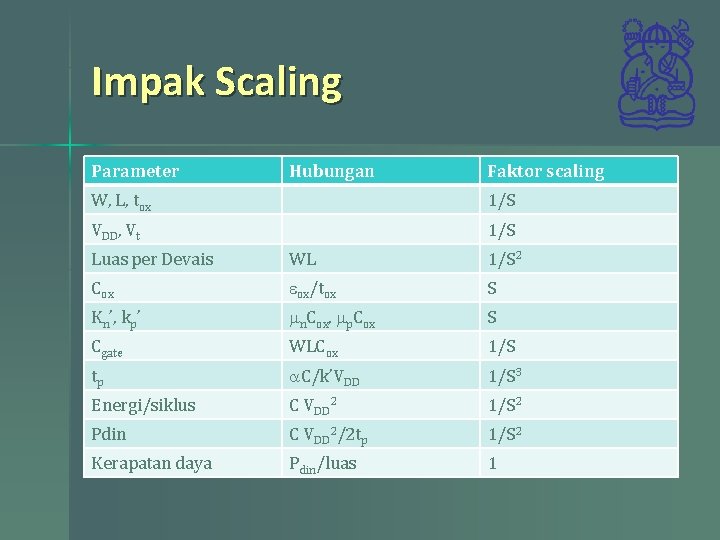

Impak Scaling Parameter Hubungan Faktor scaling W, L, tox 1/S VDD, Vt 1/S Luas per Devais WL 1/S 2 Cox eox/tox S Kn’, kp’ mn. Cox, mp. Cox S Cgate WLCox 1/S tp a. C/k’VDD 1/S 3 Energi/siklus C VDD 2 1/S 2 Pdin C VDD 2/2 tp 1/S 2 Kerapatan daya Pdin/luas 1

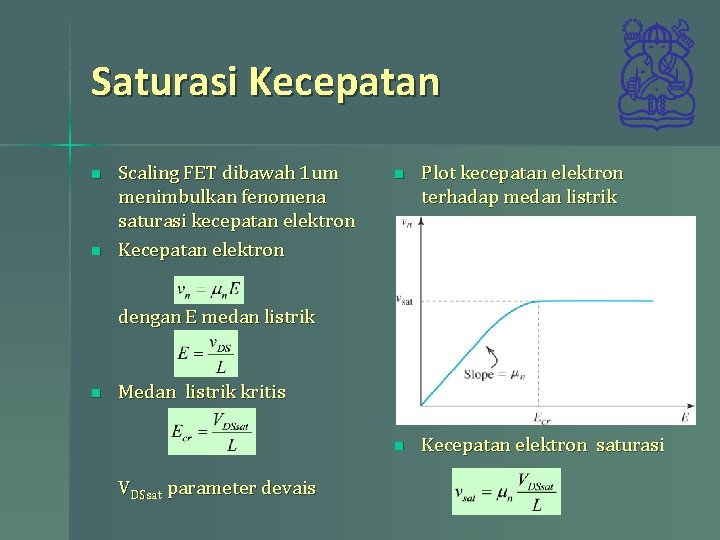

Saturasi Kecepatan n n Scaling FET dibawah 1 um menimbulkan fenomena saturasi kecepatan elektron Kecepatan elektron n Plot kecepatan elektron terhadap medan listrik n Kecepatan elektron saturasi dengan E medan listrik n Medan listrik kritis VDSsat parameter devais

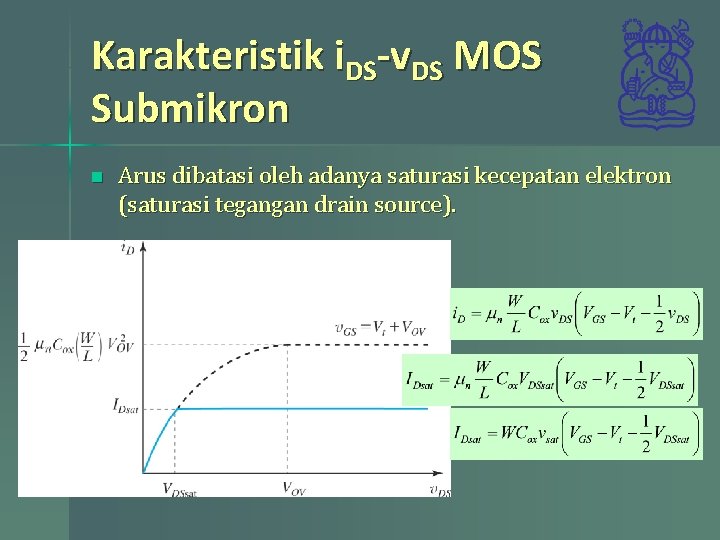

Karakteristik i. DS-v. DS MOS Submikron n Arus dibatasi oleh adanya saturasi kecepatan elektron (saturasi tegangan drain source).

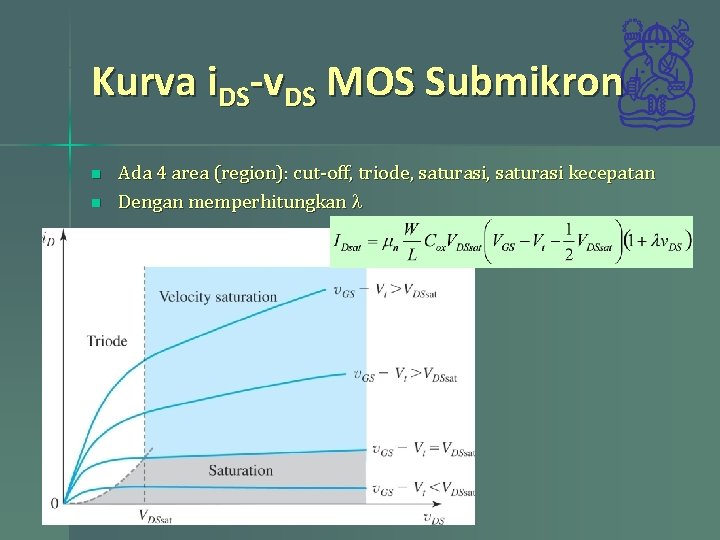

Kurva i. DS-v. DS MOS Submikron n n Ada 4 area (region): cut-off, triode, saturasi kecepatan Dengan memperhitungkan l

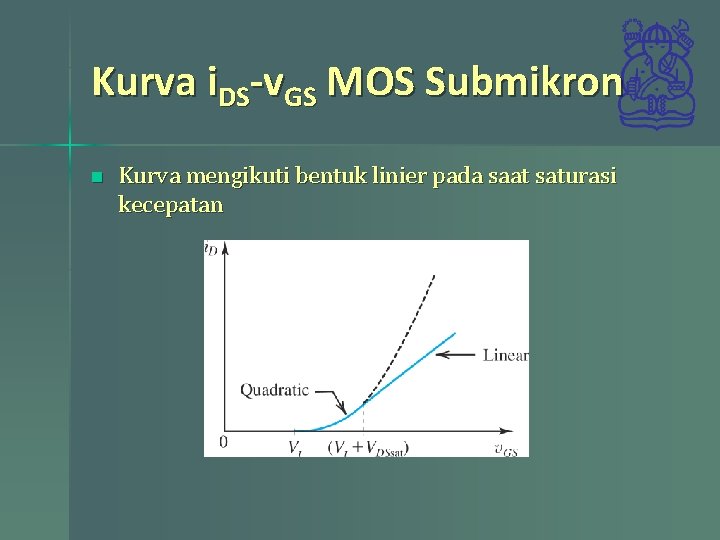

Kurva i. DS-v. GS MOS Submikron n Kurva mengikuti bentuk linier pada saat saturasi kecepatan

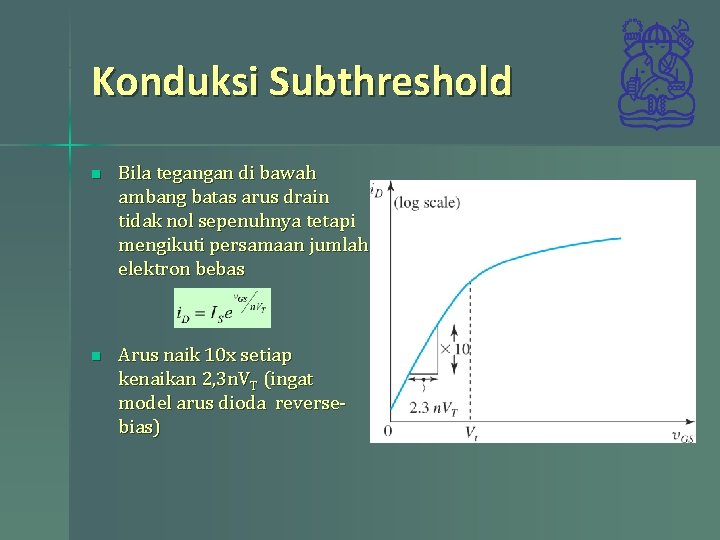

Konduksi Subthreshold n Bila tegangan di bawah ambang batas arus drain tidak nol sepenuhnya tetapi mengikuti persamaan jumlah elektron bebas n Arus naik 10 x setiap kenaikan 2, 3 n. VT (ingat model arus dioda reversebias)

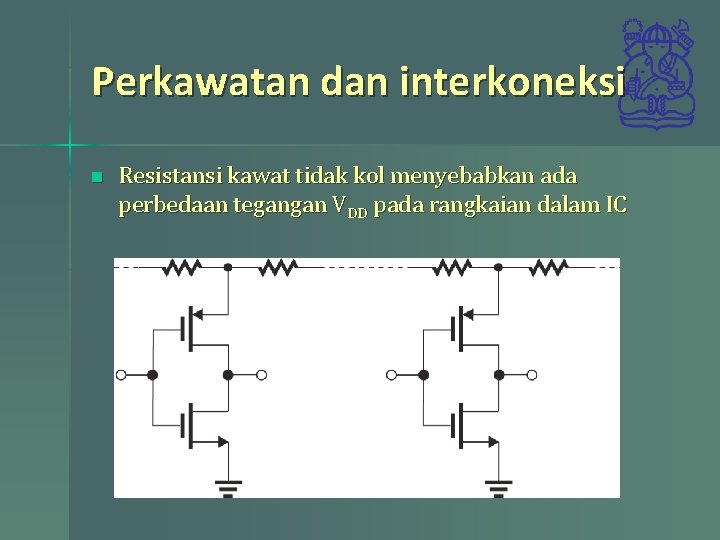

Perkawatan dan interkoneksi n Resistansi kawat tidak kol menyebabkan ada perbedaan tegangan VDD pada rangkaian dalam IC

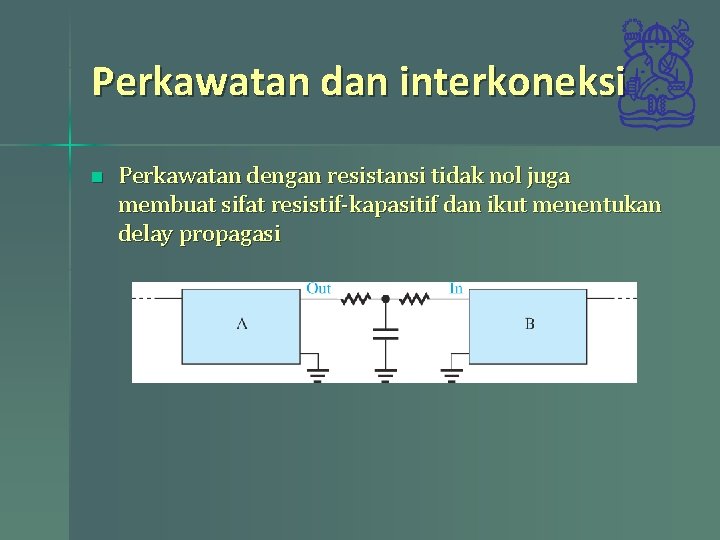

Perkawatan dan interkoneksi n Perkawatan dengan resistansi tidak nol juga membuat sifat resistif-kapasitif dan ikut menentukan delay propagasi

- Slides: 28