b 1110 Multicycle Continued ENGR x D 52

b 1110 Multicycle (Continued) ENGR x. D 52 Eric Van. Wyk Fall 2014

Today • Balancing Micro. Ops • Review Multicycle Board work so far • Generate FSM controllers • Complete Multicycle Rev 1

Balance • An unbalanced design has some operations doing more “work” (time) than the others – Wastes time in fast cycles • Moving work between operations is Balancing – Reduce the global clock period by leveling • Balance adjacent ops by register positioning – Some ops are hard to “slice”

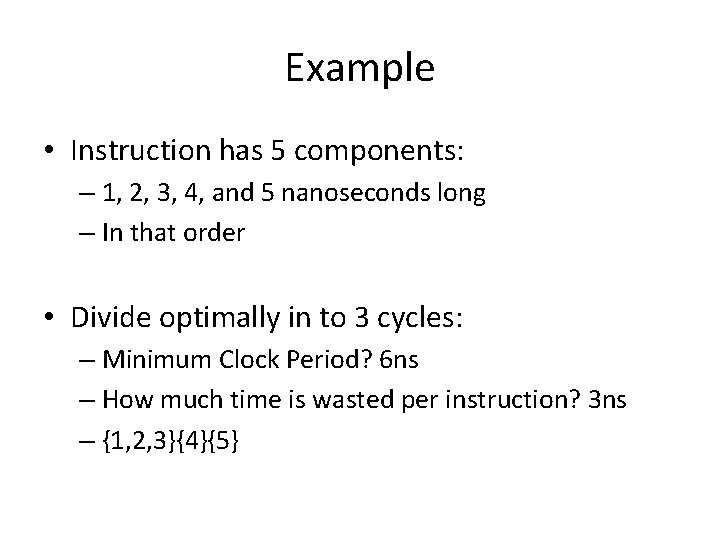

Example • Instruction has 5 components: – 1, 2, 3, 4, and 5 nanoseconds long – In that order • Divide optimally in to 3 cycles: – Minimum Clock Period? – How much time is wasted per instruction?

Example • Instruction has 5 components: – 1, 2, 3, 4, and 5 nanoseconds long – In that order • Divide optimally in to 3 cycles: – Minimum Clock Period? 6 ns – How much time is wasted per instruction? 3 ns – {1, 2, 3}{4}{5}

Balancing • Not all resources are fungible – Some micro-operations are hard to subdivide – Order of operations matters sometimes • The slowest unit sets the pace for everything • Compare “Optimal” time to Reality – Measure of Balance

![Example Timings Instr/Cycle RTL Symbolic Numeric LW: 0 IR = Mem[PC] t. X 1 Example Timings Instr/Cycle RTL Symbolic Numeric LW: 0 IR = Mem[PC] t. X 1](http://slidetodoc.com/presentation_image/a1167ceeb8de856eac8bc19ee0507e0e/image-7.jpg)

Example Timings Instr/Cycle RTL Symbolic Numeric LW: 0 IR = Mem[PC] t. X 1 + t. MEM 10 LW: 0 PC=PC+4 t. X 1+t. ALU+t. X 2 In Parallel with t. X 2+t. ALU+t. X 2 5 5 LW: 1 AB = Reg. File[_] t. RF 3 LW: 2 Res = A + SEI t. ALU 5 LW: 3 DR = Mem[Res] t. X 1 + t. MEM 10 LW: 4 Reg. File[rt] = DR t. RF+t. X 1 3 Component Symbol Delay ALU t. ALU 5 ns Register File t. RF 3 ns Instruction/Data Memory t. MEM 10 ns Muxes (Optional) t. Xn 0 ish Registers 0 0

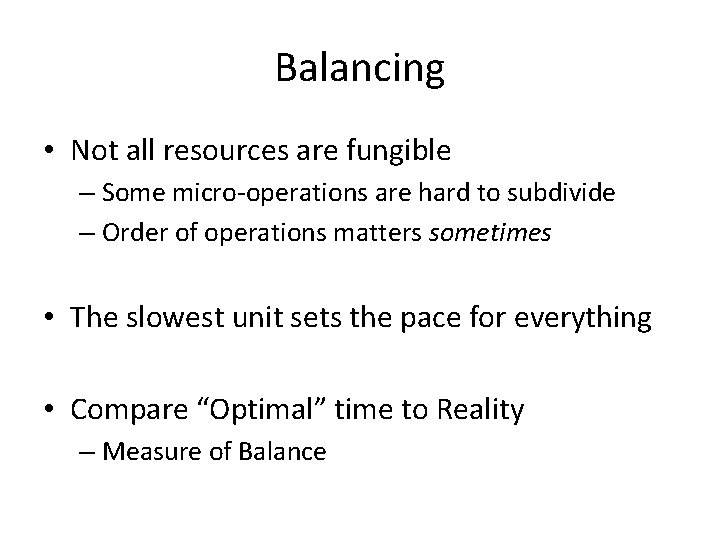

Rebalance: Combine Stages 1 and 2 Instr/Cycle RTL Symbolic Numeric LW: 0 IR = Mem[PC] t. X 1 + t. MEM 10 LW: 0 PC=PC+4 t. X 1+t. ALU+t. X 2 In Parallel with t. X 2+t. ALU+t. X 2 5 5 LW: 1/2 Res = Reg. File[]+SEI t. RF+t. ALU 8 LW: 3 DR = Mem[Res] t. X 1 + t. MEM 10 LW: 4 Reg. File[rt] = DR t. RF+t. X 1 3 Component Symbol Delay ALU t. ALU 5 ns Register File t. RF 3 ns Instruction/Data Memory t. MEM 10 ns Muxes (Optional) t. Xn 0 ish Registers 0 0

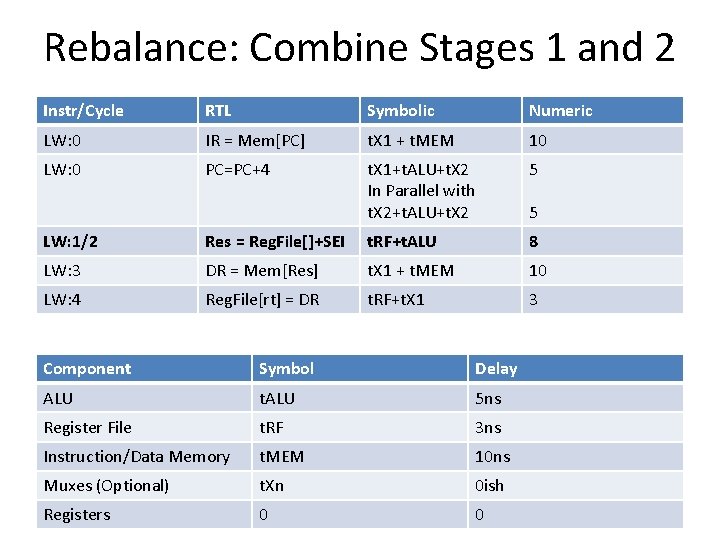

Balancing Penalty • Total time wasted per cycle from poor balance Instr/Cycle Time Penalty LW: IF 10 0 LW: ID 3 7 LW: ID/EX 8 2 LW: EX 5 5 LW: MEM 10 0 LW: WB 3 7 21 9 31 19

Back to Review!

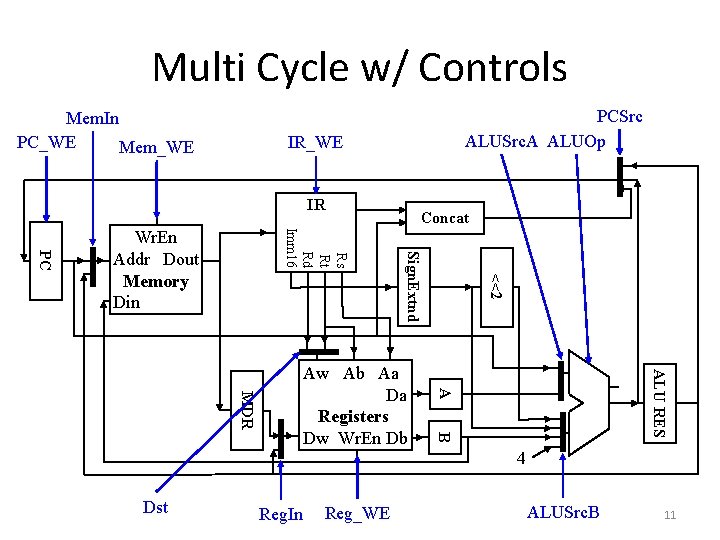

Multi Cycle w/ Controls Mem. In PC_WE Mem_WE PCSrc ALUSrc. A ALUOp IR_WE IR <<2 ALU RES Reg_WE B Reg. In A Aw Ab Aa Da Registers Dw Wr. En Db MDR Dst Sign. Extnd Rs Rt Rd Imm 16 PC Wr. En Addr Dout Memory Din Concat 4 ALUSrc. B 11

![Phases: Jump • IF: • • ID: EX: MEM: WB: Instruction Register = Memory[PC] Phases: Jump • IF: • • ID: EX: MEM: WB: Instruction Register = Memory[PC]](http://slidetodoc.com/presentation_image/a1167ceeb8de856eac8bc19ee0507e0e/image-12.jpg)

Phases: Jump • IF: • • ID: EX: MEM: WB: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: 28], IR[25: 0], b 00

![Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31:](http://slidetodoc.com/presentation_image/a1167ceeb8de856eac8bc19ee0507e0e/image-13.jpg)

Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: 28], IR[25: 0], b 00 IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout Data Memory

![Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31:](http://slidetodoc.com/presentation_image/a1167ceeb8de856eac8bc19ee0507e0e/image-14.jpg)

Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: 28], IR[25: 0], b 00 Memory 4 IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

![Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31:](http://slidetodoc.com/presentation_image/a1167ceeb8de856eac8bc19ee0507e0e/image-15.jpg)

Phases: Jump • IF: • ID: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: 28], IR[25: 0], b 00 Concat b 00 Memory 4 IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

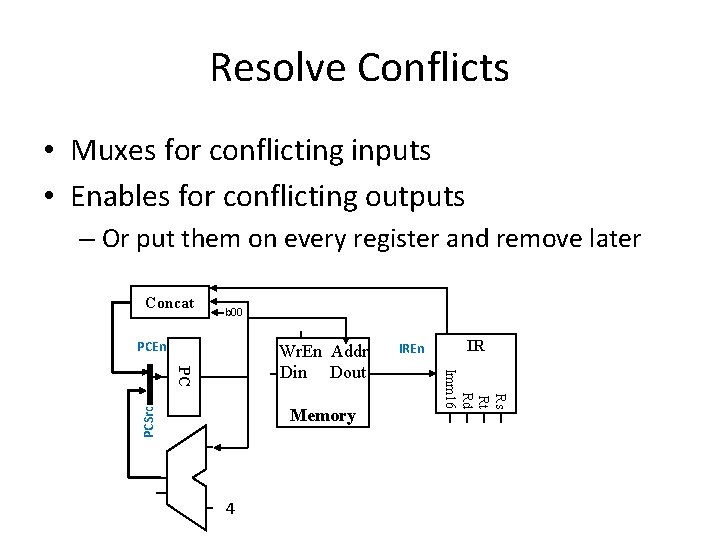

Resolve Conflicts • Muxes for conflicting inputs • Enables for conflicting outputs – Or put them on every register and remove later Concat b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

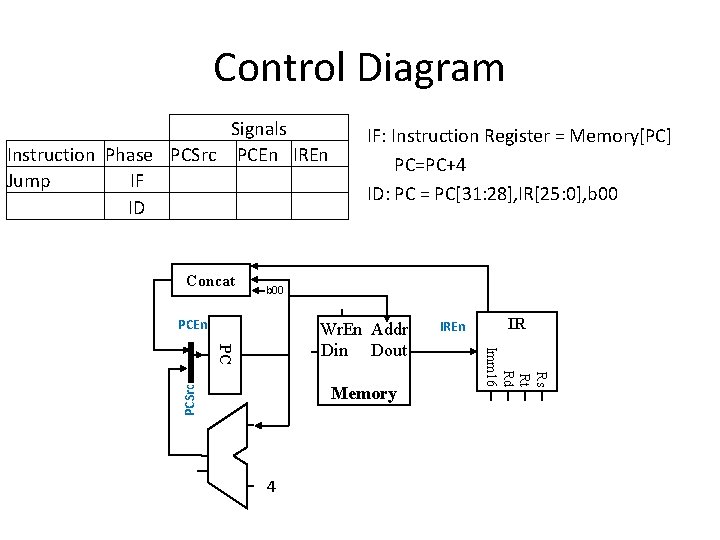

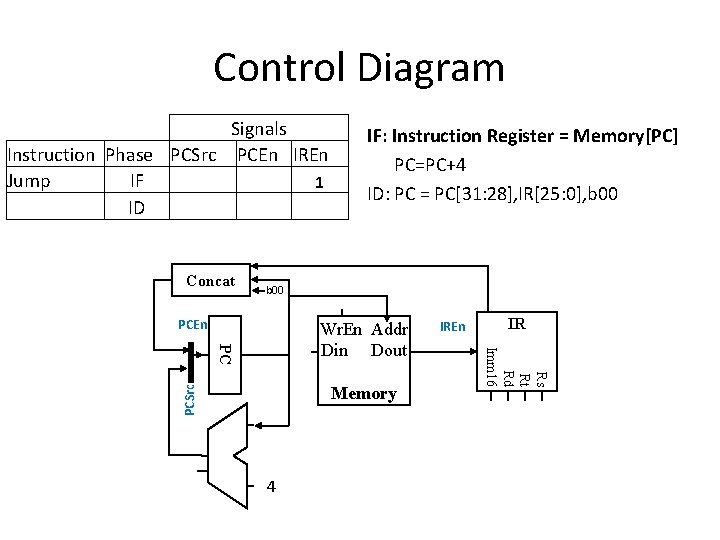

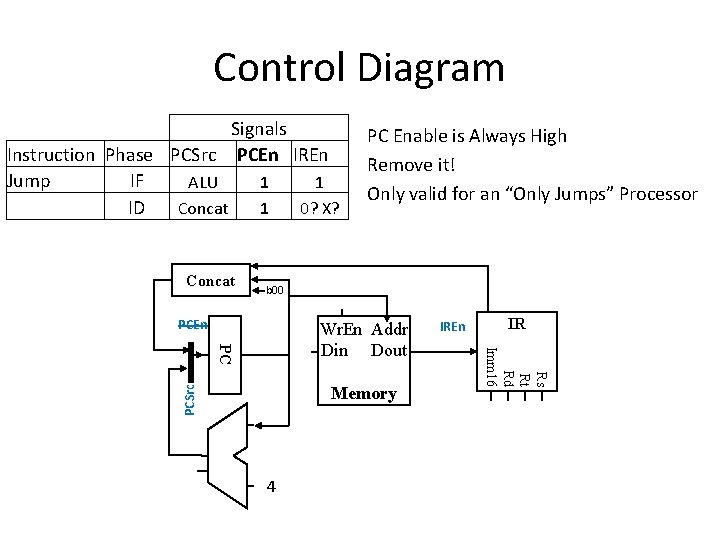

Control Diagram Signals Instruction Phase PCSrc PCEn IREn Jump IF ID Concat IF: Instruction Register = Memory[PC] PC=PC+4 ID: PC = PC[31: 28], IR[25: 0], b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

Control Diagram Signals Instruction Phase PCSrc PCEn IREn Jump IF 1 ID Concat IF: Instruction Register = Memory[PC] PC=PC+4 ID: PC = PC[31: 28], IR[25: 0], b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

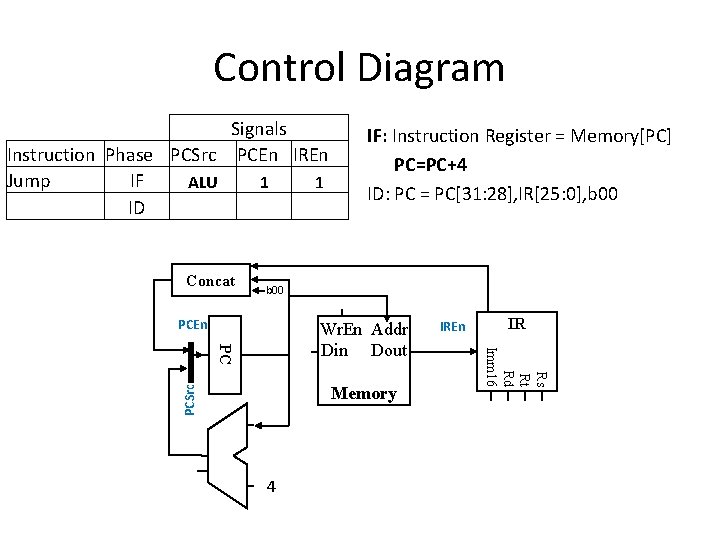

Control Diagram Signals Instruction Phase PCSrc PCEn IREn Jump IF ALU 1 1 ID Concat IF: Instruction Register = Memory[PC] PC=PC+4 ID: PC = PC[31: 28], IR[25: 0], b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

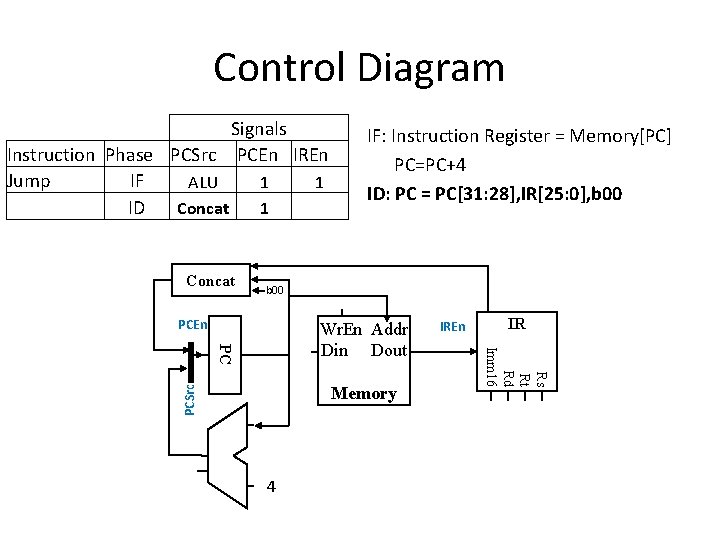

Control Diagram Signals Instruction Phase PCSrc PCEn IREn Jump IF ALU 1 1 ID Concat 1 Concat IF: Instruction Register = Memory[PC] PC=PC+4 ID: PC = PC[31: 28], IR[25: 0], b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

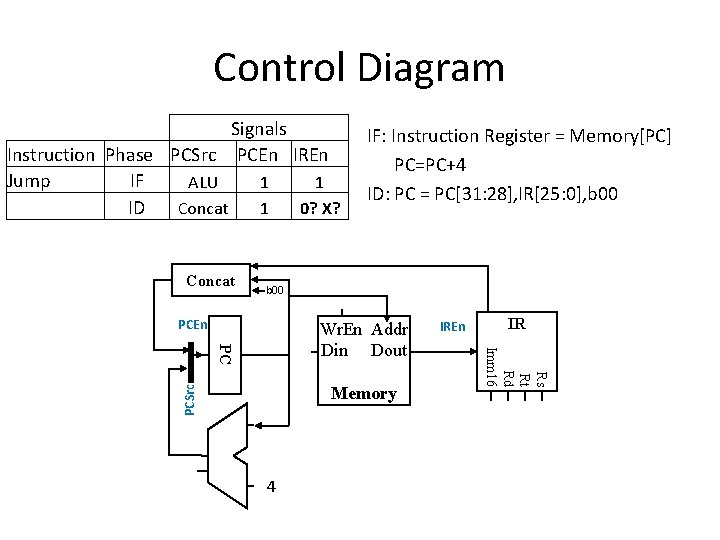

Control Diagram Signals Instruction Phase PCSrc PCEn IREn Jump IF ALU 1 1 ID Concat 1 0? X? Concat IF: Instruction Register = Memory[PC] PC=PC+4 ID: PC = PC[31: 28], IR[25: 0], b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

Control Diagram Signals Instruction Phase PCSrc PCEn IREn Jump IF ALU 1 1 ID Concat 1 0? X? Concat PC Enable is Always High Remove it! Only valid for an “Only Jumps” Processor b 00 PCEn PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

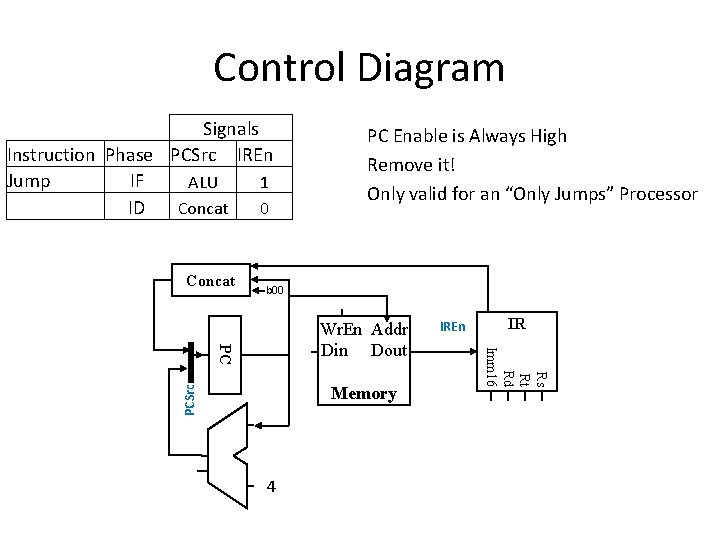

Control Diagram Signals Instruction Phase PCSrc IREn Jump IF ALU 1 ID Concat 0 Concat PC Enable is Always High Remove it! Only valid for an “Only Jumps” Processor b 00 PCSrc Memory 4 IREn IR Rs Rt Rd Imm 16 PC Wr. En Addr Din Dout

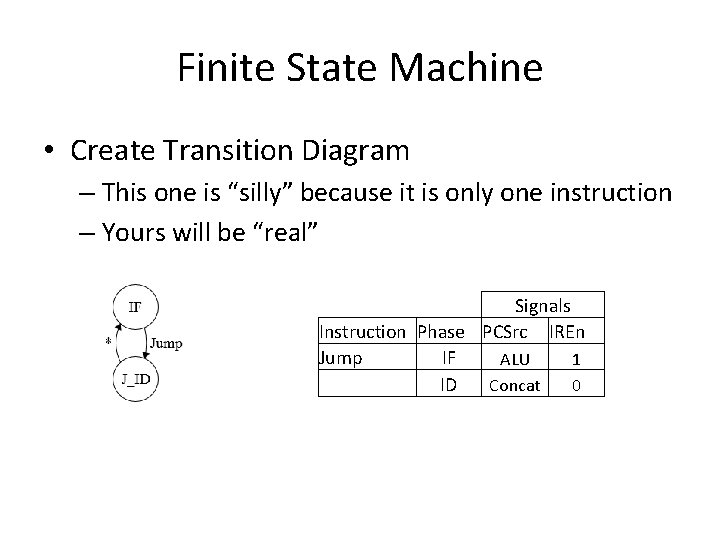

Finite State Machine • Create Transition Diagram – This one is “silly” because it is only one instruction – Yours will be “real” Signals Instruction Phase PCSrc IREn Jump IF ALU 1 ID Concat 0

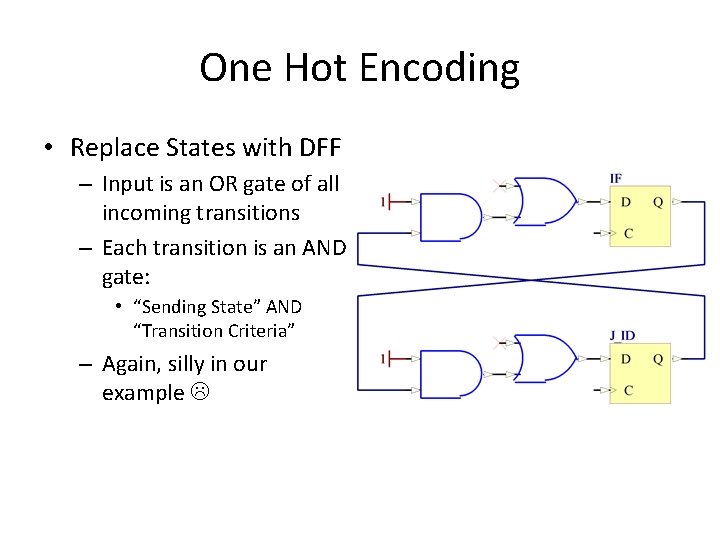

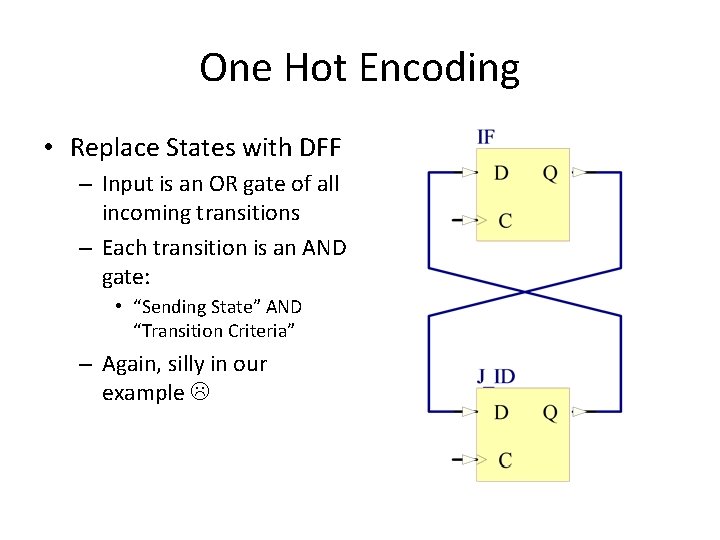

One Hot Encoding • Replace States with DFF – Input is an OR gate of all incoming transitions – Each transition is an AND gate: • “Sending State” AND “Transition Criteria” – Again, silly in our example

One Hot Encoding • Replace States with DFF – Input is an OR gate of all incoming transitions – Each transition is an AND gate: • “Sending State” AND “Transition Criteria” – Again, silly in our example

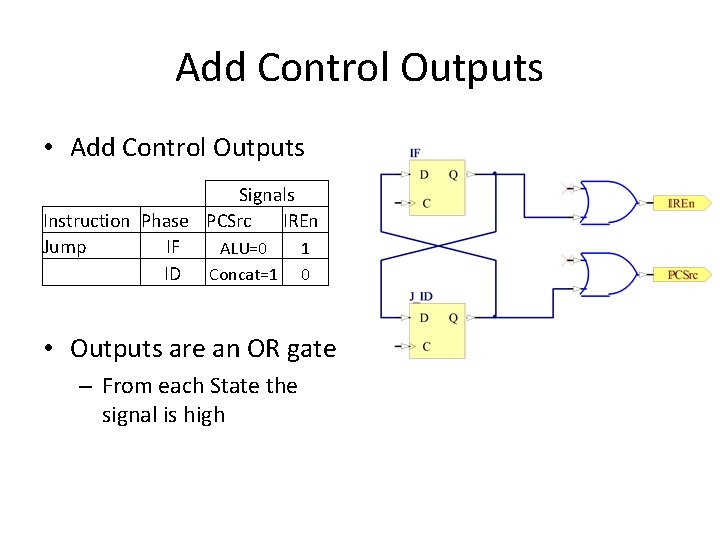

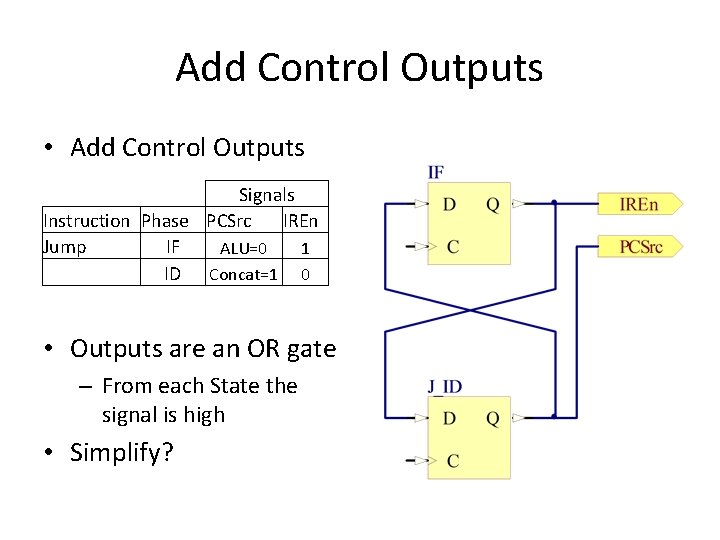

Add Control Outputs • Add Control Outputs Signals Instruction Phase PCSrc IREn Jump IF ALU=0 1 ID Concat=1 0 • Outputs are an OR gate – From each State the signal is high

Add Control Outputs • Add Control Outputs Signals Instruction Phase PCSrc IREn Jump IF ALU=0 1 ID Concat=1 0 • Outputs are an OR gate – From each State the signal is high • Simplify?

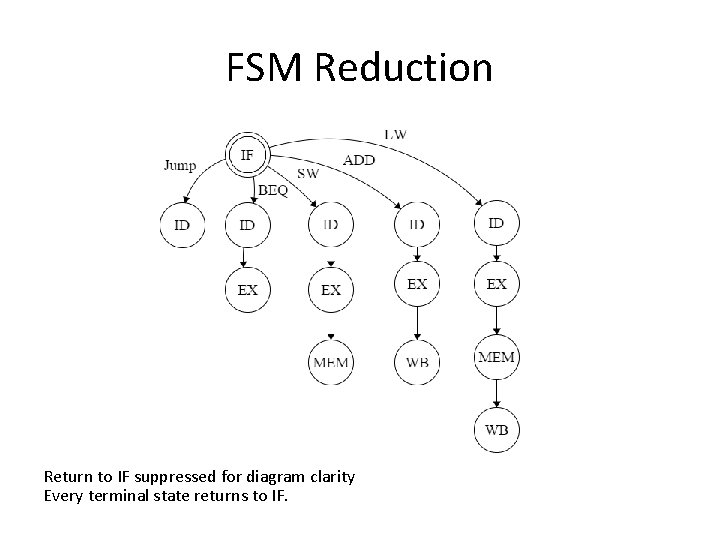

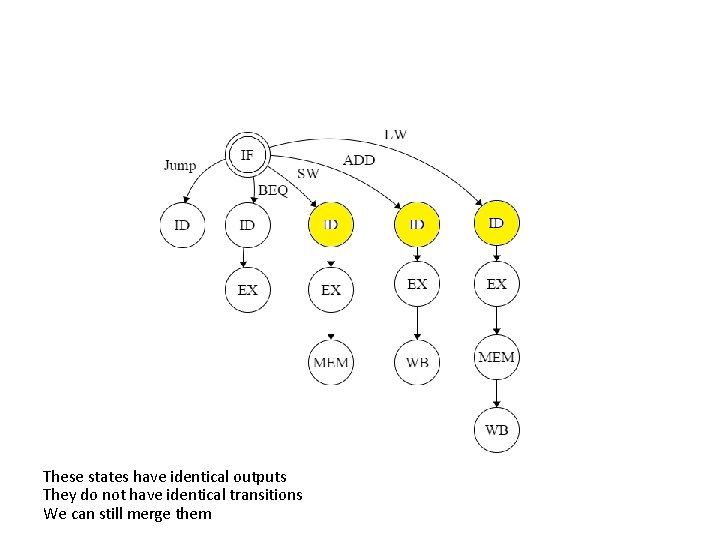

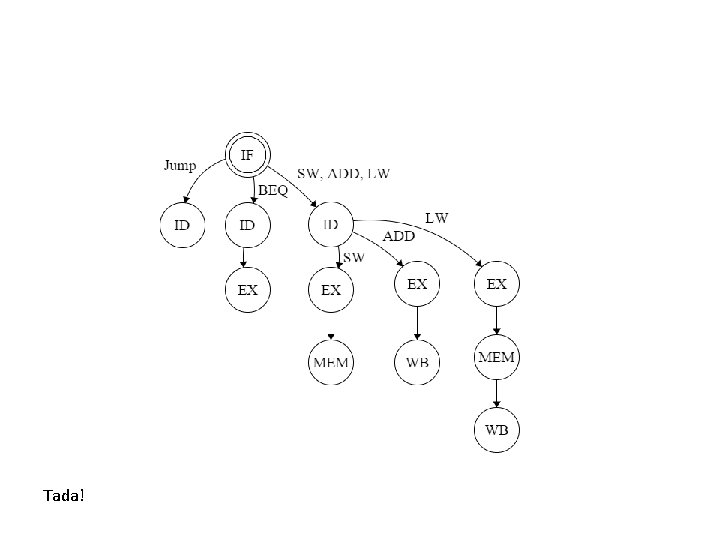

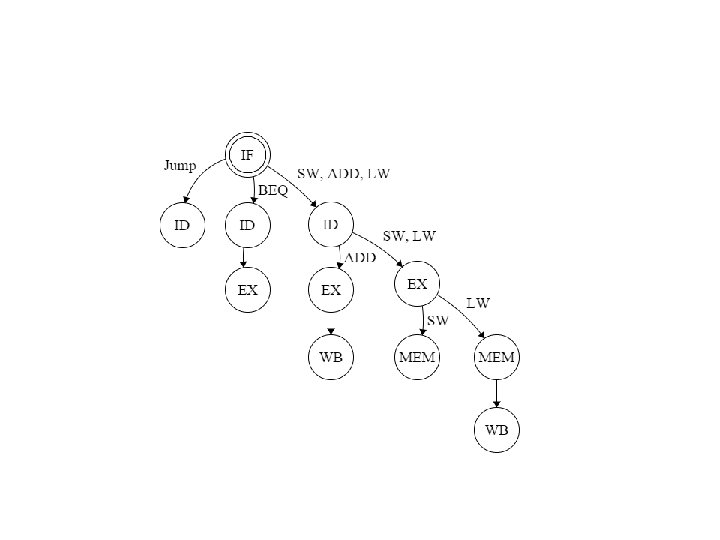

FSM Reduction Return to IF suppressed for diagram clarity Every terminal state returns to IF.

These states have identical outputs They do not have identical transitions We can still merge them

Tada!

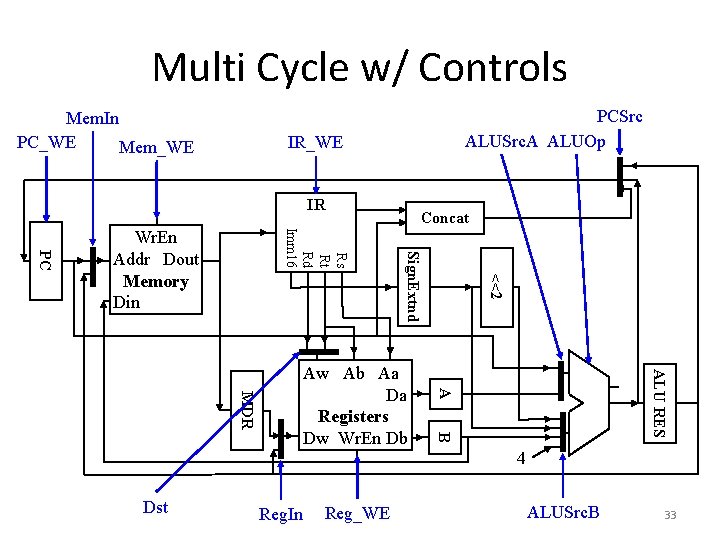

Multi Cycle w/ Controls Mem. In PC_WE Mem_WE PCSrc ALUSrc. A ALUOp IR_WE IR <<2 ALU RES Reg_WE B Reg. In A Aw Ab Aa Da Registers Dw Wr. En Db MDR Dst Sign. Extnd Rs Rt Rd Imm 16 PC Wr. En Addr Dout Memory Din Concat 4 ALUSrc. B 33

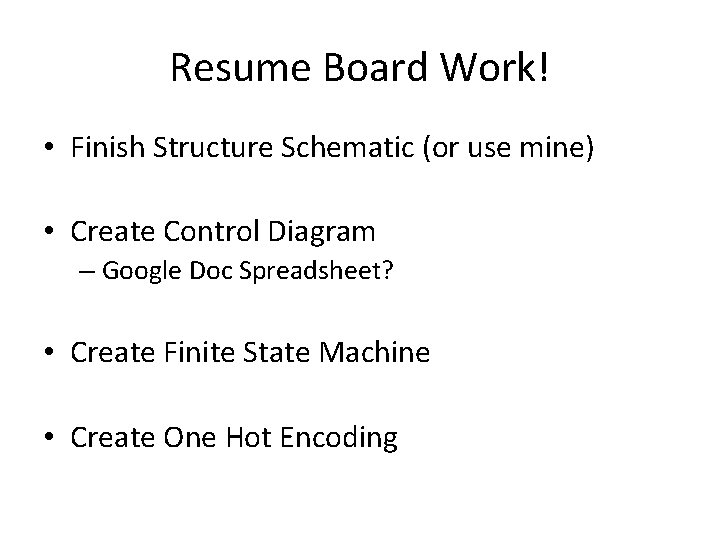

Resume Board Work! • Finish Structure Schematic (or use mine) • Create Control Diagram – Google Doc Spreadsheet? • Create Finite State Machine • Create One Hot Encoding

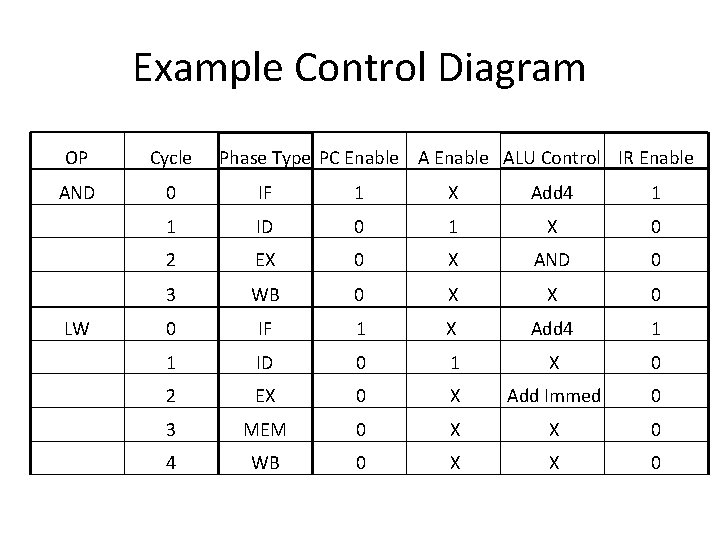

Example Control Diagram OP Cycle Phase Type PC Enable ALU Control IR Enable AND 0 IF 1 X Add 4 1 1 ID 0 1 X 0 2 EX 0 X AND 0 3 WB 0 X X 0 LW 0 IF 1 X Add 4 1 1 ID 0 1 X 0 2 EX 0 X Add Immed 0 3 MEM 0 X X 0 4 WB 0 X X 0

Phases: Load Word • IF: • ID: • EX: • MEM: • WB: Instruction Register = Memory[PC] PC=PC+4 A = Reg. File[rs] B = Reg. File[IR[16: 20]] Result = A + sign extended immediate Data. Reg = Mem[Result] Reg. File[rt] = Data. Reg

Phases: ADD • IF: • ID: • EX: • MEM: • WB: Instruction Register = Memory[PC] PC=PC+4 A = Reg. File[rs] B = Reg. File[rt] Result = A + B Reg. File[rd] = Result

Phases: Store Word • IF: • ID: • EX: • MEM: • WB: Instruction Register = Memory[PC] PC=PC+4 A = Reg. File[rs] B = Reg. File[rt] Result = A + sign extended immediate Mem[Result] = B

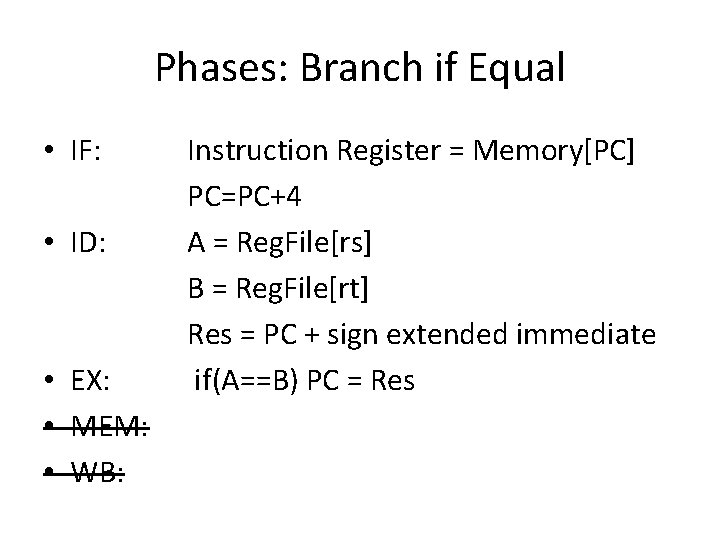

Phases: Branch if Equal • IF: • ID: • EX: • MEM: • WB: Instruction Register = Memory[PC] PC=PC+4 A = Reg. File[rs] B = Reg. File[rt] Res = PC + sign extended immediate if(A==B) PC = Res

![Phases: Jump • IF: • • ID: EX: MEM: WB: Instruction Register = Memory[PC] Phases: Jump • IF: • • ID: EX: MEM: WB: Instruction Register = Memory[PC]](http://slidetodoc.com/presentation_image/a1167ceeb8de856eac8bc19ee0507e0e/image-40.jpg)

Phases: Jump • IF: • • ID: EX: MEM: WB: Instruction Register = Memory[PC] PC=PC+4 PC = PC[31: 28], IR[25: 0], b 00

- Slides: 41