AVR Classic MKd taymerlr AVR Classic MKd taymerlrin

- Slides: 10

AVR Classic MK-də taymerlər

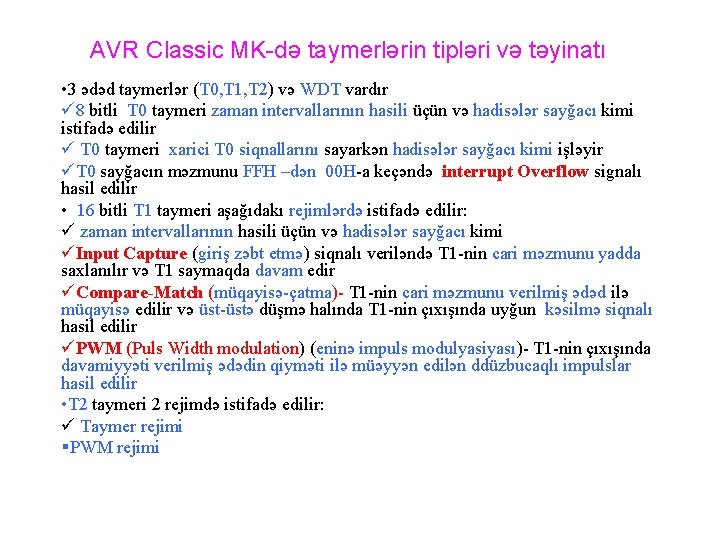

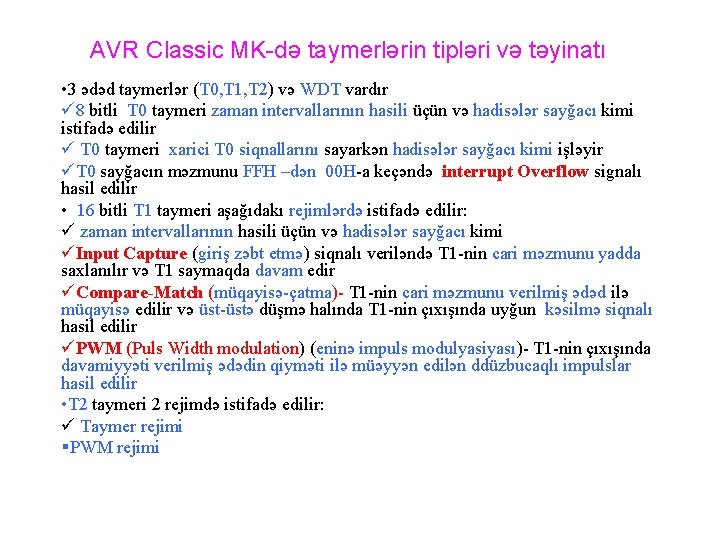

AVR Classic MK-də taymerlərin tipləri və təyinatı • 3 ədəd taymerlər (T 0, T 1, T 2) və WDT vardır ü 8 bitli T 0 taymeri zaman intervallarının hasili üçün və hadisələr sayğacı kimi istifadə edilir ü T 0 taymeri xarici T 0 siqnallarını sayarkən hadisələr sayğacı kimi işləyir üT 0 sayğacın məzmunu FFH –dən 00 H-a keçəndə interrupt Overflow signalı hasil edilir • 16 bitli T 1 taymeri aşağıdakı rejimlərdə istifadə edilir: ü zaman intervallarının hasili üçün və hadisələr sayğacı kimi üInput Capture (giriş zəbt etmə) siqnalı veriləndə T 1 -nin cari məzmunu yadda saxlanılır və T 1 saymaqda davam edir üCompare-Match (müqayisə-çatma)- T 1 -nin cari məzmunu verilmiş ədəd ilə müqayisə edilir və üst-üstə düşmə halında T 1 -nin çıxışında uyğun kəsilmə siqnalı hasil edilir üPWM (Puls Width modulation) (eninə impuls modulyasiyası)- T 1 -nin çıxışında davamiyyəti verilmiş ədədin qiyməti ilə müəyyən edilən ddüzbucaqlı impulslar hasil edilir • T 2 taymeri 2 rejimdə istifadə edilir: ü Taymer rejimi §PWM rejimi

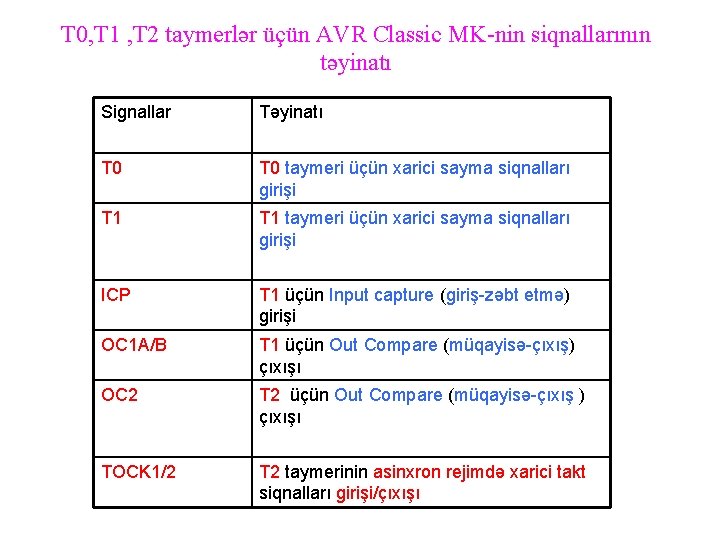

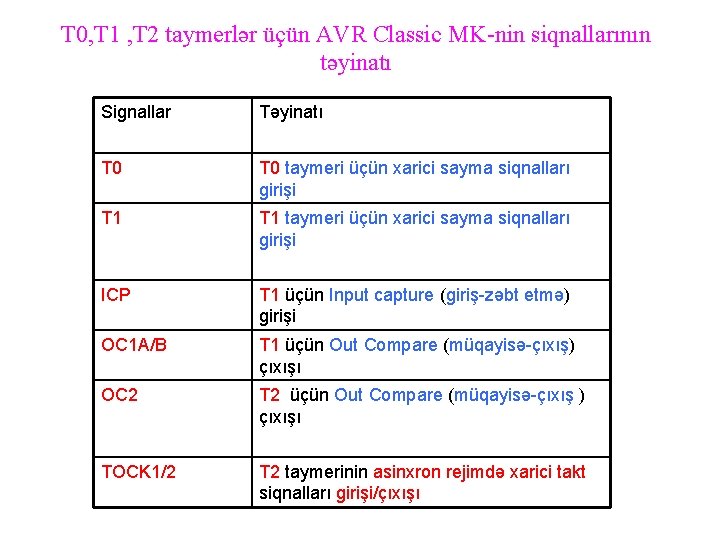

T 0, T 1 , T 2 taymerlər üçün AVR Classic MK-nin siqnallarının təyinatı Signallar Təyinatı T 0 taymeri üçün xarici sayma siqnalları girişi T 1 taymeri üçün xarici sayma siqnalları girişi ICP T 1 üçün Input capture (giriş-zəbt etmə) girişi OC 1 A/B T 1 üçün Out Compare (müqayisə-çıxış) çıxışı OC 2 T 2 üçün Out Compare (müqayisə-çıxış ) çıxışı TOCK 1/2 T 2 taymerinin asinxron rejimdə xarici takt siqnalları girişi/çıxışı

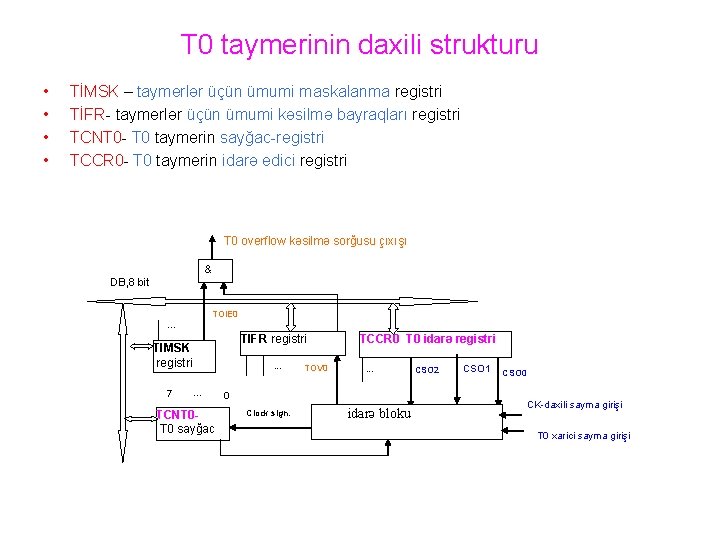

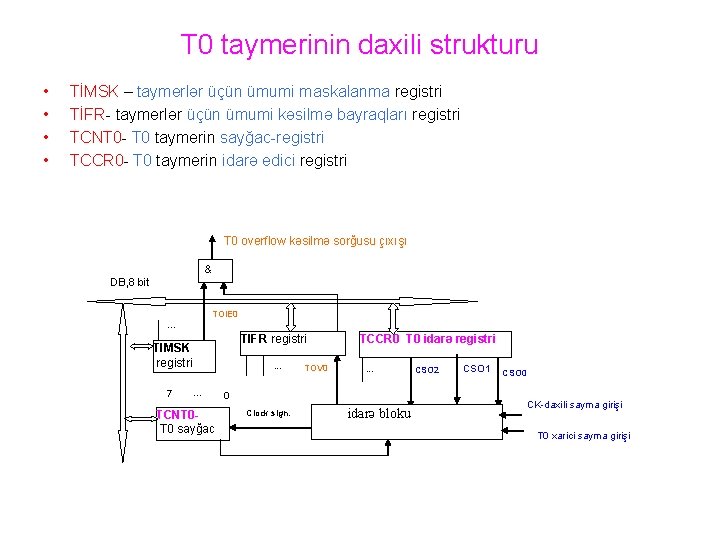

T 0 taymerinin daxili strukturu • • TİMSK – taymerlər üçün ümumi maskalanma registri TİFR- taymerlər üçün ümumi kəsilmə bayraqları registri TCNT 0 - T 0 taymerin sayğac-registri TCCR 0 - T 0 taymerin idarə edici registri T 0 overflow kəsilmə sorğusu çıxışı & DB, 8 bit TOIE 0 . . . TIFR registri TIMSK registri 7 . . . TCNT 0 T 0 sayğac TOV 0 TCCR 0 T 0 idarə registri. . . 0 Clock sign. idarə bloku CSO 2 CSO 1 CSO 0 CK-daxili sayma girişi T 0 xarici sayma girişi

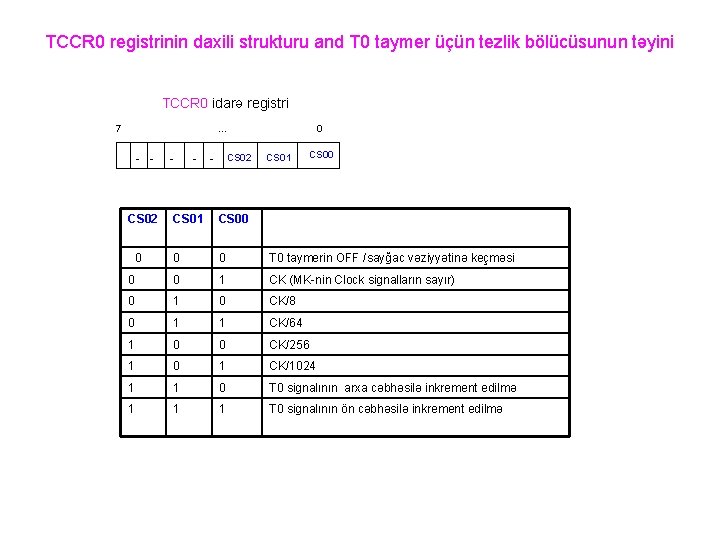

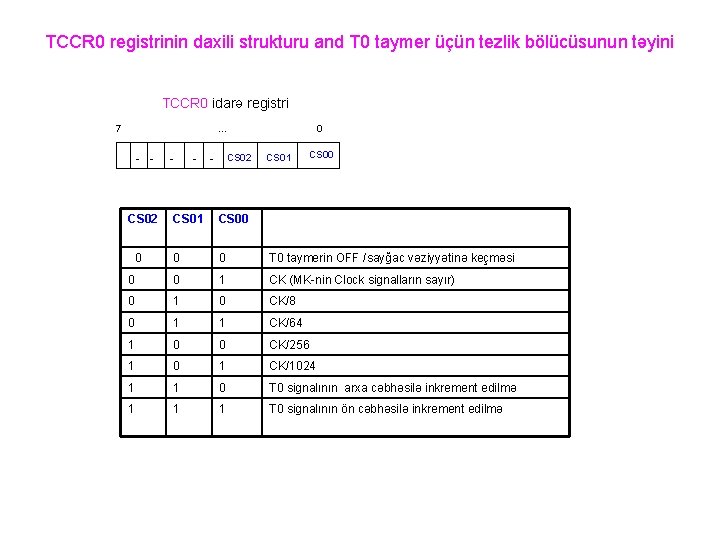

TCCR 0 registrinin daxili strukturu and T 0 taymer üçün tezlik bölücüsunun təyini TCCR 0 idarə registri … 7 - - CS 02 - 0 CS 01 CS 00 0 0 T 0 taymerin OFF /sayğac vəziyyətinə keçməsi 0 0 1 CK (MK-nin Clock signalların sayır) 0 1 0 CK/8 0 1 1 CK/64 1 0 0 CK/256 1 0 1 CK/1024 1 1 0 T 0 signalının arxa cəbhəsilə inkrement edilmə 1 1 1 T 0 signalının ön cəbhəsilə inkrement edilmə 0

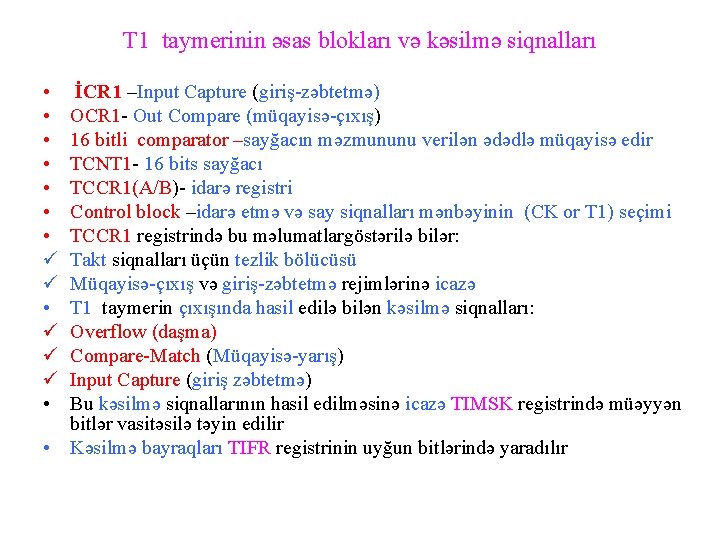

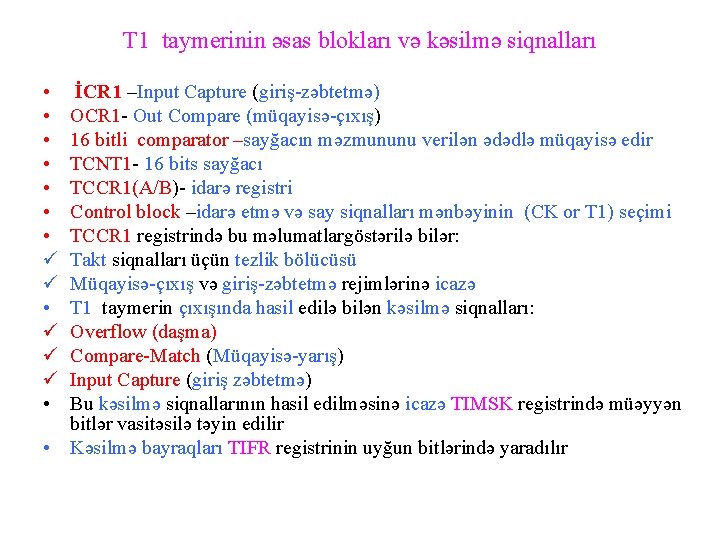

T 1 taymerinin əsas blokları və kəsilmə siqnalları • • ü ü ü • İCR 1 –Input Capture (giriş-zəbtetmə) OCR 1 - Out Compare (müqayisə-çıxış) 16 bitli comparator –sayğacın məzmununu verilən ədədlə müqayisə edir TCNT 1 - 16 bits sayğacı TCCR 1(A/B)- idarə registri Control block –idarə etmə və say siqnalları mənbəyinin (CK or T 1) seçimi TCCR 1 registrində bu məlumatlargöstərilə bilər: Takt siqnalları üçün tezlik bölücüsü Müqayisə-çıxış və giriş-zəbtetmə rejimlərinə icazə T 1 taymerin çıxışında hasil edilə bilən kəsilmə siqnalları: Overflow (daşma) Compare-Match (Müqayisə-yarış) Input Capture (giriş zəbtetmə) Bu kəsilmə siqnallarının hasil edilməsinə icazə TIMSK registrində müəyyən bitlər vasitəsilə təyin edilir • Kəsilmə bayraqları TIFR registrinin uyğun bitlərində yaradılır

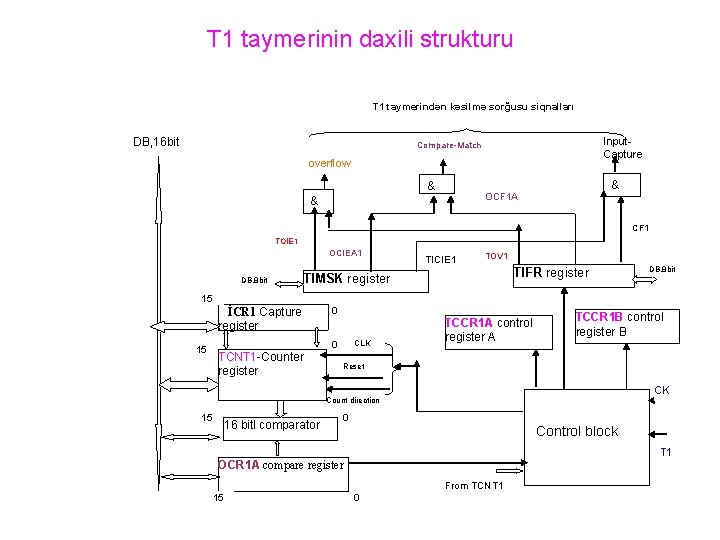

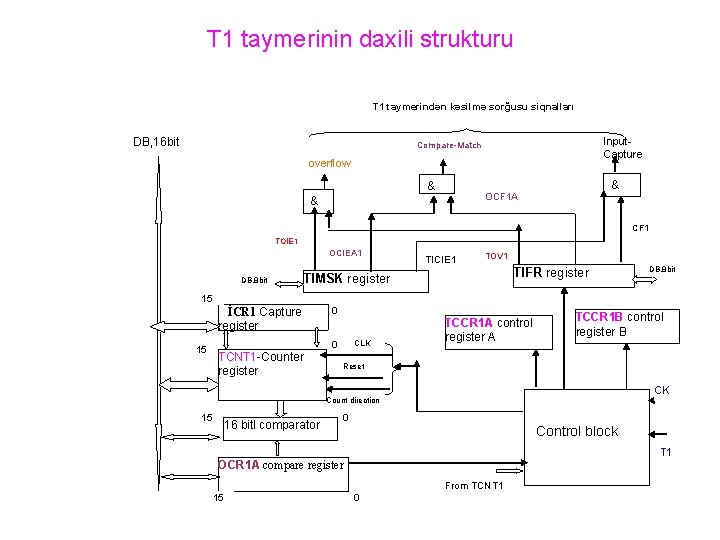

T 1 taymerinin daxili strukturu T 1 taymerindən kəsilmə sorğusu siqnalları DB, 16 bit Input. Capture Compare-Match overflow & & OCF 1 A & CF 1 TOIE 1 OCIEA 1 DB, 8 bit TICIE 1 TOV 1 TIFR register TIMSK register DB, 8 bit 15 İCR 1 Capture register 15 0 CLK 0 TCNT 1 -Counter register TCCR 1 A control register A TCCR 1 B control register B Reset CK Count direction 15 16 bitl comparator 0 Control block T 1 OCR 1 A compare register From TCNT 1 15 0

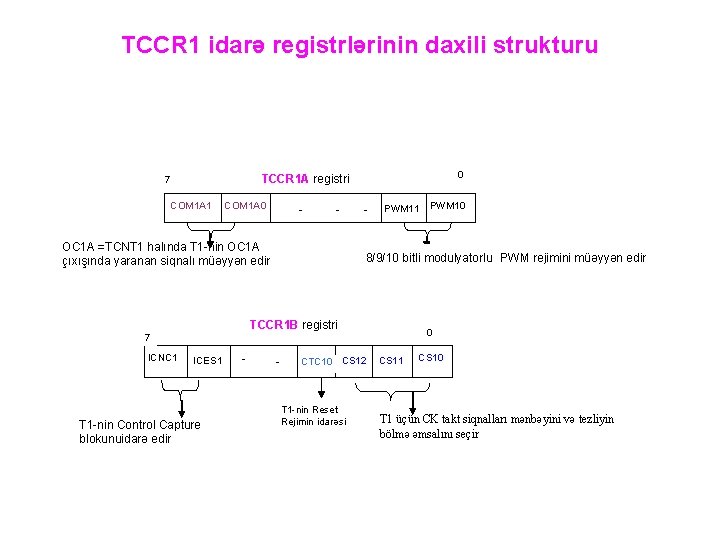

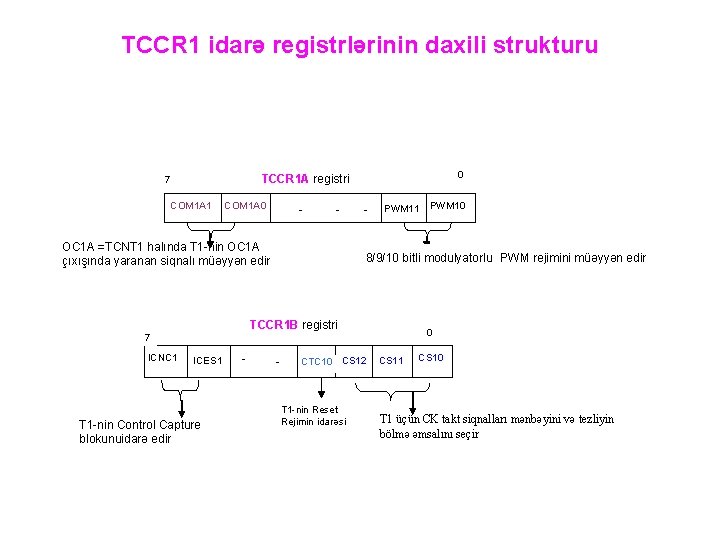

TCCR 1 idarə registrlərinin daxili strukturu 0 TCCR 1 A registri 7 COM 1 A 1 COM 1 A 0 - - OC 1 A =TCNT 1 halında T 1 -nin OC 1 A çıxışında yaranan siqnalı müəyyən edir - PWM 11 8/9/10 bitli modulyatorlu PWM rejimini müəyyən edir TCCR 1 B registri 0 7 ICNC 1 ICES 1 T 1 -nin Control Capture blokunuidarə edir - PWM 10 - CTC 10 CS 12 T 1 -nin Reset Rejimin idarəsi CS 11 CS 10 T 1 üçün CK takt siqnalları mənbəyini və tezliyin bölmə əmsalını seçir

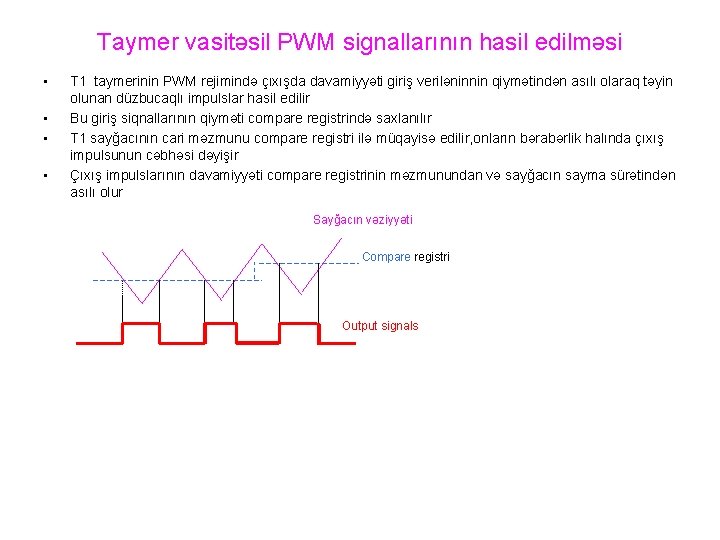

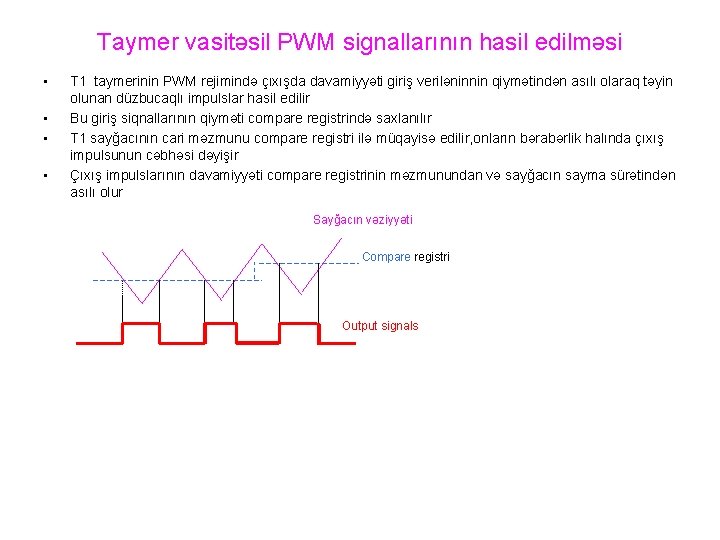

Taymer vasitəsil PWM signallarının hasil edilməsi • • T 1 taymerinin PWM rejimində çıxışda davamiyyəti giriş veriləninnin qiymətindən asılı olaraq təyin olunan düzbucaqlı impulslar hasil edilir Bu giriş siqnallarının qiyməti compare registrində saxlanılır T 1 sayğacının cari məzmunu compare registri ilə müqayisə edilir, onların bərabərlik halında çıxış impulsunun cəbhəsi dəyişir Çıxış impulslarının davamiyyəti compare registrinin məzmunundan və sayğacın sayma sürətindən asılı olur Sayğacın vəziyyəti Compare registri Output signals

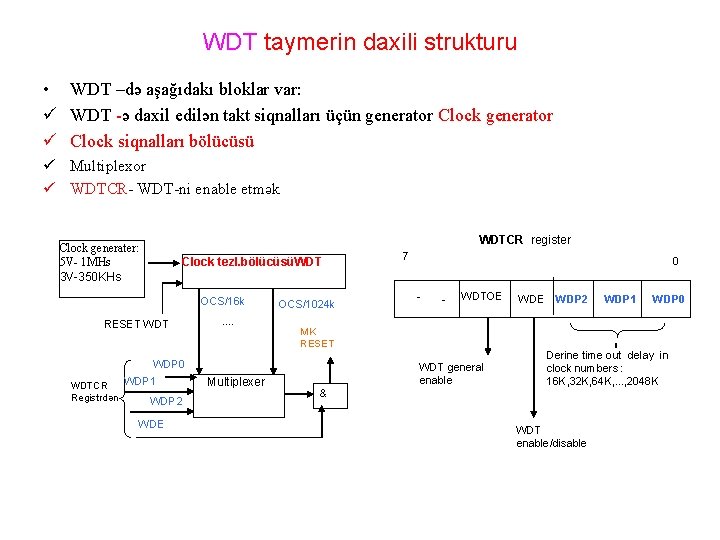

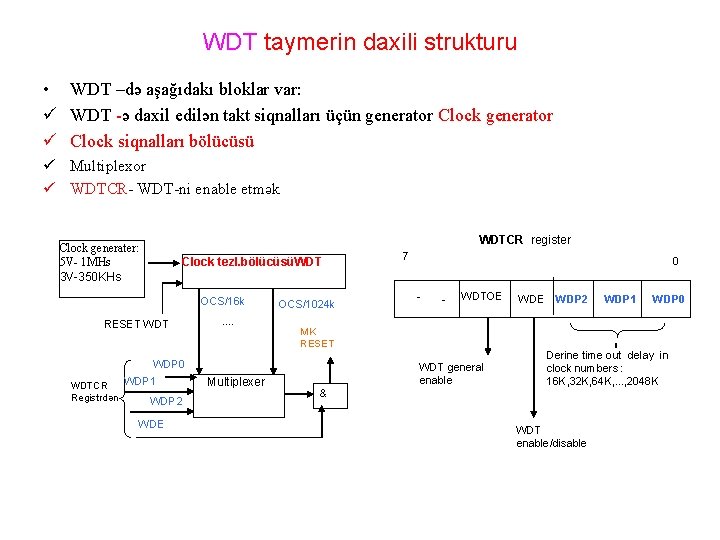

WDT taymerin daxili strukturu • WDT –də aşağıdakı bloklar var: ü WDT -ə daxil edilən takt siqnalları üçün generator Clock generator ü Clock siqnalları bölücüsü ü Multiplexor ü WDTCR- WDT-ni enable etmək WDTCR register Clock generater: 5 V- 1 MHs 3 V-350 KHs Clock tezl. bölücüsüWDT OCS/16 k RESET WDT . . OCS/1024 k WDE Multiplexer 0 - - WDTOE MK RESET WDP 0 WDP 1 WDTCR Registrdən WDP 2 7 WDT general enable & WDE WDP 2 WDP 1 WDP 0 Derine time out delay in clock numbers : 16 K, 32 K, 64 K, . . . , 2048 K WDT enable/disable