Automatic Model Refinement of Gm C Integrators for

![Simplified Gm. C Model [Zele, Allstot, JSSC’ 96] Simplified models are not sufficiently accurate Simplified Gm. C Model [Zele, Allstot, JSSC’ 96] Simplified models are not sufficiently accurate](https://slidetodoc.com/presentation_image_h2/d799de234fa28f9156adde19830c1360/image-9.jpg)

- Slides: 20

Automatic Model Refinement of Gm. C Integrators for High-Level Simulations of Continuous-Time Sigma-Delta Modulators Michel Vasilevski Hassan Aboushady, Marie-Minerve Louërat Laboratory LIP 6 University Pierre and Marie Curie, Paris 6, France May 2009

Outline 1. Motivations 2. Gm. C Model Refinement 3. Characterization Flow 4. Results and Application 5. Conclusion M. Vasilevski Laboratory LIP 6, University Paris 6 2

Outline 1. Motivations 2. Gm. C Model Refinement 3. Characterization Flow 4. Results and Application 5. Conclusion M. Vasilevski Laboratory LIP 6, University Paris 6 3

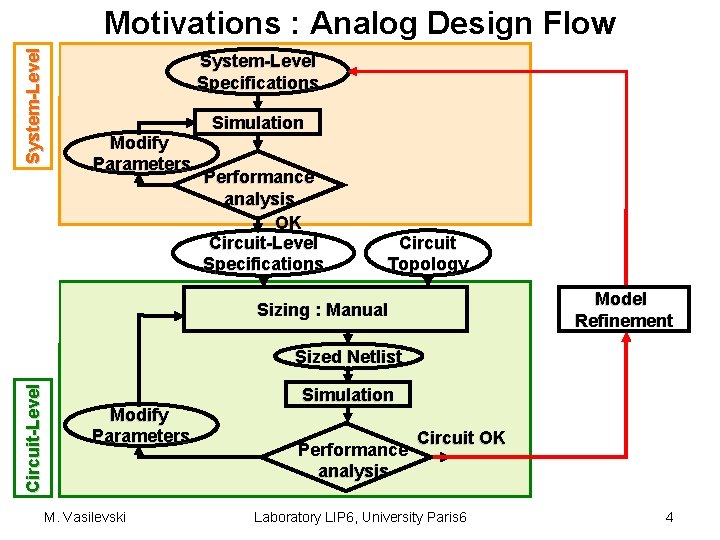

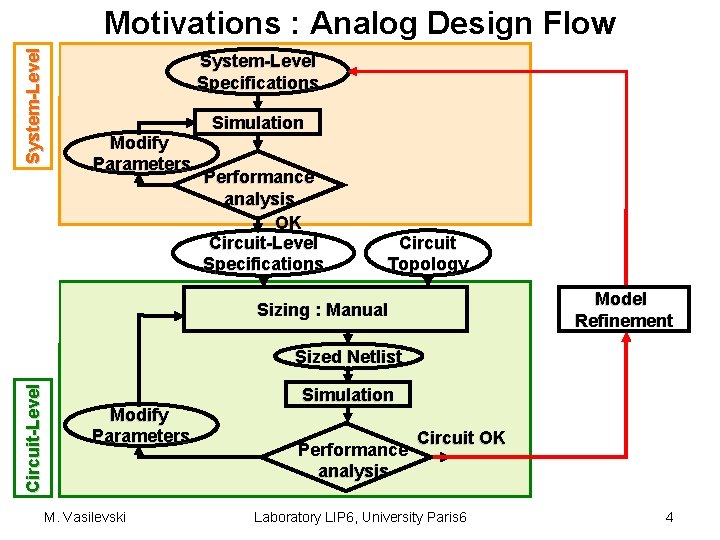

S y s te m -L e v e l Motivations : Analog Design Flow System-Level Specifications Modify Parameters Simulation Performance analysis OK Circuit-Level Specifications Circuit Topology Model Refinement Sizing : Manual C i r c u i t-L e v e l Sized Netlist Modify Parameters M. Vasilevski Simulation Performance analysis Circuit OK Laboratory LIP 6, University Paris 6 4

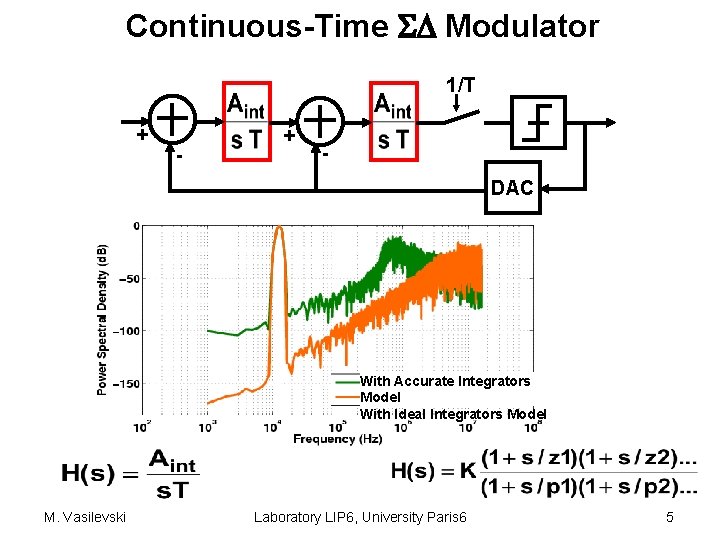

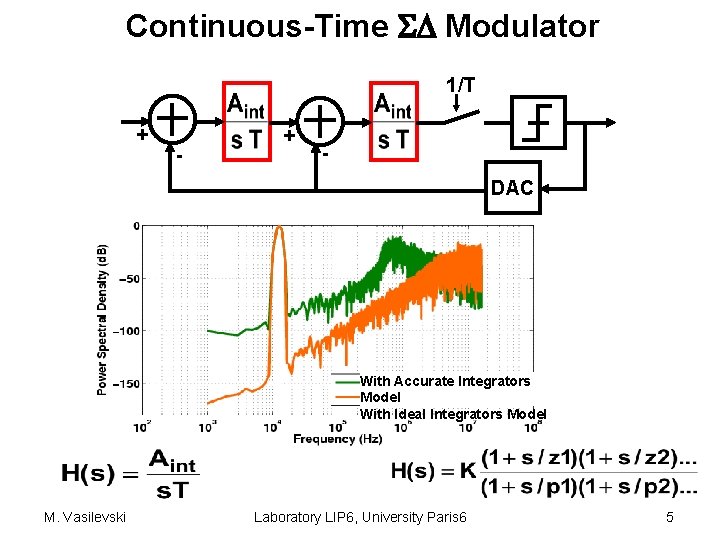

Continuous-Time SD Modulator 1/T + - + DAC With Accurate Integrators Model With Ideal Integrators Model M. Vasilevski Laboratory LIP 6, University Paris 6 5

Outline 1. Motivations 2. Gm. C Model Refinement 3. Characterization Flow 4. Results and Application 5. Conclusion M. Vasilevski Laboratory LIP 6, University Paris 6 6

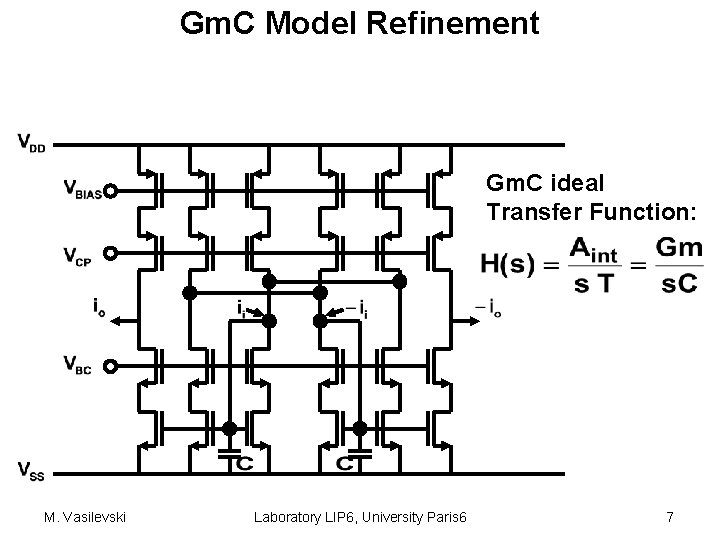

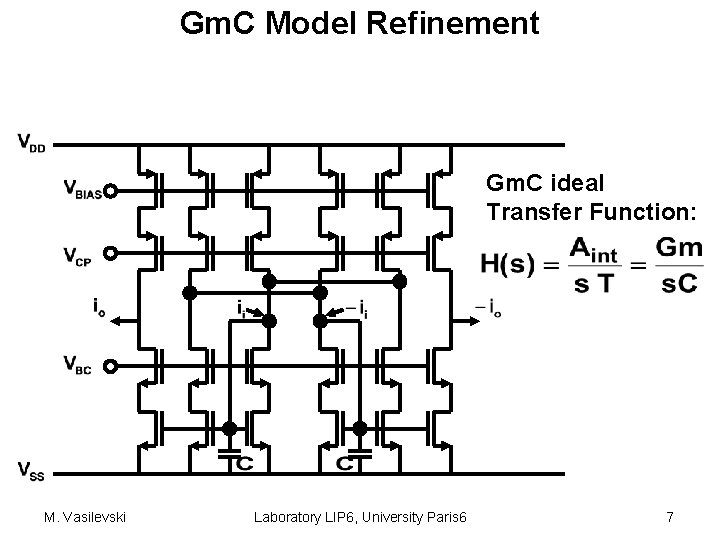

Gm. C Model Refinement Gm. C ideal Transfer Function: M. Vasilevski Laboratory LIP 6, University Paris 6 7

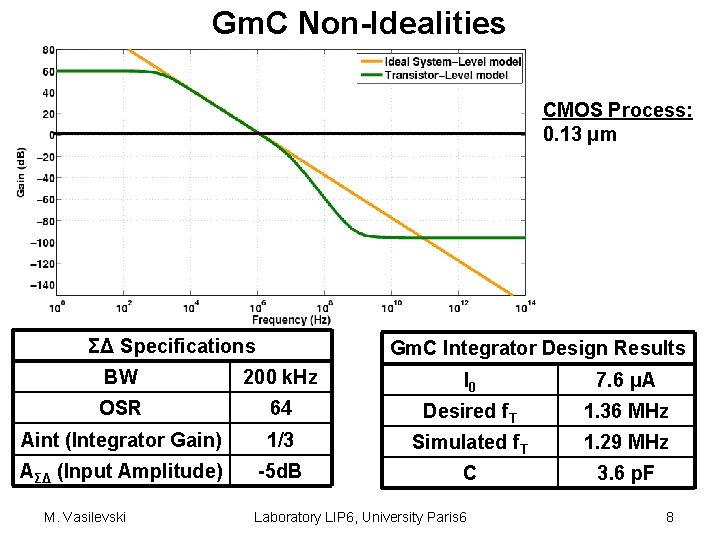

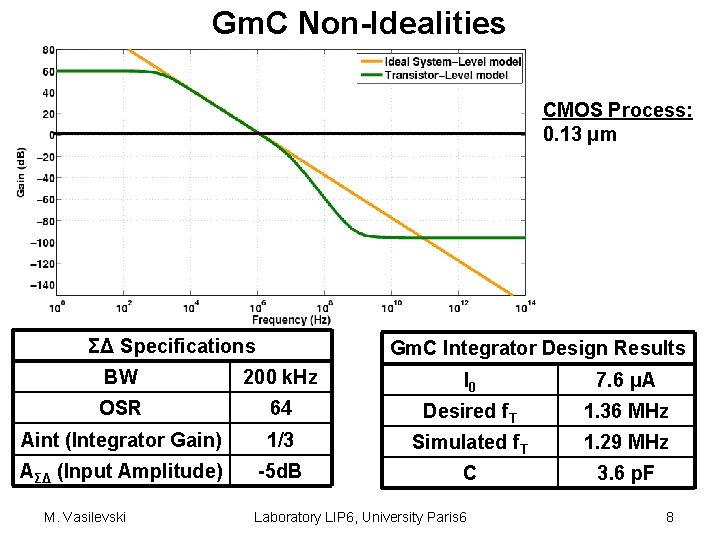

Gm. C Non-Idealities CMOS Process: 0. 13 μm ΣΔ Specifications Gm. C Integrator Design Results BW 200 k. Hz I 0 7. 6 μA OSR 64 Desired f. T 1. 36 MHz Aint (Integrator Gain) 1/3 Simulated f. T 1. 29 MHz AΣΔ (Input Amplitude) -5 d. B C 3. 6 p. F M. Vasilevski Laboratory LIP 6, University Paris 6 8

![Simplified Gm C Model Zele Allstot JSSC 96 Simplified models are not sufficiently accurate Simplified Gm. C Model [Zele, Allstot, JSSC’ 96] Simplified models are not sufficiently accurate](https://slidetodoc.com/presentation_image_h2/d799de234fa28f9156adde19830c1360/image-9.jpg)

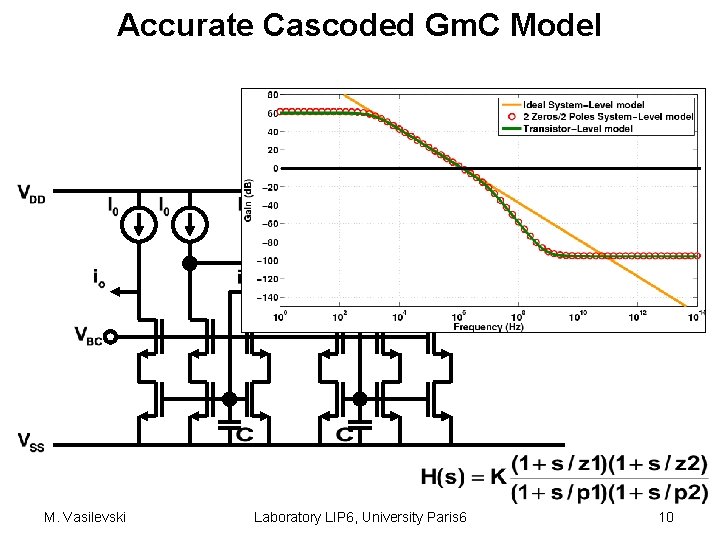

Simplified Gm. C Model [Zele, Allstot, JSSC’ 96] Simplified models are not sufficiently accurate M. Vasilevski Laboratory LIP 6, University Paris 6 9

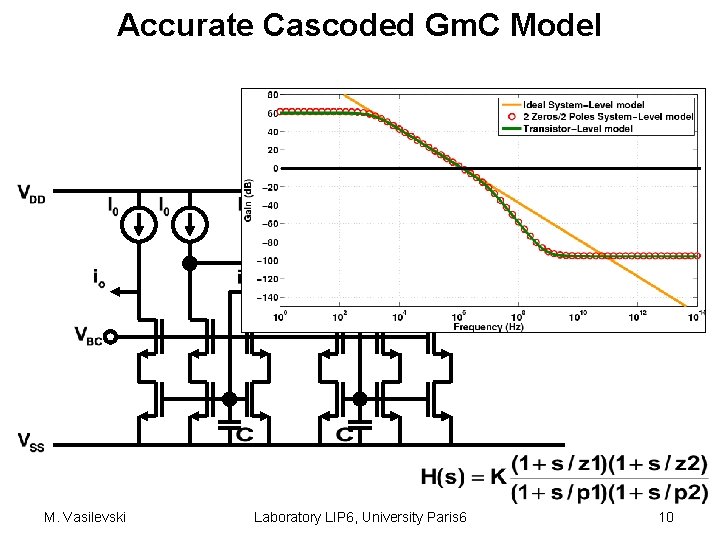

Accurate Cascoded Gm. C Model M. Vasilevski Laboratory LIP 6, University Paris 6 10

Outline 1. Motivations 2. Gm. C Model Refinement 3. Characterization Flow 4. Results and Application 5. Conclusion M. Vasilevski Laboratory LIP 6, University Paris 6 11

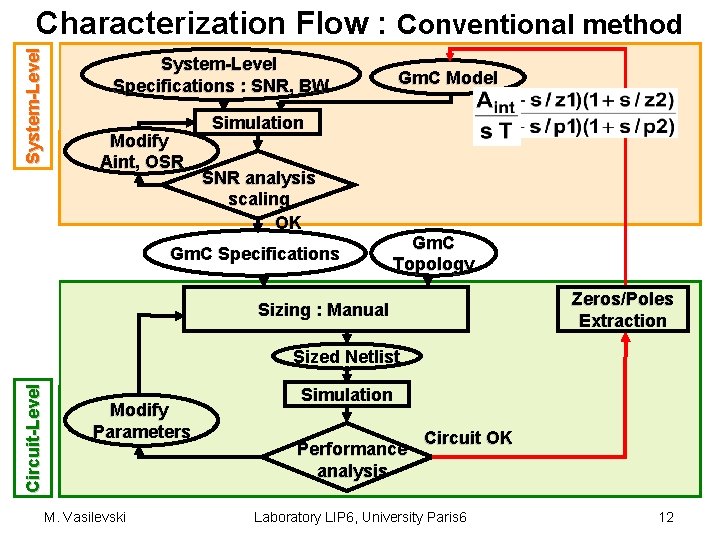

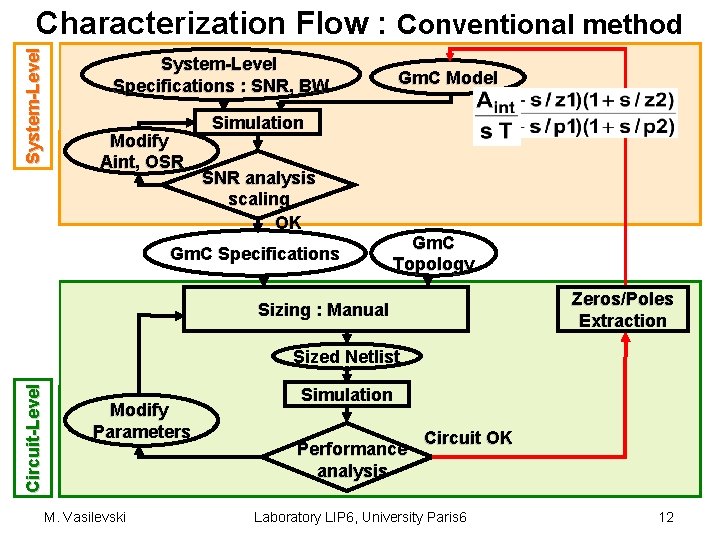

S y s te m -L e v e l Characterization Flow : Conventional method System-Level Specifications : SNR, BW Modify Aint, OSR Gm. C Model Simulation SNR analysis scaling OK Gm. C Specifications Gm. C Topology Zeros/Poles Extraction Sizing : Manual C i r c u i t-L e v e l Sized Netlist Modify Parameters M. Vasilevski Simulation Performance analysis Circuit OK Laboratory LIP 6, University Paris 6 12

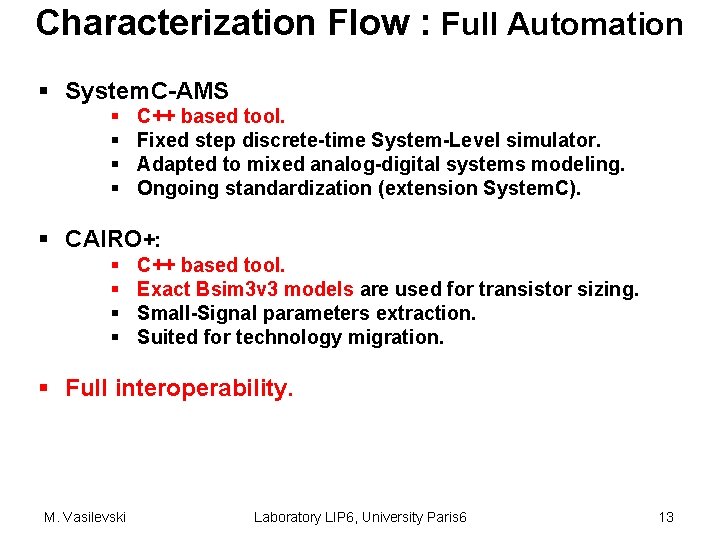

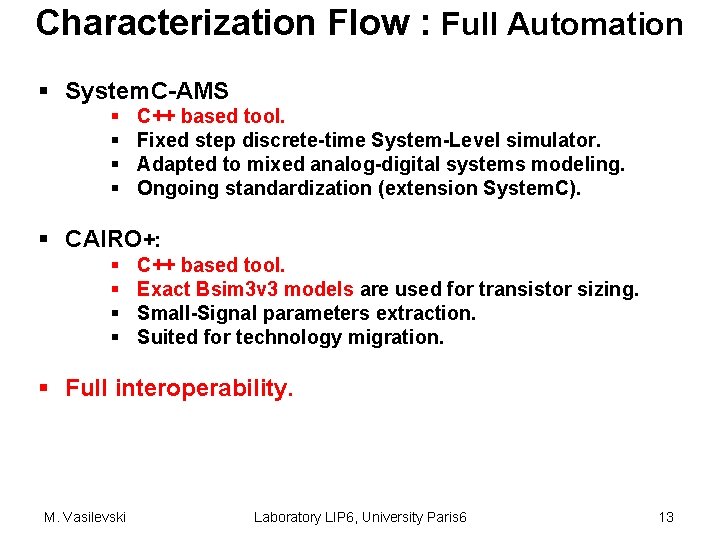

Characterization Flow : Full Automation § System. C-AMS § § C++ based tool. Fixed step discrete-time System-Level simulator. Adapted to mixed analog-digital systems modeling. Ongoing standardization (extension System. C). § CAIRO+: § § C++ based tool. Exact Bsim 3 v 3 models are used for transistor sizing. Small-Signal parameters extraction. Suited for technology migration. § Full interoperability. M. Vasilevski Laboratory LIP 6, University Paris 6 13

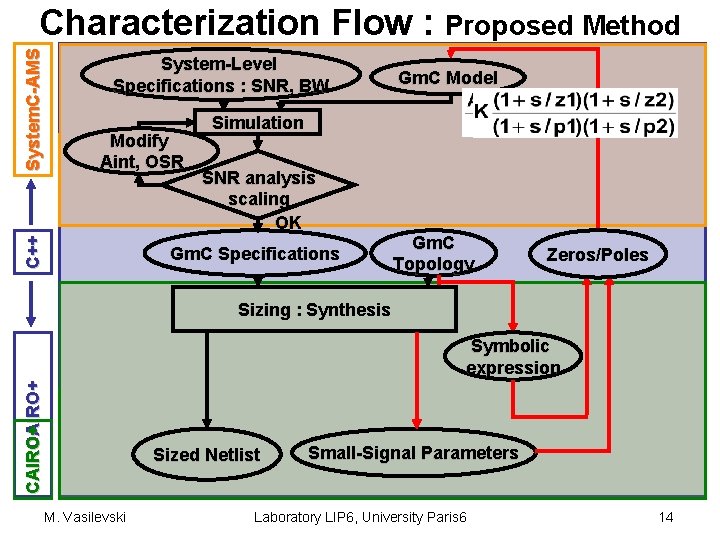

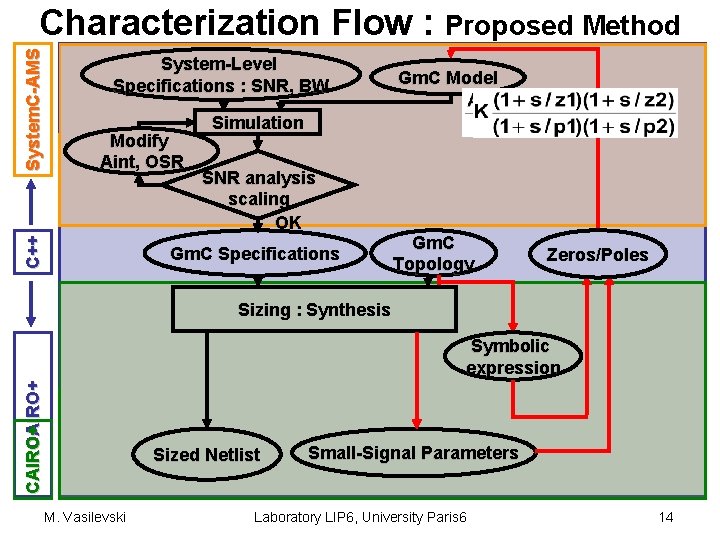

System-Level Specifications : SNR, BW Modify Aint, OSR C+ + S y s te m C -A MS Characterization Flow : Proposed Method Gm. C Model Simulation SNR analysis scaling OK Gm. C Specifications Gm. C Topology Zeros/Poles Sizing : Synthesis CAI RO C+ AI RO + Symbolic expression Sized Netlist M. Vasilevski Small-Signal Parameters Laboratory LIP 6, University Paris 6 14

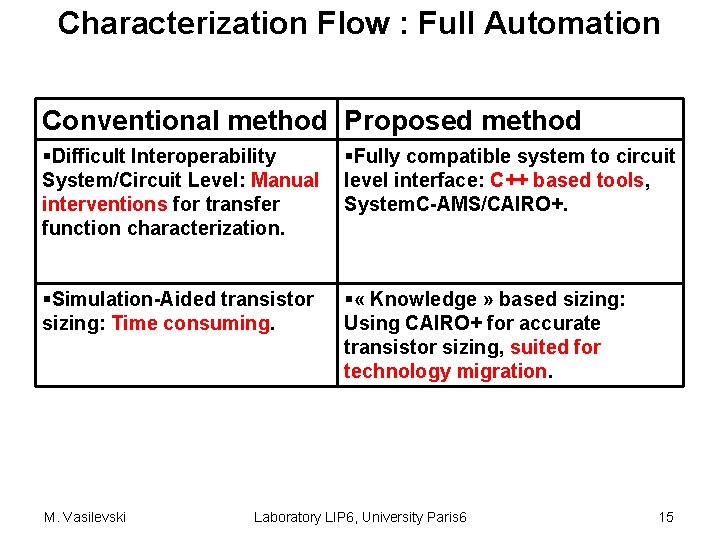

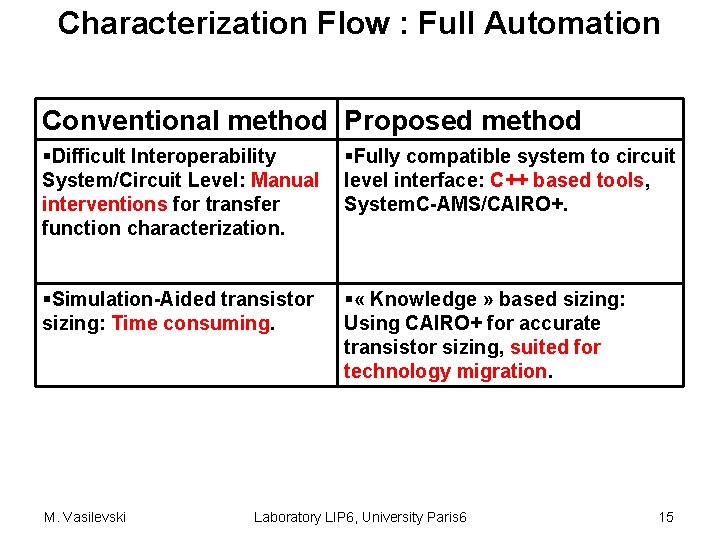

Characterization Flow : Full Automation Conventional method Proposed method §Difficult Interoperability System/Circuit Level: Manual interventions for transfer function characterization. §Fully compatible system to circuit level interface: C++ based tools, System. C-AMS/CAIRO+. §Simulation-Aided transistor sizing: Time consuming. § « Knowledge » based sizing: Using CAIRO+ for accurate transistor sizing, suited for technology migration. M. Vasilevski Laboratory LIP 6, University Paris 6 15

Outline 1. Motivations 2. Gm. C Model Refinement 3. Characterization Flow 4. Results and Application 5. Conclusion M. Vasilevski Laboratory LIP 6, University Paris 6 16

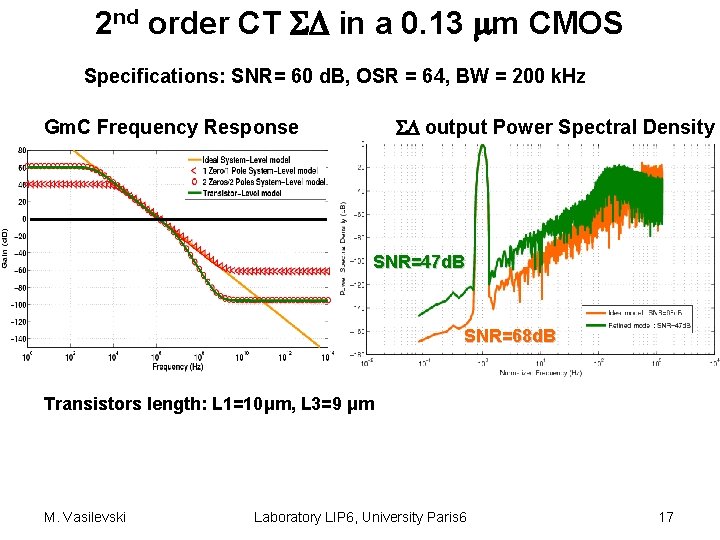

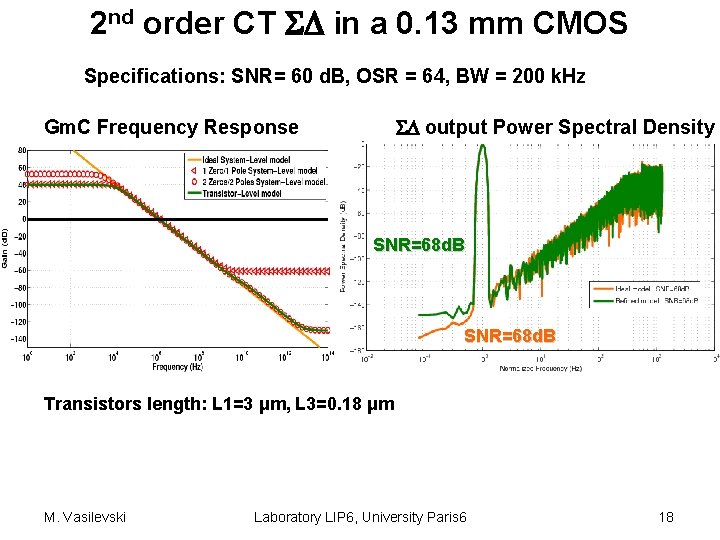

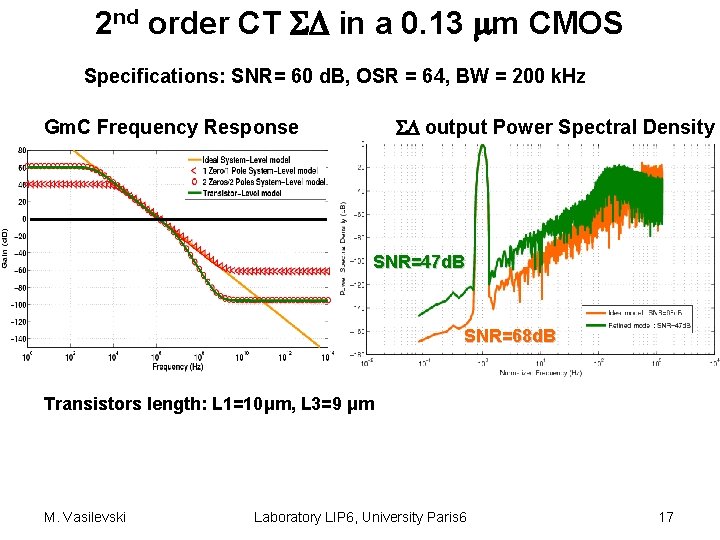

2 nd order CT SD in a 0. 13 mm CMOS Specifications: SNR= 60 d. B, OSR = 64, BW = 200 k. Hz SD output Power Spectral Density Gm. C Frequency Response SNR=47 d. B SNR=68 d. B Transistors length: L 1=10μm, L 3=9 μm M. Vasilevski Laboratory LIP 6, University Paris 6 17

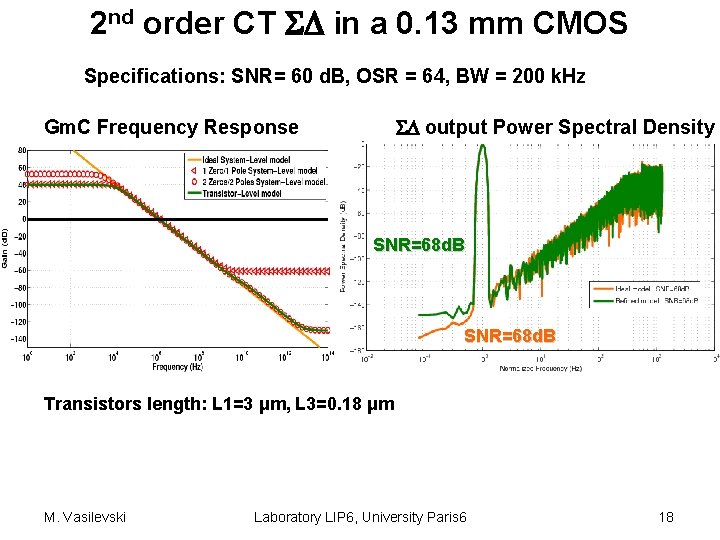

2 nd order CT SD in a 0. 13 mm CMOS Specifications: SNR= 60 d. B, OSR = 64, BW = 200 k. Hz SD output Power Spectral Density Gm. C Frequency Response SNR=68 d. B Transistors length: L 1=3 μm, L 3=0. 18 μm M. Vasilevski Laboratory LIP 6, University Paris 6 18

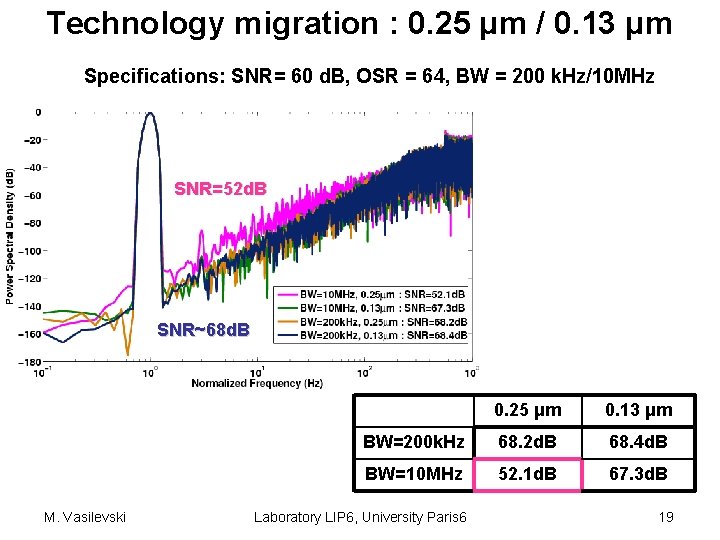

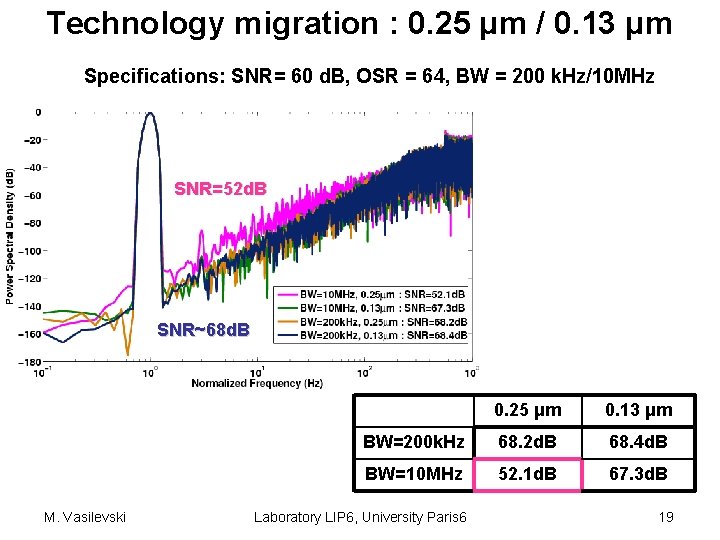

Technology migration : 0. 25 μm / 0. 13 μm Specifications: SNR= 60 d. B, OSR = 64, BW = 200 k. Hz/10 MHz SNR=52 d. B SNR~68 d. B M. Vasilevski 0. 25 μm 0. 13 μm BW=200 k. Hz 68. 2 d. B 68. 4 d. B BW=10 MHz 52. 1 d. B 67. 3 d. B Laboratory LIP 6, University Paris 6 19

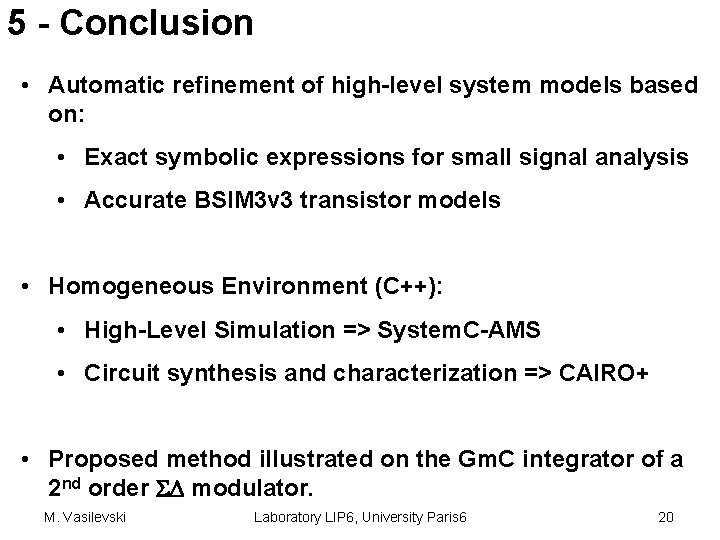

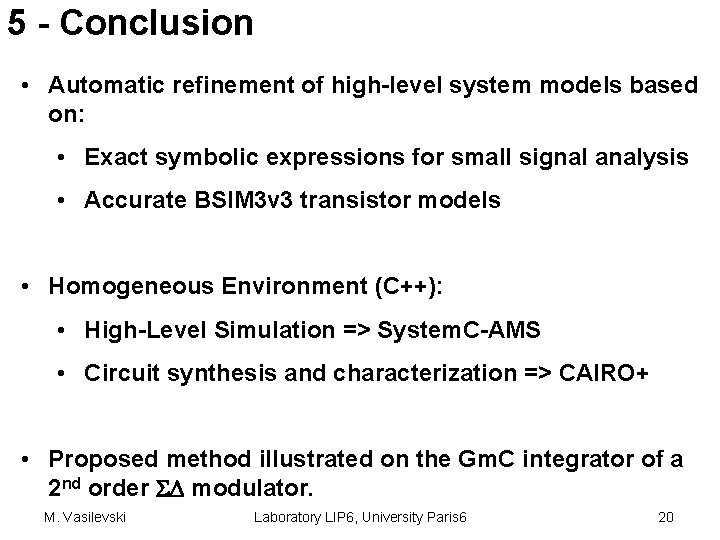

5 - Conclusion • Automatic refinement of high-level system models based on: • Exact symbolic expressions for small signal analysis • Accurate BSIM 3 v 3 transistor models • Homogeneous Environment (C++): • High-Level Simulation => System. C-AMS • Circuit synthesis and characterization => CAIRO+ • Proposed method illustrated on the Gm. C integrator of a 2 nd order SD modulator. M. Vasilevski Laboratory LIP 6, University Paris 6 20